# **Spread Spectrum Clock Generator**

# **MB88153**

#### **■ DESCRIPTION**

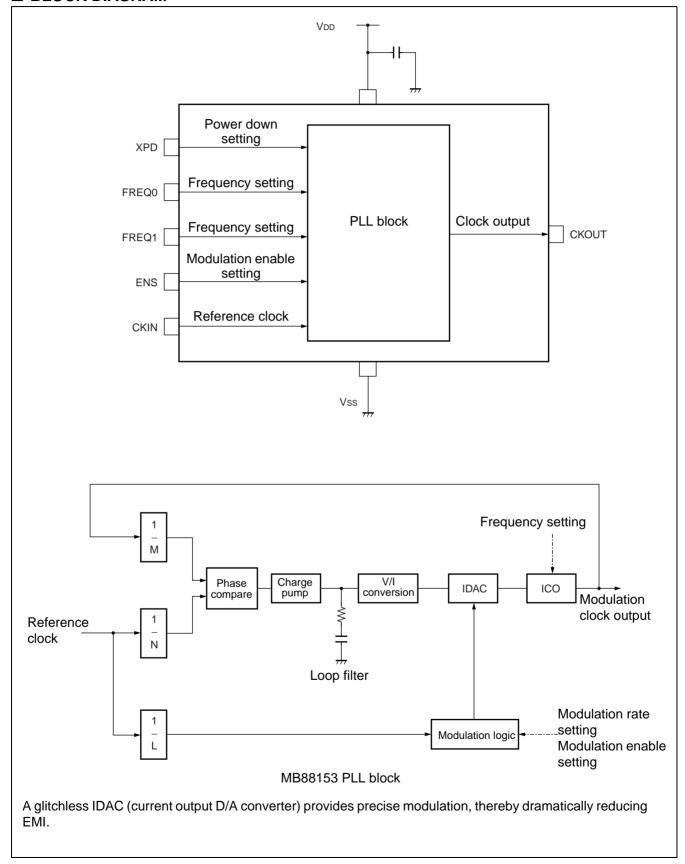

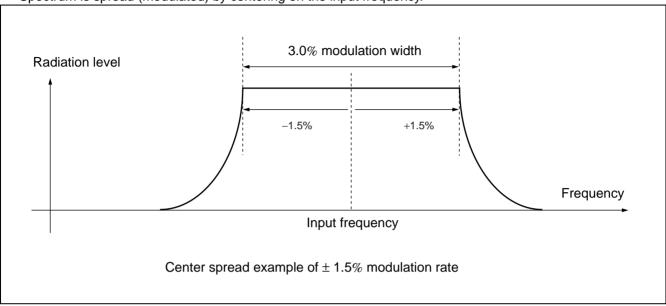

MB88153 is a clock generator for EMI (Electro Magnetic Interference) reduction. The peak of unnecessary (EMI) can be attenuated by making the oscillation frequency slightly modulate periodically with the internal modulator. It corresponds to both of the center spread which modulates input frequency as Middle Centered and down spread which modulates so as not to exceed input frequency.

#### **■ FEATURE**

- Power down pin : 600 μA (Max) consumption current at power down

- Input frequency: 16.6 MHz to 134 MHz

- Output frequency: 16.6 MHz to 134 MHz (One-fold input frequency)

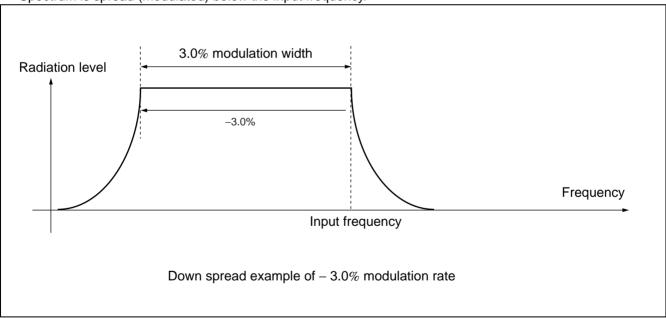

- Modulation rate can select from  $\pm 0.5\%$ ,  $\pm 1.5\%$  1.0% or 3.0%. (For center spread / down spread.)

- Modulation clock output Duty: 40% to 60%

- Modulation clock Cycle-Cycle Jitter: Less than 100 ps

- Low current consumption by CMOS process: 4.0 mA (24 MHz: Typ-sample, no load)

- Power supply voltage: 3.3 V ± 0.3 V

- Operating temperature : − 40 °C to +85 °C

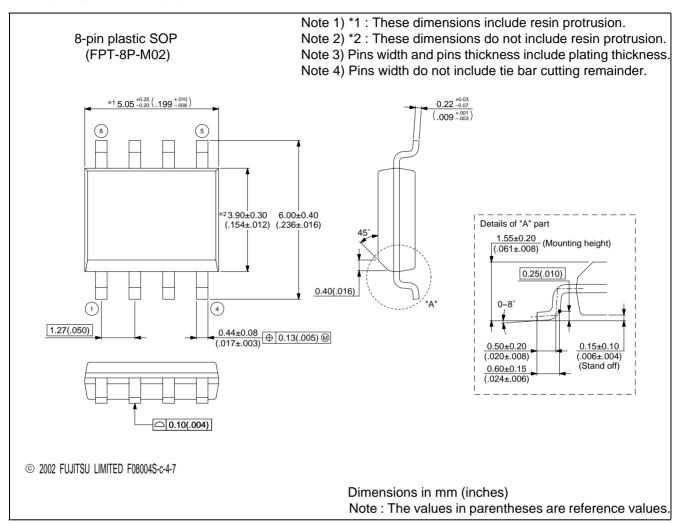

- Package : SOP 8-pin

#### **■ PACKAGE**

# **■ PRODUCT LINEUP**

MB88153 has four kinds of modulation rate and modulation type (center/down spread).

| Product     | Modulation rate | Modulation type |

|-------------|-----------------|-----------------|

| MB88153-100 | -1.0%           | Down            |

| MB88153-101 | -3.0%           | Dowii           |

| MB88153-110 | ±0.5%           | Center          |

| MB88153-111 | ±1.5%           | Center          |

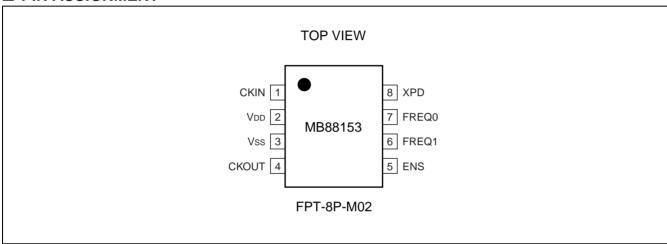

# **■ PIN ASSIGNMENT**

# **■ PIN DESCRIPTION**

| Pin name        | I/O | Pin no. | Description                                                    |

|-----------------|-----|---------|----------------------------------------------------------------|

| CKIN            | I   | 1       | Clock input pin                                                |

| V <sub>DD</sub> | _   | 2       | Power supply voltage pin                                       |

| Vss             | _   | 3       | GND pin                                                        |

| CKOUT           | 0   | 4       | Modulated clock output pin "L" output at power down            |

| ENS             | I   | 5       | Modulation enable setting pin                                  |

| FREQ1           | I   | 6       | Frequency setting pin                                          |

| FREQ0           | I   | 7       | Frequency setting pin (with pull-up resistor)                  |

| XPD             | I   | 8       | Power down pin (with pull-up resistor) Power down at "L" input |

# ■ I/O CIRCUIT TYPE

| Pin                    | Circuit type | Remarks                                                 |

|------------------------|--------------|---------------------------------------------------------|

| CKIN,<br>ENS,<br>FREQ1 |              | CMOS hysteresis input                                   |

| FREQ0,<br>XPD          | 50 kΩ        | CMOS hysteresis input with pull-up resistor 50 kΩ (typ) |

| CKOUT                  |              | CMOS output     "L" output at power down                |

#### **■ HANDLING DEVICES**

#### **Preventing Latchup**

A latchup can occur if, on this device, (a) a voltage higher than  $V_{DD}$  or a voltage lower than  $V_{SS}$  is applied to an input or output pin or (b) a voltage higher than the rating is applied between  $V_{DD}$  and  $V_{SS}$ . The latchup, if it occurs, significantly increases the power supply current and may cause thermal destruction of an element. When you use this device, be very careful not to exceed the maximum rating.

#### Handling unused pins

Do not leave an unused input pin open, since it may cause a malfunction. Handle by, using a pull-up or pull-down resistor.

Unused output pin should be opened.

#### Power supply pins

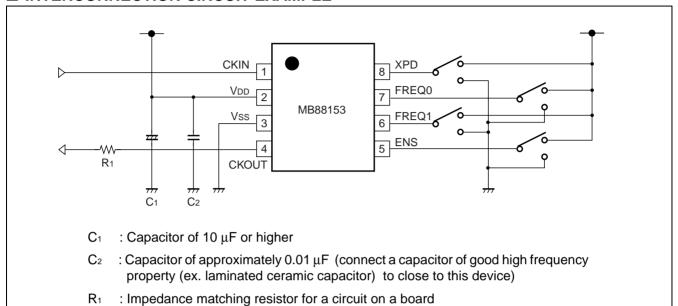

Please design connecting the power supply pin of this device by as low impedance as possible from the current supply source.

We recommend connecting electrolytic capacitor (about 10  $\mu$ F) and the ceramic capacitor (about 0.01  $\mu$ F) in parallel between Vss and VDD near the device, as a bypass capacitor.

#### Clock I/O circuit

Noise near the CKIN pin may cause the device to malfunction. Design the printed circuit board so that the wiring for the clock input does not intersect any other wiring.

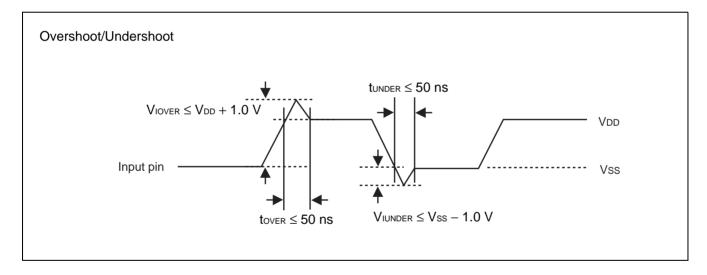

Please pay attention so that an overshoot and an undershoot do not occur to an input clock of CKIN pin.

Design the printed circuit board that surrounds the CKIN and CKOUT pins with ground.

## **■ BLOCK DIAGRAM**

#### **■ PIN SETTING**

When changing the pin setting, the stabilization wait time for the modulation clock required. The stabilization wait time for the modulation clock takes the maximum value of Lock-Up time in "■ ELECTRICAL CHARACTER-ISTICS • AC characteristics".

ENS modulation enable setting

| ENS | Modulation    |

|-----|---------------|

| L   | No modulation |

| Н   | Modulation    |

Note: Spectrum does not spread when "L" is set to ENS. The clock with low jitter can be obtained.

FREQ0, FREQ1 frequency setting

| FREQ0 | FREQ1              | Input frequency range |

|-------|--------------------|-----------------------|

| L     | L                  | 16.6 MHz to 40 MHz    |

| L     | Н                  | 66 MHz to 134 MHz     |

| Н     | H L 33 MHz to 67 N |                       |

| Н     | Н                  | 40 MHz to 80 MHz      |

Note: It is set according to the frequency of the clock input to the device. Set FREQ0 pin to "H" for the pin opened because FREQ0 pin has pull-up resistor.

XPD power down setting

| XPD Power down |                  |  |  |

|----------------|------------------|--|--|

| L              | Power down       |  |  |

| Н              | Normal operation |  |  |

Note: When "L" is set to XPD pin, the power down operation is implemented and "L" is output to CKOUT pin. When "H" is input to XPD pin or XPD pin is opened, normal operation is implemented because the XPD pin has pull-up resistor.

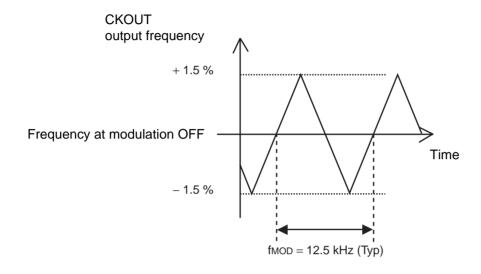

## • Center spread

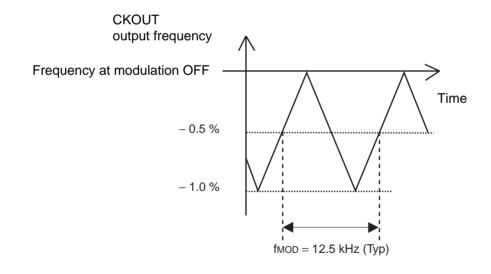

## • Down spread

# Spectrum is spread (modulated) below the input frequency.

## ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                      | Symbol          | Rating                     |                                       |      |  |

|--------------------------------|-----------------|----------------------------|---------------------------------------|------|--|

| rarameter                      | Symbol          | Min                        | Max                                   | Unit |  |

| Power supply voltage*          | V <sub>DD</sub> | - 0.5                      | + 4.0                                 | V    |  |

| Input voltage*                 | Vı              | Vss - 0.5                  | V <sub>DD</sub> + 0.5                 | V    |  |

| Output voltage*                | Vo              | Vss - 0.5                  | V <sub>DD</sub> + 0.5                 | V    |  |

| Storage temperature            | Тѕт             | <b>– 55</b>                | + 125                                 | °C   |  |

| Operation junction temperature | TJ              | - 40                       | + 125                                 | °C   |  |

| Output current                 | lo              | <b>- 14</b>                | + 14                                  | mA   |  |

| Overshoot                      | Viover          | _                          | V <sub>DD</sub> + 1.0 (tover ≤ 50 ns) | V    |  |

| Undershoot                     | Viunder         | Vss - 1.0 (tunder ≤ 50 ns) | _                                     | V    |  |

$<sup>^{*}</sup>$ : The parameter is based on  $V_{\text{SS}} = 0.0 \text{ V}$ .

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

(Vss = 0.0 V)

| Parameter               | Sym-            | Pin                                | Conditions             |                      | Unit |                       |       |

|-------------------------|-----------------|------------------------------------|------------------------|----------------------|------|-----------------------|-------|

| Parameter               | bol             | FIII                               | Conditions             | Min                  | Тур  | Max                   | Offic |

| Power supply voltage    | V <sub>DD</sub> | V <sub>DD</sub>                    | _                      | 3.0                  | 3.3  | 3.6                   | V     |

| "H" level input voltage | ViH             | CKIN, ENS,<br>FREQ0, FREQ1,<br>XPD | _                      | $V_{DD} \times 0.80$ | _    | V <sub>DD</sub> + 0.3 | V     |

| "L" level input voltage | VıL             | CKIN, ENS,<br>FREQ0, FREQ1,<br>XPD | _                      | Vss                  | _    | $V_{DD} \times 0.20$  | V     |

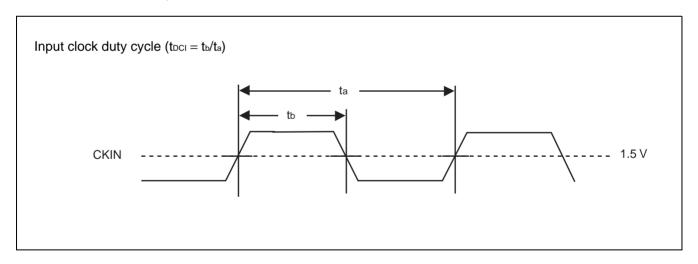

| Input clock duty cycle  | <b>t</b> DCI    | CKIN                               | 16.6 MHz to<br>134 MHz | 40                   | 50   | 60                    | %     |

| Operating temperature   | Та              | _                                  | _                      | - 40                 | _    | + 85                  | °C    |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

## **■ ELECTRICAL CHARACTERISTICS**

DC Characteristics

(Ta =

$$-40$$

°C to  $+85$  °C, V<sub>DD</sub> =  $3.3$  V  $\pm$  0.3 V, V<sub>SS</sub> =  $0.0$  V)

| Parameter                | Cymbal | Din                                      | Conditions                                                             | Value                 |     |                 | Unit |

|--------------------------|--------|------------------------------------------|------------------------------------------------------------------------|-----------------------|-----|-----------------|------|

| Parameter                | Symbol | Pin                                      | Conditions                                                             | Min                   | Тур | Max             | Unit |

| Output voltage           | Vон    | CKOUT                                    | "H" level output<br>Іон = - 4 mA                                       | V <sub>DD</sub> - 0.5 | _   | V <sub>DD</sub> | V    |

| Output voltage           | Vol    | CKOUT                                    | "L" level output<br>IoL = 4 mA                                         | Vss                   | _   | 0.4             | V    |

| Output impedance         | Zo     | CKOUT                                    | 16.6 MHz to 134 MHz                                                    | _                     | 45  | _               | Ω    |

| Input capacitance        | Cin    | CKIN,<br>ENS,<br>FREQ0,<br>FREQ1,<br>XPD | Ta = +25 °C,<br>V <sub>DD</sub> = V <sub>I</sub> = 0.0 V,<br>f = 1 MHz | _                     | _   | 16              | pF   |

|                          |        |                                          | 16.6 MHz to 67 MHz                                                     | _                     | _   | 15              |      |

| Load capacitance         | CL     | CKOUT                                    | 67 MHz to 100 MHz                                                      | _                     | _   | 10              | pF   |

|                          |        |                                          | 100 MHz to 134 MHz                                                     | _                     | _   | 7               |      |

| Input Pull-up resistance | Rpu    | FREQ0,<br>XPD                            | V <sub>IL</sub> = 0.0 V                                                | 25                    | 50  | 200             | kΩ   |

| Power supply current     | Icc    | V <sub>DD</sub>                          | No load capacitance at 24 MHz output                                   |                       | 4.0 | 6.0             | mA   |

| Power down current       | lpd    | V <sub>DD</sub>                          | Input clock stopping                                                   | _                     | _   | 600             | μΑ   |

## AC Characteristics

(Ta =

$$-40$$

°C to  $+85$  °C, V<sub>DD</sub> =  $3.3$  V  $\pm 0.3$  V, Vss =  $0.0$  V)

| Parameter               | Symbol               | Pin Conditions |                                                                                | Value |      |     | Unit |

|-------------------------|----------------------|----------------|--------------------------------------------------------------------------------|-------|------|-----|------|

| raiametei               | Symbol Pin Condition |                | Conditions                                                                     | Min   | Тур  | Max | Unit |

| Input frequency         | fin                  | CKIN           | _                                                                              | 16.6  | _    | 134 | MHz  |

| Output frequency        | fоит                 | CKOUT          | _                                                                              | 16.6  | _    | 134 | MHz  |

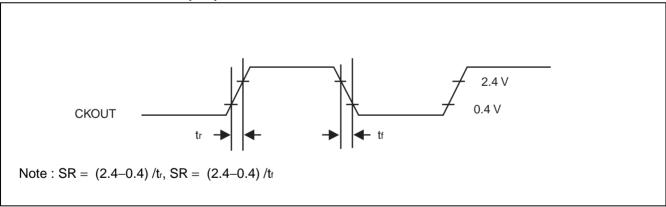

| Output slew rate        | SR                   | СКОИТ          | Load capacitance 15 pF<br>0.4 V to 2.4 V                                       | 0.4   | _    | 4.0 | V/ns |

| Output clock duty cycle | tocc                 | CKOUT          | 1.5 V                                                                          | 40    |      | 60  | %    |

| Modulation frequency    | fмор                 | CKOUT          | _                                                                              | _     | 12.5 |     | kHz  |

| Lock-up time            | <b>t</b> LK          | CKOUT          | _                                                                              | _     | 2    | 5   | ms   |

| Cycle-cycle jitter      | tuc                  | CKOUT          | No load capacitance, Ta = $+25$ °C, VDD = $3.3$ V, Standard deviation $\sigma$ | _     |      | 100 | ps   |

Note: The modulation clock stabilization wait time is required after the power is turned on, the IC recovers from power saving, or after FREQ (frequency range) or ENS (modulation ON/OFF) setting is changed. For the modulation clock stabilization wait time, assign the maximum value for lock-up time.

# ■ OUTPUT CLOCK DUTY CYCLE (tocc = tb/ta)

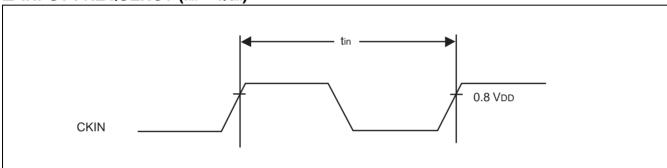

# ■ INPUT FREQUENCY (fin = 1/tin)

# ■ OUTPUT SLEW RATE (SR)

# **■ CYCLE-CYCLE JITTER**

Note: Cycle-cycle jitter is defined the difference between a certain cycle and immediately after (or, immediately before).

11

# **■ MODULATION WAVEFORM**

• ±1.5% modulation rate, Example of center spread

• −1.0% modulation rate, Example of down spread

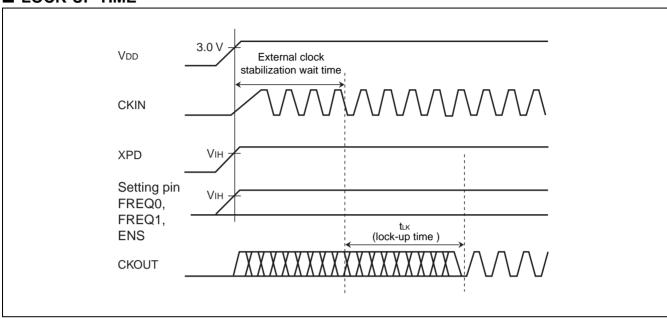

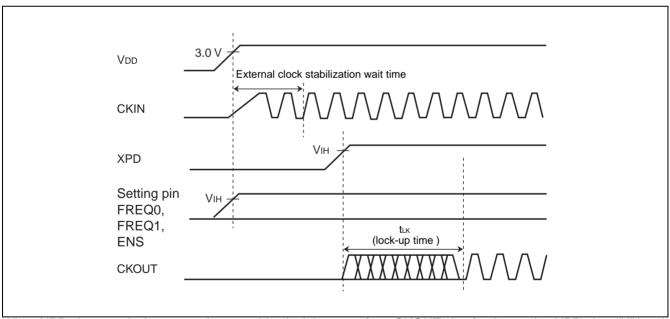

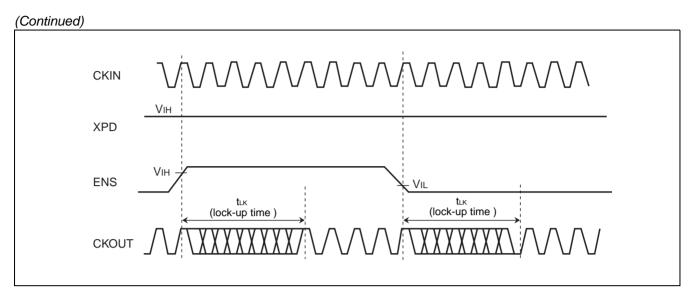

## **■ LOCK-UP TIME**

If the XPD pin is fixed at the "H" level, the maximum time after the power is turned on until the set clock signal is output from CKOUT pin is (the stabilization wait time of input clock to CKIN pin) + (the lock-up time "tuk"). For the input clock stabilization time, check the characteristics of the resonator or oscillator used.

When XPD pin controls the power-down, stable clock is output from CKOUT pin after becoming XPD pin = "H" level (in the maximum after lock-Up time ( $t_{LK}$ )).

When ENS pin is controlled for enable modulation, it is necessary for the stably clock output from CKOUT pin to wait lock-up time ( $t_{LK}$ ).

Note: In the following cases, it is necessary for the stably clock output from CKOUT pin, to wait lock-up time (tlk).

- After releasing power-down

- When you change other terminal settings

Output frequency, output clock duty cycle, modulation frequency, and cycle-cycle jitter are not guaranteed until the output clock is stable. It is recommended to take procedure to release of reset after. lock-up time (tlk) on the device using the modulation clock or etc.

# ■ INTERCONNECTION CIRCUIT EXAMPLE

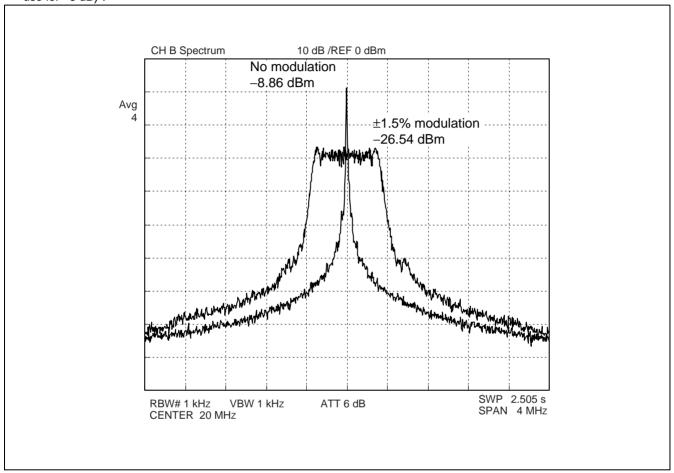

## ■ SPECTRUM EXAMPLE CHARACTERISTICS

The condition of the examples of the characteristic is shown as follows: Input frequency = 20 MHz (Output frequency = 20 MHz), use for MB88153-111.

Power-supply voltage = 3.3 V, None load capacity. Modulation rate =  $\pm 1.5\%$  (center spread).

Spectrum analyzer HP4396B is connected with CKOUT. The result of the measurement with RBW = 1 kHz (ATT use for -6 dB).

# **■** ORDERING INFORMATION

| Part number              | modulation rate | modulation type | Package           | Remarks                 |  |

|--------------------------|-----------------|-----------------|-------------------|-------------------------|--|

| MB88153PNF-G-100-JNE1    | -1.0%           | Down            |                   |                         |  |

| MB88153PNF-G-101-JNE1    | -3.0%           | Down            | 8-pin plastic SOP |                         |  |

| MB88153PNF-G-110-JNE1    | ±0.5%           | Center          | (FPT-8P-M02)      |                         |  |

| MB88153PNF-G-111-JNE1    | ±1.5%           | Center          |                   |                         |  |

| MB88153PNF-G-100-JN-EFE1 | -1.0%           | Down            |                   |                         |  |

| MB88153PNF-G-101-JN-EFE1 | -3.0%           | Down            | 8-pin plastic SOP | Emboss taping (EF type) |  |

| MB88153PNF-G-110-JN-EFE1 | ±0.5%           | Center          | (FPT-8P-M02)      |                         |  |

| MB88153PNF-G-111-JN-EFE1 | ±1.5%           | Center          |                   |                         |  |

| MB88153PNF-G-100-JN-ERE1 | -1.0%           | Down            |                   |                         |  |

| MB88153PNF-G-101-JN-ERE1 | -3.0%           | Down            | 8-pin plastic SOP | Emboss taping           |  |

| MB88153PNF-G-110-JN-ERE1 | ±0.5%           | Center          | (FPT-8P-M02)      | (ER type)               |  |

| MB88153PNF-G-111-JN-ERE1 | ±1.5%           | Center          |                   |                         |  |

## **■ PACKAGE DIMENSION**

# **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

#### F0502