# The Fujitsu H.264 Format Video-Processing IC MB86H50

#### Introduction

The Fujitsu MB86H50 is the industry's first H.264 format video-processing IC to support the H.264 High Profile, Level 4.0 standard used in next-generation DVDs. The new IC enables high-resolution recording, playback and transmission of high-definition video on audio-visual products such as portable A/V products, hard disk recorders, and home network equipment.

The H.264 format was jointly promul-gated by the ITU-T (International Telecommunication Union, Telecommunication Standardization Sector) and ISO/IEC (International

Organization for Standardization/ International Electrotechnical Commission). To achieve its superior performance, H.264 needs high computational loads to be processed at the time of compression. The High Profile, Level 4.0 version of H.264 requires very high data-processing volumes to maximize image quality, so a high-speed IC is required for real-time H.264 compression. Building on its work developing chips for MPEG formats, Fujitsu has been involved in standards-setting organizations related to H.264, in addition to product development.

#### Applications

- Mobile Digital Broadcasts

- Next-Generation DVDs for HDTV

- Web Delivery of Digital TV Broadcasts

- Mobile Video Players

- Hard Disk Recorders

- Internet Broadcasts (VoD)

- IPTV Phones

- Video Cameras

- Mobile TV Phones

# The Fujitsu H.264 Format Video-Processing IC, MB86H50

#### Features

## Real-time Compression and Decompression of HDTV Video and Sound

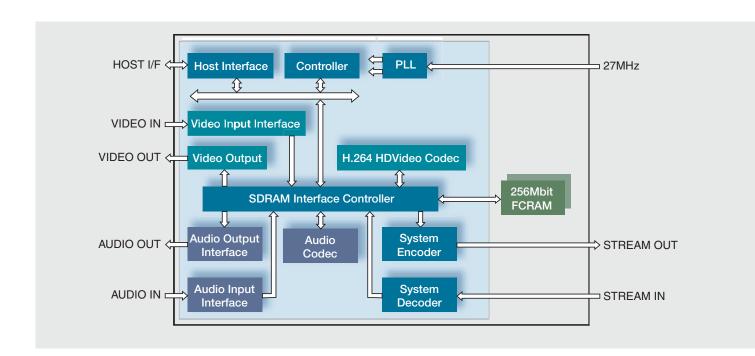

The new video-processing IC can do real-time compression and decompression of high-definition video, with a maximum of up to 1440 dots x 1080 lines. The sound is simultaneously compressed and decompressed in Dolby Digital format. This is the first time these processing features have been integrated onto a single chip for general use.

# **Embedded Memory for Smaller Size and Lower Power Consumption**

This is also the industry's first H.264-supportive LSI featuring two pieces of embedded 256Mbit FCRAM. The optimized design combines logic and memory on one LSI chip, enabling a more compact size and lower power consumption.

# **Proprietary Compression and Image-Enhancement Technology**

A proprietary "self-tuning" algorithm developed by Fujitsu Laboratories automatically applies a lighter compression method to high-action zones where compression artifacts are most noticeable (such as human faces or slow-moving objects) and stronger compression method in other zones. This enables image-data size to be reduced to one-half to one-third that of the MPEG-2 format with equivalent image quality.

| Specifi                    | cations             |                                                                                  |

|----------------------------|---------------------|----------------------------------------------------------------------------------|

| Video                      | Specifications      | H.264 High Profile / Level 4.0 Half-Duplex<br>Codec                              |

|                            | Resolution          | 1440 x 1080 x 60i/50i, 1280 x 720 x 60p/50p,<br>720 x 480 x 60i, 720 x 576 x 50i |

|                            | Bit Rate            | 20Mbps (max.)                                                                    |

|                            | Interface           | SMPTE 274M / SMPTE296M-2001,<br>ITU-R BT.656                                     |

|                            | Scaler              | Input: video input 1920 → 1440<br>Output: 1440 → video output 1920               |

| Audio                      | Format              | Dolby Digital (AC-3), linear PCM, MPEG-2<br>AAC, MPEG-1 Audio Layer2             |

|                            | Channels            | 2 channels                                                                       |

|                            | Interface           | LR serial                                                                        |

| System                     | Format              | TS CBR / VBR                                                                     |

|                            | Stream<br>Interface | 8-bit parallel or serial                                                         |

| Host Interface             |                     | General-purpose 16-bit interface                                                 |

| Input Clock                |                     | 27MHz                                                                            |

| Frequency                  |                     | 27MHz, 108MHz (memory only: 135MHz)                                              |

| Power Consumption (target) |                     | 600mW (typ., 1.2V, when encoding)                                                |

| Package                    |                     | FBGA 650pin 15mm square SiP<br>(0.5mm pitch)                                     |

| Memory                     |                     | 256Mbit FCRAM x 2                                                                |

|                            |                     |                                                                                  |

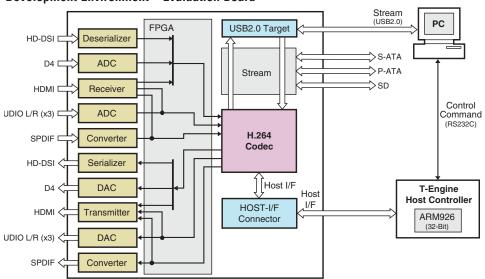

#### **Development Environment – Evaluation Board**

### FUJITSU MICROELECTRONICS AMERICA, INC.

Corporate Headquarters 1250 E. Arques Avenue, M/S 333, Sunnyvale, CA 94085-5401 Tel: (800) 866-8608 Fax: (408) 737-5999 E-mail: inquiry@fma.fujitsu.com Web Site: http://us.fujitsu.com/micro