# ASSP Dual Serial Input PLL FrequencySynthesizer MB15F03L

# ■ DESCRIPITON

The Fujitsu MB15F03L is a serial input Phase Locked Loop (PLL) frequency synthesizer with a 1800MHz and a 250MHz prescalers. A 64/65 or a 128/129 for the 1800MHz prescaler, and a 16/17 or a 32/33 for 250MHz prescaler can be selected that enables pulse swallow operation.

The latest BiCMOS process technology is used, resultantly a supply current is limited as low as 5.0mA typ. at a supply voltage of 3.0V.

Furthermore, a super charger circuit is included to provide a fast tuning as well as low noise performance. As a result of this, MB15F03L is ideally suitable for digital mobile communications, such as PHS(Personal Handy Phone System), PCN (Personal Communication Network) and PCS(Personal Communication Service).

# ■ FEATURES

- High frequency operation RF synthesizer: 1800MHz max. / IF synthesizer: 250MHz max.

- Low power supply voltage: Vcc = 2.7 to 3.6V

- Very Low power supply current : Icc = 5.0 mA typ. (Vcc = 3V)

- Power saving function : Supply current at power saving mode Typ.0.1μA (Vcc=3V), Max.10μA (IPs1=IPs2)

- Dual modulus prescaler : 1800MHz prescaler(64/65,128/129) , 250MHz prescaler(16/17,32/33)

- Serial input 14-bit programmable reference divider: R = 5 to 16,383

- Serial input 18-bit programmable divider consisting of:

- Binary 7-bit swallow counter: 0 to 127

- Binary 11-bit programmable counter: 5 to 2,047

- On-chip high performance charge pump circuit and phase comparator, achieving high-speed lock-up and low phase noise

- On-chip phase control for phase comparator

- Wide operating temperature: Ta = -40 to 85°C

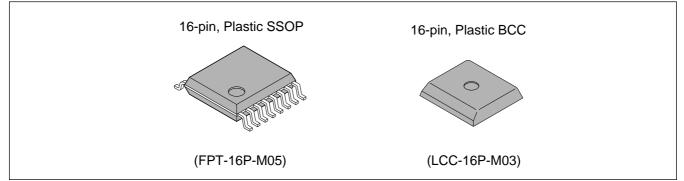

### PACKAGE

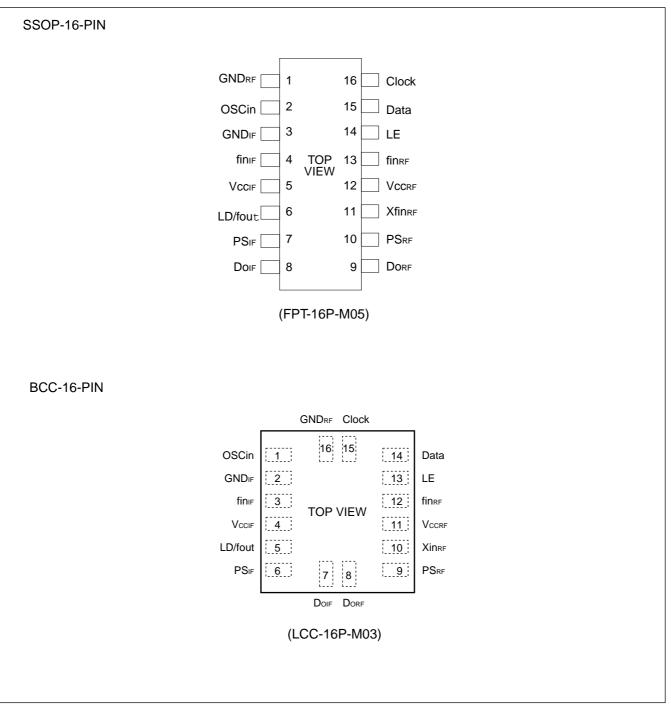

#### ■ PIN ASSIGNMENT

# ■ PIN DESCRIPTION

| Pin     | No.    | Pin     |     | Descriptions                                                                                                                                                                                                                         |

|---------|--------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP-16 | BCC-16 | name    | I/O | Descriptions                                                                                                                                                                                                                         |

| 1       | 16     | GNDrf   | _   | Ground for RF–PLL section.                                                                                                                                                                                                           |

| 2       | 1      | OSCin   | I   | The programmable reference divider input. TCXO should be connected with a AC coupling capacitor.                                                                                                                                     |

| 3       | 2      | GNDIF   | _   | Ground for the IF-PLL section.                                                                                                                                                                                                       |

| 4       | 3      | finif   | I   | Prescaler input pin for the IF-PLL.<br>The connection with VCO should be AC coupling.                                                                                                                                                |

| 5       | 4      | Vccif   | _   | Power supply voltage input pin for the IF-PLL section.                                                                                                                                                                               |

| 6       | 5      | LD/fout | 0   | Lock detect signal output (LD) / phase comparator monitoring output<br>(fout)<br>The output signal is selected by a LDS bit in a serial data.<br>LDS bit = "H" ; outputs fout signal<br>LDS bit = "L" ; outputs LD signal            |

| 7       | 6      | PSIF    | I   | Power saving mode control for the IF-PLL section. This pin must be set<br>at "L" Power-ON. (Open is prohibited.)<br>PSIF = "H"; Normal mode<br>PSIF = "L"; Power saving mode                                                         |

| 8       | 7      | Doif    | 0   | Charge pump output for the IF-PLL section.<br>Phase characteristics of the phase detector can be reversed by FC-bit.                                                                                                                 |

| 9       | 8      | Dorf    | 0   | Charge pump output for the RF-PLL section.<br>Phase characteristics of the phase detector can be reversed by FC-bit.                                                                                                                 |

| 10      | 9      | PSrf    | I   | Power saving mode control for the RF-PLL section. This pin must be set<br>at "L" Power-ON. (Open is prohibited.)<br>PSRF = "H"; Normal mode<br>PSRF = "L"; Power saving mode                                                         |

| 11      | 10     | Xfinrf  | I   | Prescaler complimentary input for the RF-PLL section.<br>This pin should be grounded via a capacitor.                                                                                                                                |

| 12      | 11     | VCCRF   | _   | Power supply voltage input pin for the RF-PLL section, the shift register<br>and the oscillator input buffer. When power is OFF, latched data of RF-<br>PLL is cancelled.                                                            |

| 13      | 12     | finrf   | I   | Prescaler input pin for the RF-PLL.<br>The connection with VCO should be AC coupling.                                                                                                                                                |

| 14      | 13     | LE      | I   | Load enable signal input (with the schmitt trigger circuit.)<br>When LE is "H", data in the shift register is transferred to the<br>corresponding<br>latch according to the control bit in a serial data.                            |

| 15      | 14     | Data    | I   | Serial data input (with the schmitt trigger circuit.)<br>A data is transferred to the corresponding latch (IF-ref counter, IF-prog.<br>counter, RF-ref. counter, RF-prog. counter) according to the control bit<br>in a serial data. |

| 16      | 15     | Clock   | I   | Clock input for the 23-bit shift register (with the schmitt trigger circuit.)<br>One bit data is shifted into the shift register on a rising edge of the clock.                                                                      |

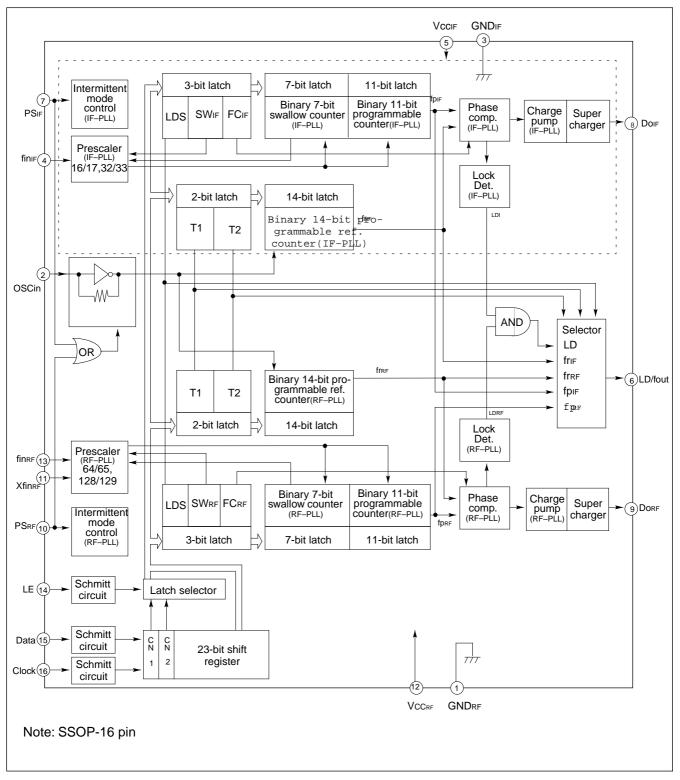

BLOCK DIAGRAM

# ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol | Rating           | Unit | Remark    |

|----------------------|--------|------------------|------|-----------|

| Power supply voltage | Vcc    | -0.5 to +4.0     | V    |           |

| Input voltage        | Vi     | -0.5 to Vcc +0.5 | V    |           |

| Output voltage       | Vo     | -0.5 to Vcc +0.5 | V    |           |

|                      | lo     | -10 to +10       | mA   | Except Do |

| Output current       | Ido    | -25 to +25       | mA   | Do output |

| Storage temperature  | Тѕтс   | -55 to +125      | °C   |           |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol |     | Value |     | Unit | Note        |

|-----------------------|--------|-----|-------|-----|------|-------------|

| Faianetei             | Symbol | Min | Тур   | Max | Unit | Note        |

| Power supply voltage  | Vcc    | 2.7 | 3.0   | 3.6 | V    | VCCIF=VCCRF |

| Input voltage         | Vi     | GND | _     | Vcc | V    |             |

| Operating temperature | Та     | -40 | _     | +85 | °C   |             |

WARNING: Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always yse semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with repect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.

#### **Handling Precautions**

- This device should be transported and stored in anti-static containers.

- This is a static-sensitive device; take proper anti-ESD precautions. Ensure that personnel and equipment are properly grounded. Cover workerbenches with grounded conductive mats.

- Always turn the power supply off before inserting or removing the device from its socket.

- Protect leads with a conductive sheet when handling or transporting PC boards with devices.

# ELECTRICAL CHARACTERISTICS

(Vcc=2.7V to 3.6V, Ta=-40°C to 85°C)

|                                  |                                |                     | 0 14                               | (*              | Value             | 3.6V, 1a=-40°0  | <b>′</b> |

|----------------------------------|--------------------------------|---------------------|------------------------------------|-----------------|-------------------|-----------------|----------|

| Paramete                         | er                             | Symbol              | Condition                          | Min.            | Тур.              | Max.            | Unit     |

| Power supply sur                 | ront                           |                     | finı⊧ = 233.15MHz,<br>fosc = 12MHz | —               | 1.5               | _               | mA       |

| Power supply cur                 | ent                            | ICCRF <sup>*2</sup> | finrr = 1800MHz,<br>fosc = 12MHz   | _               | 3.5               | _               | - MA     |

| Power saving curr                | ront                           | Ipsif               | Vccı⊧ current<br>at PSı⊧ ="L"      | _               | 0.1 <sup>*3</sup> | 10              | μA       |

| rower saving cur                 | ent                            | Ipsrf               | VccrF current<br>at PSIF/RF ="L"   | _               | 0.1 <sup>*3</sup> | 10              | μΑ       |

|                                  | finiF <sup>*4</sup>            | finı⊧               | IF-PLL                             | 50              | —                 | 250             |          |

| Operating<br>frequency           | finrf*4                        | finrf               | RF–PLL                             | 100             | —                 | 1800            | MHz      |

|                                  | OSCin                          | fosc                | _                                  | 3               | _                 | 40              |          |

|                                  | finif                          | Vfinif              | IF–PLL, 50Ω<br>termination         | -10             | _                 | +2              | dBm      |

| Input sensitivity                | finrf                          | Vfinrf              | RF–PLL, 50Ω<br>termination         | -10             | _                 | +2              | dBm      |

|                                  | OSCin                          | Vosc                | _                                  | 0.5             | _                 | Vcc             | Vp-p     |

|                                  | Data,                          | Vін                 | Schmitt trigger input              | Vccx0.7+<br>0.4 | _                 | _               | v        |

| Input voltage                    | Clock,<br>LE                   | VIL                 | Schmitt trigger input              | _               | _                 | Vccx0.3<br>-0.4 | V        |

|                                  | PSIF,                          | Vін                 | —                                  | Vccx0.7         | —                 | _               | V        |

|                                  | PSrf                           | VIL                 | —                                  | _               | _                 | Vccx0.3         |          |

|                                  | Data,                          | IIH <sup>*5</sup>   | —                                  | -1.0            |                   | +1.0            |          |

| Input current                    | Clock,<br>LE,<br>PSif,<br>PSrf | lı∟*5               | _                                  | -1.0            | _                 | +1.0            | μΑ       |

|                                  | OSCin                          | Ін                  | —                                  | 0               | _                 | +100            |          |

|                                  | OSCin                          | IIL <sup>*5</sup>   | —                                  | -100            | _                 | 0               | μA       |

|                                  |                                | Vон                 | Іон=–1.0mA                         | Vcc-0.4         | —                 | _               | V        |

| Output voltage                   | LD/fout                        | Vol                 | lo∟= 1.0mA                         | _               | _                 | 0.4             |          |

|                                  | Doif,                          | Vdoh                | Іоон =-1.0mA                       | Vcc-0.4         | —                 | _               | V        |

|                                  | DORF                           | Vdol                | Vcc=3.0V, IDOL=1.0mA               | _               | —                 | 0.4             | V        |

| High impedance<br>cutoff current | Doif,<br>Dorf                  | IOFF                | Vcc=3.0V,<br>Voff=GND to Vcc       |                 |                   | 3.0             | nA       |

(Continued)

#### (Continued)

(Vcc=2.7V to 3.6V, Ta=-40°C to 85°C)

| Paramete       | ~r      | Symbol             | Condition                            |      |      | Unit |      |

|----------------|---------|--------------------|--------------------------------------|------|------|------|------|

| Falamete       | 51      | Symbol             | Condition                            | Min. | Тур. | Max. | Unit |

|                | LD/fout | Ioн⁺⁵              | Vcc = 3.0V                           | -1.0 | —    | —    | mA   |

|                | LD/IOUI | lol                | Vcc = 3.0V                           |      |      | 1.0  |      |

| Output current | Doif,   | IDOH <sup>*5</sup> | Vcc = 3.0V, Vрон =<br>2.0V , Ta=25°С | -11  |      | -6   | mA   |

|                | Dorf    | Idol               | Vcc = 3.0V, VDOL =<br>1.0V, Ta=25°C  | 8    |      | 15   |      |

\*1: Conditions ; VCCIF = 3V, Ta =  $25^{\circ}$ C, in locking state.

\*2: Conditions ; VCCRF = 3V, Ta = 25°C, in locking state.

\*3: fosc = 12.8 MHz , Vcc = 3.0V, Ta =  $25^{\circ}C$

\*4: AC coupling with a 1000pF capacitor connected.

\*5: The symbol "-"(minus) means direction of current flow.

# FUNCTIONAL DESCRIPTIONS

The divide ratio can be calculated using the following equation:

$f_{VCO} = \{(P \times N) + A\} \times f_{OSC} \div R \quad (A < N)$

fvco: Output frequency of external voltage controlled oscillator (VCO)

P: Preset divide ratio of dual modulus prescaler (16 or 32 for IF-PLL, 64 or 128 for RF-PLL)

N: Preset divide ratio of binary 11-bit programmable counter (5 to 2,047)

A: Preset divide ratio of binary 7-bit swallow counter ( $0 \le A \le 127$ )

fosc: Reference oscillation frequency

R: Preset divide ratio of binary 14-bit programmable reference counter (5 to 16,383)

#### **Serial Data Input**

Serial data is entered using three pins, Data pin, Clock pin, and LE pin. Programmable dividers of IF/RF–PLL sections, programmable reference dividers of IF/RF PLL sections are controlled individually. Serial data of binary data is entered through Data pin.

On rising edge of clock, one bit of serial data is transferred into the shift register. When load enable signal is high, the data stored in the shift register is transferred to one of latch of them depending upon the control bit data setting.

| Con | trol bit | Destination of serial data                                      |

|-----|----------|-----------------------------------------------------------------|

| CN1 | CN2      |                                                                 |

| L   | L        | The programmable reference counter for the IF-PLL.              |

| Н   | L        | The programmable reference counter for the RF-PLL.              |

| L   | Н        | The programmable counter and the swallow counter for the IF-PLL |

| Н   | Н        | The programmable counter and the swallow counter for the RF-PLL |

#### Table1. Control Bit

### **Shift Register Configuration**

| LSE<br>↓                            | 3           | Data Flow |                         |              |                     |               |        |        |        |        |        |        |         |         |         |         |         |       |       |      |    |                      |

|-------------------------------------|-------------|-----------|-------------------------|--------------|---------------------|---------------|--------|--------|--------|--------|--------|--------|---------|---------|---------|---------|---------|-------|-------|------|----|----------------------|

| 1                                   | 2           | 3         | 4                       | 5            | 6                   | 7             | 8      | 9      | 10     | 11     | 12     | 13     | 14      | 15      | 16      | 17      | 18      | 19    | 20    | 21   | 22 | 23                   |

| C<br>N<br>1                         | C<br>N<br>2 | Т<br>1    | T<br>2                  | R<br>1       | R<br>2              | R<br>3        | R<br>4 | R<br>5 | R<br>6 | R<br>7 | R<br>8 | R<br>9 | R<br>10 | R<br>11 | R<br>12 | R<br>13 | R<br>14 | x     | x     | х    | x  | x                    |

| CN1,<br>R1 to<br>T1, 2<br>X<br>Note | ) R14       | 4         | : Div<br>: Tes<br>: Dui | t pui<br>mmy | atio<br>pos<br>bits | e bit<br>(Set | "0"    | or "1  |        | e pro  | ogra   | mma    | able    | refe    | renc    | e co    | unte    | er (5 | to 16 | 6,38 | 3) | [Tab<br>[Tab<br>[Tab |

|        | Pro    | gram                                       | mabl   | e Co     | unte            | r              |                  |                  |         |                 |                 |             |        |        |         |        |        |        |        |        |         |         |

|--------|--------|--------------------------------------------|--------|----------|-----------------|----------------|------------------|------------------|---------|-----------------|-----------------|-------------|--------|--------|---------|--------|--------|--------|--------|--------|---------|---------|

| LSB    |        | Data Flow MSB                              |        |          |                 |                |                  |                  |         |                 |                 |             |        |        |         |        |        |        |        |        |         |         |

| 1      | 2      | 3                                          | 4      | 5        | 6               | 7              | 8                | 9                | 10      | 11              | 12              | 13          | 14     | 15     | 16      | 17     | 18     | 19     | 20     | 21     | 22      | 23      |

| C<br>N | C<br>N | L<br>D                                     | S<br>W | F<br>C   | A<br>1          | A<br>2         | А<br>3           | A<br>4           | A<br>5  | A<br>6          | A<br>7          | N<br>1      | N<br>2 | N<br>3 | N<br>4  | N<br>5 | N<br>6 | N<br>7 | N<br>8 | N<br>9 | N<br>10 | N<br>11 |

| 1      | 2      | S                                          | IF/RF  | IF/RF    |                 |                |                  |                  |         |                 |                 |             |        |        |         |        |        |        |        |        |         |         |

|        |        | CN1                                        | , 2    | : C      | Contro          | ol bit         |                  |                  |         |                 |                 |             |        |        |         |        |        |        |        | [Tabl  | e. 1]   |         |

|        |        | N1 to                                      | o N11  | : C      | Divide          | ratio          | settir           | ng bits          | s for t | he pro          | ogran           | nmab        | le cou | Inter  | (5 to 2 | 2,047  | )      |        |        | [Tab   | e. 4]   |         |

|        |        | A1 to                                      | 5 A7   | : C      | Divide          | ratio          | settir           | ng bits          | s for t | he sw           | allow           | cour        | ter (0 | to 12  | 27)     |        |        |        |        | [Tab   | le. 5]  |         |

|        |        | SWIF                                       | /RF    | : C<br>( | Divide<br>16/17 | ratio<br>or 32 | settir<br>2/33 f | ng bit<br>or the | for th  | e pre<br>LL, 64 | scale<br>4/65 d | r<br>or 128 | 8/129  | for th | e RF·   | -PLL)  |        |        |        | [Tabl  | le. 6]  |         |

|        |        | FCIF/                                      | RF     | : F      | hase            | e cont         | rol bit          | for th           | ne pha  | ase d           | etecto          | or          |        |        |         |        |        |        |        | [Tab   | le. 7]  |         |

|        |        | LDS : LD/fout signal select bit [Table. 8] |        |          |                 |                |                  |                  |         |                 |                 |             |        |        |         |        |        |        |        |        |         |         |

|        |        | Note                                       | e: Da  | ata inj  | put w           | vith N         | ISB f            | irst.            |         |                 |                 |             |        |        |         |        |        |        |        |        |         |         |

### Table2. Binary 14-bit Programmable Reference Counter Data Setting

| Divide<br>ratio<br>(R) | R<br>14 | R<br>13 | R<br>12 | R<br>11 | R<br>10 | R<br>9 | R<br>8 | R<br>7 | R<br>6 | R<br>5 | R<br>4 | R<br>3 | R<br>2 | R<br>1 |

|------------------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 5                      | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 1      |

| 6                      | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 0      |

| •                      | •       | •       | •       | •       | •       | •      | •      | •      | •      | •      | •      | •      | •      | •      |

| 16383                  | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Note: • Divide ratio less than 5 is prohibited.

# Table.3 Test Purpose Bit Setting

| Т<br>1 | T<br>2 | LD/fout pin state |

|--------|--------|-------------------|

| L      | L      | Outputs friF.     |

| н      | L      | Outputs frRF.     |

| L      | Н      | Outputs fpiF.     |

| Н      | Н      | Outputs fprr.     |

| Divide<br>ratio<br>(N) | N<br>11 | N<br>10 | N<br>9 | N<br>8 | N<br>7 | N<br>6 | N<br>5 | N<br>4 | N<br>3 | N<br>2 | N<br>1 |

|------------------------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 5                      | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 1      |

| 6                      | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 0      |

| •                      | •       | •       | •      | •      | •      | •      | •      | •      | •      | •      | •      |

| 2047                   | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

#### Table.4 Binary 11-bit Programmable Counter Data Setting

Note: • Divide ratio less than 5 is prohibited.

#### Table.5 Binary 7-bit Swallow Counter Data Setting

| Divide<br>ratio<br>(A) | A<br>7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 |

|------------------------|--------|--------|--------|--------|--------|--------|--------|

| 0                      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 1                      | 0      | 0      | 0      | 0      | 0      | 0      | 1      |

| •                      | •      | •      | •      | •      | •      | •      | •      |

| 127                    | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Note: • Divide ratio (A) range = 0 to 127

#### Table. 6 Prescaler Data Setting

|                           |        | SW = "H" | SW = "L" |

|---------------------------|--------|----------|----------|

| Prescaler<br>divide ratio | IF-PLL | 16/17    | 32/33    |

|                           | RF-PLL | 64/65    | 128/129  |

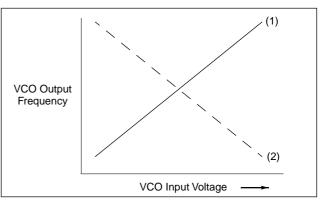

#### Table. 7 Phase Comparator Phase Switching Data Setting

|              | FCIF,RF = H | FCIF,RF = L |  |  |

|--------------|-------------|-------------|--|--|

|              | DOIF,RF     | Doif,rf     |  |  |

| fr > fp      | Н           | L           |  |  |

| fr = fp      | Z           | Z           |  |  |

| fr < fp      | L           | Н           |  |  |

| VCO polarity | (1)         | (2)         |  |  |

Note: • Z = High-impedance

• Depending upon the VCO and LPF polarity, FC bit should be set.

#### Table. 8 LD/fout Output Select Data Setting

| LDS | LD/fout output signal           |  |

|-----|---------------------------------|--|

| Н   | fout (frif/Rf, fpif/Rf) signals |  |

| L   | LD signal                       |  |

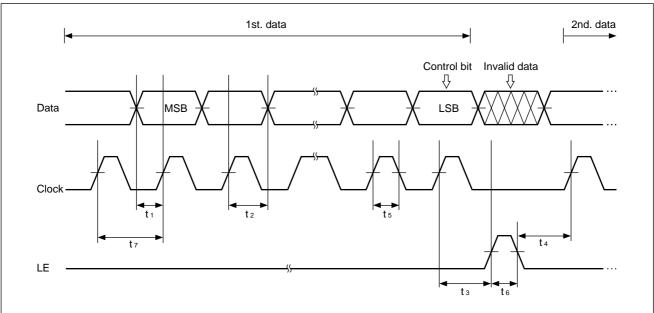

# **Serial Data Input Timing**

On rising edge of the clock, one bit of the data is transferred into the shift register.

| Parameter | Min | Тур | Max | Unit | Parameter | Min | Тур | Max | Unit |

|-----------|-----|-----|-----|------|-----------|-----|-----|-----|------|

| t1        | 20  | —   | _   | ns   | t5        | 30  | —   | -   | ns   |

| t2        | 20  | _   | -   | ns   | t6        | 100 | _   | Ι   | ns   |

| t3        | 30  | -   | _   | ns   | t7        | 100 | _   | -   | ns   |

| t4        | 20  | _   | _   | ns   |           |     |     |     |      |

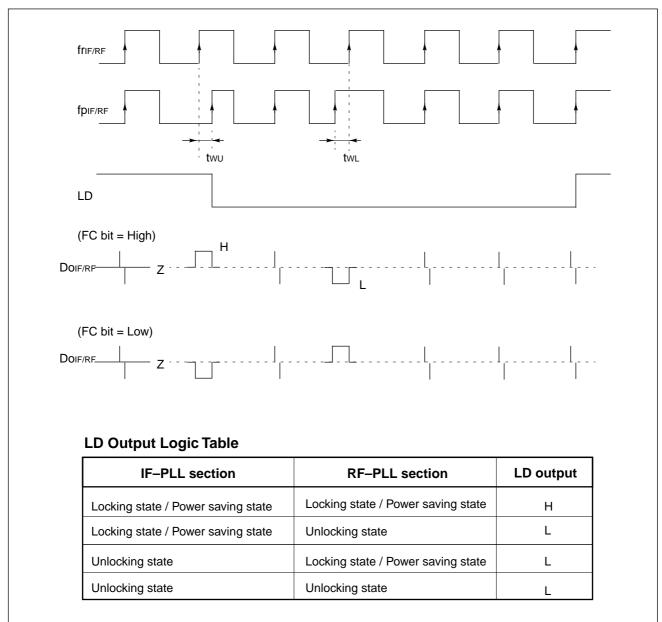

Note: •Phase error detection range =  $-2\pi$  to  $+2\pi$

•Pulses on DOIF/RF signals are output to prevent dead zone.

•LD output becomes low when phase error is two or more.

•LD output becomes high when phase error is tw∟ or less and continues to be so for three cycles or more. •tw∪ and tw∟ depend on OSCin input frequency as follows.

$twu \ge 4/fosc:$  i.e.  $twu \ge 312.5$ ns when foscin = 12.8 MHz

twL  $\leq$  8/fosc: i.e. twL  $\leq$  625.0ns when foscin = 12.8 MHz

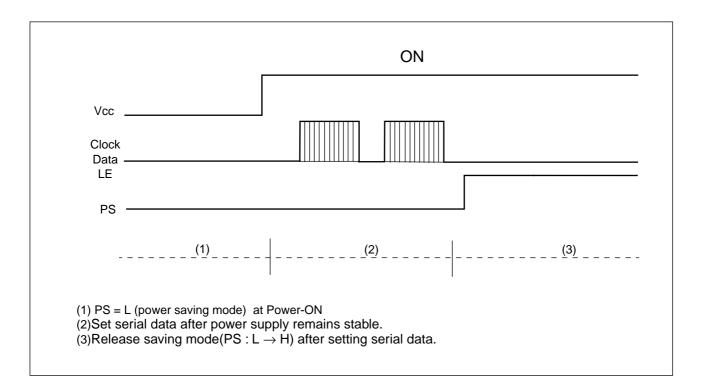

# ■ POWER SAVING MODE (INTERMITTENT MODE CONTROL CIRCUIT)

Setting a PS<sub>IF(RF)</sub> pin to Low, IF-PLL (RF-PLL) enters into power saving mode resultant current consumption can be limited to  $10\mu A$  (typ.). Setting PS pin to High, power saving mode is released so that the device works normally.

In addition, the intermittent operation control circuit is included which helps smooth start up from stand by mode. In general, the power consumption can be saved by the intermittent operation that powering down or waking up the synthesizer. Such case, if the PLL is powered up uncontrolled, the resulting phase comparator output signal is unpredictable due to an undefined phase relation between reference frequency (fr) and comparison frequency (fp) and may in the worst case take longer time for lock up of the loop.

To prevent this, the intermittent operation control circuit enforces a limited error signal output of the phase detector during power up. Thus keeping the loop locked.

PS pin must be set "L" at Power-ON.

Allow 1 µs after frequency stabilization on power-up for exiting the power saving mode (PS: L to H) Serial data can be entered during the power saving mode.

During the power saving mode, the corresponding section except for indispensable circuit for the power saving function stops working, then current consumption is reduced to  $10\mu A$  per one PLL section.

At that time, the Do and LD become the same state as when a loop is locking. That is, the Do becomes high impedance.

A VCO control voltage is naturally kept at the locking voltage which defined by a LPF's time constant. As a result of this, VCO's frequency is kept at the locking frequency.

| PSIF | PSRF | IF-PLL counters | <b>RF-PLL counters</b> | OSC input buffer |

|------|------|-----------------|------------------------|------------------|

| L    | L    | OFF             | OFF                    | OFF              |

| Н    | L    | ON              | OFF                    | ON               |

| L    | Н    | OFF             | ON                     | ON               |

| Н    | Н    | ON              | ON                     | ON               |

# ■ TYPICAL CHARACTERISITICS

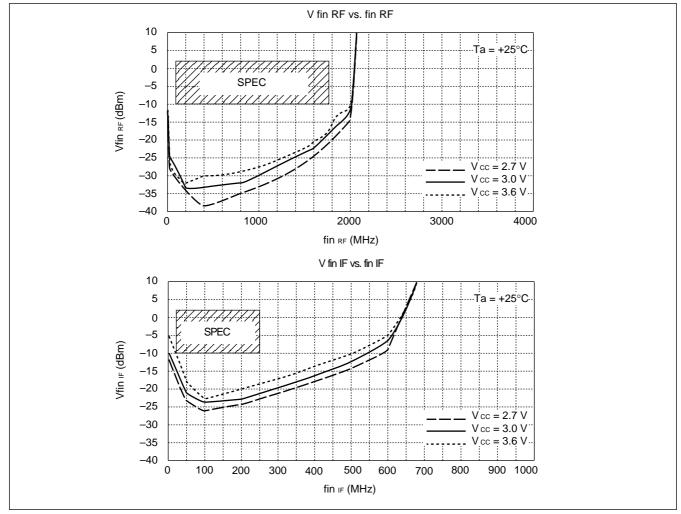

### 1. fin Input Sensitivity

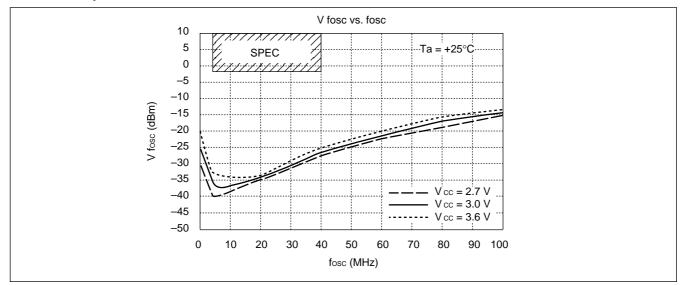

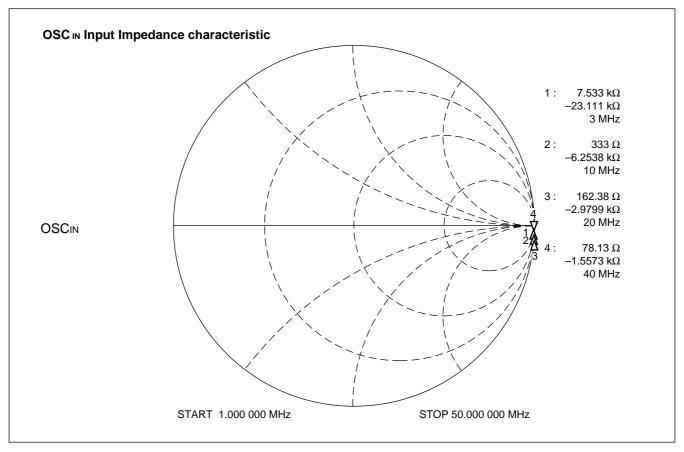

#### 2. OSCin Input Characteristics

### 3. Dorr Output Current

# **MB15F03L**

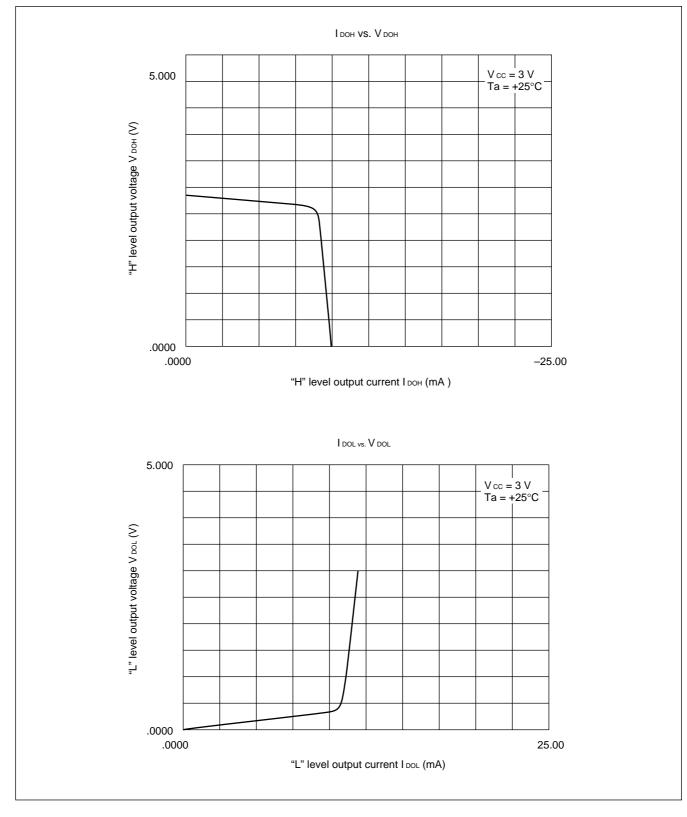

### 4. DoiF Output Current

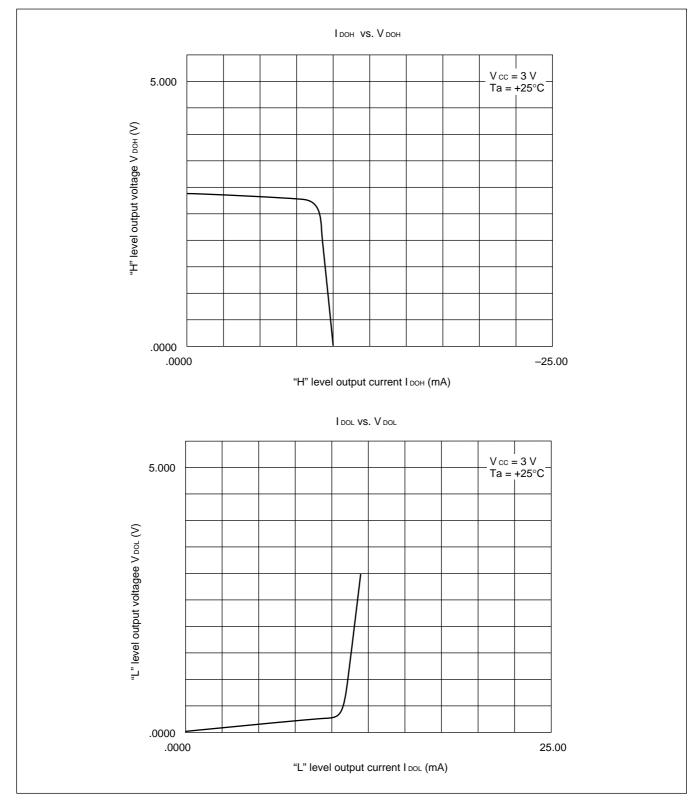

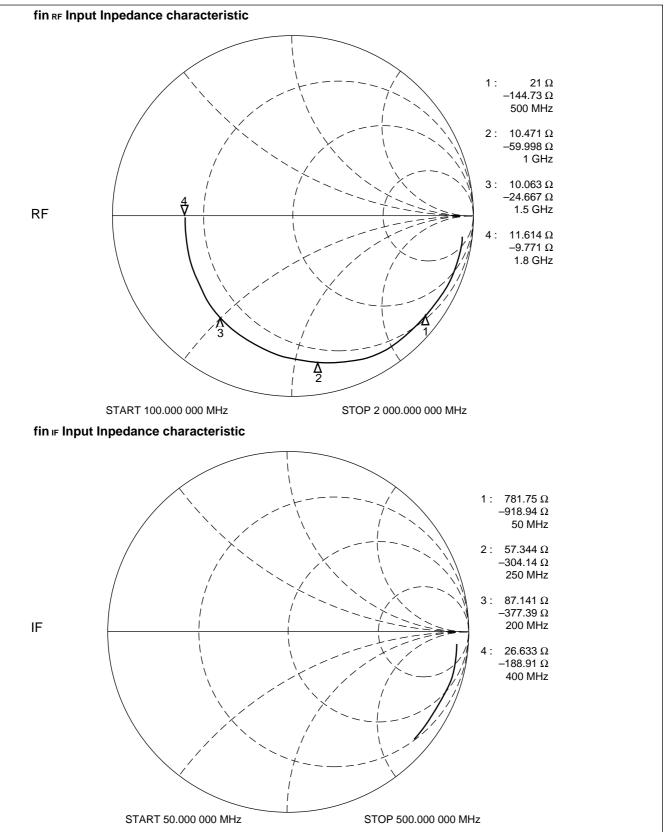

#### 5. Input Impedance.

# **MB15F03L**

#### (Continued)

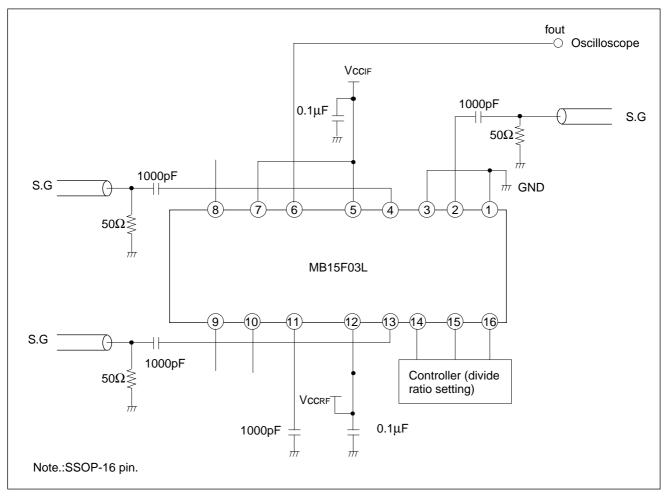

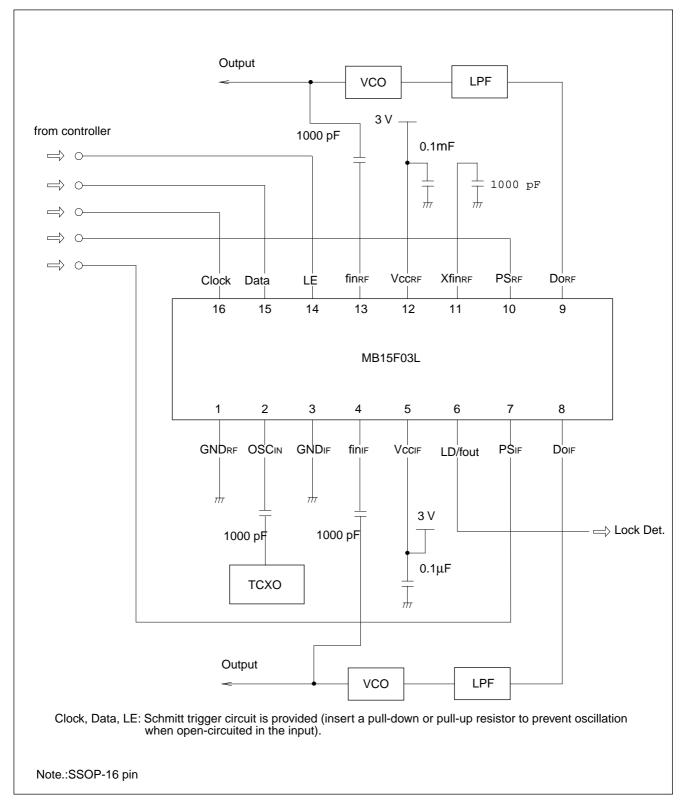

# ■ APPLICATION EXAMPLE

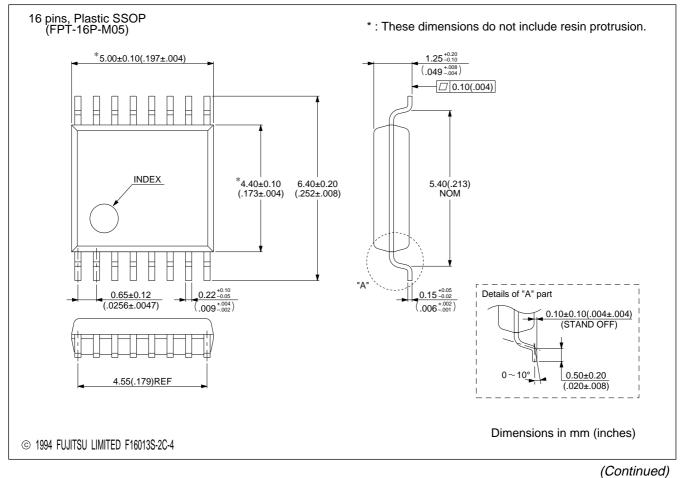

# ■ ORDERING INFORMATION

| Part number  | Package                              | Remarks |

|--------------|--------------------------------------|---------|

| MB15F03L PFV | 16pin, Plastic SSOP<br>(FPT-16P-M05) |         |

| MB15F03L PV  | 16pin, Plastic BCC<br>(LCC-16P-M03)  |         |

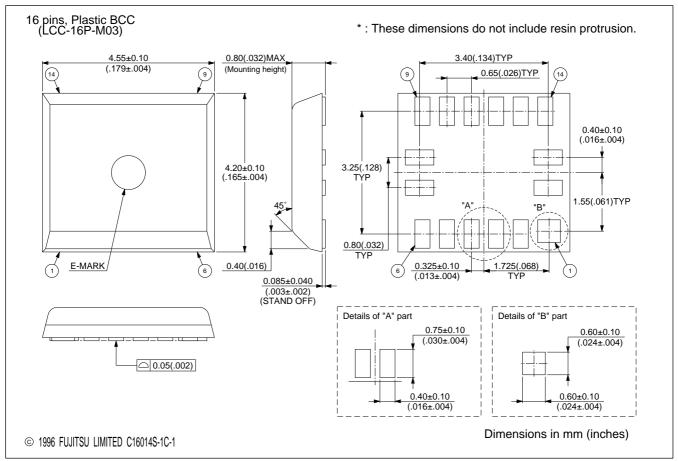

### PACKAGE DIMENSION

(Continued)

# **MB15F03L**

# FUJITSU LIMITED

For further information please contact:

#### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-88, Japan Tel: (044) 754-3753 Fax: (044) 754-3329

#### North and South America

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, U.S.A. Tel: (408) 922-9000 Fax: (408) 432-9044/9045

#### Europe

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 63303 Dreieich-Buchschlag Germany Tel: (06103) 690-0 Fax: (06103) 690-122

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LIMITED #05-08, 151 Lorong Chuan New Tech Park Singapore 556741 Tel: (65) 281 0770 Fax: (65) 281 0220 All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.