# LTC 1588/LTC 1589/LTC 1592 TECHNOLOGY 12-/14-/16-Bit SoftSpan DACs with Programmable Output Range

FEATURES

- Six Programmable Output Ranges Unipolar Mode: OV to 5V, OV to 10V Bipolar Mode: ±5V, ±10V, ±2.5V, -2.5V to 7.5V

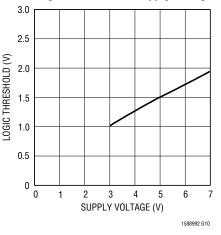

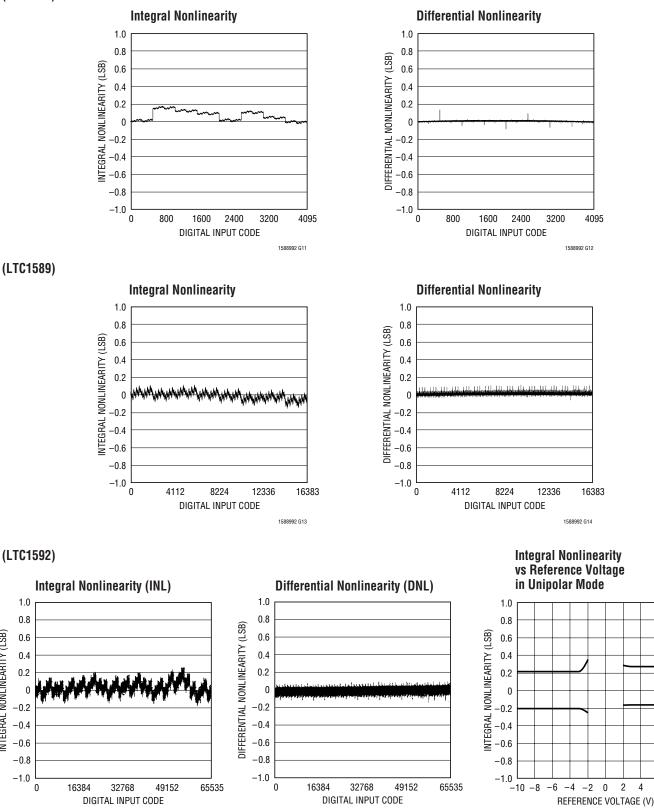

- 1LSB Max DNL and INL Over the Industrial Temperature Range

- Glitch Impulse < 2nV-s

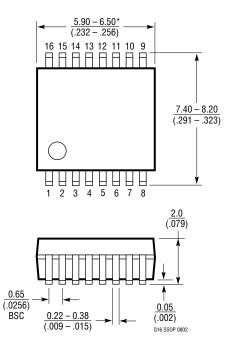

- 16-Lead SSOP Package

- Power-On Reset to 0V

- Asynchronous Clear to 0V for All Ranges

#### **APPLICATIONS**

- Process Control and Industrial Automation

- Precision Instrumentation

- Direct Digital Waveform Generation

- Software-Controlled Gain Adjustment

- Automatic Test Equipment

#### DESCRIPTION

The LTC<sup>®</sup>1588/LTC1589/LTC1592 are serial input 12-/14-/16-bit multiplying current output DACs that operates from a single 5V supply. These SoftSpan<sup>™</sup> DACs can be software-programmed for either unipolar or bipolar mode through a 3-wire SPI interface. In either mode, the voltage output range can also be software-programmed. Two output ranges in unipolar mode and four output ranges in bipolar mode are available.

INL and DNL are accurate to 1LSB over the industrial temperature range in both unipolar and bipolar modes. True 16-bit 4-quadrant multiplication is achieved with on-chip four quadrant multiplication resistors. The LTC1588/LTC1589/LTC1592 are available in a 16-lead SSOP package.

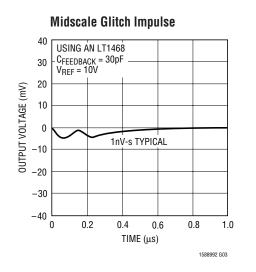

These devices include an internal deglitcher circuit that reduces the glitch impulse to less than 2nV-s (typ).

The asynchronous clear pin resets the LTC1588/LTC1589/ LTC1592 to 0V in unipolar or bipolar mode.

T, LTC and LT are registered trademarks of Linear Technology Corporation. SoftSpan is a trademark of Linear Technology Corporation.

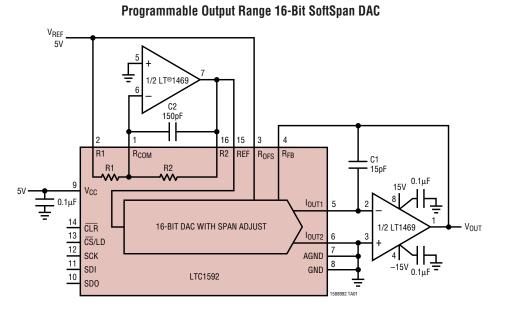

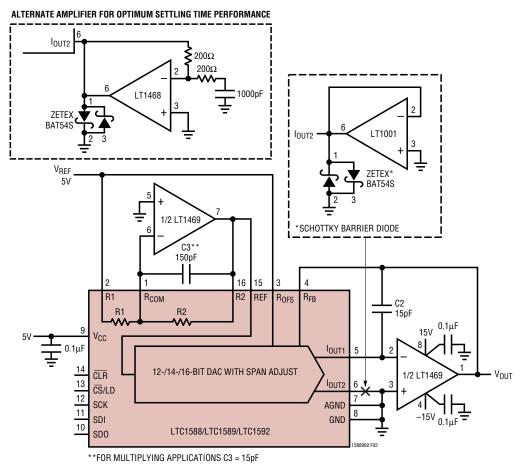

### TYPICAL APPLICATION

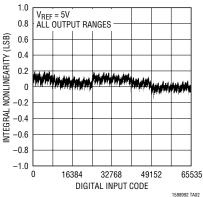

#### LTC1592 Integral Nonlinearity

1588992fa

Downloaded from Elcodis.com electronic components distributor

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>CC</sub> to AGND, GND–0.3V to 7V                              |  |

|----------------------------------------------------------------------|--|

| AGND to GND $-0.3V$ to (V <sub>CC</sub> + 0.3V)                      |  |

| GND to AGND $-0.3V$ to $(V_{CC} + 0.3V)$                             |  |

| R <sub>COM</sub> to AGND, GND0.3V to 12V                             |  |

| REF to AGND, GND±15V                                                 |  |

| R <sub>OFS</sub> , R <sub>FB</sub> , R1, R2 to AGND, GND±15V         |  |

| Digital Inputs to AGND, GND $-0.3V$ to (V <sub>CC</sub> + 0.3V)      |  |

| $I_{OUT1}$ , $I_{OUT2}$ to AGND, GND0.3V to (V <sub>CC</sub> + 0.3V) |  |

| Maximum Junction Temperature 150°C                                   |  |

| Operating Temperature Range                                          |  |

| LTC1588C/LTC1589C/LTC1592C 0°C to 70°C                               |  |

| LTC1588I/LTC1589I/LTC1592I –40°C to 85°C                             |  |

| Storage Temperature Range –65°C to 150°C                             |  |

| Lead Temperature (Soldering, 10 sec)                                 |  |

|                                                                      |  |

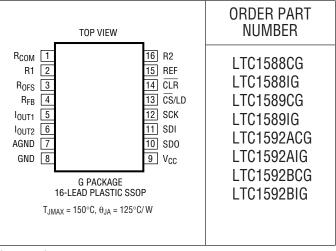

### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>CC</sub> = 5V, V<sub>REF</sub> = 5V, I<sub>OUT2</sub> = AGND = GND = 0V.

| SYMBOL           | PARAMETER                            | CONDITIONS                                   | TEMPERATURE                                                   |   | LTC1588<br>Min typ Max | LTC1589<br>Min typ max | LTC1592B<br>Min typ Max | LTC1592A<br>Min typ Max | UNITS      |

|------------------|--------------------------------------|----------------------------------------------|---------------------------------------------------------------|---|------------------------|------------------------|-------------------------|-------------------------|------------|

| Accuracy         |                                      |                                              |                                                               |   |                        |                        |                         |                         |            |

|                  | Resolution                           |                                              |                                                               | • | 12                     | 14                     | 16                      | 16                      | Bits       |

| INL              | Integral<br>Nonlinearity             | (Notes 2, 3)                                 | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • | ±1<br>±1               | ±1<br>±1               | ±2<br>±2                | ±0.3 ±1<br>±0.4 ±1      | LSB<br>LSB |

| DNL              | Differential<br>Nonlinearity         | Guaranteed<br>Monotonic (Note 3)             | T <sub>MIN</sub> to T <sub>MAX</sub>                          | • | ±1                     | ±1                     | ±1                      | ±0.2 ±1                 | LSB        |

| GE               | Gain Error                           | All Output Ranges<br>(Note 3)                | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • | -0.20 ±3<br>-0.22 ±3   | -1.0 ±4<br>-1.3 ±6     | -3 ±16<br>-4 ±24        | -2 ±16<br>-3 ±16        | LSB<br>LSB |

| BZE              | Bipolar Zero Error                   | All Bipolar Ranges<br>(Note 3)               | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • | ±1<br>±1               | ±2.5<br>±4.0           | ±10<br>±16              | ±5<br>±8                | LSB<br>LSB |

|                  | Gain Temperature<br>Coefficient      | $\Delta$ Gain/ $\Delta$ Temperature (Note 4) |                                                               | • | 3                      | 3                      | 3                       | 1 3                     | ppm/°C     |

| I <sub>LKG</sub> | I <sub>OUT1</sub> Leakage<br>Current | (Note 5)                                     | T <sub>A</sub> = 25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub> | • | ±5<br>±15              | ±5<br>±15              | ±5<br>±15               | ±5<br>±15               | nA<br>nA   |

| PSRR             | Power Supply<br>Rejection            | $V_{CC} = 5V \pm 10\%$                       |                                                               | • | ±0.01±0.15             | ±0.05±0.5              | ±2                      | ±0.2 ±2                 | LSB/V      |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are $T_A = T_{MIN}$ to $T_{MAX}$ , $V_{CC} = 5V$ , $V_{REF} = 5V$ , $I_{OUT2} = AGND = GND = OV$ .

| SYMBOL           | PARAMETER                               | CONDITIONS                                                |   | MIN           | ТҮР           | MAX            | UNITS             |

|------------------|-----------------------------------------|-----------------------------------------------------------|---|---------------|---------------|----------------|-------------------|

| Referenc         | e Input                                 |                                                           |   |               |               |                |                   |

| R <sub>REF</sub> | DAC Input Resistance (Unipolar)         | (Note 6)                                                  |   | 5             | 7             | 10             | kΩ                |

| R1, R2           | R1, R2 Resistance                       | (Notes 6, 11)                                             |   | 10            | 14            | 20             | kΩ                |

| R <sub>OFS</sub> | Offset Resistance (Bipolar)             | ±5V, ±10V, ±2.5V Ranges<br>-2.5V to 7.5V Range            | • | 10<br>20      | 14<br>28      | 20<br>40       | kΩ<br>kΩ          |

| R <sub>FB</sub>  | Feedback Resistance (Unipolar)          | 5V Range<br>10V Range                                     | • | 5<br>10       | 7<br>14       | 10<br>20       | kΩ<br>kΩ          |

|                  | Feedback Resistance (Bipolar)           | ±5V and -2.5V to 7.5V Ranges<br>±10V Range<br>±2.5V Range | • | 10<br>20<br>5 | 14<br>28<br>7 | 20<br>40<br>10 | kΩ<br>kΩ<br>kΩ    |

| Analog O         | Dutputs (Note 4)                        |                                                           |   |               |               |                |                   |

| C <sub>OUT</sub> | Output Capacitance (I <sub>OUT1</sub> ) | DAC Load All 1s<br>DAC Load All 0s                        |   |               | 160<br>100    |                | pF<br>pF          |

| AC Perfo         | rmance (Note 4)                         |                                                           |   |               |               |                |                   |

|                  | Settling Time                           | 5V Range, 0V to 5V Step with LT1468 (Note 7)              |   |               | 2             |                | μs                |

|                  | Midscale Glitch Impulse                 | (Note 10)                                                 |   |               | 2             |                | nV-s              |

|                  | Multiplying Feedthrough Error           | $V_{REF} = \pm 10V$ , 10kHz Sine Wave                     |   |               | 1             |                | mV <sub>P-P</sub> |

| THD              | Total Harmonic Distortion               | (Note 8) Multiplying                                      |   |               | -108          |                | dB                |

|                  | Output Noise Voltage Density            | (Note 9) At I <sub>OUT1</sub>                             |   |               | 11            |                | nV/√Hz            |

| Digital In       | iputs                                   | ,                                                         |   |               |               |                |                   |

| V <sub>IH</sub>  | Digital Input High Voltage              |                                                           |   | 2.4           |               |                | V                 |

| V <sub>IL</sub>  | Digital Input Low Voltage               |                                                           |   |               |               | 0.8            | V                 |

| I <sub>IN</sub>  | Digital Input Current                   |                                                           |   |               |               | ±1             | μA                |

| CIN              | Digital Input Capacitance               | $V_{IN} = 0V$ (Note 4)                                    |   |               |               | 8              | pF                |

| Digital O        | utputs                                  |                                                           |   |               |               |                |                   |

| V <sub>OH</sub>  | Digital Output High Voltage             | I <sub>0H</sub> = 200μA                                   |   | 4             |               |                | V                 |

| V <sub>OL</sub>  | Digital Output Low Voltage              | I <sub>0L</sub> = 1.6mA                                   |   |               |               | 0.4            | V                 |

| Timing C         | haracteristics                          |                                                           |   |               |               |                |                   |

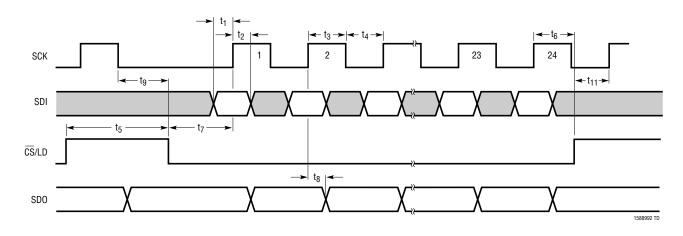

| t <sub>1</sub>   | Serial Input Valid to SCK Setup Time    |                                                           |   | 60            |               |                | ns                |

| t <sub>2</sub>   | Serial Input Valid to SCK Hold Time     |                                                           |   | 0             |               |                | ns                |

| t <sub>3</sub>   | SCK Pulse Width High                    |                                                           |   | 35            |               |                | ns                |

| t <sub>4</sub>   | SCK Pulse Width Low                     |                                                           |   | 35            |               |                | ns                |

| t <sub>5</sub>   | CS/LD Pulse High Width                  |                                                           |   | 360           |               |                | ns                |

| t <sub>6</sub>   | LSB SCK High to CS/LD High              |                                                           |   | 35            |               |                | ns                |

| t <sub>7</sub>   | CS/LD Low to SCK High                   |                                                           |   | 0             |               |                | ns                |

| t <sub>8</sub>   | SCK to SDO Propagation Delay            | C <sub>LOAD</sub> = 50pF                                  |   | 20            |               | 180            | ns                |

| tg               | SCK Low to CS/LD Low                    |                                                           |   | 35            |               |                | ns                |

| t <sub>10</sub>  | Clear Pulse Low Width                   |                                                           |   | 100           |               |                | ns                |

| t <sub>11</sub>  | CS/LD High to SCK Positive Edge         |                                                           |   | 35            |               |                | ns                |

|                  | SCK Frequency                           | Non-Daisy Chain (Note 12)<br>Daisy Chain (Note 13)        | • |               |               | 14.2<br>4.1    | MHz<br>MHz        |

#### **ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating

temperature range, otherwise specifications are  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = 5V$ ,  $V_{REF} = 5V$ ,  $I_{OUT2} = AGND = GND = 0V$ .

| SYMBOL          | PARAMETER                       | CONDITIONS                             |   | MIN | ТҮР | MAX | UNITS |  |  |

|-----------------|---------------------------------|----------------------------------------|---|-----|-----|-----|-------|--|--|

| Power Supply    |                                 |                                        |   |     |     |     |       |  |  |

| V <sub>CC</sub> | Supply Voltage                  |                                        |   | 4.5 | 5   | 5.5 | V     |  |  |

| I <sub>CC</sub> | Supply Current, V <sub>CC</sub> | Digital Inputs = 0V or V <sub>CC</sub> | • |     |     | 10  | μA    |  |  |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2:  $\pm 1LSB = \pm 0.0015\%$  of full scale =  $\pm 15.3ppm$  of full scale (LTC1592).  $\pm 1LSB = \pm 0.006\%$  of full scale =  $\pm 61.2ppm$  of full scale (LTC1589).  $\pm 1LSB = 0.024\%$  of full scale =  $\pm 244.8ppm$  of full scale (LTC1588).

Note 3: Using internal feedback resistor.

Note 4: Guaranteed by design, not subject to test.

**Note 5:** I<sub>OUT1</sub> with DAC register loaded to all 0s.

Note 6: Typical temperature coefficient is 100ppm/°C.

**Note 7:** To 0.0015% for a full-scale change, measured from the falling edge of LD for the LTC1592 only.

Note 8:  $REF = 6V_{RMS}$  at 1kHz. DAC register loaded with all 1s. Output amplifier = LT1468.

**Note 9:** Calculation from  $e_n = \sqrt{4kTRB}$  where:  $k = Boltzmann constant (1.38E-23 J/°K); R = resistance (<math>\Omega$ ); T = temperature (°K); B = bandwidth (Hz).

**Note 10:** Midscale transition code: 32767 to 32768 for the LTC1592, 8191 to 8192 for the LTC1589, 2047 to 2048 for the LTC1588.

**Note 11:** R1 and R2 are measured between R1 and R<sub>COM</sub>, R2 and R<sub>COM</sub>. **Note 12:** If a continuous clock is used with data changing on the rising edge of SCK, setup and hold time ( $t_1$ ,  $t_2$ ) will limit the maximum clock frequency. If data changes on the falling edge of SCK then the setup time will limit the maximum clock frequency to 8MHz (continuous 50% duty cycle clock).

**Note 13:** SDO propagation delay and SDI setup time  $(t_8, t_1)$  limit the maximum clock frequency for daisy chaining.

#### TYPICAL PERFORMANCE CHARACTERISTICS (LTC1588/LTC1589/LTC1592)

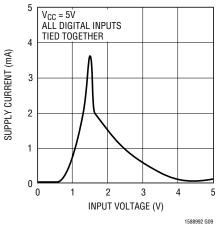

#### Supply Current vs Input Voltage

#### Logic Threshold vs Supply Voltage

#### TYPICAL PERFORMANCE CHARACTERISTICS

(LTC1588)

6 8 10

2 4

1588992 G02

LINEAR

1.0

0.8

0.6

0.4

0.2

-0.2

-0.4

-0.6

-0.8

-1.0

С

NTEGRAL NONLINEARITY (LSB)

1588992 G01

### TYPICAL PERFORMANCE CHARACTERISTICS (LTC1592)

### PIN FUNCTIONS

$R_{COM}$  (Pin 1): Center Tap Point of the Two Bipolar Resistors R1 and R2. Normally tied to the inverting input of an external amplifier. When these resistors are not used, connect this pin to ground. The absolute maximum voltage range on this pin is -0.3V to 12V.

**R1 (Pin 2):** Bipolar Resistor R1. The main reference input  $V_{REF}$ , typically 5V. Accepts up to ±15V. Normally tied to  $R_{OFS}$  (Pin 3) and the reference input voltage  $V_{REF}$  (5V). When not used connect this pin to ground.

$R_{0FS}$  (Pin 3): Bipolar Offset Network. This pin provides the offset of the output voltage range for bipolar modes. Accepts up to  $\pm 15V$ . Normally tied to R1 and the reference input voltage  $V_{REF}$  (5V). Alternatively, this pin may be driven from a different voltage than  $V_{REF}$ .

$R_{FB}$  (Pin 4): Feedback Network. Normally tied to the output of the current to voltage converter op amp. Range limited to  $\pm 15$ V.

### PIN FUNCTIONS

**I**<sub>OUT1</sub> (**Pin 5**): True DAC Current Output. Tied to the inverting input of the current-to-voltage op amp.

**I**<sub>OUT2</sub> (**Pin 6**): Complement of DAC Current Output. Normally tied to AGND pin.

**AGND (Pin 7):** Analog Ground. Tie to the system's analog ground plane.

**GND (Pin 8):** Ground. Tie to the system's analog ground plane.

$V_{CC}$  (Pin 9): Positive Supply Input. 4.5V  $\leq V_{CC} \geq$  5.5V. Requires a 0.1µF bypass capacitor to ground.

**SDO (Pin 10):** Serial Data Output. Data at this pin is shifted out on the rising edge of SCK.

SDI (Pin 11): Serial Data Input.

**SCK (Pin 12):** Serial Interface Clock. Data on the SDI pin is shifted into the input shift register on rising edge of SCK.

**CS/LD (Pin 13):** Chip Select Input. When  $\overline{CS}/LD$  is low, SCK is enabled for shifting data into the input shift register. When  $\overline{CS}/LD$  is pulled high, SCK is disabled and the control logic executes the control word (the first 4 bits of the input data stream as shown in Table 1).

**CLR (Pin 14):** When CLR is taken to a logic low, it sets the DAC output to OV and all internal registers to zero code.

**REF (Pin 15):** DAC Reference Input. Typically 5V, accepts up to  $\pm 15V$ .

**R2 (Pin 16):** Bipolar Resistor R2. Normally tied to the DAC reference input REF (Pin 15) and the output of the inverting amplifier tied to  $R_{COM}$  (Pin 1).

### FUNCTION TABLE

#### Table 1

|    |         |    |    |                                                            | h                                | nternal Regi  | ster Status           |               |

|----|---------|----|----|------------------------------------------------------------|----------------------------------|---------------|-----------------------|---------------|

|    | COMMAND |    |    | OPERATION<br>EACH COMMAND IS EXECUTED                      | SREG<br>DATA WORD<br>Dn IN INPUT | BUF1<br>INPUT | BUF2<br>DAC<br>BUFFER | DAC<br>Output |

| C3 | C2      | C1 | CO | ON THE RISING EDGE OF CS/LD                                | SHIFT REGISTER                   | BUFFER        | (DAC OUTPUT)          |               |

| 0  | 0       | 0  | 0  | Copy Data Word Dn in SReg to Buf1                          | Dn ——                            | → Dn          | No Change             | No Change     |

| 0  | 0       | 0  | 1  | Copy the Data in Buf1 to Buf2                              | Х                                | Dn —          | —→ Dn                 | No Change     |

| 0  | 0       | 1  | 0  | Copy Data Word Dn in SReg to Buf1 and Buf2                 | Dn —                             | → Dn          | → Dn                  | No Change     |

| 0  | 0       | 1  | 1  | Reserved (Do Not Use)                                      |                                  |               |                       |               |

| 0  | 1       | 0  | 0  | Reserved (Do Not Use)                                      |                                  |               |                       |               |

| 0  | 1       | 0  | 1  | Reserved (Do Not Use)                                      |                                  |               |                       |               |

| 0  | 1       | 1  | 0  | Reserved (Do Not Use)                                      |                                  |               |                       |               |

| 0  | 1       | 1  | 1  | Reserved (Do Not Use)                                      |                                  |               |                       |               |

| 1  | 0       | 0  | 0  | Set Range to 5V. Copy Dn in SReg to Buf1 and Buf2          | Dn                               | → Dn          | _ <b>→</b> Dn         | 5V            |

| 1  | 0       | 0  | 1  | Set Range to 10V. Copy Dn in SReg to Buf1 and Buf2         | Dn —                             | —► Dn         | _ <b>→</b> Dn         | 10V           |

| 1  | 0       | 1  | 0  | Set Range to $\pm$ 5V. Copy Dn in SReg to Buf1 and Buf2    | Dn —                             | → Dn          | _ <b>→</b> Dn         | ±5V           |

| 1  | 0       | 1  | 1  | Set Range to $\pm 10$ V. Copy Dn in SReg to Buf1 and Buf2  | Dn —                             | —► Dn         | └→ Dn                 | ±10V          |

| 1  | 1       | 0  | 0  | Set Range to $\pm 2.5$ V. Copy Dn in SReg to Buf1 and Buf2 | Dn —                             | <b>→</b> Dn   | _→ Dn                 | ±2.5V         |

| 1  | 1       | 0  | 1  | Set Range to –2.5V to 7V. Copy Dn in SReg to Buf1 and Buf2 | Dn —                             | → Dn          | └ <del>→</del> Dn     | -2.5V to 7.5V |

| 1  | 1       | 1  | 0  | Reserved (Do Not Use)                                      |                                  |               |                       |               |

| 1  | 1       | 1  | 1  | No Operation                                               | Х                                | No Change     | No Change             | No Change     |

Data Word Dn (n = 0 to 15) is the last 16 bits shifted into the input shift register SReg that corresponds to the DAC code.

### LTC1588/LTC1589/LTC1592

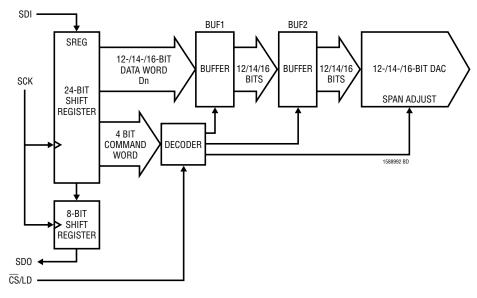

### **BLOCK DIAGRAM**

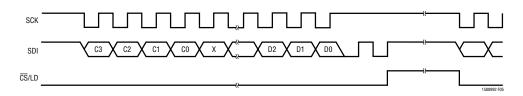

### TIMING DIAGRAM

### OPERATION

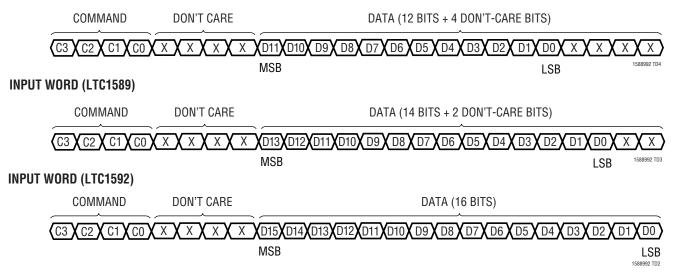

#### **INPUT WORD (LTC1588)**

#### Serial Interface

When the  $\overline{CS}/LD$  is brought to a logic low, the data on the SDI input is loaded into the shift register on the rising edge of the clock. A 4-bit command word (C3 C2 C1 C0), followed by four "don't care" bits and 16 data bits (MSB-first) is the minimum loading sequence required for the LTC1588/LTC1589/LTC1592. When the  $\overline{CS}/LD$  is brought to a logic high, the clock is disabled internally and the command word is executed.

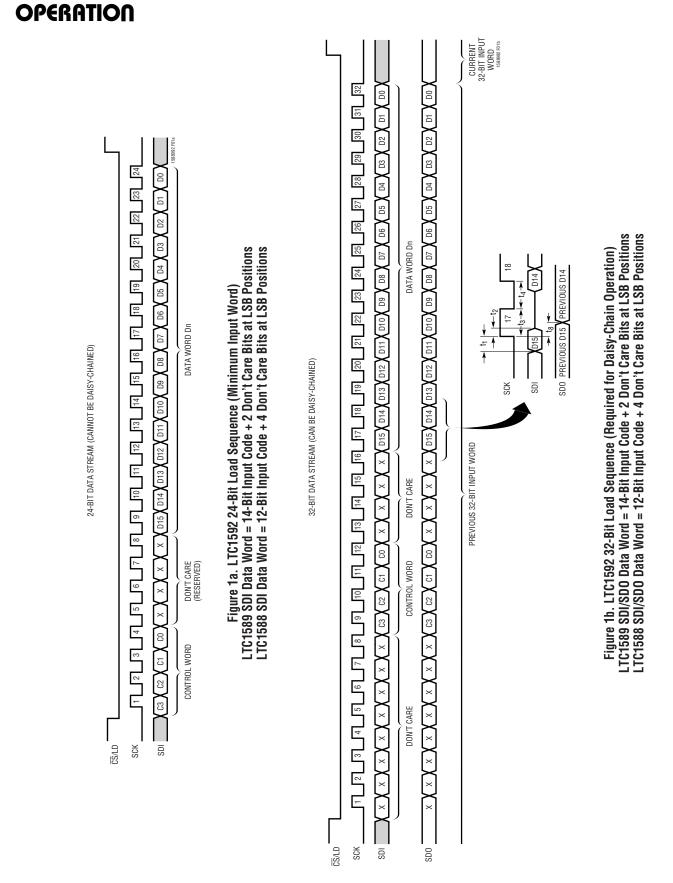

If no daisy-chaining is required, the input stream can be 24-bit wide as shown in Figure 1a. The first four bits are the command word, followed by four "don't care" bits, then a 16-bit data word. The last four bits (LSBs) of this 16-bit data word are don't cares for the LTC1588. For the LTC1589, the last 2 bits of the 16-bit data word are don't cares.

If daisy-chaining is required or the input needs to be written in two 16-bit wide segments, then the input stream must be 32-bit wide and the first 8 bits loaded are "don't care" bits. The remaining bits work the same as a 24-bit stream which is described in the previous paragraph. The output of the internal 32-bit shift register is available on the SDO pin 32 clock cycles later.

Multiple LTC1588/LTC1589/LTC1592s may be daisychained together by connecting the SDO pin to the SDI pin of the next IC. The clock and  $\overline{CS}/LD$  signals should remain common to all ICs in the daisy-chain. The serial data is clocked to all ICs, then the  $\overline{CS}/LD$  signal is pulled high to update all of them simultaneously.

#### **Power-On Reset and Clear**

When the power supply is first turned on, the LTC1588/ LTC1589/LTC1592 will power up in 5V unipolar mode (C3 C2 C1 C0 = 1000). All the internal registers are set to zeros and the DAC is set to zero code.

The LTC1588/LTC1589/LTC1592 must first be programmed in either unipolar or bipolar mode. There are six operating modes available and can be software-programmed by the command word. When a CLR signal is brought to low, it clears all internal registers to zero. The DAC output voltage goes to zero volts. If an update DAC command (C3 C2 C1 C0 = 0001) is issued immediately after the CLR signal, the DAC output remains at zero volts.

If a  $\overline{\text{CLR}}$  signal is given within a 100ns interval immediately after  $\overline{\text{CS}}/\text{LD}$  goes high, the user should reload the output range.

#### **Output Range Programming**

There are two output ranges available in unipolar mode and four output ranges available in bipolar mode. See Function Table for details. All output ranges are with respect to a 5V reference input. When changing the LTC1588/ LTC1589/LTC1592 to a new mode, the command word and data are given at the same time (24 or 32 bit). When

Downloaded from Elcodis.com electronic components distributor

## OPERATION

$\overline{\text{CS}}$ /LD goes high, the mode changes and the DAC output goes to a value corresponding to the data code.

Examples using the LTC1592:

- 1. Using a 24-bit loading sequence, load the unipolar range of 0V to 10V with the DAC output at zero volt:

- a) CS/LD ₹

- b) Clock SDI = 1001 XXXX 0000 0000 0000 0000

- c)  $\overline{\text{CS}}/\text{LD} \ \ \vec{F}$ ; then V<sub>OUT</sub> = 0V

- Using a 24-bit loading sequence, load the bipolar range of ±5V and the DAC output at zero volt:

- a) CS/LD ₹

- b) Clock SDI = 1010 XXXX 1000 0000 0000 0000

- c)  $\overline{\text{CS}}/\text{LD}$  ; then  $V_{\text{OUT}} = 0V$  on the ±5V range

3. Using a 32-bit load sequence, load the bipolar range of  $\pm 10V$  with the DAC output voltage at 5V initially. Then change the DAC output to -5V:

a) CS/LD ₹

- b) Clock SDI = XXXX XXXX 1011 XXXX 1100 0000 0000 0000

- c)  $\overline{\text{CS}}/\text{LD}$ ; then V<sub>OUT</sub> = 5V on the ±10V range

Next, the bipolar range of  $\pm 10V$  is retained and the DAC output voltage is changed to  $V_{OUT} = -5V$ :

- a) CS/LD ₹

- c)  $\overline{\text{CS}}/\text{LD}$  ; then V<sub>OUT</sub> = -5V on the  $\pm 10\text{V}$  range

### APPLICATIONS INFORMATION

#### **Op Amp Selection**

Because of the extremely high accuracy of the 16-bit LTC1592, careful thought should be given to op amp selection in order to achieve the exceptional performance of which the part is capable. Fortunately, the sensitivity of INL and DNL to op amp offset has been greatly reduced compared to previous generations of multiplying DACs.

Tables 2 and 3 contain equations for evaluating the effects of op amp parameters on the LTC1592's accuracy when programmed in a unipolar or bipolar output range. These are the changes the op amp can cause to the INL, DNL, unipolar offset, unipolar gain error, bipolar zero and bipolar gain error. Tables 2 and 3 can also be used to determine the effects of op amp parameters on the LTC1589 and the LTC1588. However, the results obtained from Tables 2 and 3 are in 16-bit LSBs. Divide these results by 4 (LTC1589) and 16 (LTC1588) to obtain the correct LSB sizing. Table 4 contains a partial list of LTC precision op amps recommended for use with the LTC1592. The easy-to-use design equations simplify the selection of op amps to meet the system's specified error budget. Select the amplifier from Table 4 and insert the specified op amp parameters in Table 3. Add up all the errors for each category to determine the effect the op amp has on the accuracy of the LTC1592. Arithmetic summation gives an (unlikely) worstcase effect. A root-sum-square (RMS) summation produces a more realistic estimate.

Op amp offset will contribute mostly to output offset and gain error and has minimal effect on INL and DNL. For the LTC1592, a  $250\mu$ V op amp offset will cause about 0.65LSB INL degradation and 0.15LSB DNL degradation with a 10V full-scale range (20V range in bipolar). For the LTC1592 programmed in a unipolar mode, the same  $250\mu$ V op amp offset will cause a 3.3LSB zero-scale error and a 3.3LSB gain error with a 10V full-scale range.

While not directly addressed by the simple equations in Tables 2 and 3, temperature effects can be handled just as easily for unipolar and bipolar applications. First, consult an op amp's data sheet to find the worst-case  $V_{OS}$  and  $I_B$  over temperature. Then, plug these numbers in the  $V_{OS}$  and  $I_B$  equations from Table 3 and calculate the temperature induced effects.

For applications where fast settling time is important, Application Note 74, entitled "*Component and Measurement*

Table 2. Variables for Each Output Range That Adjust the Equations in Table 3

| OUTPUT RANGE  | A1  | A2 | A3  | A4  | A5  |

|---------------|-----|----|-----|-----|-----|

| 5V            | 1.1 | 2  |     |     | 1   |

| 10V           | 2.2 | 3  |     |     | 1.5 |

| ±5V           | 2   | 2  | 1.2 | 1   | 1.5 |

| ±10V          | 4   | 4  | 1.2 | 1   | 2.5 |

| ±2.5V         | 1   | 1  | 1.6 | 1   | 1   |

| -2.5V to 7.5V | 1.9 | 3  | 1   | 0.5 | 1.5 |

*Advances Ensure 16-Bit DAC Settling Time*," offers a thorough discussion of 16-bit DAC settling time and op amp selection.

#### **Precision Voltage Reference Considerations**

Much in the same way selecting an operational amplifier for use with the LTC1592 is critical to the performance of the system, selecting a precision voltage reference also requires due diligence. The output voltage of the LTC1592 is directly affected by the voltage reference; thus, any voltage reference error will appear as a DAC output voltage error.

There are three primary error sources to consider when selecting a precision voltage reference for 16-bit applications: output voltage initial tolerance, output voltage temperature coefficient and output voltage noise.

Initial reference output voltage tolerance, if uncorrected, generates a full-scale error term. Choosing a reference

| Table 0. From to Has Frenchises | Determine On Ann Effects   |                                      |

|---------------------------------|----------------------------|--------------------------------------|

| Table 3. Easy-to-Use Equations  | Determine Up Amp Effects o | on DAC Accuracy in All Output Ranges |

|                         |                                                                 |                                                                  | UNIPOLAR                                                       | BIPOLAR ZERO                                                                               | UNIPOLAR GAIN                                                   | <b>BIPOLAR GAIN</b>                                             |

|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| OP AMP                  | INL (LSB)                                                       | DNL (LSB)                                                        | OFFSET (LSB)                                                   | ERROR (LSB)                                                                                | ERROR (LSB)                                                     | ERROR (LSB)                                                     |

| V <sub>OS1</sub> (mV)   | $V_{OS1} \bullet 2.4 \bullet \left(\frac{5V}{V_{REF}}\right)$   | $V_{OS1} \bullet 0.6 \bullet \left(\frac{5V}{V_{REF}}\right)$    | $V_{OS1} \bullet 13.2 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $A3 \bullet V_{OS1} \bullet 19.8 \bullet \left(\frac{5V}{V_{REF}}\right)$                  | $V_{OS1} \bullet 13.2 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $V_{OS1} \bullet 13.2 \bullet \left(\frac{5V}{V_{REF}}\right)$  |

| I <sub>B1</sub> (nA)    | $I_{B1} \bullet 0.0003 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.00008 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.13 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $I_{B1} \bullet 0.01 \bullet \left(\frac{5V}{V_{REF}}\right)$                              | $I_{B1} \bullet 0.0018 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.0018 \bullet \left(\frac{5V}{V_{REF}}\right)$ |

| A <sub>VOL1</sub> (V/V) | A1 • $\left(\frac{16.5k}{A_{VOL1}}\right)$                      | A2 • $\left(\frac{1.5k}{A_{VOL1}}\right)$                        | 0                                                              | 0                                                                                          | A5 • $\left(\frac{131k}{A_{VOL1}}\right)$                       | A5 • $\left(\frac{131k}{A_{VOL1}}\right)$                       |

| V <sub>OS2</sub> (mV)   | 0                                                               | 0                                                                | 0                                                              | $A4 \bullet \left( V_{OS2} \bullet 13.1 \bullet \left( \frac{5V}{V_{REF}} \right) \right)$ | $V_{OS2} \bullet 26.2 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $V_{OS2} \bullet 26.2 \bullet \left(\frac{5V}{V_{REF}}\right)$  |

| I <sub>B2</sub> (mV)    | 0                                                               | 0                                                                | 0                                                              | A4 • $\left(I_{B2} \bullet 0.05 \bullet \left(\frac{5V}{V_{REF}}\right)\right)$            | $I_{B2} \bullet 0.1 \bullet \left(\frac{5V}{V_{REF}}\right)$    | $I_{B2} \bullet 0.1 \bullet \left(\frac{5V}{V_{REF}}\right)$    |

| A <sub>VOL2</sub> (V/V) | 0                                                               | 0                                                                | 0                                                              | A4 • $\left(\frac{66k}{A_{VOL2}}\right)$                                                   | $\left(\frac{131k}{AVOL2}\right)$                               | $\left(\frac{131k}{A_{VOL2}}\right)$                            |

# Table 4. Partial List of LTC Precision Amplifiers Recommended for Use with the LTC1588/LTC1589/LTC1592, with Relevant Specifications

|               | AMPLIFIER SPECIFICATIONS     |                      |                         |                            |                            |                      |                                  |                                 |                            |  |

|---------------|------------------------------|----------------------|-------------------------|----------------------------|----------------------------|----------------------|----------------------------------|---------------------------------|----------------------------|--|

| AMPLIFIER     | <b>V<sub>0S</sub><br/>μV</b> | I <sub>B</sub><br>nA | A <sub>OL</sub><br>V/mV | VOLTAGE<br>NOISE<br>nV/√Hz | CURRENT<br>NOISE<br>pA/√Hz | SLEW<br>RATE<br>V/µs | GAIN BANDWIDTH<br>Product<br>MHz | tsettling<br>with LTC1592<br>μs | POWER<br>DISSIPATION<br>mW |  |

| LT1001        | 25                           | 2                    | 800                     | 10                         | 0.12                       | 0.25                 | 0.8                              | 120                             | 46                         |  |

| LT1097        | 50                           | 0.35                 | 1000                    | 14                         | 0.008                      | 0.2                  | 0.7                              | 120                             | 11                         |  |

| LT1112 (Dual) | 60                           | 0.25                 | 1500                    | 14                         | 0.008                      | 0.16                 | 0.75                             | 115                             | 10.5/0p Amp                |  |

| LT1124 (Dual) | 70                           | 20                   | 4000                    | 2.7                        | 0.3                        | 4.5                  | 12.5                             | 19                              | 69/Op Amp                  |  |

| LT1468        | 75                           | 10                   | 5000                    | 5                          | 0.6                        | 22                   | 90                               | 2.5                             | 117                        |  |

| LT1469 (Dual) | 125                          | 10                   | 2000                    | 5                          | 0.6                        | 22                   | 90                               | 2.5                             | 123/Op Amp                 |  |

with low output voltage initial tolerance, like the LT1236  $(\pm 0.05\%)$ , minimizes the gain error caused by the reference; however, a calibration sequence that corrects for system zero- and full-scale error is always recommended.

A reference's output voltage temperature coefficient affects not only the full-scale error, but can also affect the circuit's INL and DNL performance. If a reference is chosen with a loose output voltage temperature coefficient, then the DAC output voltage along its transfer characteristic will be very dependent on ambient conditions. Minimizing the error due to reference temperature coefficient can be achieved by choosing a precision reference with a low output voltage temperature coefficient and/or tightly controlling the ambient temperature of the circuit to minimize temperature gradients.

As precision DAC applications move to 16-bit and higher performance, reference output voltage noise may contribute a dominant share of the system's noise floor. This in turn can degrade system dynamic range and signal-tonoise ratio. Care should be exercised in selecting a voltage reference with as low an output noise voltage as practical for the system resolution desired. Precision voltage references, like the LT1236, produce low output noise in the 0.1Hz to 10Hz region, well below the 16-bit LSB level in 5V or 10V full-scale systems. However, as the circuit bandwidths increase, filtering the output of the reference may be required to minimize output noise.

# Table 5. Partial List of LTC Precision References Recommended for Use with the LTC1588/LTC1589/LTC1592 with Relevant Specifications

| REFERENCE                | INITIAL<br>Tolerance | TEMPERATURE<br>DRIFT | 0.1Hz to 10Hz<br>NOISE |

|--------------------------|----------------------|----------------------|------------------------|

| LT1019A-5,<br>LT1019A-10 | ±0.05%               | 5ppm/°C              | 12μV <sub>P-P</sub>    |

| LT1236A-5,<br>LT1236A-10 | ±0.05%               | 5ppm/°C              | 3μV <sub>P-P</sub>     |

| LT1460A-5,<br>LT1460A-10 | ±0.075%              | 10ppm/°C             | 20µV <sub>P-P</sub>    |

| LT1790A-2.5              | ±0.05%               | 10ppm/°C             | 12µV <sub>Р-Р</sub>    |

#### Grounding

As with any high resolution converter, clean grounding is important. A low impedance analog ground plane and star grounding techniques should be used.  $I_{OUT2}$  must be tied to the star ground with as low a resistance as possible. When it is not possible to locate star ground close to  $I_{OUT2}$ , a low resistance trace should be used to route this pin to star ground. This minimizes the voltage drop from this pin to ground caused by the code dependent current flowing to ground. When the resistance of this circuit board trace becomes greater than  $1\Omega$ , a force/sense amplified configuration should be used to drive this pin (see Figure 2). This preserves the excellent accuracy (1LSB INL and DNL) of the LTC1588/LTC1589/LTC1592.

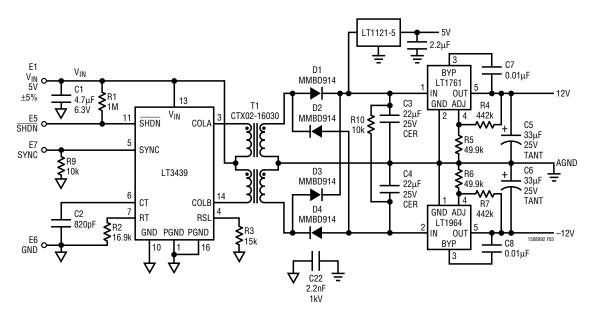

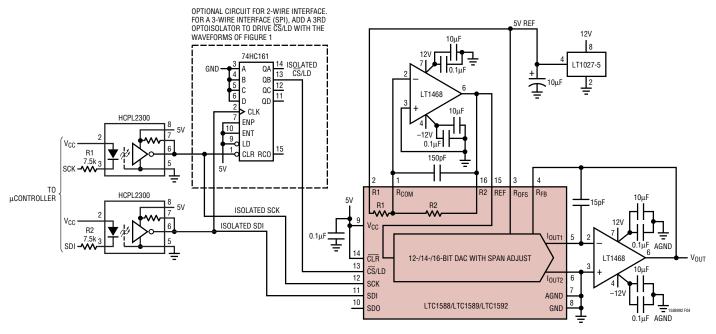

#### An Isolated 16-Bit Subsystem Using the LTC1592

The circuit in Figure 4 is a complete example of an optically isolated analog output subsystem that supports most of the legacy ranges that are still common in industrial environments. This circuit uses only two optoisolators, the load pulse ( $\overline{CS}$ /LD) being derived from a series of transitions on the data line (SDI) after the clock (SCK) is halted high. If a single chip microcontroller with an automated SPI interface is to be used, the SPI port can transfer the 24 bits as three bytes. Subsequently, the data output port pin can be reassigned to general purpose port operation and exercised to produce a number of transitions to generate the load pulse. Alternatively, the entire sequence can be programmed bit by bit with a general purpose port. Figure 5 shows the timing.

The DC/DC converter, Figure 3 based on the LT<sup>®</sup>3439 ultralow noise transformer driver provides a compact means of powering this circuit, and allows the output to deliver output current that is only limited by the LT1468 capabilities. The output capability of the DC/DC converter itself is 80mA at  $\pm$ 12V and is available as demo board DC511A. This circuit as shown requires approximately 130mA of the 5V supply (no load). The total surface area required is less than 2 square inches.

Figure 3. Isolated Power Supplies for the Circuit of Figure 4

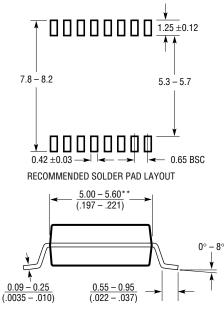

#### PACKAGE DESCRIPTION

G Package 16-Lead Plastic SSOP (5.3mm) (Reference LTC DWG # 05-08-1640)

NOTE:

1. CONTROLLING DIMENSION: MILLIMETERS

2. DIMENSIONS ARE IN MILLIMETERS (INCHES)

3. DRAWING NOT TO SCALE

- \* DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .152mm (.006") PER SIDE

- \*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED .254mm (.010") PER SIDE

Figure 4. Optically Isolated 16-Bit SoftSpan System

Figure 5. Timing Diagram for the Circuit of Figure 4

#### **RELATED PARTS**

| PART NUMBER                | DESCRIPTION                             | COMMENTS                                      |

|----------------------------|-----------------------------------------|-----------------------------------------------|

| LTC1591/LTC1597            | Parallel 14-/16-Bit Current Output DACs | On-Chip 4-Quadrant Resistors                  |

| LTC1595/LTC1596            | Serial 16-Bit Current Output DACs       | Low Glitch, ±1LSB Maximum INL, DNL            |

| LTC1599                    | 2-Byte, 16-Bit Current Output DAC       | On-Chip 4-Quadrant Resistors                  |

| LTC1821                    | Parallel 16-Bit Voltage Outupt DAC      | Precision 16-Bit Settling in 2µs for 10V Step |

| LTC2600/LTC2610<br>LTC2620 | Octal 16-/14-/12-Bit DACs               | Single Supply, µPower in Narrow SSOP16        |