# Passive-Input Digital Isolators - Open Drain Outputs

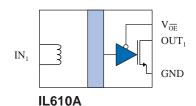

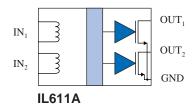

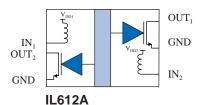

#### **Functional Diagrams**

#### **Features**

- 10 Mbps Data Rate

- Flexible Inputs with Very Wide Input Voltage Range

- Failsafe Output (logic high output for zero coil current)

- Output Enable (IL610A)

- 3.3 V or 5 V Power Supply

- 2500 V<sub>RMS</sub> Isolation (1 minute)

- Low Power Dissipation

- -40°C to 85°C Temperature Range

- 20 kV/µs Transient Immunity

- Low EMC Footprint

- UL1577 and IEC61010-2001 Approval

- 8-Pin MSOP, SOIC, and PDIP Packages

- Bare Die Available

#### **Applications**

- General Purpose Optocoupler Replacement

- Wired-OR Alarms

- SPI Interface

- I<sup>2</sup>C

- RS-485, RS-422, or RS-232

- Space-Critical Multi-Channel Applications

- Isolated Relays and Actuators

#### **Description**

The IL600A-Series are isolated signal couplers with opendrain outputs. They have a similar interface but better performance and higher package density than optocouplers.

The devices are manufactured with NVE's patented\* IsoLoop<sup>®</sup> spintronic Giant Magnetoresistive (GMR) technology for small size, high speed, and low power.

A single resistor sets the maximum input current for voltages above 0.5 V. A capacitor in parallel with the current-limit resistor provides improved dynamic performance.

These versatile components simplify inventory requirements by replacing a variety of optocouplers, functioning over a wide range of data rates, edge speeds, and power supply levels. The devices are available in MSOP, SOIC, and PDIP packages, as well as bare die.

IsoLoop® is a registered trademark of NVE Corporation. \*U.S. Patent number 5,831,426; 6,300,617 and others.

Absolute Maximum Ratings(1)

| Parameters                            | Symbol                      | Min. | Тур. | Max.           | Units | Test Conditions |

|---------------------------------------|-----------------------------|------|------|----------------|-------|-----------------|

| Storage Temperature                   | $T_{s}$                     | -55  |      | 150            | °C    |                 |

| Ambient Operating Temperature         | $T_A$                       | -55  |      | 125            | °C    |                 |

| Supply Voltage                        | $V_{\scriptscriptstyle DD}$ | -0.5 |      | 7              | V     |                 |

| DC Input Current                      | $I_{\rm IN}$                | -25  |      | 25             | mA    |                 |

| AC Input Current (Single-Ended Input) | $I_{\rm IN}$                | -35  |      | 35             | mA    |                 |

| AC Input Current (Differential Input) | $ m I_{IN}$                 | -75  |      | 75             | mA    |                 |

| Output Voltage                        | $V_{o}$                     | -0.5 |      | $V_{DD} + 1.5$ | V     |                 |

| Maximum Output Current                | $I_{o}$                     | -10  |      | 10             | mA    |                 |

| ESD                                   |                             |      | 2    |                | kV    | HBM             |

Note 1: Operating at absolute maximum ratings will not damage the device. Parametric performance is not guaranteed at absolute maximum ratings.

**Recommended Operating Conditions**

| Parameters                      | Symbol                      | Min. | Тур. | Max. | Units     | Test Conditions          |

|---------------------------------|-----------------------------|------|------|------|-----------|--------------------------|

| Ambient Operating Temperature   | T <sub>A</sub>              | -40  |      | 85   | °C        |                          |

| Supply Voltage                  | $V_{\scriptscriptstyle DD}$ | 3.0  |      | 5.5  | V         |                          |

| Input Current Low               | $I_{\text{IN Low}}$         | 5    |      | 10   | mA        | Current flow direction   |

| Input Current High              | $I_{\text{IN HIGH}}$        | -10  |      | 0.5  | mA        | defined as positive when |

| Differential Input Current Low  | $I_{\text{IN LOW}}$         | 5    |      | 60   | mA        | flowing into the Coil-   |

| Differential Input Current High | $I_{\text{IN HIGH}}$        | -60  |      | -5   | mA        | terminal and out Coil+   |

| Open Drain Reverse Voltage      | $V_{SD}$                    | -0.5 |      |      | V         |                          |

| Open Drain Voltage              | $V_{DS}$                    |      |      | 6.5  | V         |                          |

| Open Drain Load Current         | $I_{OD}$                    |      |      | 7    | mA        |                          |

| Common Mode Input Voltage       | $V_{\rm CM}$                |      |      | 400  | $V_{RMS}$ |                          |

**Insulation Specifications**

| Parameters                          | Symbol           | Min. | Тур.                  | Max. | Units                 | Test Conditions              |

|-------------------------------------|------------------|------|-----------------------|------|-----------------------|------------------------------|

| Creepage Distance (external)        |                  |      |                       |      |                       |                              |

| MSOP                                |                  | 3.01 |                       |      | mm                    |                              |

| 0.15" SOIC                          |                  | 4.03 |                       |      | mm                    |                              |

| 0.3" PDIP                           |                  | 7.08 |                       |      | mm                    |                              |

| Internal Isolation Distance         |                  |      | 9                     |      | μm                    |                              |

| Leakage Current                     |                  |      | 0.2                   |      | μΑ                    | 240 V <sub>RMS</sub> , 60 Hz |

| Barrier Impedance                   |                  |      | >10 <sup>14</sup>   7 |      | $\Omega \parallel pF$ |                              |

| Rated Voltage (1minute; MSOP)       | $V_{\rm ISO}$    | 1000 |                       |      | $V_{AC}$              | 50 Hz to 60 Hz               |

| Rated Voltage (1 min.; SOIC & PDIP) | V <sub>ISO</sub> | 2500 |                       |      | $V_{AC}$              | 50 Hz to 60 Hz               |

## **Safety and Approvals**

#### IEC61010-2001

TUV Certificate Numbers: N1502812, N1502812-101

#### Classification: Reinforced Insulation

| Model                        | Package      | Pollution Degree | Material Group | Max. Working Voltage             |

|------------------------------|--------------|------------------|----------------|----------------------------------|

| IL610A-1, IL611A-1, IL612A-1 | MSOP         | II               | III            | $150 V_{RMS}$                    |

| IL610A-2, IL611A-2, IL612A-2 | PDIP         | II               | III            | $300 \text{ V}_{\text{RMS}}$     |

| IL610A-3, IL611A-3, IL612A-3 | SOIC (0.15") | II               | III            | $150  \mathrm{V}_{\mathrm{RMS}}$ |

#### **UL 1577**

Component Recognition Program File Number: E207481

Rated 2500V<sub>RMS</sub> for 1 minute (SOIC, PDIP)

#### **Soldering Profile**

Per JEDEC J-STD-020C

#### Electrostatic Discharge Sensitivity

This product has been tested for electrostatic sensitivity to the limits stated in the specifications. However, NVE recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

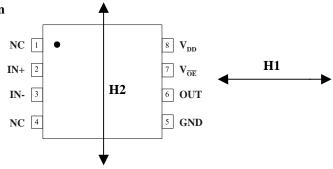

## **IL610A Pin Connections**

| 1 | NC                  | No internal connection                                        |

|---|---------------------|---------------------------------------------------------------|

| 2 | IN+                 | Coil connection                                               |

| 3 | IN-                 | Coil connection                                               |

| 4 | NC                  | No internal connection                                        |

| 5 | GND                 | Ground return for V <sub>DD</sub>                             |

| 6 | OUT                 | Data out                                                      |

| 7 | $V_{\overline{OE}}$ | Output enable. Internally held low with $100 \text{ k}\Omega$ |

| 8 | $V_{\mathrm{DD}}$   | Supply Voltage                                                |

# NC $\boxed{1}$ $\bullet$ $\boxed{8}$ $V_{DD}$ $\boxed{1N+2}$ $\boxed{7}$ $V_{\overline{OE}}$ $\boxed{1N-3}$ $\boxed{6}$ OUT $\boxed{5}$ GND

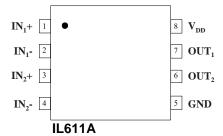

## **IL611A Pin Connections**

| 1 | IN <sub>1</sub> + | Channel 1 coil connection         |

|---|-------------------|-----------------------------------|

| 2 | IN <sub>1</sub> - | Channel 1 coil connection         |

| 3 | IN <sub>2</sub> + | Channel 2 coil connection         |

| 4 | IN <sub>2</sub> - | Channel 2 coil connection         |

| 5 | GND               | Ground return for V <sub>DD</sub> |

| 6 | $OUT_2$           | Data out, channel 2               |

| 7 | $OUT_1$           | Data out, channel 1               |

| 8 | $V_{\mathrm{DD}}$ | Supply Voltage                    |

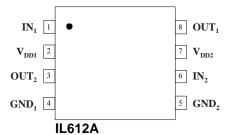

#### **IL612A Pin Connections**

| 1 | $IN_1$             | Data in, channel 1                 |

|---|--------------------|------------------------------------|

| 2 | $V_{\mathrm{DD1}}$ | Supply Voltage 1                   |

| 3 | $OUT_2$            | Data out, channel 2                |

| 4 | $GND_1$            | Ground return for V <sub>DD1</sub> |

| 5 | $GND_2$            | Ground return for V <sub>DD2</sub> |

| 6 | $IN_2$             | Data in, channel 2                 |

| 7 | $V_{\mathrm{DD2}}$ | Supply Voltage 2                   |

| 8 | $OUT_1$            | Data out, channel 1                |

# **Electrical Specifications**

Electrical specifications are  $T_{min}$  to  $T_{max}$  and 3.0 V to 5.5 V unless otherwise stated.

| Parameters                                         | Symbol                                                                                                                                                        | Min.           | Тур.                     | Max.             | Units          | Test Conditions                                                       |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|------------------|----------------|-----------------------------------------------------------------------|

| Coil Input Impedance                               | $Z_{COIL}$                                                                                                                                                    |                | 85  9                    |                  | μ  nH          | $T_{AMB} = 25^{\circ}C$<br>$V_{DD} = 3.0 \text{ V to } 5.5 \text{ V}$ |

| Temperature Coeff of Coil Resistance               | TC R <sub>COIL</sub>                                                                                                                                          |                | 0.2                      | 0.25             | Ω/°C           | $V_{DD} = 3.0 \text{ V to } 5.5 \text{ V}$                            |

| Input Threshold for Output Logic High              | $I_{\mathrm{INH}}$                                                                                                                                            | 0.5            | 1                        |                  | mA             | Single or Differential V <sub>DD</sub> = 3.0 V to 5.5 V               |

| Input Threshold for Output Logic Low               | $I_{\mathrm{INL}}$                                                                                                                                            | 5              | 3.5                      |                  | mA             | Single or Differential $V_{DD} = 3.0 \text{ V}$ to 5.5 V              |

| Quiescent Current                                  | $\begin{array}{c} \mathrm{IL610A,I_{DD}} \\ \mathrm{IL611A,I_{DD}} \\ \mathrm{IL612A,I_{DD1}} \\ \mathrm{IL612A,I_{DD2}} \end{array}$                         |                | 2<br>4<br>2<br>2         | 3<br>6<br>3<br>3 | mA<br>mA<br>mA | $V_{DD} = 5 \text{ V}, I_{IN}=0$ $R_{pullup} = \text{open circuit}$   |

| Quiescent Current                                  | $\begin{array}{c} \text{IL610A, I}_{\text{DD}} \\ \text{IL611A, I}_{\text{DD}} \\ \text{IL612A, I}_{\text{DD1}} \\ \text{IL612A, I}_{\text{DD2}} \end{array}$ |                | 1.3<br>2.6<br>1.3<br>1.3 | 2<br>4<br>2<br>2 | mA<br>mA<br>mA | $V_{DD}$ = 3.3 V, $I_{IN}$ =0 $R_{pullup}$ = open circuit             |

| Logic High Output Voltage <sup>(1)</sup>           | $V_{OH}$                                                                                                                                                      |                | $V_{\mathrm{DD}}$        |                  | V              | Off State                                                             |

| Logic Low Output Voltage                           | $V_{OL}$                                                                                                                                                      |                | 0 0.4                    | 0.1              | V              | $I_O = -20 \mu A$ $I_O = -4 \text{ mA}$                               |

| Logic Output Current                               | $ I_{O} $                                                                                                                                                     | 7              | 10                       |                  | mA             | -0 :                                                                  |

| Failsafe Operation Input Current <sup>(4)</sup>    | $I_{FS-HIGH}$                                                                                                                                                 | -25<br>5       |                          | 0.5<br>25        | mA<br>mA       | See Test Circuit 1                                                    |

|                                                    | I <sub>FS-LOW</sub>                                                                                                                                           | tching Specifi | estions at <b>5V</b>     | 23 IIIA          |                |                                                                       |

| Parameters                                         | Symbol                                                                                                                                                        | Min.           | Typ.                     | Max.             | Units          | Test Conditions                                                       |

| Input Signal Rise and Fall Times                   | t <sub>IR</sub> , t <sub>IF</sub>                                                                                                                             | 171111         |                          | 10               | μs             | See Test Circuit 1                                                    |

| Data Rate                                          | CIK, CIF                                                                                                                                                      | 10             |                          | 10               | Mbps           | See Test Circuit 1                                                    |

| Minimum Pulse Width                                | PW                                                                                                                                                            | 100            |                          |                  | ns             | See Test Circuit 1                                                    |

| Propagation Delay Input to Output<br>(High to Low) | $t_{ m PHL}$                                                                                                                                                  |                | 20                       | 25               | ns             | See Test Circuit 1                                                    |

| Propagation Delay Input to Output (Low to High)    | $t_{\rm PLH}$                                                                                                                                                 |                | 50                       | 75               | ns             | See Test Circuit 1                                                    |

| Common Mode Transient Immunity                     | $ CM_H ,  CM_L $                                                                                                                                              | 15             | 20                       |                  | kV/μs          | $V_T = 300 V_{peak}$                                                  |

| Failsafe Operation Input Current <sup>(2)</sup>    | I <sub>FS-HIGH</sub><br>I <sub>FS-LOW</sub>                                                                                                                   | -25<br>8       |                          | 0.5<br>5         | mA<br>mA       | See Test Circuit 1                                                    |

|                                                    | Swite                                                                                                                                                         | ching Specific | ations at 3.3V           |                  |                | _                                                                     |

| Parameters                                         | Symbol                                                                                                                                                        | Min.           | Тур.                     | Max.             | Units          | Test Conditions                                                       |

| Input Signal Rise and Fall Times                   | $t_{\rm IR},t_{ m IF}$                                                                                                                                        |                |                          | 10               | μs             | See Test Circuit 1                                                    |

| Data Rate                                          |                                                                                                                                                               | 10             |                          |                  | Mbps           | See Test Circuit 1                                                    |

| Minimum Pulse Width                                | PW                                                                                                                                                            | 100            |                          |                  | ns             | See Test Circuit 1                                                    |

| Propagation Delay Input to Output (High to Low)    | $t_{ m PHL}$                                                                                                                                                  |                | 20                       | 25               | ns             | See Test Circuit 1                                                    |

|                                                    |                                                                                                                                                               |                |                          |                  |                |                                                                       |

| Propagation Delay Input to Output                  | $t_{\rm PLH}$                                                                                                                                                 |                | 50                       | 75               | ns             | See Test Circuit 1                                                    |

|                                                    | $t_{PLH}$ $ CM_H ,  CM_L $                                                                                                                                    | 15             | 50                       | 75               | ns<br>kV/μs    | See Test Circuit 1 $V_T = 300 V_{peak}$                               |

#### Notes:

- 1.  $V_{\tiny DD}$  refers to the supply voltage on the output side of the isolated channel.

- 2. Failsafe Operation is defined as the guaranteed output state which will be achieved if the DC input current falls between the input levels specified (see Test Circuit 1 for details). Note if Failsafe to Logic Low is required, power supply voltages must be set to 5 V. Failsafe low on 3.3 V supplies is not specified but will typically require at least 8 mA of coil current.

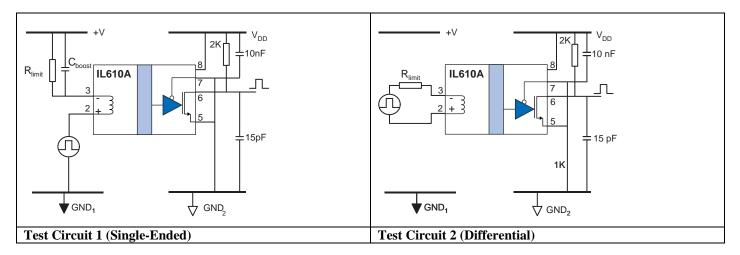

#### **Test Circuits**

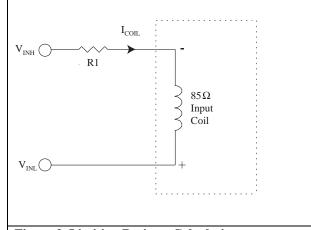

The test circuits below were used to obtain the specifications on the previous pages. In differential mode, the boost capacitor is generally not required, but it may be used to increase external magnetic field immunity.

#### **Operation**

IL600-A Series Isolators are current mode devices. Changes in current flow into the input coil result in logic state changes at the output. One of the significant advantages of the passive coil input is that both single ended and differential inputs can be handled without reverse bias protection. The GMR sensor switches the output to logic low if current flows from (In–) to (In+). Resistors set the coil input current to the 5 mA minimum. There is no limit to input voltages because there are no semiconductor input structures.

The absolute maximum current through the coil of the IL600-Series is 25 mA DC, or  $\pm 75$  mA in differential mode. The worst-case logic low threshold current is 5 mA. While typical threshold currents are actually less, NVE recommends 5 mA logic low thresholds as a minimum design value. In all cases, the current must flow from In– to In+ in the coil to switch the output low. This is the case for true or inverted data, in single-ended or differential configurations. Output logic high is the zero input current state. Note that current flowing from Coil+ to Coil- (negative current in the specifications) will push the GMR sensor further into the high state.

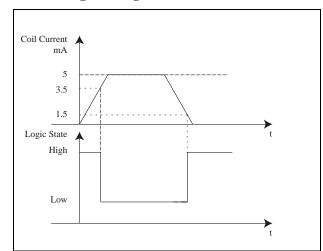

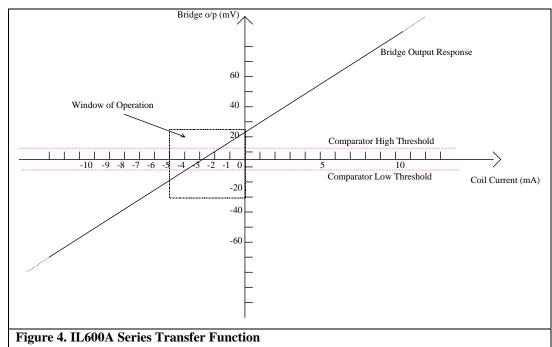

Figure 1 shows the response of the IL600-Series. The GMR bridge structure is designed so the output of the isolator is logic high with no signal present. The output will switch to the low state with approximately 3.5 mA of coil current, and switch back to the high state when the input current falls below 1.5 mA. This allows glitch-free interface with low slew rate signals.

To calculate the value of the protection resistor (R1), use Ohm's law as shown in the examples below. Note that only the magnitude of the voltage across the coil is important; the absolute values of  $V_{\text{INH}}$  and  $V_{\text{INL}}$  are arbitrary.

#### **Calculating Limiting Resistor Value**

Figure 1. IL600A-Series Transfer Function

Figure 2. Limiting Resistor Calculation Equivalent Circuit

**Example 1.** In this case,  $T_{\text{NOM}} = 25^{\circ}\text{C}$ ,  $V_{\text{IN}}$  High = 24 V,  $V_{\text{IN}}$  Low = 1.8 V,  $R_{\text{COIL}} = 85~\Omega$  and  $I_{\text{COIL}}$  minimum is specified as 5 mA. Total loop resistance is:

$$(R1 + R_{\text{COIL}}) = \frac{(V_{\text{INH}} - V_{\text{INL}})}{I_{\text{COIL}}} = \frac{22.2 \ \Omega}{0.005} = 4440 \ \Omega$$

Therefore:

$$R1 = 4440 \Omega - 85 \Omega = 4355 \Omega$$

**Example 2**. At a maximum operating temperature of 85°C:

$$T_{\text{MAX}}=85^{\circ}\text{C},\,T_{\text{NOM}}=25^{\circ}\text{C},\,V_{\text{IN}}\text{High}=5\,\,\text{V},\,V_{\text{IN}}\text{Low}=0\,\,\text{V},\,\text{and nominal}$$

$$R_{\text{COIL}}=85\,\,\Omega.$$

At  $T_{\text{MAX}} = 85^{\circ}\text{C}$ :

$$R_{\text{COIL}} = 85 + (T_{\text{MAX}} - T_{\text{NOM}}) \text{ x TCR}_{\text{COIL}}$$

=  $85 + (85 - 25) \text{ x } 0.2 = 85 + 12 = 97 \Omega$

Therefore, the recommended series resistor is:

$$R1 = \frac{(V_{INH} - V_{INL})}{I_{COIL}} - R_{COIL}$$

$$R1 = \frac{(5-0)}{0.005} - 97 = 903 \Omega$$

Allowance should also be made for the temperature coefficient of the current limiting resistor to ensure that  $I_{\text{\tiny COIL}}$  is at least 5 mA at the maximum operating temperature.

#### **Failsafe Operation**

Internal failsafe biasing ensures the output will always switch to the high state if the input coil is open-circuit. This is true for either 5 V or 3.3 V output supplies. The specifications on pages 5 and 6 show the enhanced failsafe conditions available with the IL600A-Series Isolators that cover the non-open circuit condition. The output will remain in the state specified, or will switch to that state, if the specified current is flowing in the coil. Note that positive values of current mean current flow into the In– input (pin 3 in Test Circuit 1).

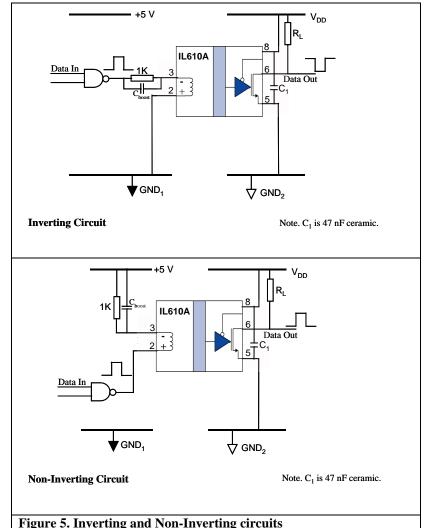

#### Single-Ended or Differential Input

The IL610A and IL611A can be run with single-ended or differential inputs. In differential mode, coil current reverses each cycle. In single-ended mode, a "boost capacitor" placed across the current limit resistor provides pulsed current reversal for correct operation. In the differential mode, current will naturally flow through the coil in both directions without the boost cap, although the cap can still be used if application factors such as increased external field immunity or improved PWD performance mandate. Absolute Maximum recommended coil current in single-ended mode is 25 mA while differential mode allows up to  $\pm 75$  mA to flow. The difference in specifications is due to the risk of electromigration of coil metals under constant current flow. In single ended mode, long-term DC current flow above 25 mA can cause erosion of the coil metal (rather like river flow does to its banks).

In differential mode, erosion takes place in both directions as each current cycle reverses and has a net effect of zero up to the fuse current. A current of more than 100 mA will cause the coil to irreparably fuse open.

There are many applications where the differential option can be very useful. One advantage over optocouplers and other high-speed couplers is that no reverse bias protection for the input structure is required for a differential signal. This reduces cost and complexity. One of the more common applications is for an isolated Differential Line Receiver. For example, RS-485 can drive an IL610 directly for a fraction of the cost of an isolated RS-485 node (see *Illustrative Applications* section).

#### **Typical Resistor Values**

| $V_{COIL}$ | 0.125W, 10% Resistor |

|------------|----------------------|

| 3.3 V      | 560 Ω                |

| 5 V        | 910 Ω                |

The table shows typical values for the external resistor in 5 V and 3 V logic systems. As always, these values as approximate and should be adjusted for temperature or other application specifics If the expected temperature range is large, 5% or even 1% tolerance resistors may provide additional design margin. Alternatively, see the

Applications Information section for circuit ideas allowing more generalized resistor selection.

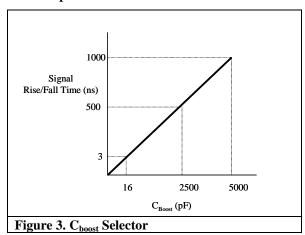

#### **Boost Capacitor**

The boost capacitor in parallel with the current-limiting resistor boosts the instantaneous coil current at the signal transition. The boost pushes the GMR bridge output through the comparator threshold voltage with less propagation delay and pulse width distortion.

The instantaneous boost capacitor current is proportional to input edge speeds ( $C\frac{dV}{dt}$ ). Select a capacitor value based on the rise and fall times of the input signal to be isolated that provides approximately 20 mA of additional "boost" current. Figure 3 is a guide to boost capacitor selection. For standard logic signals (t<sub>r</sub>,t<sub>f</sub> < 10 ns), a 16 pF capacitor is recommended. The capacitor value is generally not critical, and can often vary  $\pm 50\%$  with little noticeable difference in device performance.

#### **Dynamic Power Consumption**

Power consumption is proportional to duty cycle, not data rate. The use of NRZ coding minimizes power dissipation since no additional power is consumed when the output is in the high state. In differential mode, where the logic high condition may still require a current to be forced through the coil, power consumption will be higher than a typical NRZ single ended configuration.

#### **Power Supply Decoupling**

47 nF ceramic capacitors are recommended to decouple the power supplies. The capacitors should be placed as close as possible to the appropriate  $V_{DD}$  pin for optimal output wave shaping.

#### **Applications Information**

IL600A-Series Isolators are current mode devices. This means that a current of a certain magnitude and direction must flow in the input coil to change the output logic state. Figure 4 shows a simplified transfer curve for a typical IL600A-Series data channel.

The transfer function for this device is approximately linear. An applied coil input current creates a magnetic field that causes the GMR bridge output to change in proportion to the applied field. The GMR bridge is connected to a comparator. When the bridge output is greater than the comparator high threshold level, the output will go high. Similarly, when the bridge output is less than the comparator low threshold, the output will go low. The "Window of Operation" shown in Figure 4 highlights the specified corners of device operation. An input current

of approximately -3.5 mA or -1.5 mA will cause the device to hover around the comparator switching thresholds producing an unstable output. For single-ended operation across the entire temperature range and power supply range, the magnitude of the coil current for a logic low should be at least -5 mA, and the magnitude of the coil current for a logic high should be between -0.5 mA and 0 mA. The stated direction of the current is negative in Figure 4 because the magnetic field is negative with respect to Earth Field. Current is always fed into the In– terminal of an IL600A-Series device. Since these currents are actually sourced, not sunk, by the user, the specified currents are quoted as positive values in the *Electrical Specifications* section of this data sheet.

When designing circuits using digital logic, most designers are aware that the input to a logic gate is differential with respect to ground. Separate ground layers, star points or planes usually need to be designed into circuit boards with fast switching currents to reduce ground voltage bounce caused by inductance in ground returns. Ground error voltages can cause data errors in high-speed circuits due to their impact on the effective logic threshold voltage at any given instant. Similarly, when using IL600A-Series devices, the designer should be aware that it is the voltage magnitude across the coil that creates the current, not just the value of the input voltage. To illustrate this point, consider the single-ended non-inverting and inverting cases.

In the non-inverting circuit, the In-terminal is connected via a 1 k $\Omega$  current-limiting resistor to the supply rail, and the input is connected to the In+ terminal. Assume the supply voltage is +5 V and the input signal is a 5 V CMOS signal. A 1  $k\Omega$  resistance is selected to limit the coil current to 5 mA. For the purpose of this illustration we will ignore the coil resistance. When a logic high (+5 V) is applied to the input, the current through the coil is zero. When the input is a logic low (0 V), approximately 5 mA flows through the coil from the In- side to the In+ side. Figure 4 shows that the device will transition to both logic states easily under these conditions. Now assume that the 5 V rail is at 5.5 V and the CMOS input signal is loaded so that its high level is only 4.5 V. When a logic high (4.5 V) appears on the input, there is still a current of -1mA flowing through the coil. Figure 4 shows that the device is getting close to the off-state threshold of -1.5 mA, and now exceeds the specification of -0.5 mA for this logic level. Some intermittent operation or complete non-function should be expected in this case. The designer must ensure that the difference between the logic high voltage and the power supply voltage is such that the residual current in the coil is lower than 0.5 mA.

The inverting configuration design problem is similar to the problems associated with standard logic. In the inverting configuration, the signal into the coil is differential with respect to ground. The designer must ensure that the difference between the logic low voltage and the coil ground is such that the residual coil current is less than 0.5 mA. Conventional ground bounce design precautions apply.

The IL612A does not offer inverting operation because the coil In– inputs are internally hardwired to the device power supply. Therefore it is important to ensure the isolator power supply is at the same voltage as the power supply to the source of the input logic signal.

IL600 devices are simple to use as long as it is remembered that there must be enough coil current (5 mA) to ensure logic low output, and close to zero current (0.5 mA to 0 mA) to ensure logic high output.

#### **Electromagnetic Compatibility and Magnetic Field Immunity**

Because IL600-Series Isolators are completely static, they have the lowest emitted noise of any non-optical isolators.

IsoLoop devices operate by imposing a magnetic field on a GMR sensor, which translates the change in field into a change in logic state. There are several ways of enhancing magnetic field immunity. The devices are manufactured with a magnetic shield above the sensor. The shield acts as a flux concentrator to boost the magnetic signal from the internal coil, and as a shield against external magnetic fields. The shield absorbs surrounding stray flux until it becomes saturated. At saturation the shield is transparent to external applied fields, and the GMR sensor may react to the field. To compensate for this effect, IsoLoop Isolators use Wheatstone Bridge structures that are only sensitive to differential magnetic fields.

Providing a larger internal field will reduce the effect of an external field on the GMR sensor.

Immunity to external magnetic fields can also be enhanced by proper orientation of the device with respect to the field direction, the use of differential signaling, and field boosting capacitors.

Two ways to enhance immunity to external magnetic field are summarized below.

## 1. Orientation of the device with respect to the field direction

An applied field in the "H1" direction is the worst case for magnetic immunity. In this case the external field is in the same direction as the applied internal field. In one direction it will tend to help switching; in the other it will hinder switching. This can cause unpredictable operation.

An applied field in direction "H2" has considerably less effect and results in higher magnetic immunity.

#### 2. Differential Signaling and Boost Capacitors

Regardless of orientation, driving the coil differentially improves magnetic immunity. This is because the logic high state is driven by an applied field instead of zero field, as is the case with single-ended operation. The higher the coil current, the higher the internal field, and the higher the immunity to external fields.

Optimal magnetic immunity is achieved by adding the boost capacitor.

| Method                                                                             | Approximate Immunity | Immunity Description                                                                       |

|------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------|

| Field applied in H1 direction                                                      | ±20 Gauss            | A DC current of 16 A flowing in a conductor 1 cm from the device could cause disturbance.  |

| Field applied in H2 direction                                                      | ±70 Gauss            | A DC current of 56 A flowing in a conductor 1 cm from the device could cause disturbance.  |

| Field applied in any direction but with field booster capacitor (16 pF) in circuit | ±250 Gauss           | A DC current of 200 A flowing in a conductor 1 cm from the device could cause disturbance. |

#### **Data Rate and Magnetic Field Immunity**

It is easier to disrupt an isolated DC signal with an external magnetic field than it is to disrupt an isolated AC signal. Similarly, a DC magnetic field will have a greater effect on the device than an AC magnetic field of the same effective magnitude. For example, signals with pulses greater than 100 µs long are more susceptible to magnetic fields than shorter pulse widths.

#### **Illustrative Applications**

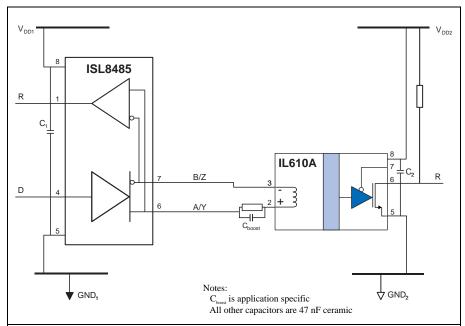

# Isolated RS-485 and RS-422 Receivers Using IL610As

IL610As can be used as simple isolated RS-485 or RS-422 receivers, terminating signals at the IL610A for a fraction of the cost of an isolated node. Cabling is greatly simplified by eliminating the need to power the input side of the receiving board. No current-limiting resistor is needed for a single receiver because it will draw less current than the driver maximum. Current limiting

| Number of | Current Limit |

|-----------|---------------|

| Nodes     | Resistors (Ω) |

| 1         | None          |

| 2         | 17            |

| 3         | 22            |

| 4         | 27            |

| 5         | 27            |

| 6         | 27            |

| 7         | 30            |

| 8         | 30            |

resistors allow at least eight nodes without exceeding the maximum load of the transceiver chip. Placement of the current-limiting resistors on both lines provides better dynamic signal balance. There is no need for line termination resistors because the IL610A coil resistance of approximately 85  $\Omega$  is close to the characteristic impedance of most cables. The circuit is intrinsically open circuit failsafe because the IL610A is guaranteed to switch to the high state when the coil input current is less than 500  $\mu A$ . For higher speed, a faster output device (such the CMOS-output IL600-Series Isolators) are needed as well as possibly better impedance matching.

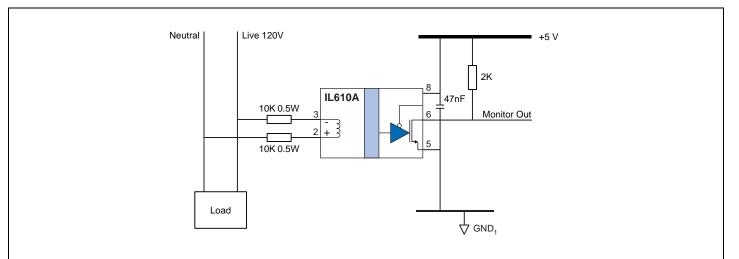

#### **Isolated 120 V Line Monitor**

The wide input voltage range of IL600 Isolators allow connection to line voltage through current-limiting resistors. In this illustrative circuit, "Monitor Out" goes low when line voltage exceeds approximately 100 V, and high when line voltage drops below approximately 10 V.

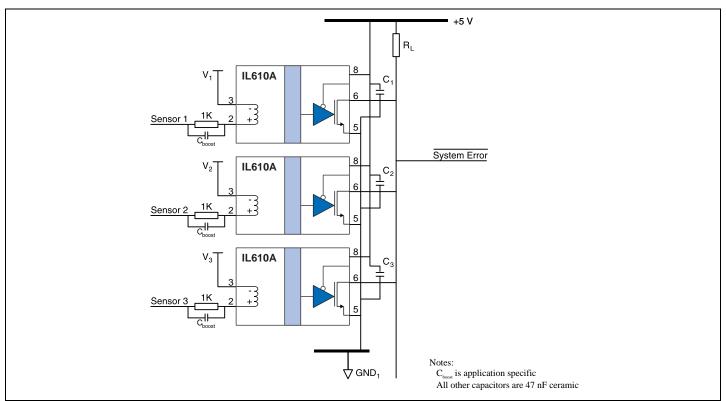

#### **Multi-channel Isolated Alarm Monitor**

The open-drain outputs of IL600A-Series Isolators allow wired-OR outputs. The inputs can be configured for inverting or non-inverting operation (see Applications Information), and a very wide input voltage range is possible. This illustrative circuit provides fail-safe output (logic high output for zero coil current) and typical logic output sink current of 10 mA for each isolator.

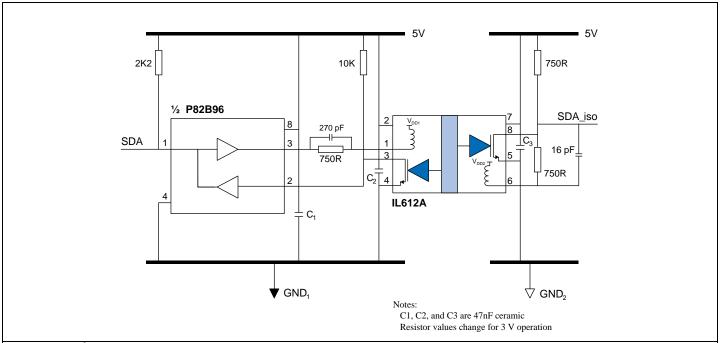

## Isolation of I<sup>2</sup>C Nodes

This circuit provides bidirectional isolation of I<sup>2</sup>C bus signals with no restrictions on data rate and none of the I<sup>2</sup>C bus latch-up problems common with other isolation circuits.

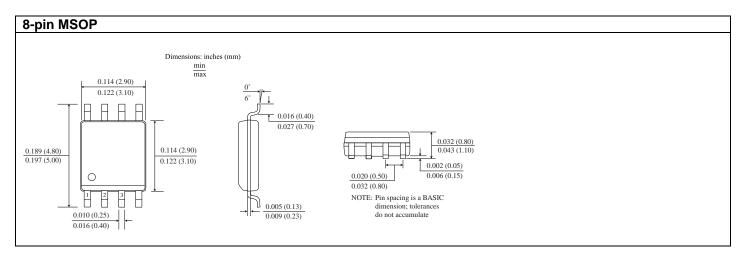

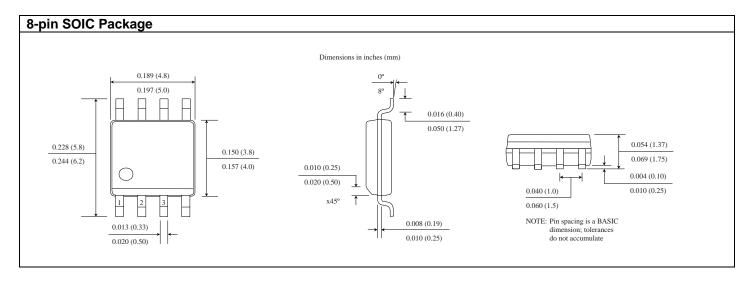

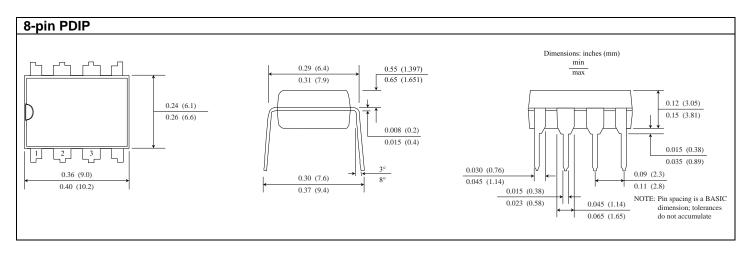

# Package Drawings, Dimensions and Specifications

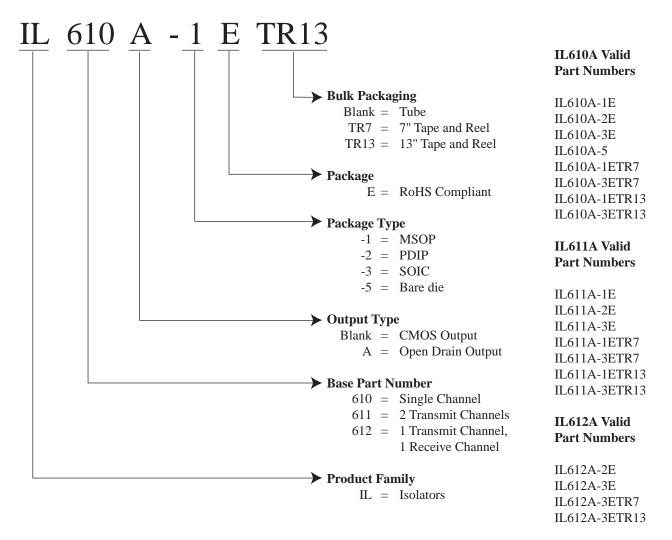

# **Ordering Information and Valid Part Numbers**

| Revision History                    |                                                                                                                                                                                   |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISB-DS-001-IL600A-P<br>January 2009 | Changes  • Added EMC details.                                                                                                                                                     |

| ISB-DS-001-IL600A-O                 | <ul> <li>Changes</li> <li>Clarified I<sup>2</sup>C application diagram and expanded caption (p. 13).</li> </ul>                                                                   |

| ISB-DS-001-IL600A-N                 | <ul><li>Changes</li><li>IEC 61010 approval for MSOP versions.</li></ul>                                                                                                           |

| ISB-DS-001-IL600A-M                 | <ul><li>Changes</li><li>Specify coil resistance as typical only.</li></ul>                                                                                                        |

|                                     | Revise section on calculating limiting resistors.                                                                                                                                 |

| ISB-DS-001-IL600A-L                 | <ul> <li>Changes</li> <li>Note on all package drawings that pin-spacing tolerances are non-accumulating; change MSOP pin-spacing dimensions and tolerance accordingly.</li> </ul> |

| ISB-DS-001-IL600A-K                 | <ul><li>Changes</li><li>Change lower limit of length on PDIP package drawing.</li></ul>                                                                                           |

|                                     | <ul> <li>Tightened pin-spacing tolerance on MSOP package drawing.</li> </ul>                                                                                                      |

| ISB-DS-001-IL600A-J                 | <ul> <li>Changes</li> <li>Changed ordering information to reflect that devices are now fully RoHS compliant with no exemptions.</li> </ul>                                        |

| ISB-DS-001-IL600A-I                 | <ul><li>Changes</li><li>Added differential drive specifications</li></ul>                                                                                                         |

|                                     | Eliminated soldering profile chart                                                                                                                                                |

| ISB-DS-001-IL600A-H                 | Changes • Changed RS-485 transceiver                                                                                                                                              |

|                                     | • Revised I <sup>2</sup> C circuit component values                                                                                                                               |

| ISB-DS-001-IL600A-G                 | <ul><li>Changes</li><li>Added enhanced failsafe specification</li></ul>                                                                                                           |

| ISB-DS-001-IL600A-F                 | Changes  • Minor changes to circuit diagrams                                                                                                                                      |

|                                     | <ul> <li>Expanded captions for illustrative applications.</li> </ul>                                                                                                              |

| ISB-DS-001-IL600A-E                 | <ul><li>Changes</li><li>Misc. typographical and syntax changes.</li></ul>                                                                                                         |

| ISB-DS-001-IL600A-D                 | <ul><li>Changes</li><li>Voltage ratings added to Insulation Specifications</li></ul>                                                                                              |

|                                     | • Notes added on use of C <sub>BOOST</sub>                                                                                                                                        |

|                                     | • 5v specifications without C <sub>BOOST</sub> removed                                                                                                                            |

|                                     | <ul> <li>Application circuits changed to show C<sub>BOOST</sub></li> </ul>                                                                                                        |

|                                     | • Figure Four shows C <sub>BOOST</sub> .                                                                                                                                          |

|                                     | Test Circuit #2 removed                                                                                                                                                           |

#### **About NVE**

An ISO 9001 Certified Company

NVE Corporation manufactures innovative products based on unique spintronic Giant Magnetoresistive (GMR) technology. Products include Magnetic Field Sensors, Magnetic Field Gradient Sensors (Gradiometers), Digital Magnetic Field Sensors, Digital Signal Isolators, and Isolated Bus Transceivers.

NVE pioneered spintronics and in 1994 introduced the world's first products using GMR material, a line of ultra-precise magnetic sensors for position, magnetic media, gear speed and current sensing.

NVE Corporation 11409 Valley View Road Eden Prairie, MN 55344-3617 USA Telephone: (952) 829-9217

Fax: (952) 829-9189 Internet: www.nve.com e-mail: isoinfo@nve.com

The information provided by NVE Corporation is believed to be accurate. However, no responsibility is assumed by NVE Corporation for its use, nor for any infringement of patents, nor rights or licenses granted to third parties, which may result from its use. No license is granted by implication, or otherwise, under any patent or patent rights of NVE Corporation. NVE Corporation does not authorize, nor warrant, any NVE Corporation product for use in life support devices or systems or other critical applications, without the express written approval of the President of NVE Corporation.

Specifications are subject to change without notice.

ISB-DS-001-IL600A-P January 2009