# ANALOG DEVICES

# 1.2 A Programmable Device Power Supply with Integrated 16-Bit Level Setting DACs

# AD5560

### FEATURES

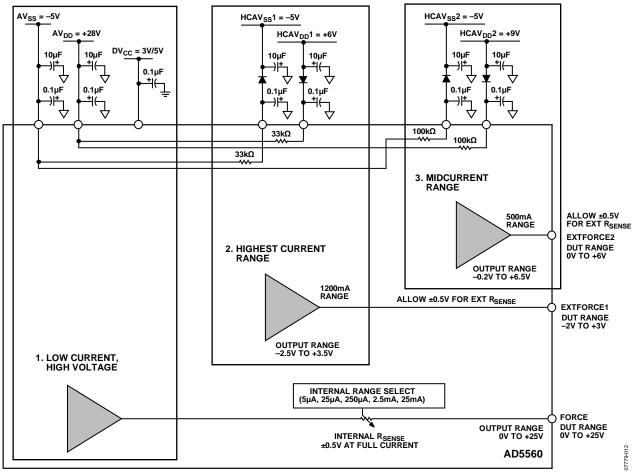

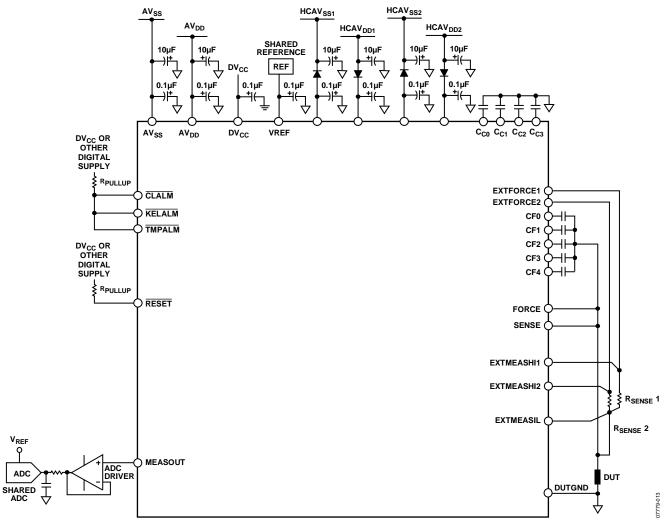

Programmable device power supply (DPS) FV, MI, MV, FNMV functions 5 internal current ranges (on-chip RSENSE)  $\pm 5 \ \mu$ A,  $\pm 25 \ \mu$ A,  $\pm 250 \ \mu$ A,  $\pm 2.5 \ m$ A,  $\pm 25 \ m$ A 2 external high current ranges (external R<sub>SENSE</sub>) EXTFORCE1: ±1.2 A maximum EXTFORCE2: ±500 mA maximum Integrated programmable levels All 16-bit DACs: force DAC, comparator DACs, clamp DACs, offset DAC, OSD DAC, DGS DAC Programmable Kelvin clamp and alarm Offset and gain correction registers on-chip Ramp mode on force DAC for power supply slewing Programmable slew rate feature, 1 V/µs to 0.3 V/µs **DUTGND Kelvin sense and alarm** 25 V FV span with asymmetrical operation within -22 V/+25 V

### **GENERAL DESCRIPTION**

The AD5560 is a high performance, highly integrated device power supply consisting of programmable force voltages and measure ranges. This part includes the required DAC levels to set the programmable inputs for the drive amplifier, as well as clamping and comparator circuitry. Offset and gain correction is included on-chip for DAC functions. A number of programmable measure current ranges are available: five internal fixed ranges and two external customer-selectable ranges (EXTFORCE1 and EXTFORCE2) that can supply currents up to  $\pm 1.2$  A and  $\pm 500$  mA, respectively. The voltage range possible at this high current level is limited by headroom and the maximum power On-chip comparators Gangable for higher current Guard amplifier System PMU connections Current clamps Die temperature sensor and shutdown feature On-chip diode thermal array Diagnostic register allows access to internal nodes Open-drain alarm flags (temperature, current clamp, Kelvin alarm) SPI-/MICROWIRE-/DSP-compatible interface 64-lead (10 mm × 10 mm) TQFP with exposed pad (on top)

### **APPLICATIONS**

Automatic test equipment (ATE) Device power supply

dissipation. Current ranges in excess of  $\pm 1.2$  A or at high current and high voltage combinations can be achieved by paralleling or ganging multiple DPS devices. Open-drain alarm outputs are provided in the event of overcurrent, overtemperature, or Kelvin alarm on either the SENSE or DUTGND line.

The DPS functions are controlled via a simple 3-wire serial interface compatible with SPI, QSPI<sup>™</sup>, MICROWIRE<sup>™</sup>, and DSP interface standards running at clock speeds of up to 50 MHz.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2008-2009 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                                                                                                                                    |

| General Description 1                                                                                                                                                                                                                                                                                                                                                            |

| Revision History                                                                                                                                                                                                                                                                                                                                                                 |

| Functional Block Diagram 4                                                                                                                                                                                                                                                                                                                                                       |

| Specifications                                                                                                                                                                                                                                                                                                                                                                   |

| Timing Characteristics                                                                                                                                                                                                                                                                                                                                                           |

| Timing Diagrams13                                                                                                                                                                                                                                                                                                                                                                |

| Absolute Maximum Ratings15                                                                                                                                                                                                                                                                                                                                                       |

| Thermal Resistance                                                                                                                                                                                                                                                                                                                                                               |

| ESD Caution15                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Configuration and Function Descriptions16                                                                                                                                                                                                                                                                                                                                    |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                              |

| Terminology                                                                                                                                                                                                                                                                                                                                                                      |

| Theory of Operation                                                                                                                                                                                                                                                                                                                                                              |

| Force Amplifier27                                                                                                                                                                                                                                                                                                                                                                |

| DAC Reference Voltage (VREF)27                                                                                                                                                                                                                                                                                                                                                   |

| Open-Sense Detect (OSD) Alarm and Clamp                                                                                                                                                                                                                                                                                                                                          |

| Device Under Test Ground (DUTGND)27                                                                                                                                                                                                                                                                                                                                              |

| GPO                                                                                                                                                                                                                                                                                                                                                                              |

| Comparators                                                                                                                                                                                                                                                                                                                                                                      |

| Current Clamps                                                                                                                                                                                                                                                                                                                                                                   |

| Short-Circuit Protection                                                                                                                                                                                                                                                                                                                                                         |

| Guard Amplifier                                                                                                                                                                                                                                                                                                                                                                  |

| Compensation Capacitors                                                                                                                                                                                                                                                                                                                                                          |

| Current Range Selection29                                                                                                                                                                                                                                                                                                                                                        |

| High Current Ranges                                                                                                                                                                                                                                                                                                                                                              |

| High Current Ranges                                                                                                                                                                                                                                                                                                                                                              |

| High Current Ranges       29         Ideal Sequence for Gang Mode       30                                                                                                                                                                                                                                                                                                       |

| 6 6                                                                                                                                                                                                                                                                                                                                                                              |

| Ideal Sequence for Gang Mode                                                                                                                                                                                                                                                                                                                                                     |

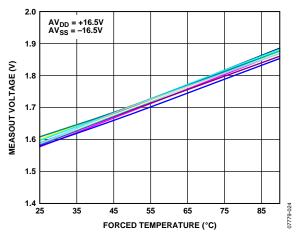

| Ideal Sequence for Gang Mode       30         Compensation for Gang Mode       30         System Force/Sense Switches       30         Die Temperature Sensor and Thermal Shutdown       31         Measure Output (MEASOUT)       31         V <sub>MID</sub> Voltage       31                                                                                                  |

| Ideal Sequence for Gang Mode       30         Compensation for Gang Mode       30         System Force/Sense Switches       30         Die Temperature Sensor and Thermal Shutdown       31         Measure Output (MEASOUT)       31         V <sub>MID</sub> Voltage       31         Force Amplifier Stability.       34                                                      |

| Ideal Sequence for Gang Mode                                                                                                                                                                                                                                                                                                                                                     |

| Ideal Sequence for Gang Mode       30         Compensation for Gang Mode       30         System Force/Sense Switches       30         Die Temperature Sensor and Thermal Shutdown       31         Measure Output (MEASOUT)       31         V <sub>MID</sub> Voltage       31         Force Amplifier Stability.       34         Poles and Zeros in a Typical System       35 |

| Compensation Strategies                                                     | 36 |

|-----------------------------------------------------------------------------|----|

| Optimizing Performance for a Known Capacitor Using<br>Autocompensation Mode | 36 |

| Adjusting the Autocompensation Mode                                         | 37 |

| Dealing with Parallel Load Capacitors                                       | 37 |

| DAC Levels                                                                  | 37 |

| Force and Comparator DACs                                                   | 37 |

| Clamp DACs                                                                  | 37 |

| OSD DAC                                                                     | 38 |

| DUTGND DAC                                                                  | 38 |

| Offset DAC                                                                  | 38 |

| Offset and Gain Registers                                                   | 38 |

| Reference Selection                                                         | 39 |

| Choosing AV <sub>DD</sub> /AV <sub>SS</sub> Power Supply Rails              | 39 |

| Choosing HCAV <sub>SS</sub> x and HCAV <sub>DD</sub> x Supply Rails         | 39 |

| Power Dissipation                                                           | 39 |

| Package Composition and Maximum Vertical Force                              |    |

| Slew Rate Control                                                           | 40 |

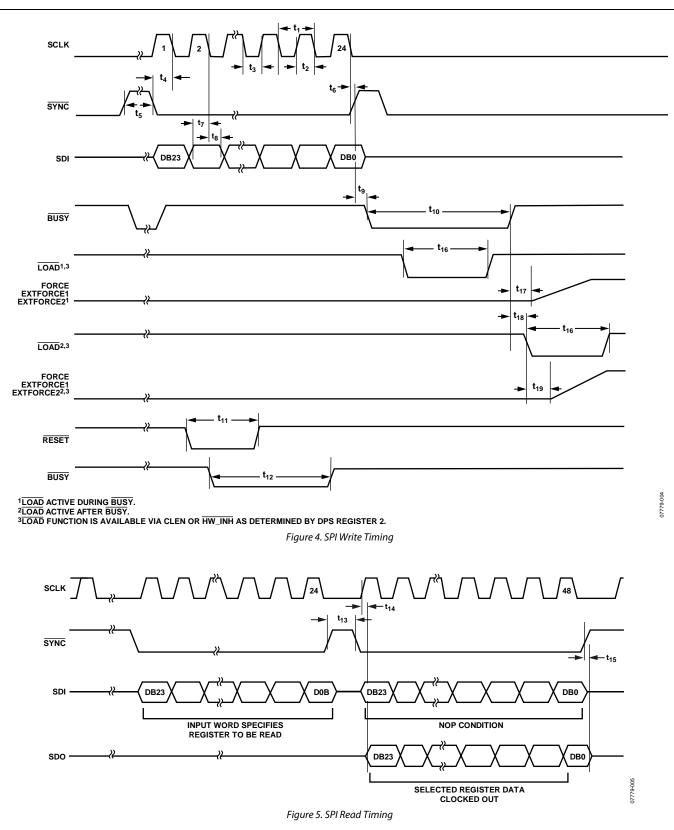

| Serial Interface                                                            | 42 |

| SPI Interface                                                               | 42 |

| SPI Write Mode                                                              | 42 |

| SDO Output                                                                  | 42 |

| RESET Function                                                              | 42 |

| BUSY Function                                                               | 42 |

| LOAD Function                                                               | 42 |

| Register Update Rates                                                       | 43 |

| Control Registers                                                           |    |

| DPS and DAC Addressing                                                      |    |

| Readback Mode                                                               | 55 |

| DAC Readback                                                                | 55 |

| Power-On Default                                                            | 55 |

| Using the HCAV <sub>DD</sub> x and HCAV <sub>SS</sub> x Supplies            | 57 |

| Power Supply Sequencing                                                     |    |

| Required External Components                                                |    |

| Power Supply Decoupling                                                     |    |

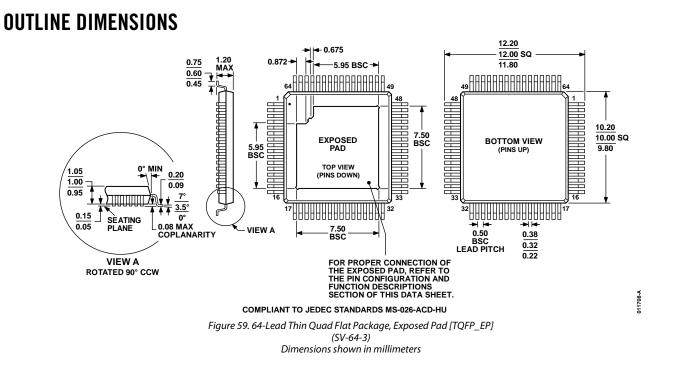

| Outline Dimensions                                                          |    |

| Ordering Guide                                                              |    |

| č                                                                           |    |

### **REVISION HISTORY**

#### 9/09—Rev. A to Rev. B

| Changes to Table 1, Measure Current and Measure Voltage |    |

|---------------------------------------------------------|----|

| Parameters                                              | 6  |

| Changes to Die Temperature Sensor and Thermal           |    |

| Shutdown Section                                        | 31 |

| Changes to Table 10 and Table 11                        | 32 |

| Changes to Table 18, Bit 15                             | 45 |

| Changes to Table 23, Bits[15:12]                        | 50 |

| Changes to Table 25                                     | 54 |

|                                                         |    |

### 12/08—Rev. 0 to Rev. A

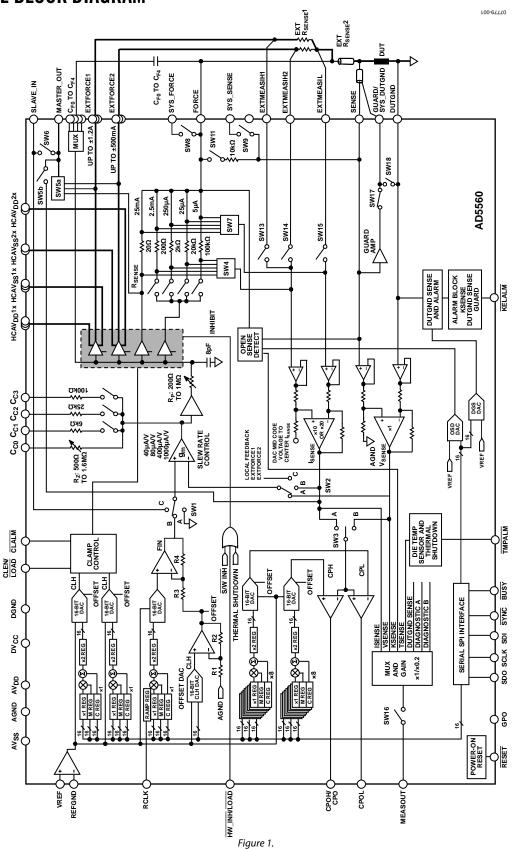

| Changes to Figure 1                                | 4  |

|----------------------------------------------------|----|

| Changes to Table 1                                 | 4  |

| Changes to Table 2                                 | 13 |

| Changes to Table 3                                 | 15 |

| Changes to Open-Sense Detect (OSD) Alarm and Clamp | 27 |

| Changes to Figure 53                               | 30 |

| Change to gm Maximum Rating, Table 13              | 34 |

| Changes to Table 19                                | 46 |

| Changes to Bit 7, Bit 8 Functions, Table 21        |    |

| Changes to Power Supply Decoupling Section         | 59 |

|                                                    |    |

### 11/08—Revision 0: Initial Version

# FUNCTIONAL BLOCK DIAGRAM

Rev. B | Page 4 of 60

# **SPECIFICATIONS**

$$\begin{split} HCAV_{DD}x &\leq (AV_{SS} + 33 \text{ V}), HCAV_{DD}x \leq AV_{DD}, HCAV_{SS}x \geq AV_{SS}, AV_{DD} \geq 8 \text{ V}, AV_{SS} \leq -5 \text{ V}, \left|AV_{DD} - AV_{SS}\right| \geq 16 \text{ V} \text{ and } \leq 33 \text{ V}, DV_{CC} = 2.3 \text{ V} \text{ to } 5.5 \text{ V}, V_{REF} = 5 \text{ V}, \text{gain (m)}, \text{offset (c)}, \text{ and DAC offset registers are at default values; } AGND = DGND = 0 \text{ V}; T_J = 25^{\circ}\text{C} \text{ to } 90^{\circ}\text{C}, \text{maximum specifications, unless otherwise noted. FSV is full-scale voltage, FSVR is full-scale voltage range, FSC is full-scale current, FSCR is full-scale current range. \end{split}$$

| Parameter                                       | Min                          | Тур  | Мах                          | Unit   | Test Conditions/Comments                                                                                                                                                     |

|-------------------------------------------------|------------------------------|------|------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FORCE VOLTAGE                                   |                              |      |                              |        |                                                                                                                                                                              |

| Force Output Voltage <sup>1</sup>               |                              |      |                              |        |                                                                                                                                                                              |

| EXTFORCE1                                       | AV <sub>ss</sub> + 2.25      |      | AV <sub>DD</sub> - 2.25      | V      | External current range, EXTFORCE1; allow                                                                                                                                     |

|                                                 | HCAV <sub>ss</sub> 1x + 1.75 |      | HCAV <sub>DD</sub> 1x - 1.75 |        | $\pm$ 500 mV for external R <sub>SENSE</sub> voltage drop.                                                                                                                   |

| EXTFORCE2                                       | AV <sub>ss</sub> + 2.25      |      | AV <sub>DD</sub> - 2.25      | V      | External current range, EXTFORCE2; allow                                                                                                                                     |

|                                                 | HCAV <sub>ss</sub> 2x + 1.75 |      | HCAV <sub>DD</sub> 2x - 1.75 |        | $\pm 500$ mV for external R <sub>SENSE</sub> voltage drop.                                                                                                                   |

| FORCE                                           | AV <sub>ss</sub> + 2.75      |      | AV <sub>DD</sub> – 2.75      | V      | Internal current ranges, includes ±500 mV for internal R <sub>SENSE</sub> voltage drop.                                                                                      |

| Headroom/Footroom <sup>1</sup>                  | -2.75                        |      | +2.75                        | V      | Internal current ranges to AV <sub>DD</sub> /AV <sub>SS</sub> , includes ±500 mV for internal R <sub>SENSE</sub> voltage drop.                                               |

| Headroom/Footroom <sup>1</sup>                  | -2.25                        |      | +2.25                        | V      | External current ranges, EXTFORCE1/<br>EXTFORCE2 to HCAV <sub>DD</sub> x and HCAV <sub>SS</sub> x supplies;<br>includes ±500 mV for external R <sub>SENSE</sub> voltage drop |

| Force Output Voltage Span                       | -22                          |      | +25                          | V      | May be a skewed range but within headroom requirements and maximum power dissipatio for current range.                                                                       |

| Forced Voltage Linearity Error                  | -2                           |      | +2                           | mV     |                                                                                                                                                                              |

| Forced Voltage Offset Error                     | -50                          |      | +50                          | mV     | Uncalibrated, use c register to calibrate, measured at midscale.                                                                                                             |

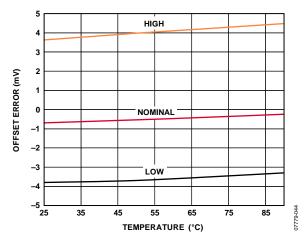

| Forced Voltage Offset Error Tempco <sup>1</sup> |                              | 27   |                              | μV/°C  | Standard deviation = 23 $\mu$ V/°C.                                                                                                                                          |

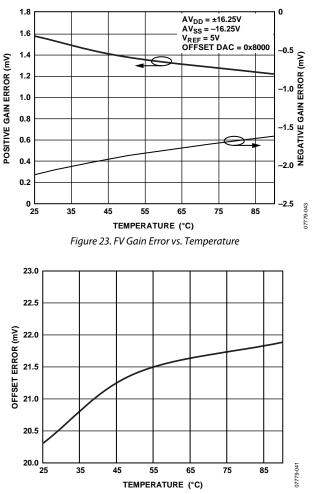

| Forced Voltage Gain Error                       | -25                          |      | +25                          | mV     | Uncalibrated, use m register to calibrate.                                                                                                                                   |

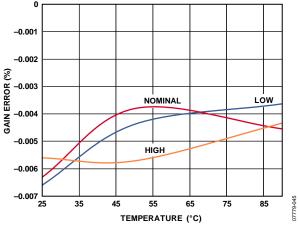

| Forced Voltage Gain Error Tempco <sup>1</sup>   |                              | 4    |                              | ppm/°C | Standard deviation = 3 ppm/°C.                                                                                                                                               |

| Short-Circuit Current Limit <sup>2</sup>        |                              |      |                              |        | Clamps off.                                                                                                                                                                  |

| EXTFORCE1                                       | -3.5                         | ±2.7 | +3.5                         | А      | Positive and negative dc short-circuit current.                                                                                                                              |

| EXTFORCE2                                       | -1.25                        | ±0.9 | +1.25                        | А      | Positive and negative dc short-circuit current.                                                                                                                              |

| FORCE                                           | -75                          | ±50  | +75                          | mA     | ±25 mA range, positive and negative dc short circuit current.                                                                                                                |

|                                                 | -20                          | ±10  | +20                          | mA     | All other ranges, positive and negative dc short-circuit current.                                                                                                            |

| Active C <sub>Fx</sub> Buffer                   | -64                          |      | +64                          | mA     |                                                                                                                                                                              |

| DC Load Regulation <sup>1</sup>                 | -1                           |      | +1                           | mV     | EXTFORCE1 range, $\pm 1$ A load current change.                                                                                                                              |

|                                                 | -0.4                         |      | +0.4                         | mV     | EXTFORCE2 range, ±0.5 A load current change                                                                                                                                  |

| Load Transient Response <sup>1</sup>            |                              | 70   |                              | mV     | 1.2 A load step into 30 $\mu F$ DUT capacitance (10 m $\Omega$ ESR).                                                                                                         |

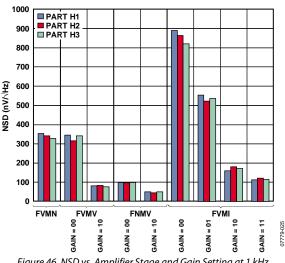

| NSD <sup>1</sup>                                |                              | 350  |                              | nV/√Hz | Measured at 1 kHz, at output of FORCE.                                                                                                                                       |

| MEASURE CURRENT RANGES                          |                              |      |                              |        | Sense resistors are trimmed to within 1%, nominal $\pm 500$ mV V <sub>RSENSE</sub> .                                                                                         |

| Internal Sense Resistors <sup>1</sup>           |                              | 100  |                              | kΩ     | ±5 μA current range.                                                                                                                                                         |

|                                                 |                              | 20   |                              | kΩ     | ±25 μA current range.                                                                                                                                                        |

|                                                 |                              | 2    |                              | kΩ     | ±250 μA current range.                                                                                                                                                       |

|                                                 |                              | 200  |                              | Ω      | ±2.5 mA current range.                                                                                                                                                       |

|                                                 |                              | 20   |                              | Ω      | ±25 mA current range.                                                                                                                                                        |

| Parameter                                     | Min                     | Тур   | Мах              | Unit          | Test Conditions/Comments                                                                                                                                      |

|-----------------------------------------------|-------------------------|-------|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measure Current Ranges                        |                         |       |                  |               | Specified current ranges with $V_{REF} = 5 V$ and $N$ gain = 20, or with $V_{REF} = 2.5 V$ and MI gain = 5.                                                   |

|                                               |                         | ±5    |                  | μA            | Set using internal sense resistor.                                                                                                                            |

|                                               |                         | ±25   |                  | μA            | Set using internal sense resistor.                                                                                                                            |

|                                               |                         | ±250  |                  | μA            | Set using internal sense resistor.                                                                                                                            |

|                                               |                         | ±2.5  |                  | mA            | Set using internal sense resistor.                                                                                                                            |

|                                               |                         | ±25   |                  | mA            | Set using internal sense resistor.                                                                                                                            |

|                                               |                         | ±500  |                  | mA            | EXTFORCE2, set by user with external sense                                                                                                                    |

|                                               |                         | ±300  |                  |               | resistor, limited by headroom requirements<br>and maximum power dissipation.                                                                                  |

|                                               |                         | ±1200 |                  | mA            | EXTFORCE1, set by user with external sense resistor, limited by headroom requirements                                                                         |

|                                               |                         |       |                  |               | and maximum power dissipation.                                                                                                                                |

| MEASURE CURRENT                               |                         |       |                  |               | All offset DAC/supply combinations settings,<br>all gain settings are measure current = ( $I_{DUT} \times R_{SENSE} \times MI$ gain), unless otherwise noted. |

|                                               | 0.64                    |       | 0.04             | M             |                                                                                                                                                               |

| Differential Input Voltage Range <sup>1</sup> | -0.64                   |       | +0.64            | V             | Maximum voltage across $R_{SENSE}$ , MI gain = 20.                                                                                                            |

|                                               | -0.7                    |       | +0.7             | V             | Maximum voltage across $R_{SENSE}$ , MI gain = 10.                                                                                                            |

| Output Voltage Span <sup>1</sup>              |                         | 25    |                  | V             | Measure current block alone (internal node).                                                                                                                  |

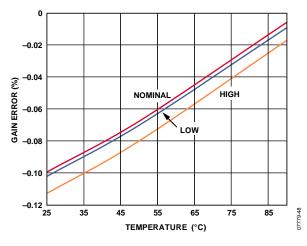

| Offset Error                                  | -1                      |       | +1               | % FSC         | At 0 A, MI gain = 20, MEASOUT gain = 1.                                                                                                                       |

| Offset Error Tempco <sup>1</sup>              |                         | -1    |                  | ppm of FSC/°C | Standard deviation = 13 ppm/°C.                                                                                                                               |

| Offset Error                                  | -1.5                    |       | +1.5             | % FSC         | At 0 A, MI gain = 10, MEASOUT gain = 1.                                                                                                                       |

| Offset Error Tempco <sup>1</sup>              |                         | -1    |                  | ppm of FSC/°C | Standard deviation = 13 ppm/°C.                                                                                                                               |

| Offset Error                                  | -1.5                    |       | +1.5             | % FSC         | At 0 A, MI gain = 20, MEASOUT gain = 0.2.                                                                                                                     |

| Offset Error Tempco <sup>1</sup>              |                         | 3     |                  | ppm of FSC/°C | Standard deviation = 13 ppm/°C.                                                                                                                               |

| Offset Error                                  | -3                      |       | +3               | % FSC         | At 0 A, MI gain = 10, MEASOUT gain = $0.2$ .                                                                                                                  |

| Offset Error Tempco <sup>1</sup>              | -                       | 8     |                  | ppm of FSC/°C | Standard deviation = 15 ppm/°C.                                                                                                                               |

| Gain Error                                    | -2                      | •     | +2               | % FSC         | Internal current ranges, all gain settings.                                                                                                                   |

| Gain Error <sup>1</sup>                       | -1                      |       | +1               | % FSC         | External current ranges, excluding R <sub>SENSE</sub> .                                                                                                       |

|                                               |                         | 20    | ΤI               |               |                                                                                                                                                               |

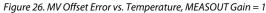

| Gain Error Tempco <sup>1</sup>                |                         | 20    |                  | ppm/°C        | Standard deviation = 5 ppm/°C.                                                                                                                                |

| MEASOUT Gain = 1                              | 0.01                    |       | . 0. 01          |               | All supply conditions.                                                                                                                                        |

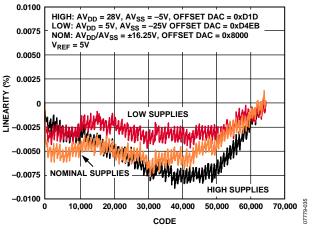

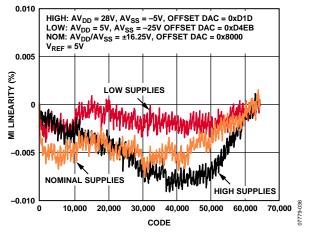

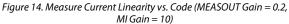

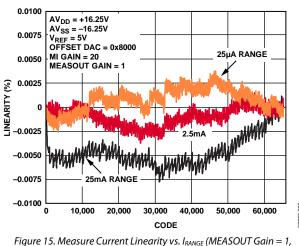

| Linearity Error                               | -0.01                   |       | +0.01            | % FSCR        | MI gain = 20 and 10.                                                                                                                                          |

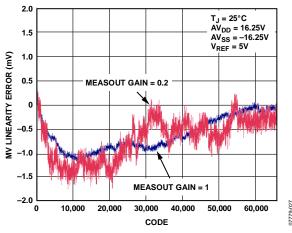

| MEASOUT Gain = 0.2                            |                         |       |                  |               | Nominal supply (±16.5 V, 0x8000 offset DAC).                                                                                                                  |

| Linearity Error                               | -0.06                   |       | +0.06            | % FSCR        | MI gain = 20.                                                                                                                                                 |

| Linearity Error                               | -0.05                   |       | +0.05            | % FSCR        | MI gain = 10.                                                                                                                                                 |

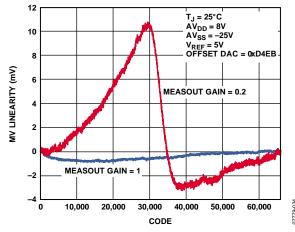

| MEASOUT Gain = 0.2                            |                         |       |                  |               | Low supply (–25 V/+8 V, 0xD4EB offset DAC).                                                                                                                   |

| Linearity Error                               | -0.125                  |       | +0.125           | % FSCR        | MI gain = 20.                                                                                                                                                 |

| Linearity Error                               | -0.175                  |       | +0.175           | % FSCR        | MI gain = 10.                                                                                                                                                 |

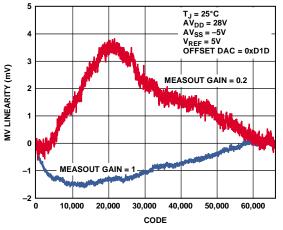

| MEASOUT Gain = 0.2                            |                         |       |                  |               | High supply (–5 V/+28 V, 0xD1D offset DAC).                                                                                                                   |

| Linearity Error                               | -0.0875                 |       | +0.0875          | % FSCR        | MI gain = 20.                                                                                                                                                 |

| Linearity Error                               | -0.1                    |       | +0.1             | % FSCR        | MI gain = 10.                                                                                                                                                 |

| Common-Mode Error                             | -0.005                  |       | +0.005           | %FSVR/V       | % of FS change at measure output per volts change in DUT voltage.                                                                                             |

| NSD <sup>1</sup>                              |                         | 900   |                  | nV/√Hz        | MI gain = 20, MEASOUT gain = 1, measured at<br>MEASOUT @ 1 kHz, inputs grounded.                                                                              |

|                                               |                         | 550   |                  | nV/√Hz        | MI gain = 10, MEASOUT gain = 1, measured at<br>MEASOUT @ 1 kHz, inputs grounded.                                                                              |

|                                               |                         | 170   |                  | nV/√Hz        | MI gain = 20, MEASOUT gain = 0.2, measured at MEASOUT @ 1 kHz, inputs grounded.                                                                               |

|                                               |                         | 110   |                  | nV/√Hz        | MI gain = 10, MEASOUT gain = 0.2, measured<br>at MEASOUT @ 1 kHz, inputs grounded.                                                                            |

| MEASURE VOLTAGE                               |                         |       |                  |               | MEASOUT Gain 1 and MEASOUT Gain 0.2.                                                                                                                          |

| Measure Voltage Range <sup>1</sup>            | AV <sub>ss</sub> + 2.75 |       | $AV_{DD} - 2.75$ | V             | All voltage ranges.                                                                                                                                           |

| Gain Error                                    | -0.1                    |       | +0.1             | % FS          |                                                                                                                                                               |

| Gain Error Tempco <sup>1</sup>                |                         | 3     |                  | ppm/°C        | Standard deviation = $2 \text{ ppm/°C}$ .                                                                                                                     |

| MEASOUT Gain = 1                              |                         |       |                  |               |                                                                                                                                                               |

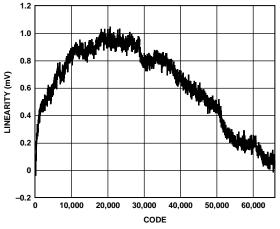

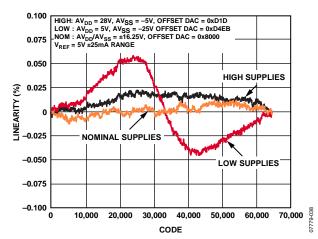

| Linearity Error                               | -2                      |       | +2               | mV            |                                                                                                                                                               |

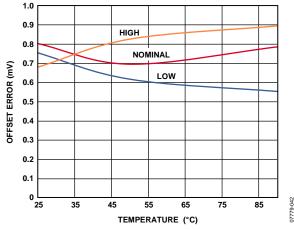

| Offset Error                                  | -12                     |       | +12              | mV            |                                                                                                                                                               |

| Parameter                                | Min   | Тур    | Мах    | Unit   | Test Conditions/Comments                                                                                                                                                     |

|------------------------------------------|-------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset Error Tempco <sup>1</sup>         |       | 2      |        | μV/°C  | Standard deviation = $12 \mu$ V/°C.                                                                                                                                          |

| NSD <sup>1</sup>                         |       | 100    |        | nV/√Hz | @ 1 kHz, at MEASOUT, inputs grounded.                                                                                                                                        |

| MEASOUT Gain = 0.2                       |       |        |        |        |                                                                                                                                                                              |

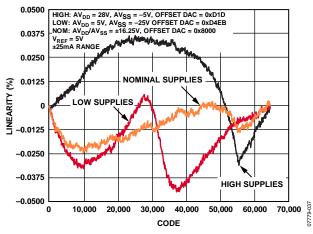

| Linearity Error                          | -5.5  |        | +5.5   | mV     | Referred to MV input, nominal supply (±16.5 V, 0x8000 offset DAC).                                                                                                           |

|                                          | -9    |        | +24    | mV     | Referred to MV input, low supply (-25 V/+8 V, 0xD4EB offset DAC).                                                                                                            |

|                                          | -4    |        | +13    | mV     | Referred to MV input, high supply (–5 V/+28 V, 0xD1D offset DAC).                                                                                                            |

| Offset Error                             | -30   |        | +20    | mV     | Referred to MV output.                                                                                                                                                       |

| Offset Error Tempco <sup>1</sup>         |       | 10     |        | μV/°C  | Standard deviation = $12 \mu V/^{\circ}C$ , referred to MV output.                                                                                                           |

| NSD <sup>1</sup>                         |       | 50     |        | nV/√Hz | @ 1 kHz, at MEASOUT, inputs grounded.                                                                                                                                        |

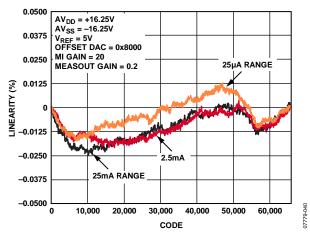

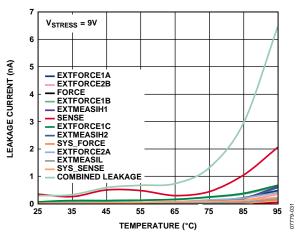

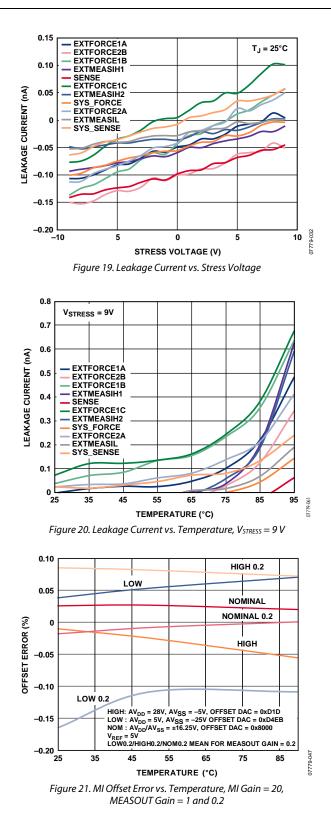

| COMBINED LEAKAGE                         |       |        |        |        | Includes SYS_SENSE, SYS_FORCE, EXTFORCE1,<br>EXTFORCE2, EXTMEASIH1, EXTMEASIH2,<br>EXTMEASIL, FORCE, and SENSE; measured with<br>PD = 1, SW-INH = 0 (power up and tristate). |

| Leakage Current                          | -37.5 |        | +37.5  | nA     |                                                                                                                                                                              |

|                                          | -30   |        | +30    | nA     | $T_{J} = 25^{\circ}C$ to 70°C.                                                                                                                                               |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.1   | ±0.4   | nA/°C  |                                                                                                                                                                              |

| SENSE INPUT                              |       |        |        |        |                                                                                                                                                                              |

| Leakage Current                          | -2.5  |        | +2.5   | nA     | Measured with $\overline{PD} = 1$ , $\overline{SW-INH} = 0$ (power-up and tristate).                                                                                         |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.01  |        | nA/°C  |                                                                                                                                                                              |

| Pin Capacitance <sup>1</sup>             |       | 10     |        | pF     |                                                                                                                                                                              |

| EXTMEASIH1, EXTMEASIH2, EXTMEASIL        |       |        |        |        |                                                                                                                                                                              |

| Leakage Current                          | -2.5  |        | +2.5   | nA     | Measured with $\overline{PD} = 1$ , $\overline{SW-INH} = 0$ (power-up and tristate).                                                                                         |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.01  |        | nA/°C  |                                                                                                                                                                              |

| Pin Capacitance <sup>1</sup>             |       | 5      |        | pF     |                                                                                                                                                                              |

| FORCE OUTPUT, FORCE                      |       | 5      |        | Pi     |                                                                                                                                                                              |

| Maximum Current Drive <sup>1</sup>       | -30   |        | +30    | mA     |                                                                                                                                                                              |

|                                          |       |        |        |        |                                                                                                                                                                              |

| Leakage Current                          | -10   |        | +10    | nA     | Measured with $\overline{PD} = 1$ , $\overline{SW-INH} = 0$ (power-up and tristate).                                                                                         |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.03  |        | nA/°C  |                                                                                                                                                                              |

| Pin Capacitance <sup>1</sup>             |       | 120    |        | pF     |                                                                                                                                                                              |

| EXTFORCE1 OUTPUTS                        |       |        |        |        |                                                                                                                                                                              |

| Maximum Current Drive <sup>1</sup>       | -1200 |        | +1200  | mA     | Set with external sense resistor, limited by headroom and power dissipation.                                                                                                 |

| Leakage Current                          | -7.5  |        | +7.5   | nA     | Measured with $\overline{PD} = 1$ , $\overline{SW-INH} = 0$ (power-up and tristate).                                                                                         |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.03  | ±0.06  | nA/°C  |                                                                                                                                                                              |

| Pin Capacitance <sup>1</sup>             |       | 275    |        | pF     |                                                                                                                                                                              |

| EXTFORCE2 OUTPUTS                        |       |        |        |        |                                                                                                                                                                              |

| Maximum Current Drive <sup>1</sup>       | -500  |        | +500   | mA     | Set with external sense resistor, limited by headroom and power dissipation.                                                                                                 |

| Leakage Current                          | -5    |        | +5     | nA     | Measured with $\overline{PD} = 1$ , $\overline{SW-INH} = 0$ (power-up and tristate).                                                                                         |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.02  | ±0.05  | nA/°C  |                                                                                                                                                                              |

| Pin Capacitance <sup>1</sup>             |       | 100    |        | pF     |                                                                                                                                                                              |

| SYS_SENSE                                |       |        |        |        |                                                                                                                                                                              |

| Voltage Range                            | AVss  |        | AVDD   | v      |                                                                                                                                                                              |

| Leakage Current                          | -2.5  |        | +2.5   | nA     | SYS_SENSE high-Z, force amplifier inhibited.                                                                                                                                 |

| -                                        | -2.5  | 10.005 |        |        | 515_SENSE High-2, force amplifier inhibited.                                                                                                                                 |

| Leakage Current Tempco <sup>1</sup>      |       | ±0.005 | ±0.025 | nA/°C  |                                                                                                                                                                              |

| Path On Resistance                       |       |        | 280    | Ω      | $AV_{DD} = 16.5 V, AV_{SS} = -16.5 V.$                                                                                                                                       |

| Pin Capacitance <sup>1</sup>             | 1     | 5      |        | pF     |                                                                                                                                                                              |

| SYS_FORCE                                |       |        |        |        |                                                                                                                                                                              |

| Voltage Range                            | AVss  |        | AVDD   | V      |                                                                                                                                                                              |

| Current Carrying Capability <sup>1</sup> | -25   |        | +25    | mA     |                                                                                                                                                                              |

| Parameter                                    | Min Typ                                                | )     | Max                            | Unit       | Test Conditions/Comments                                                                                                 |

|----------------------------------------------|--------------------------------------------------------|-------|--------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------|

| Leakage Current                              | -2.5                                                   |       | +2.5                           | nA         | SYS_FORCE high-Z, force amplifier inhibited.                                                                             |

| Leakage Current Tempco <sup>1</sup>          | ±0.0                                                   | 005   | ±0.025                         | nA/°C      |                                                                                                                          |

| Path On Resistance                           |                                                        |       | 35                             | Ω          | $AV_{DD} = 16.5 \text{ V}, AV_{SS} = -16.5 \text{ V}.$                                                                   |

| Pin Capacitance <sup>1</sup>                 | 5                                                      |       |                                | pF         |                                                                                                                          |

| SYS DUTGND                                   | 5                                                      |       |                                | pi         |                                                                                                                          |

| -                                            | A) /                                                   |       | A) /                           |            |                                                                                                                          |

| Voltage Range                                | AVss                                                   |       | AV <sub>DD</sub>               | V          |                                                                                                                          |

| Path On Resistance                           | 300                                                    |       | 400                            | Ω          | $AV_{DD} = 16.5 V, AV_{SS} = -16.5 V.$                                                                                   |

| CURRENT CLAMP                                |                                                        |       |                                |            |                                                                                                                          |

| Clamp Accuracy                               | Programmed<br>clamp value                              |       | Programmed clamp<br>value + 10 | % of FS    | MI gain = 20, with clamp separation of 2 V, and 1 V separation from AGND/0 A.                                            |

|                                              | Programmed<br>clamp value                              |       | Programmed clamp<br>value + 20 | % of FS    | MI gain = 10, with clamp separation of 2 V, and 1 V separation from AGND/0 A.                                            |

| VCLL to VCLH <sup>1</sup>                    | 2                                                      |       |                                | V          | 10% of FSCR (MI gain = 20), 20% of FSCR (MI gain = 10), restriction to prevent both clamps activating together.          |

| VCLL to 0 A <sup>1</sup>                     | 1                                                      |       |                                | V          | 5% of FSCR (MI gain = 20), 10% of FSCR (MI gain = 10), restriction to avoid impinging on FV before programmed level.     |

| VCLH to 0 A <sup>1</sup>                     | 1                                                      |       |                                | V          | 5% of FSCR (MI gain 20), 10% of FSCR (MI gain<br>= 10), restriction to avoid impinging on FV<br>before programmed level. |

| Clamp Activation Response Time <sup>1</sup>  | 20                                                     |       | 100                            | μs         | Measured from BUSY going low to visible clamping.                                                                        |

| Clamp Recovery <sup>1</sup>                  | 2                                                      |       | 5                              | μs         | Measured from BUSY going low to visible recovery.                                                                        |

| Alarm Delay <sup>1</sup>                     | 50                                                     |       |                                | μs         | Time for CLALM to flag.                                                                                                  |

| FORCE AMPLIFER                               |                                                        |       |                                | <b>P</b> 3 |                                                                                                                          |

|                                              |                                                        |       |                                |            |                                                                                                                          |

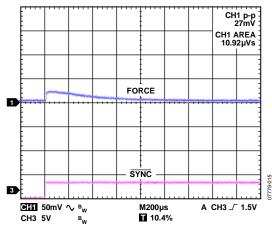

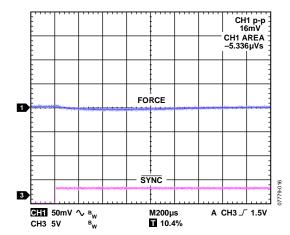

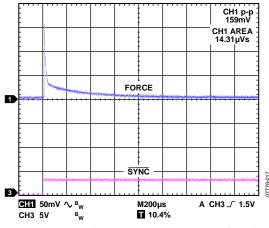

| Slew Rate <sup>1</sup>                       | 1                                                      |       |                                | V/µs       | Fastest slew rate, controlled via serial interfac                                                                        |

|                                              | 0.31                                                   | 12    |                                | V/µs       | Slowest slew rate, controlled via serial interface.                                                                      |

| Maximum Stable Load Capacitance <sup>1</sup> |                                                        |       | 160                            | μF         |                                                                                                                          |

| Voltage Overshoot/Undershoot <sup>1</sup>    |                                                        |       | 5                              | %          | Of programmed value (≥1 V).                                                                                              |

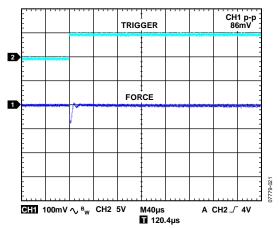

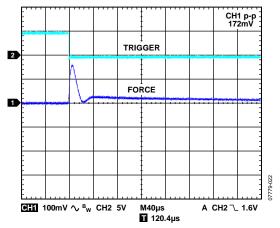

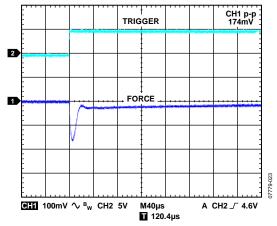

| SETTLING TIME (FORCE AMPLIFER)               | Compensation Register<br>380 nF, ESR 74 to 140 m       |       | 0x4880 (229 nF to              |            | To within 10 mV of programmed value.                                                                                     |

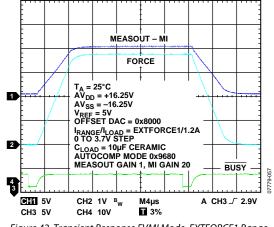

| FV (1200 mA EXTFORCE1 Range) <sup>1</sup>    | 16                                                     |       | 25                             | μs         | 3.7 V step, $R_{DUT} = 2.4 \Omega$ , $C_{DUT} = 0.22 \mu$ F, full dc load                                                |

| FV (900 mA EXTFORCE1 Range) <sup>1</sup>     | 18                                                     |       | 30                             | μs         | 8 V step, $R_{DUT} = 8.8 \Omega$ , $C_{DUT} = 0.22 \mu$ F, full dc load.                                                 |

| FV (500 mA EXTFORCE2 Range) <sup>1</sup>     | 34                                                     |       | 53                             | μs         | 15 V step, $R_{DUT} = 30 \Omega$ , $C_{DUT} = 0.22 \mu$ F, full dc load.                                                 |

| FV (300 mA EXTFORCE2 Range) <sup>1</sup>     | 25                                                     |       | 50                             | μs         | 10 V step, $R_{DUT}$ = 33.3 $\Omega$ , $C_{DUT}$ = 0.22 $\mu$ F, full dc load.                                           |

| FV (25 mA Range) <sup>1, 2</sup>             | 125                                                    |       | 180                            | μs         | 20 V step, $R_{DUT} = 800 \Omega$ , $C_{DUT} = 0.22 \mu$ F, full dc load                                                 |

| FV (2.5 mA Range) <sup>1, 2</sup>            | 300                                                    | )     | 500                            | μs         | 10 V step, $R_{DUT} = 4 k\Omega$ , $C_{DUT} = 0.22 \mu$ F, full dc load.                                                 |

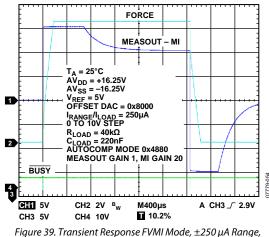

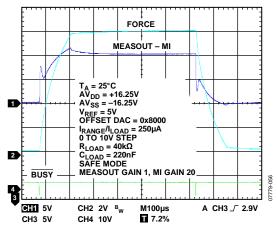

| FV (250 μA Range) <sup>1, 2</sup>            | 300                                                    | )     | 500                            | μs         | 10 V step, $R_{DUT} = 40 \text{ k}\Omega$ , $C_{DUT} = 0.22 \mu\text{F}$ , full dc load                                  |

| FV (25 μA Range) <sup>1, 2</sup>             | 400                                                    | )     | 600                            | μs         | 10 V step, $R_{DUT} = 400 \text{ k}\Omega$ , $C_{DUT} = 0.22 \mu$ F, full dc load.                                       |

| FV (5 μA Range) <sup>1, 2</sup>              | 20<br>Compensation Register<br>2.9 μF, ESR 74 to 140 m |       | 40<br>0x8880 (1.7 μF to        | μs         | 1 V step, $R_{DUT}$ = 200 k $\Omega$ , $C_{DUT}$ = 0.22 $\mu$ F, full dc load                                            |

| FV (180 mA EXTFORCE1 Range) <sup>1</sup>     | 2.5 μr, ESR / 4 το 140 m.<br>16                        | /     | 25                             | μs         | 3 V step, $C_{DUT} = 2.2 \ \mu$ F, full dc load.                                                                         |

| FV (100 mA EXTFORCE2 Range) <sup>1</sup>     | 60                                                     |       | 80                             |            | 8 V step, $C_{DUT} = 2.2 \ \mu$ F, full dc load.                                                                         |

| FV (100 MA EXTFORCE2 Range)                  | Compensation Register<br>13 μF, ESR 74 to 140 mΩ       |       |                                | μs         | $\delta$ v step, $C_{DUT} = 2.2 \ \mu$ r, full de load.                                                                  |

| FV (180 mA EXTFORCE1 Range) <sup>1</sup>     | 55                                                     |       | 70                             | μs         | 3 V step, $C_{DUT} = 10 \mu F$ , full dc load.                                                                           |

| FV (100 mA EXTFORCE2 Range) <sup>1</sup>     | 210<br>Compensation Register                           | r 1 = | 260<br>0xC880 (13 μF to        | μs         | 8 V step, $C_{DUT} = 10 \ \mu\text{F}$ , full dc load.                                                                   |

|                                              | 22 μF, ESR 74 to 140 mΩ                                | Ω)    |                                |            |                                                                                                                          |

| FV (180 mA EXTFORCE1 Range) <sup>1</sup>     | 65                                                     |       | 80                             | μs         | 3 V step, $C_{DUT} = 20 \ \mu$ F, full dc load.                                                                          |

| FV (100 mA EXTFORCE2 Range) <sup>1</sup>     | 310                                                    | )     | 370                            | μs         | 8 V step, $C_{DUT} = 20 \ \mu$ F, full dc load.                                                                          |

|                                              |                                                        |       |                                | 1          |                                                                                                                          |

| SETTLING TIME (FV, MEASURE<br>CURRENT)       | Compensation Register<br>380 nF, ESR 74 to 140 m       |       | 0x4880 (229 nF to              |            | To within 10 mV of programmed value.                                                                                     |

Rev. B | Page 8 of 60

| MI (500 mA EXTFORCE2 Range) <sup>1</sup> 69         95         μs         load.         Load. <thload.< th="">         Load.         <thload.< <="" th=""><th>omments</th><th>Test Conditions/Comments</th><th>Unit</th><th>Max</th><th>Тур</th><th>Min</th><th>Parameter</th></thload.<></thload.<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | omments                                                       | Test Conditions/Comments                                                                            | Unit    | Max               | Тур | Min  | Parameter                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------|-------------------|-----|------|------------------------------------------|

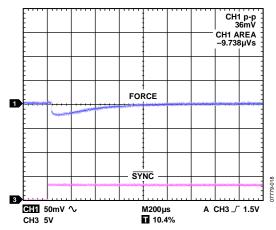

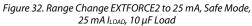

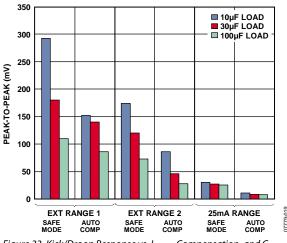

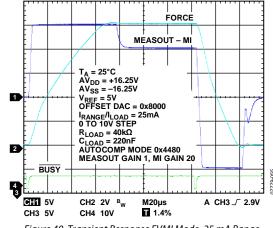

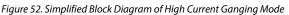

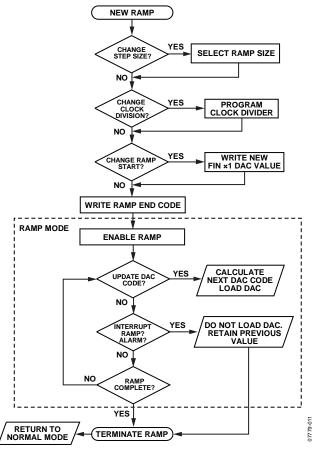

| MI (500 mA EXTFORCE2 Range) <sup>1</sup> 69         95         μs         15 ¥ ters (her = 30.3.0, Car<br>load,<br>mode, Rer= 30.3.0, Car<br>load, Rer= 30.3.0, Car<br>load,<br>MI (25 mA Range) <sup>1,2</sup> MI (25 mA Range) <sup>1,2</sup> 650         μs         201 ¥tep, Rer= 30.3, 0, Car<br>load,<br>mode, Rer= 30.3, 0, Car<br>load,<br>MI (25 mA Range) <sup>1,2</sup> MI Buffer Alone <sup>1</sup> 10         15         μs         201 ¥tep, Rer= 40.0, Car<br>load,<br>MI (25 mA Range) <sup>1,2</sup> MI Buffer Alone <sup>1</sup> 10         15         μs         37 V step, Rer= 40.0, Car<br>load,<br>MV (1200 mA Range) <sup>1</sup> MV (120 mA Range) <sup>1</sup> 16         μs         37 V step, Rer= 24.0, Car<br>load,<br>MV (300 mA Range) <sup>1</sup> MV (1500 mA Range) <sup>1</sup> 16         μs         37 V step, Rer= 30.0, Car<br>load,<br>MV (300 mA Range) <sup>1.2</sup> MV (300 mA Range) <sup>1.2</sup> 34         μs         10 V step, Rer= 30.0, Car<br>load,<br>MV (25 mA Range) <sup>1.2</sup> MV (25 mA Range) <sup>1.2</sup> 300         500         μs         10 V step, Rer= 30.0, Car<br>load,<br>MV (25 mA Range) <sup>1.2</sup> VV (25 µA Range) <sup>1.2</sup> 300         500         μs         10 V step, Rer= 30.0, Car<br>load,<br>MV (25 µA Range) <sup>1.2</sup> VF (100 mA EXTFORCE1 Range) <sup>1.2</sup> 300         500         μs         10 V step, Rer= 30.1, Car<br>load,<br>MV (25 µA Range) <sup>1.2</sup> VF (100 mA EXTFORCE1 Range) <sup>1.2</sup> 300         500         μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\Omega$ , C <sub>DUT</sub> = 0.22 µF, full dc                | 8 V step, $R_{DUT} = 8.8 \Omega$ , $C_{DUT} = 0.22 \mu$                                             | μs      | 42                | 32  |      | MI (900 mA EXTFORCE1 Range) <sup>1</sup> |