# Wireless Components

FM Car Radio IC with PLL TUA 4401K V 2.1

Specification 17.02.00

| Revision History: Current Version: 02.00 |                                 |                                              |  |  |

|------------------------------------------|---------------------------------|----------------------------------------------|--|--|

| Previous Vers                            | ion:Data Sheet                  | 23.09.1999                                   |  |  |

| Page<br>(in previous<br>Version)         | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |  |

| 3-7                                      | 3-7                             | Functional description pin 41 corrected      |  |  |

| 3-11                                     | 3-11                            | Functional description pin 41 corrected      |  |  |

| 5-3                                      | 5-3                             | Sequence tests 310 to 317 changed (Item)     |  |  |

| 5-5                                      | 5-5                             | Values attack current changed                |  |  |

| 5-5                                      | 5-5                             | Values recovery current changed              |  |  |

| 5-5                                      | 5-5                             | Values detector characteristic changed       |  |  |

ABM®, AOP®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®-2, SICOFI®-4, SICOFI®-4, SICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

#### Edition 03.99

Published by Infineon Technologies AG i. Gr., SC, Balanstraße 73, 81541 München

© Infineon Technologies AG i. Gr. 08.03.00.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 1. 2Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

**Productinfo**

# **Productinfo**

#### **General Description**

The TUA 4401K is the first Infineon Carradio IC using BICMOS technology.

The combination of an analog FM receiver circuit and a digital PLL synthesizer on the same chip reduces the over all pin count in comparison to two separate IC's and in addition the number of necessary external components. This gives the flexibility both for high performance and low cost applications.

The recommended applications for this device are FM only carradios and background receivers, capable for all world standards.

#### Package

#### **Features**

- Double balanced RF mixer with low noise figure, high IP3 and wide dynamic range

- Strictly symmetrical RF circuitry

- IF amplifier with adjustable gain

- Double frequency 1st LO option

- 7 stage limiter amplifier with dB linear fieldstrength output

- Low distortion coincidence demodulator

- Multipath detector with analog output

- CMOS PLL-Synthesizer

- Resolution between 100 kHz and 6.25kHz

- Search tuning stop with IF counter and Fieldstrength/Multipath evaluation

- ADC's for fieldstr. and multipath detector

- I<sup>2</sup>C Bus operation

## **Applications**

FM only car radio receiver, background receiver

## **Ordering Information**

| Туре      | Ordering Code | Package |

|-----------|---------------|---------|

| TUA 4401K |               | MQFP-44 |

# Table of Contents

| 1 | Table of Contents |                                       |   | 1-1        |

|---|-------------------|---------------------------------------|---|------------|

| 2 | Produ             | uct Description                       |   | 2-1        |

|   | 2.1               | General Description                   |   | 2-2        |

|   | 2.2               | Applications                          |   | 2-3        |

|   | 2.3               | Features                              |   | 2-3        |

|   | 2.4               | Package Outlines                      |   | 2-4        |

| 3 | Funct             | tional Description                    |   | 3-1        |

|   | 3.1               | Pin Configuration                     |   | 3-2        |

|   | 3.2               | Block Diagram                         |   | 3-12       |

|   | 3.3               | Functional Block Diagram              |   | 3-13       |

|   | 3.4               | Circuit Description                   |   | 3-14       |

| 4 | Appli             | cations                               |   | 4-1        |

|   | 4.1               | Application and Circuits              |   | 4-2        |

| 5 | Refer             | ence                                  |   | 5-1        |

|   | 5.1               | Electrical Data                       |   | 5-2        |

|   | 5.1.1             | Absolute Maximum Range                | 9 | 5-2<br>5-2 |

|   | 5.1.2<br>5.1.3    | Operating Range AC/DC Characteristics |   | 5-2<br>5-3 |

|   | 5.2               | Phase detector outputs                |   | 5-7        |

|   | 5.3               | Bus Interface                         |   | 5-8        |

|   | 5.4               | I2C Bus Timing                        |   | 5-13       |

| Con | Contents of this Chapter |  |  |  |  |  |

|-----|--------------------------|--|--|--|--|--|

| 2.1 | General Description      |  |  |  |  |  |

| 2.2 | Applications             |  |  |  |  |  |

| 2.3 | Features                 |  |  |  |  |  |

| 2.4 | Package Outlines         |  |  |  |  |  |

# 2.1 General Description

The TUA 4401K is the first Infineon Carradio IC using BICMOS technology. The combination of an analog FM receiver circuit and a digital PLL synthesizer on the same chip reduces the over all pin count in comparison to two separate IC's and in addition the number of necessary external components. This gives the flexibility both for high performance and low cost applications.

The recommended applications for this device are FM only carradios and background receivers, capable for all world standards.

#### TUA 4401K features:

#### Frontend

- High level, high impedance mixer input with improved dynamic range

- High input / output 3rd order intercept point

- Integrated prestage AGC generation and control for PIN diodes and MOS tetrode

- Bus controlled AGC threshold

- 2 pin 1st local oscillator with improved low phase noise, internally coupled to PLL. Double frequency operation possible

- Strictly symmetrical RF parts

- PLL with fast acquisition mode

- Resolution 100 kHz, 50 kHz, 25 kHz, 12,5 kHz, 10 kHz and 6.25 kHz

- High running (61.5 MHz) crystal oscillator to avoid interference with bus controlled adjustment

#### IF amplification, demodulation and STS

- Low noise IF amplifier

- Gain adjust with DC control voltage or serial bus possible

- 7 stage IF limiter with extended fieldstrength range suitable for the IF frequency range of 10.7 MHz ... 21.4 MHz

- Fieldstrength DC output and ADC output available

- Low distortion coincidence demodulator (using short loop AFC principle) with MPX output

- Wideband multipath detector with analog output and ADC output

- IF counter for search tuning stop with selectable IF center frequency, window width and programmable thresholds for fieldstrength and multipath evaluation

- STS informations -in window-,-below-,-beyond- available

#### I<sup>2</sup>C Bus

- I<sup>2</sup>C bus (2 wire, fast mode device with 400 kbit/s) operation possible

- Bus interface with low threshold voltage Schmitt Trigger inputs for interfacing 3V or 5V microprocessors

# 2.2 Applications

■ FM only car radio receiver, background receiver

## 2.3 Features

- Double balanced RF mixer with low noise figure, high IP3 and wide dynamic range

- Strictly symmetrical RF circuitry

- Double frequency 1st LO option

- IF amplifier with adjustable gain

- 7 stage limiter amplifier with dB linear fieldstrength output

- Low distortion coincidence demodulator

- Multipath detector with analog output

- CMOS PLL-Synthesizer

- Resolution between 100 kHz and 6.25kHz

- Search tuning stop with IF counter and Fieldstrength/Multipath evaluation

- ADC's for fieldstr. and multipath detector

- I<sup>2</sup>C Bus operation

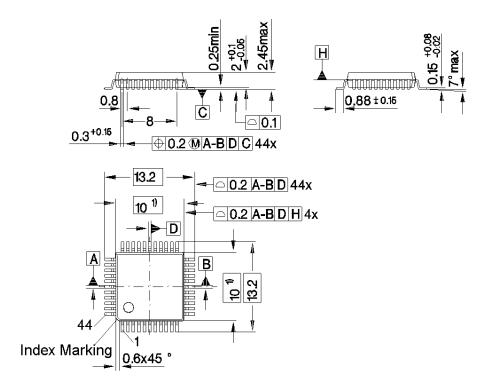

# 2.4 Package Outlines

MQFP 44

| Contents of this Chapter |                          |      |  |

|--------------------------|--------------------------|------|--|

| 3.1                      | Pin Configuration        | 3-2  |  |

| 3.2                      | Block Diagram            | 3-12 |  |

| 3.3                      | Functional Block Diagram | 3-13 |  |

| 3.4                      | Circuit Description      | 3-14 |  |

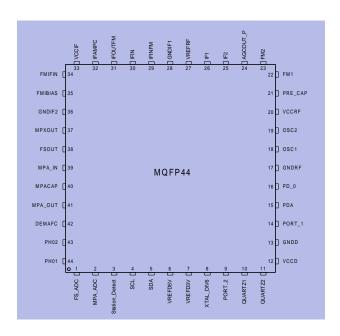

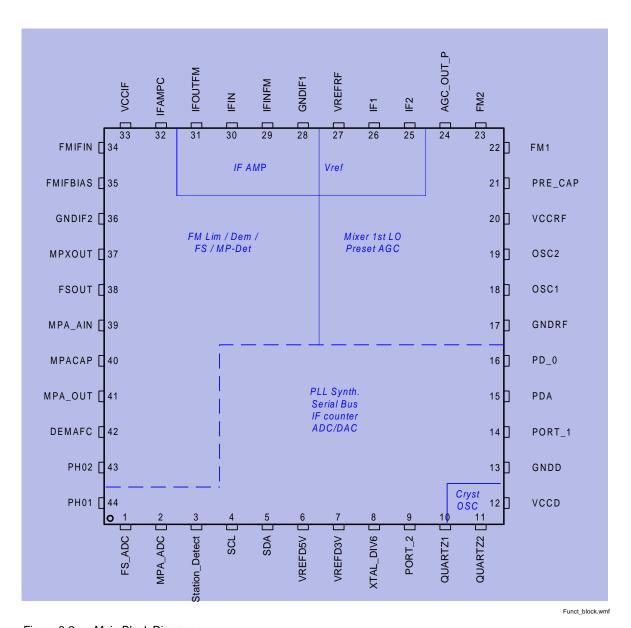

# 3.1 Pin Configuration

Pin\_config.wmf

Figure 3-1 IC Pin Configuration

| Table 3-1 | Table 3-1 Pin Configuration |                          |                                                             |  |  |  |

|-----------|-----------------------------|--------------------------|-------------------------------------------------------------|--|--|--|

| Pin No.   | Symbol                      | Equivalent I/O-Schematic | Function                                                    |  |  |  |

| 2         | FS_ADC  MPA_ADC             | 1                        | 1: ADC input fieldstrength  2: ADC input multipath detector |  |  |  |

|         | Table 3-1 Pin Configuration (continued) |                          |                                                       |  |

|---------|-----------------------------------------|--------------------------|-------------------------------------------------------|--|

| Pin No. | Symbol                                  | Equivalent I/O-Schematic | Function                                              |  |

| 3       | Station_Detect                          | GNDD 3                   | 3:<br>IF counter output station<br>detector           |  |

| 4       | SCL                                     | 4 330 +5V GNDD           | 4:<br>I <sup>2</sup> C bus clock input                |  |

| 5       | SDA                                     | 5 330 GNDD               | 5:<br>I <sup>2</sup> C bus data in/output             |  |

| 6       | VREFD5V                                 |                          | 6:<br>Reference voltage digital<br>section (5V)       |  |

| 7       | VREFD3V                                 |                          | 7:<br>Reference voltage digital<br>section (3V)       |  |

| 8       | XTAL_DIV6                               | 2k 200fF GNDD            | 8:<br>Crystal oscillator auxiliary output (10.25 MHz) |  |

| Table 3-1 Pin Configuration (continued) |         |                                          |                                                                  |  |

|-----------------------------------------|---------|------------------------------------------|------------------------------------------------------------------|--|

| Pin No.                                 | Symbol  | Equivalent I/O-Schematic                 | Function                                                         |  |

| 9                                       | PORT_2  | 330<br>+ 5 V 9<br>GNDD                   | 9:<br>Switch port output 2(open<br>drain)                        |  |

| 10                                      | QUARTZ1 | 10 + V + V + V + V + V + V + V + V + V + | 10:<br>Reference oscillator input<br>/ Crystal                   |  |

| 11                                      | QUARTZ2 |                                          | Reference oscillator input / Crystal                             |  |

| 12                                      | VCCD    |                                          | 12: Positive power supply voltage for serial bus and synthesizer |  |

| 13                                      | GNDD    |                                          | 13:<br>Ground for serial bus and<br>synthesizer                  |  |

| 14                                      | PORT_1  | + 5 V 14  GNDD                           | 14:<br>Switch port output 1<br>(open drain)                      |  |

|                                         |         |                                          |                                                                  |  |

| Table 3- | Table 3-1 Pin Configuration (continued) |                          |                                                                                |  |

|----------|-----------------------------------------|--------------------------|--------------------------------------------------------------------------------|--|

| Pin No.  | Symbol                                  | Equivalent I/O-Schematic | Function                                                                       |  |

| 15       | PDA                                     | PD GNDD                  | 15:<br>PLL phasedetector output<br>analog (Tuningvoltage)                      |  |

| 16       | PD_0                                    | +5 V 16 NC               | 16:<br>PLL chargepump output<br>(Phase detector tristate<br>chargepump output) |  |

| 17       | GNDRF                                   |                          | 17:<br>Ground for RF part                                                      |  |

| Table 3- | Table 3-1 Pin Configuration (continued) |                          |                                                                               |  |

|----------|-----------------------------------------|--------------------------|-------------------------------------------------------------------------------|--|

| Pin No.  | Symbol                                  | Equivalent I/O-Schematic | Function                                                                      |  |

| 18       | OSC1                                    | 18 + V 0                 | 18:<br>1st local oscillator circuit<br>19:<br>1st local oscillator circuit    |  |

| 20       | VCCRF                                   |                          | 20:<br>Positive power supply<br>voltage for RF part                           |  |

| 21       | PRE_CAP                                 | 21<br>6,4V               | 21:<br>Prestage AGC time constant capacitor; output for<br>MOS tetrode gate 2 |  |

| Table 3- | Table 3-1 Pin Configuration (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |  |

|----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| Pin No.  | Symbol                                  | Equivalent I/O-Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Function                                                                 |  |

| 22       | FM1                                     | 25 26 1<br>26 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22:<br>FM 1st mixer symmetrical<br>input                                 |  |

| 23       | FM2                                     | 22<br>23<br><del>S</del> ON DE CONTROL | 23:<br>FM 1st mixer symmetrical<br>input                                 |  |

| 24       | AGCOUT_P                                | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24:<br>Prestage AGC current<br>output for PIN diode nor-<br>mal polarity |  |

| Table 3- | Table 3-1 Pin Configuration (continued) |                                                                |                                                 |  |  |

|----------|-----------------------------------------|----------------------------------------------------------------|-------------------------------------------------|--|--|

| Pin No.  | Symbol                                  | Equivalent I/O-Schematic                                       | Function                                        |  |  |

| 25       | IF2                                     | 25 26 26 22 22 22 22 25 26 26 26 26 26 26 26 26 26 26 26 26 26 | 25:<br>1st mixer output (open<br>collector)     |  |  |

| 26       | IF1                                     | 23                                                             | 26:<br>1st mixer output (open<br>collector)     |  |  |

| 27       | VREFRF                                  |                                                                | 27:<br>Reference voltage RF<br>section (4.8V)   |  |  |

| 28       | GNDIF1                                  |                                                                | 28:<br>Ground for IF amplifier                  |  |  |

| 29       | IFINFM                                  | 30 + V                                                         | 29:<br>10.7 MHz IF amplifier<br>input           |  |  |

| 30       | IFIN                                    | 29<br>3,8V +                                                   | 30:<br>10.7 MHz IF amplifier<br>operation point |  |  |

|         |          | ation (continued)                          |                                                                                |

|---------|----------|--------------------------------------------|--------------------------------------------------------------------------------|

| Pin No. | Symbol   | Equivalent I/O-Schematic                   | Function                                                                       |

| 31      | IFOUTFM  | 31 + V • • • • • • • • • • • • • • • • • • | 31:<br>10.7 MHz IF amplifier output                                            |

| 32      | IFAMPC   | 32<br>+ V                                  | 32:<br>10.7 MHz IF amplifier DC<br>gain control adjust block-<br>ing capacitor |

| 33      | VCCIF    |                                            | 33:<br>Positive power supply<br>voltage for IF amplifier                       |

| 34      | FMIFIN   | 35 + V                                     | 34:<br>FM limiter input                                                        |

| 35      | FMIFBIAS | 5,5 V + 5                                  | 35:<br>FM limiter input bias<br>decoupling capacitor                           |

| 36      | GNDIF2   |                                            | 36:<br>Ground for limiter ampli-<br>fier                                       |

| Table 3-1 | l Pin Configura | ation (continued)        |                                 |

|-----------|-----------------|--------------------------|---------------------------------|

| Pin No.   | Symbol          | Equivalent I/O-Schematic | Function                        |

| 37        | MPXOUT          | 37<br>37                 | 37:<br>FM MPX signal output     |

| 38        | FSOUT           | 38 NC + V                | 38:<br>Fieldstrength output     |

| 39        | MPA_IN          | 39 + V 9 86k             | 39:<br>Multipath detector input |

| Table 3- | 1 Pin Configura | ation (continued)                       |                                                  |

|----------|-----------------|-----------------------------------------|--------------------------------------------------|

| Pin No.  | Symbol          | Equivalent I/O-Schematic                | Function                                         |

| 40       | MPACAP          | 4 7 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 | 40:<br>Multipath detector rectifier<br>capacitor |

| 41       | MPA_OUT         | 9+ V<br>41                              | 41:<br>Multipath detector output                 |

| 42       | DEMAFC          | 76k 42                                  | 42:<br>Demodulator AFC block-<br>ing capacitor   |

| 43       | PH02            | + V                                     | 43:<br>Demodulator circuit                       |

| 44       | PH01            | 43/44<br>+<br>-<br>4,8V                 | 44:<br>Demodulator circuit                       |

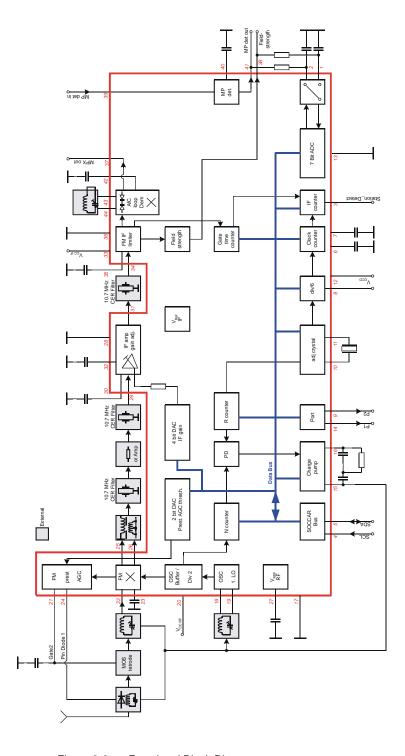

# 3.2 Block Diagram

Figure 3-2 Main Block Diagram

Wireless Components 3 - 12 Specification, 17.02.00

# 3.3 Functional Block Diagram

Funct\_block.wmf

Figure 3-3 Functional Block Diagram

# 3.4 Circuit Description

The TUA 4401K is a one chip FM car radio system consisting of RF frontend, gain adjustable IF amplifier, FM-IF limiter amplifier, demodulator, PLL synthesizer, IF counter for STS and ADC's for fieldstrength and multipath detector. The serial bus is a  $\rm I^2C$  type.

#### 1. FM frontend

The frontend consists of a two pin varactor tuned oscillator, a double balanced mixer and a prestage AGC control circuit. The mixer has an improved intermodulation behaviour and converts the RF signal to the 10,7 MHz IF range . Two inputs allow both symmetrical and unsymmetrical operation. The integrated AGC stage for prestage control drives MOSFETS as well as PIN diodes a with cur- rent driver. The AGC threshold can be set with a serial bus controlled 2 Bit DAC. For background receiver application the oscillator is able run at double frequency, a subsequent frequency divider by 2 is activated by serial bus to provide the correct mixer frequency.

#### 2. FM IF amplifier

After the mixer an IF amplifier is present for IF post amplification. Input and output impedance are both 330 Ohms for matching with ceramic filters. For adjusting the over all gain the IF amplifier gain can be adjusted with a serial bus controlled 4 Bit DAC.

#### 3. FM limiter and demodulator

The FM IF amplifier includes a seven stage capacitive coupled limiter amplifier and a fieldstrength generator with high linearity and increased dynamic range. The coincidence demodulator has an additional AFC short loop circuit with integrated varactor diode in parallel to the external tank circuit to improve the distortion bahaviour in case of detuning.

#### 4. Multipath detector

A wideband multipath detector with analog output is available.

- 5. A/D converter for fieldstrength and multipath detector The 7 bit A/D converter has two input channels and works as successive approximation converter. The conversion time for both input signals is  $t=32~\mu s$ . The 7-bit digital-words from both channels (14 bit) are read out together via bus into two bytes with the read subaddress 82H. The input voltage range for both channels is 0...VREFD5V.

- 6. IF counter and multipath/fieldstrength evaluation for STS FM center frequencies ar available in two ranges set by bit D7 in subaddress 05H. For D7=1 the range of centerfrequency is 20.800 MHz...22.3875 MHz in 128 steps (12.5 kHz per step). For D7=0 the range of centerfrequency is 10.400 MHz...11.1937 MHz in 128 steps (6.25 kHz per step). The gate time is adjustable in 8 steps from 320us...40.96ms and the tolerance of the accepted count value, the window is adjustable in 5 steps from +/- (6.25kHz...100kHz) for D7=0 in sub-address 05H and

+/- (12.5 kHz...200 kHz) for D7=1 in subaddress 05H. The results IF\_CENT and IF\_WINDOW are read out via bus (read-subaddress 82H&83H) or pin Station Detect.

If the IF frequency is into the preselected window, Station\_Detect goes from high to low level. If the IF frequency is outside the preselected window, Station\_Detect is high. The bit IF\_WINDOW is a hint IF-frequency that is to low (IF\_WINDOW=high) or is to high (IF\_WINDOW=low). In addition to the frequency measurement, thresholds for multipath and field-

strength voltages can be programmed via bus (subaddress 0BH).

Station\_Detect will only go to low level in case of field-strength and multipath voltages are beyond the thresholds and the frequency is inside the window. When setting the thresholds to zero multipath and fieldstrength evaluation is disabled.

#### 7. Crystal oscillator

A master crystal oscillator provides all necessary clock frequencies for the whole IC. A 61.5 MHz crystal is used in 3rd harmonic mode.

The oscillator frequency can fine tuned with a serial bus controlled 4 bit D/A converter.

The crystal frequency is used as reference frequency for the PLL oscillator and IF counter. It is also used as clock for the ADC's. Finally the crystal frequency divided by 6 (10.25 MHz) is available at a pin as low pass filtered voltage, it can be disabled with the serial bus.

#### 8. Output ports

PORT\_1 / 2 are NMOS Open drain outputs.

#### 9. I<sup>2</sup>C Bus

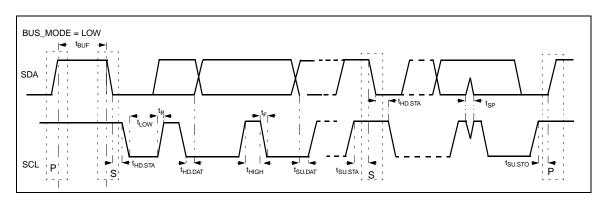

The TUA4401K supports the I $^2$ C bus protocol (2 wire). All bus pins ( SCL, SDA) are Schmitt triggered input buffer for 3V or 5V  $\mu$ C.

The bit stream begins with the most significant bit (MSB), is shifted in (write mode) on the low to high transition of CLK and is shifted out (read mode) on the high to low transition of CLK

#### I<sup>2</sup>C bus mode:

Data Transition:

Data transition on the pin SDA must only occur when the clock SCL is low. SDA transitions while SCL is high will be interpreted as start or stop condition.

#### Start Condition (STA):

A start condition is defined by a high to low transition of the SDA line while SCL is at a stable high level. This start condition must precede any command and initiate a data transfer onto the bus.

#### Stop Condition (STO):

A stop condition is defined by a low to high transition of the SDA while the SCL line is at a stable high level. This condition terminate the communication between the devices and forces the bus interface into the initial conditions.

#### Acknowledge (ACK):

Indicates a successful data transfer. The transmitter will release the bus after sending 8 bit of data. During the 9th clock cycle the receiver will pull the SDA line to low level to indicate it has receive the 8 bits of data correctly.

#### Data Transfer Write Mode:

To start the communication, the bus master must initiate a start condition, followed by the 8bit chip address (write). The chip address for the TUA 4401 is fixed as "1100110" (MSB at first). The last bit (LSB=A0) of the chip address byte defines the type of operation to be performed:

A0=1, a read operation is selected and A0=0, a write operation is selected. After this comparison the TUA 4401 will generate an ACK.

After this device addressing the desired subaddress byte and data bytes must be followed. The subaddresses determines which one of the 9 data bytes (00H...07H, 0BH) is transmitted first. At the end of data transition the master must be generate the stop condition.

#### Data Transfer Read Mode:

To start the communication in the read mode, the bus master must initiate a start condition, followed by the 8bit chip address (write: A0=0), followed by the sub address read (82H/83H), followed by the chip address (read: A0=1). After that procedure the 16bit/8bit data register 82H/83H is read out. After the first 8 bit read out, the uP mandatory send LOW during the ACK-clock. After the second 8 bit read out the uP mandatory send HIGH during the ACK-clock. At the end of data transition the master must be generate the stop condition.

#### 10.PLL Synthesizer

### R / N Counter

The TUA 4401K has 2 identical 16bit counter for R and N path. Input frequency for the R-counter is the buffered XTAL-frequency (61.5MHz). Tuning steps can be selected by the 16bit R-counter from  $f_R$ = 6.25kHz...100kHz. Input frequency for the N-counter is the buffered LO-frequency (in FM mode 98.2MHz...118.7MHz).

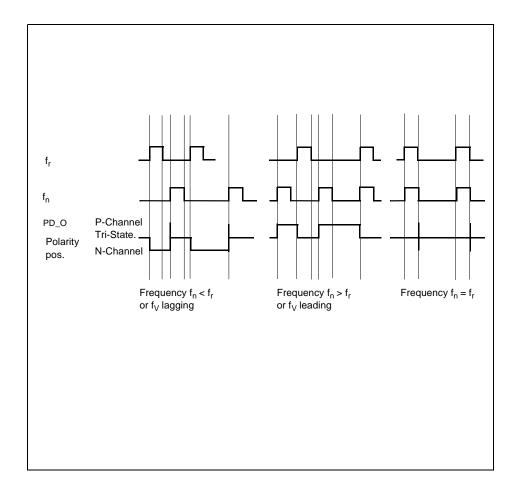

#### Three State Phase Comparator

The phase comparator generates a phase error signal according to phase difference between  $f_R$  (R counter output) and  $f_N$  (N counter output). This phase error signal drives the charge pump current generator.

#### Charge Pump

The charge pump generates signed pulses of current. 4 current values are available.

#### Loop Amp

The integrated rail to rail loop amplifier allows an active loop filter design with external components.

Two modes are available with status bit D11: high speed and normal mode.

# 4 Applications

| Cont | ents of this Chapter     |      |      |    |

|------|--------------------------|------|------|----|

| .1   | Application and Circuits | <br> | <br> | 4- |

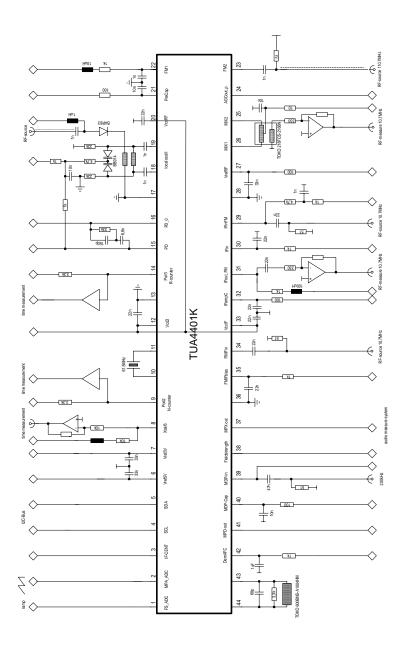

# 4.1 Application and Circuits

■ FM only car radio receiver, background receiver

4401K\_Test\_circ.wmf

Figure 4-1 Test Circuit

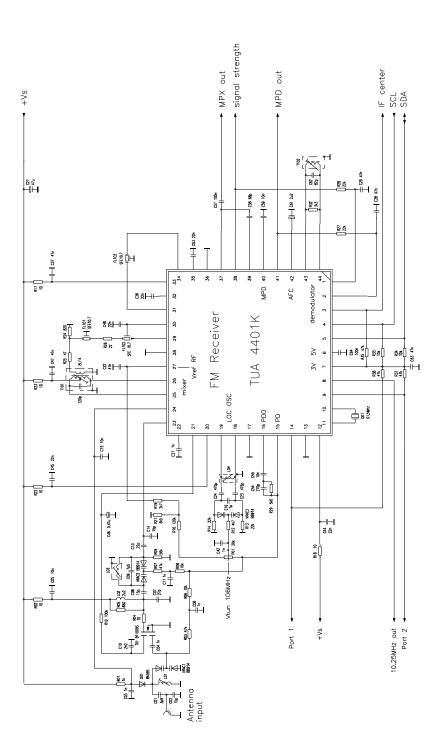

# **Applications**

4401K\_SPEC.eps

Figure 4-2 Application Circuit

| Cont           | ents of this Chapter                                                                          |

|----------------|-----------------------------------------------------------------------------------------------|

| 5.1.1<br>5.1.2 | Electrical Data. 5-2 Absolute Maximum Range 5-2 Operating Range 5-2 AC/DC Characteristics 5-3 |

| 5.2            | Phase detector outputs5-7                                                                     |

| 5.3            | Bus Interface5-8                                                                              |

| 5.4            | I2C Bus Timing                                                                                |

# 5.1 Electrical Data

# 5.1.1 Absolute Maximum Range

The maximal ratings may not be exceeded under any circumstances, not even momentary and individual, as permanent damage to the IC will result.

| Table 5-1 Absolute Maximum Range                                  |                   |       |        |      |  |  |  |  |  |

|-------------------------------------------------------------------|-------------------|-------|--------|------|--|--|--|--|--|

| Parameter                                                         | Symbol            | Limit | Values | Unit |  |  |  |  |  |

|                                                                   |                   | min   |        |      |  |  |  |  |  |

|                                                                   |                   |       |        |      |  |  |  |  |  |

| ESD-Protection all bipolar pins HBM ( R=1.5k $\Omega$ , C=100pF ) | V <sub>ESD</sub>  | - 1   | 1      | kV   |  |  |  |  |  |

| ESD-Protection all CMOS pins HBM ( R=1.5k $\Omega$ , C=100pF )    | V <sub>ESD</sub>  | -1    | 1      | kV   |  |  |  |  |  |

| Total power dissipation                                           | P <sub>tot</sub>  |       | 900    | mW   |  |  |  |  |  |

| Ambient temperature                                               | T <sub>A</sub>    | - 40  | 85     | °C   |  |  |  |  |  |

| Junction temperature                                              | Tj                |       | 150    | °C   |  |  |  |  |  |

| Storage temperature                                               | T <sub>stg</sub>  | - 40  | 125    | °C   |  |  |  |  |  |

| Thermal resistance P-MQFP-44 (sys-air)                            | T <sub>thSA</sub> |       | 65     | K/W  |  |  |  |  |  |

All values are referred to ground (pin), unless stated otherwise.

All currents are designated according to the source and sink principle, i.e. if the device pin is to be regarded as a sink (the current flows into the stated pin to internal ground), it has a negative sign, and if it is a source (the current flows from Vs across the designated pin), it has a positive sign.

# 5.1.2 Operating Range

Within the operational range the IC operates as described in the circuit description.

The AC / DC characteristic limits are not guaranteed.

| Table 5-2 Operating Ratings |                  |              |     |      |                 |   |      |  |  |  |

|-----------------------------|------------------|--------------|-----|------|-----------------|---|------|--|--|--|

| Parameter                   | Symbol           | Limit Values |     | Unit | Test Conditions | L | Item |  |  |  |

|                             |                  | min          | max |      |                 |   |      |  |  |  |

|                             |                  |              |     |      |                 |   |      |  |  |  |

| Supply voltage              | V <sub>VCC</sub> | 8            | 9   | V    |                 |   |      |  |  |  |

| Current consumption         | I <sub>vcc</sub> |              | 111 | mA   |                 |   |      |  |  |  |

| Ambient temperature         | T <sub>A</sub>   | - 40         | 85  | °C   |                 |   |      |  |  |  |

# 5.1.3 AC/DC Characteristics

AC/DC characteristics involve the spread of values guaranteed in the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

| Table 5-3 AC/DC Characteris      | tics with T <sub>A</sub> 25 | °C, V <sub>VC</sub> | <sub>C</sub> = 8.5 \ | /   |      |                             |   |            |

|----------------------------------|-----------------------------|---------------------|----------------------|-----|------|-----------------------------|---|------------|

|                                  | Symbol                      | Li                  | mit Valu             | es  | Unit | Test Conditions             | L | Item       |

|                                  |                             | min                 | typ                  | max |      |                             |   |            |

| Power Supply                     |                             |                     |                      |     |      |                             |   |            |

| Total current consumption        | I <sub>VCC</sub>            |                     | 85                   | 111 | mA   |                             |   |            |

| 1st local oscillator             |                             |                     |                      |     |      |                             |   |            |

| Frequency range                  | f <sub>1st LO</sub>         | 50                  |                      | 250 | MHz  |                             |   |            |

| Frequency range                  | f <sub>1st LO</sub>         | 50                  |                      | 150 | MHz  | Q factor of coil > 90       |   |            |

| Frequency range                  | f <sub>1st LO</sub>         | 160                 |                      | 250 | MHz  | coil tbf; see<br>SUB06h     |   |            |

| Negative input impedance         | Z <sub>18-19</sub>          |                     | - 1000               |     | Ω    | f = 100 MHz                 | L |            |

| RF mixer                         |                             |                     |                      |     |      |                             |   |            |

| Mixer current                    | lmix                        | 11                  | 14                   | 17  | mA   |                             |   | 101        |

| Input frequency                  | f <sub>22-23</sub>          | 60                  |                      | 140 | MHz  |                             |   |            |

| Max input RF level               | V <sub>22-23</sub>          | 120                 |                      |     | dΒμV |                             |   |            |

| Input impedance                  | R <sub>22-23</sub>          |                     | 1.8                  |     | kΩ   |                             | L |            |

| single ended                     | C <sub>22-23</sub>          |                     | 2.5                  |     | pF   |                             | L |            |

| Mixer gain                       | A <sub>mix</sub>            | 12                  | 15                   | 18  | dB   |                             |   | 259        |

| Input IP3                        |                             |                     | 126                  |     | dΒμV | IM = 60 dB                  | L |            |

| Noise Figure                     | F                           |                     | 6                    |     | dB   |                             | L |            |

| Reference voltage RF section     | V <sub>27</sub>             | 4.3                 | 4.8                  | 5.3 | V    |                             |   | 104        |

| Prestage AGC outputs             |                             |                     |                      |     |      |                             |   |            |

| AGC threshold range              | V <sub>22-23</sub>          | 48                  | 60                   | 72  | mV   | see diagram<br>SUB06h       |   | 310<br>311 |

| AGC threshold range              | V <sub>22-23</sub>          | 36                  | 45                   | 54  | mV   | see diagram<br>SUB06h       |   | 312<br>313 |

| AGC threshold range              | V <sub>22-23</sub>          | 24                  | 30                   | 36  | mV   | see diagram<br>SUB06h       |   | 314<br>315 |

| AGC threshold range              | V <sub>22-23</sub>          | 10                  | 15                   | 20  | mV   | see diagram<br>SUB06h       |   | 316<br>317 |

| AGC voltage for MOSFET<br>Gate 2 | V <sub>21</sub>             | 5.7                 | 6.4                  |     | V    | V <sub>22-23</sub> = 0 mV   |   | 106        |

| AGC voltage for MOSFET<br>Gate 2 | V <sub>21</sub>             |                     |                      | 0.1 | V    | V <sub>22-23</sub> = 200 mV |   | 300        |

| AGC current normal polarity      | l <sub>24</sub>             | 10                  | 13                   |     | mA   | $V_{22-23} = 0 \text{ mV}$  |   | 115        |

|                                     | Symbol              | 1 6 | mit Valu | AS  | Unit                  | Test Conditions                                         | L | Item  |

|-------------------------------------|---------------------|-----|----------|-----|-----------------------|---------------------------------------------------------|---|-------|

|                                     | Syllibol            | min |          | max | Offic                 | rest Conditions                                         | _ | iteii |

| AGC current normal polarity         | l <sub>24</sub>     |     | typ      | 0.1 | mA                    | V <sub>22-23</sub> = 200 mV                             |   | 301   |

| Integrator current                  | I <sub>21</sub>     | -75 | -50      | -25 | μΑ                    | $V_{22-23} = 0 \text{ mV};$                             |   | 117   |

| <b>.</b>                            | 21                  |     |          |     | •                     | Vm = 3V                                                 |   |       |

| Integrator current                  | l <sub>21</sub>     | 25  | 50       | 75  | μΑ                    | $V_{22-23} = 200 \text{ mV};$<br>Vm = 3V                |   | 303   |

| IF amplifier                        |                     |     |          |     |                       |                                                         |   |       |

| DC input voltage                    | V <sub>29</sub>     | 3.4 | 3.7      | 4.0 | V                     |                                                         |   | 108   |

| Input resistance                    | R <sub>29</sub>     |     | 330      |     | Ω                     |                                                         | L |       |

| Output resistance                   | R <sub>31</sub>     |     | 330      |     | Ω                     |                                                         | L |       |

| Max. Voltage gain                   | A <sub>31-29</sub>  | 23  | 26       | 29  | dB                    | see<br>diagram SUB07h                                   |   | 403   |

| Min. Voltage gain                   | A <sub>31-29</sub>  | 10  | 13       | 16  | dB                    | see<br>diagram SUB07h                                   |   | 405   |

| Noise figure                        | F                   |     | 7        |     | dB                    | $R_G = 330 \Omega$                                      |   |       |

| IF limiter amplifier / fieldstren   | gth generator       |     |          |     |                       |                                                         |   |       |

| Input voltage for limiter threshold | V <sub>34</sub>     |     | 25       | 45  | μV <sub>rm</sub><br>s | $f_{in} = 10.7 \text{ MHz};$<br>$V_{37} - 3 \text{ dB}$ |   | 470   |

| AM suppression                      | A <sub>AM</sub>     | 70  | 80       |     | dB                    | m = 30 %,<br>V <sub>34</sub> =100mV                     |   | 469   |

| Fieldstrength voltage               | V <sub>38</sub>     |     | 0.4      | 0.8 | V                     | $V_{34} = 0 \text{ mV}_{rms}$                           |   | 450   |

| Fieldstrength voltage               | V <sub>38</sub>     | 1.5 | 1.9      | 2.3 | V                     | $V_{34} = 1 \text{ mV}_{rms}$                           |   | 451   |

| Fieldstrength voltage               | V <sub>38</sub>     | 2.4 | 2.9      | 3.4 | V                     | $V_{34} = 10 \text{ mV}_{rms}$                          |   | 452   |

| Fieldstrength voltage               | V <sub>38</sub>     | 3.6 | 4.2      | 4.8 | V                     | $V_{34} = 200 \text{ mV}_{rms}$                         |   | 471   |

| Fieldstrength dynamic range         | V <sub>38dyn</sub>  |     | 90       |     | dB                    |                                                         |   |       |

| Fieldstrength linearity             | V <sub>38lin</sub>  |     | ±1       |     | dB                    |                                                         |   |       |

| Fieldstrength temperature drift     | V <sub>38temp</sub> |     |          | ±3  | dB                    |                                                         |   |       |

| FM demodulator                      |                     |     |          |     |                       |                                                         |   |       |

| AF output voltage                   | V <sub>37</sub>     | 500 | 600      | 720 | mV <sub>rm</sub><br>s | $\Delta F = 75 \text{ kHz};$ $f_{IF}=10.7 \text{ MHz}$  |   | 455   |

| AF output voltage                   | V <sub>37</sub>     |     | 300      |     | mV <sub>rm</sub><br>s | $\Delta$ F = 75 kHz;<br>f <sub>IF</sub> = 21.4 MHz      | L |       |

| Total harmonic distortion           | THD <sub>37</sub>   |     | 0.3      | 0.6 | %                     | ΔF = 75 kHz                                             |   | 456   |

| Total harmonic distortion detuned   | THD <sub>37</sub>   |     |          | 0.8 | %                     | f <sub>in</sub> = 10.7 MHz<br>± 50 kHz;<br>ΔF = 75 kHz  |   | 457   |

|                                 | Symbol                        | Li                           | mit Valu                     | es                           | Unit                | Test Conditions                                              | L | Item            |

|---------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|---------------------|--------------------------------------------------------------|---|-----------------|

|                                 |                               | min                          | typ                          | max                          |                     |                                                              |   |                 |

| Multipath detector              |                               |                              |                              |                              |                     |                                                              |   |                 |

| Attack current                  | I <sub>40</sub> *)            | 700                          | 900                          | 1200                         | μΑ                  | $V_{39} = 350 \text{ mV}_{rms};$<br>$V_m = 5 \text{ V}$      |   | 801             |

| Recovery current                | l <sub>40</sub> *)            | -8                           | -13                          | -18                          | μΑ                  | $V_{39} = 0 V_{rms};$<br>$V_{m} = 3.6 V$                     |   | 802             |

| Start voltage                   | V <sub>41Def</sub>            |                              | 4.7                          |                              | V                   | $V_{39} = 0 V_{rms}$                                         |   | 114             |

| Detector characteristic         | V <sub>41</sub>               | V <sub>41Def</sub><br>-3.1 V | V <sub>41Def</sub><br>-2.8 V | V <sub>41Def</sub><br>-2.5 V | V                   | $f_{39} = 200 \text{ kHz}$<br>$V_{39} = 40 \text{ mV}_{rms}$ |   | 800             |

| *) Detector currents are measu  | red between the               | e output į                   | oin (-pole                   | ) and a v                    | oltage so           | ource V <sub>m</sub>                                         |   |                 |

| Crystal oscillator              |                               |                              |                              |                              |                     |                                                              |   |                 |

| Operating frequency             | f <sub>10-11</sub>            |                              | 61.5                         |                              | MHz                 | 3rd harmonic                                                 |   |                 |

| Negative input impedance        | Z <sub>10-11</sub>            |                              | - 250                        |                              | Ω                   | f = 61.5 MHz                                                 |   |                 |

| Negative input impedance        | Z <sub>10-11</sub>            |                              | 1.4                          |                              | kΩ                  | f = 20.5 MHz                                                 |   |                 |

| Input impedance crystal         | R <sub>cr</sub>               |                              |                              | 70                           | Ω                   | 3rd harmonic                                                 |   |                 |

| Spurious harmonics crystal      | a <sub>sp</sub>               |                              |                              | - 20                         | dB                  | f < 200 MHz                                                  |   |                 |

| Bus controlled adjust range     | ∆f <sub>adj</sub>             |                              | ± 40                         |                              | ppm                 | see diagram<br>SUB06h                                        |   |                 |

| Bus controlled output XTAL_DIV6 | V <sub>XTAL_DIV6</sub> on AC  |                              | 500                          |                              | $mV_{pp}$           | f = 10.25 MHz,<br>C <sub>load</sub> = 10 pF                  |   |                 |

| Bus controlled output XTAL_DIV6 | V <sub>XTAL_DIV6</sub> on DC  | 1.0                          | 1.5                          | 2.0                          | V <sub>DC</sub>     | f = 10.25 MHz,<br>C <sub>load</sub> = 10 pF                  |   | 180             |

| Bus controlled output XTAL_DIV6 | V <sub>XTAL_DIV6</sub> off DC |                              |                              | 50                           | ${\sf mV}_{\sf DC}$ | C <sub>load</sub> = 10 pF                                    |   | 197             |

| Chargepump output (Loopfile     | ter input)                    |                              |                              |                              |                     |                                                              |   |                 |

| DC voltage                      | V <sub>PD_0</sub>             | 2.3                          | 2.5                          | 2.7                          | V                   | locked                                                       |   | 251<br>252      |

| DC current                      | ± I <sub>PD_03</sub>          | 3.2                          | 4                            | 5.2                          | mA                  | see Status,<br>Subaddress 00H,                               |   | 220             |

| DC current                      | ± I <sub>PD_02</sub>          | 1.6                          | 2                            | 2.6                          | mA                  | bit D1, D2                                                   |   | to              |

| DC current                      | ± I <sub>PD_01</sub>          | 0.8                          | 1                            | 1.3                          | mA                  | $V_{PD_0} = 2.5V$                                            |   | 227             |

| DC current                      | ± I <sub>PD_00</sub>          | 400                          | 500                          | 700                          | uA                  |                                                              |   |                 |

| Tristate output current         | ± I <sub>PD_00FF</sub>        |                              | 0.1                          | 10                           | nA                  | V <sub>PD_0</sub> = 2.5V ,<br>guaranteed by<br>design        |   | 228             |

| Loop amplifier tuningvoltage    | output (Loopf                 | ilter out                    | put)                         |                              |                     |                                                              |   |                 |

| LOW output voltage              | $V_{PDA\_L}$                  | 0                            |                              | 400                          | mV                  | I <sub>TUNE</sub> = 100 uA                                   |   | 23 <sup>-</sup> |

| HIGH output voltage             | $V_{PDA\_H}$                  | V <sub>VCC</sub><br>-0.5V    |                              | V <sub>CC</sub>              | mV                  | I <sub>TUNE</sub> = -100 uA                                  |   | 230             |

| Table 5-3 AC/DC Characteristics with T <sub>A</sub> 25 °C, V <sub>VCC</sub> = 8.5 V (continued) |                      |          |          |        |          |                                                                       |   |                  |  |  |  |

|-------------------------------------------------------------------------------------------------|----------------------|----------|----------|--------|----------|-----------------------------------------------------------------------|---|------------------|--|--|--|

|                                                                                                 | Symbol               | Li       | mit Valu | es     | Unit     | Test Conditions                                                       | L | Item             |  |  |  |

|                                                                                                 |                      | min      | typ      | max    |          |                                                                       |   |                  |  |  |  |

| HIGH output current source                                                                      | I <sub>PDA_H</sub>   | -1.9     | -2.4     | -2.9   | mA       | $V_{TUNE} = 4V$ ,                                                     |   | 232              |  |  |  |

| LOW output current source                                                                       | I <sub>PDA_L</sub>   | -0.9     | -1.2     | -1.5   | mA       | V <sub>PD_0</sub> = 0V<br>(see Status,<br>Subaddress 00H,<br>bit D11) |   | 233              |  |  |  |

| PLL for synthesizer (see PLL                                                                    | Synthesizer o        | n page 3 | 3-16)    |        |          |                                                                       |   |                  |  |  |  |

| PLL / VCO step size<br>(programmable via R-<br>counter)                                         | f <sub>ref</sub>     | 6.25     |          | 100    | kHz      | f <sub>crystal</sub> = 61.5 MHz                                       |   |                  |  |  |  |

| N-counter divide ratio                                                                          | N                    | 2        |          | 65535  |          | 16-Bit                                                                |   | 200<br>to<br>207 |  |  |  |

| R-counter divide ratio                                                                          | R                    | 2        |          | 65535  |          | 16-Bit                                                                |   | 210<br>to<br>216 |  |  |  |

| Port outputs, PORT_1, PORT                                                                      | _2, IF_CENT, II      | F_WIND   | OW (see  | Output | ports or | page 3-15)                                                            |   |                  |  |  |  |

| LOW output voltage                                                                              | V <sub>P</sub>       | 0        | 100      | 400    | mV       | I <sub>P</sub> = 1 mA                                                 |   | *1)              |  |  |  |

| HIGH Leakage current                                                                            | I <sub>P_LEACK</sub> | 0        |          | 100    | nA       | V <sub>P</sub> = 5 V                                                  |   | *2)              |  |  |  |

<sup>\*1) 830, 840, 831, 834</sup> \*2) 118, 119, 124, 125

# I<sup>2</sup>C bus (SCL, SDA) (see I2C Bus Timing on page 5-12 and Bus Data Format on page 3-15)

| H-input voltage                                 | V <sub>IH</sub> | 2.10 | 5.50 | V  |                                               |   | 150 |

|-------------------------------------------------|-----------------|------|------|----|-----------------------------------------------|---|-----|

| L-input voltage                                 | V <sub>IL</sub> | -0.5 | 0.90 | V  |                                               |   | 150 |

| Hysteresis of Schmitt trigger inputs (SCL, SDA) | $V_{hys}$       | 0.30 |      | V  |                                               |   |     |

| Input capacity                                  | C <sub>I</sub>  |      | 5    | pF |                                               |   |     |

| I <sup>2</sup> C bus leakage current            | I_LEACK         | 0    | 1    | μΑ | Values only valid for applied V <sub>CC</sub> | L |     |

## Ref voltages

| Ref voltage | V <sub>6</sub> | 4.5 | 5.0 | 5.5 | V |  | 102 |

|-------------|----------------|-----|-----|-----|---|--|-----|

| Ref voltage | V <sub>7</sub> | 2.7 | 3.0 | 3.3 | V |  | 103 |

# 5.2 Phase detector outputs

# 5.3 Bus Interface

1. Bus Interface

# I<sup>2</sup>C Bus

2. Bus Data Format

## I<sup>2</sup>C Bus Write Mode

|     | MSB | СНІ | P ADD | RESS | (WRIT | ΓE) |   | LSB |     | MSB |    | ADDF<br>07H, |    | (WRIT | E) |    | LSB |     | MSB | DATA | A IN X. | 0 (X= | =7 or 1 | 5) |    | LSB |     |     |

|-----|-----|-----|-------|------|-------|-----|---|-----|-----|-----|----|--------------|----|-------|----|----|-----|-----|-----|------|---------|-------|---------|----|----|-----|-----|-----|

| STA | 1   | 1   | 0     | 0    | 1     | 1   | 0 | 0   | ACK | S7  | S6 | S5           | S4 | S3    | S2 | S1 | S0  | ACK | DX  |      | D5      | D4    | D3      | D2 | D1 | D0  | ACK | STO |

# I<sup>2</sup>C Bus Read Mode

|     | MSB | CHIE | P ADD | RESS | (WRIT | ΓE) |   | LSB |     | MSB | SUB | ADDF | RESS | (READ | ) 82H/ | '83H | LSB |     |     | MSB | CHIF | ADD | RESS | (REAI | D) |   | LSB |     |

|-----|-----|------|-------|------|-------|-----|---|-----|-----|-----|-----|------|------|-------|--------|------|-----|-----|-----|-----|------|-----|------|-------|----|---|-----|-----|

| STA | 1   | 1    | 0     | 0    | 1     | 1   | 0 | 0   | ACK | 1   | 0   | 0    | 0    | 0     | 0      | 1    | 0   | ACK | STA | 1   | 1    | 0   | 0    | 1     | 1  | 0 | 1   | ACK |

| MSB | DATA OUT FROM SUB ADD 82H |     |     |     | LSB |    | MSB | DATA              | OUT | FROM | SUB A | DD 821 | H/83H | LSB |    |    |                   |     |

|-----|---------------------------|-----|-----|-----|-----|----|-----|-------------------|-----|------|-------|--------|-------|-----|----|----|-------------------|-----|

| R15 | R14                       | R13 | R12 | R11 | R10 | R9 | R8  | ACK <sup>1)</sup> | R7  | R6   | R5    | R4     | R3    | R2  | R1 | R0 | ACK <sup>2)</sup> | STO |

<sup>1):</sup> mandatory LOW send by uP, 2): mandatory HiGH send by uP Chipaddress Organisation

| Chip Address |   |   |   |   |   |   |     |                    |  |

|--------------|---|---|---|---|---|---|-----|--------------------|--|

| MSB          |   |   |   |   |   |   | LSB | Function           |  |

| 1            | 1 | 0 | 0 | 1 | 1 | 0 | 0   | Chip Address Write |  |

| 1            | 1 | 0 | 0 | 1 | 1 | 0 | 1   | Chip Address Read  |  |

## Subaddress Organisation

| Sub A | Addres | ddresses of Data Registers Write |   |   |   |   |     |     |             |  |  |  |  |

|-------|--------|----------------------------------|---|---|---|---|-----|-----|-------------|--|--|--|--|

| MSB   | Bin    |                                  |   |   |   |   | LSB | Hex | Function    |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 0 | 0 | 0   | 00H | Status      |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 0 | 0 | 1   | 01H | R_Counter   |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 0 | 1 | 0   | 02H | N_Counter   |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 0 | 1 | 1   | 03H | Mute_DAC7   |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 1 | 0 | 0   | 04H | IF_COUNT_P1 |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 1 | 0 | 1   | 05H | IF_COUNT_P2 |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 1 | 1 | 0   | 06H | Specials    |  |  |  |  |

| 0     | 0      | 0                                | 0 | 0 | 1 | 1 | 1   | 07H | Gain_DAC4   |  |  |  |  |

| 0     | 0      | 0                                | 0 | 1 | 0 | 1 | 1   | 0BH | COMP-PRESET |  |  |  |  |

| Sub A | Sub Address of Data Register Read |   |   |   |   |   |     |     |                                                                   |  |  |  |

|-------|-----------------------------------|---|---|---|---|---|-----|-----|-------------------------------------------------------------------|--|--|--|

| MSB   | Bin                               |   |   |   |   |   | LSB | Hex | Function                                                          |  |  |  |

| 1     | 0                                 | 0 | 0 | 0 | 0 | 1 | 0   | 82H | Result Multipath,<br>Fieldstrength,<br>IF_Window and<br>IF_Center |  |  |  |

| 1     | 0                                 | 0 | 0 | 0 | 0 | 1 | 1   | 83H | Result-MISC                                                       |  |  |  |

# Data Byte Specification

|            | Status<br>Subaddress 00H |  |  |  |  |  |  |  |  |

|------------|--------------------------|--|--|--|--|--|--|--|--|

| Bit        | Function                 |  |  |  |  |  |  |  |  |

| MSB<br>D15 | not used (must be=0)     |  |  |  |  |  |  |  |  |

| D14        | Port_2 (0=low, 1=high)   |  |  |  |  |  |  |  |  |

| D13        | Port_1 (0=low, 1=high)   |  |  |  |  |  |  |  |  |

| D12        | not used (must be=0)     |  |  |  |  |  |  |  |  |

| D11        | Loopamp current          |  |  |  |  |  |  |  |  |

| D10        | not used (must be=0)     |  |  |  |  |  |  |  |  |

| D9         | not used (must be=0)     |  |  |  |  |  |  |  |  |

| D8         | not used (must be=0)     |  |  |  |  |  |  |  |  |

| D7         | ADC_Single               |  |  |  |  |  |  |  |  |

| D6         | ADC_Mode                 |  |  |  |  |  |  |  |  |

| D5         | ADC_ON                   |  |  |  |  |  |  |  |  |

| D4         | IF_DAC4                  |  |  |  |  |  |  |  |  |

| D3         | not used (must be=0)     |  |  |  |  |  |  |  |  |

| D2         | CP_Current 2             |  |  |  |  |  |  |  |  |

| D1         | CP_Current 1             |  |  |  |  |  |  |  |  |

| D0<br>LSB  | CP_Mode                  |  |  |  |  |  |  |  |  |

| R_Cou      | ınter<br>dress 01H |

|------------|--------------------|

| Bit        | Function           |

| MSB<br>D15 | 2 <sup>15</sup>    |

| D14        | 2 <sup>14</sup>    |

| D13        | 2 <sup>13</sup>    |

| D12        | 2 <sup>12</sup>    |

| D11        | 2 <sup>11</sup>    |

| D10        | 2 <sup>10</sup>    |

| D9         | 2 <sup>9</sup>     |

| D8         | 2 <sup>8</sup>     |

| D7         | 2 <sup>7</sup>     |

| D6         | 2 <sup>6</sup>     |

| D5         | 2 <sup>5</sup>     |

| D4         | 24                 |

| D3         | 2 <sup>3</sup>     |

| D2         | 2 <sup>2</sup>     |

| D1         | 2 <sup>1</sup>     |

| D0<br>LSB  | 20                 |

| N_Cou      | unter<br>Idress 02H |

|------------|---------------------|

| Bit        | Function            |

| MSB<br>D15 | 2 <sup>15</sup>     |

| D14        | 2 <sup>14</sup>     |

| D13        | 2 <sup>13</sup>     |

| D12        | 2 <sup>12</sup>     |

| D11        | 2 <sup>11</sup>     |

| D10        | 2 <sup>10</sup>     |

| D9         | 2 <sup>9</sup>      |

| D8         | 2 <sup>8</sup>      |

| D7         | 2 <sup>7</sup>      |

| D6         | 2 <sup>6</sup>      |

| D5         | 2 <sup>5</sup>      |

| D4         | 2 <sup>4</sup>      |

| D3         | 2 <sup>3</sup>      |

| D2         | 2 <sup>2</sup>      |

| D1         | 2 <sup>1</sup>      |

| D0<br>LSB  | 20                  |

| Results Fieldstrength, Multipath                                                    |                              |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------|--|--|--|--|--|--|

| Results Fieldstrength, Multipath<br>and IF counter<br>Subaddress 82H (read address) |                              |  |  |  |  |  |  |

| Bit                                                                                 | Function                     |  |  |  |  |  |  |

| MSB<br>D15                                                                          | IF_window                    |  |  |  |  |  |  |

| D14                                                                                 | Multipath_2 <sup>6</sup>     |  |  |  |  |  |  |

| D13                                                                                 | Multipath_2 <sup>5</sup>     |  |  |  |  |  |  |

| D12                                                                                 | Multipath_2 <sup>4</sup>     |  |  |  |  |  |  |

| D11                                                                                 | Multipath_2 <sup>3</sup>     |  |  |  |  |  |  |

| D10                                                                                 | Multipath_2 <sup>2</sup>     |  |  |  |  |  |  |

| D9                                                                                  | Multipath_2 <sup>1</sup>     |  |  |  |  |  |  |

| D8                                                                                  | Multipath_2 <sup>0</sup>     |  |  |  |  |  |  |

| D7                                                                                  | IF_center                    |  |  |  |  |  |  |

| D6                                                                                  | Fieldstrength_2 <sup>6</sup> |  |  |  |  |  |  |

| D5                                                                                  | Fieldstrength_2 <sup>5</sup> |  |  |  |  |  |  |

| D4                                                                                  | Fieldstrength_2 <sup>4</sup> |  |  |  |  |  |  |

| D3                                                                                  | Fieldstrength_2 <sup>3</sup> |  |  |  |  |  |  |

| D2                                                                                  | Fieldstrength_2 <sup>2</sup> |  |  |  |  |  |  |

| D1                                                                                  | Fieldstrength_2 <sup>1</sup> |  |  |  |  |  |  |

| D0<br>LSB                                                                           | Fieldstrength_2 <sup>0</sup> |  |  |  |  |  |  |

| Mute_<br>Subad | DAC7<br>dress 03H |

|----------------|-------------------|

| Bit            | Function          |

| MSB<br>D7      | Enable            |

| D6             | MDAC_6            |

| D5             | MDAC_5            |

| D4             | MDAC_4            |

| D3             | MDAC_3            |

| D2             | MDAC_2            |

| D1             | MDAC_1            |

| D0<br>LSB      | MDAC_0            |

|                |                   |