### Downloaded from **Elcodis.com** electronic components distributor

# nP3454 4.4-Gbps Network Processor with Integrated Traffic Manager

# **Applications**

- Switched Ethernet Platforms

- WLAN Access Controllers

- Ethernet Over SONET/SDH

- CPE Equipment, MTU/MDU

### Features

### 4.4-Gbps Traffic Throughput

AMCC

- High-performance traffic manager and network processor integrated in one device

- Standalone or integrated high-density line card solutions

- Existing software libraries supporting IPv4, IPv6, MPLS, Ethernet over MPLS, RMON, ACL, L2 bridging, 802.1p, 802.1q, and MPLS VPN

#### Standards-Based Line Interfaces

Integrated GE(GMII) MACs

### **Integrated Traffic Manager**

- Stream-Based Traffic ManagementHardware- and Software-Based

- Admission Control • Strict Priority (SP) and Weighted Fair Queuing (WFQ)

- Four CoS per Port

- Support for Unicast, Multicast, and Broadcast Operations

#### **Network Processing Features**

- nP<sup>5</sup><sup>™</sup>-based nPcore<sup>™</sup> technology

- Per-flow metering and statistics for millions of flows

- Fully-programmable packet manipulation to accommodate future protocols

- On-chip debugging engine

- 8K instruction space

### **Benefits**

- High integration: Significant form factor, cost, and power savings

- Hardware-based Traffic Manager for guaranteed performance

- Software compatibility with

nP32xx, nP345x, nP36xx, nP37xx, and

nP7250

- Simple programming model for rapid development and quick time-to-market

- Software portability

The nP3454 is a successor to AMCC's highly-adopted nP3404 Network Processor with Integrated Traffic Manager device. The nP3454 is pin-compatible with the nP3404, but with twice the performance.

The nP3454 is implemented using industry leading  $nP^{5}$ <sup>TM</sup> technology (also found in the nP37xx/nP36xx devices) with enhanced network processing and traffic management.

The increased performance, efficiency, headroom, flexibility, and integration afforded by this proven technology enables customers to deliver more features at lower cost, power, and size than ever before. High-density Ethernet interfaces combined with superior programmability provide the best combination for enabling value-added Ethernet Services for Wireline/WiFi Access and Metro Ethernet Networks.

# Industry Leading Performance and Flexibility

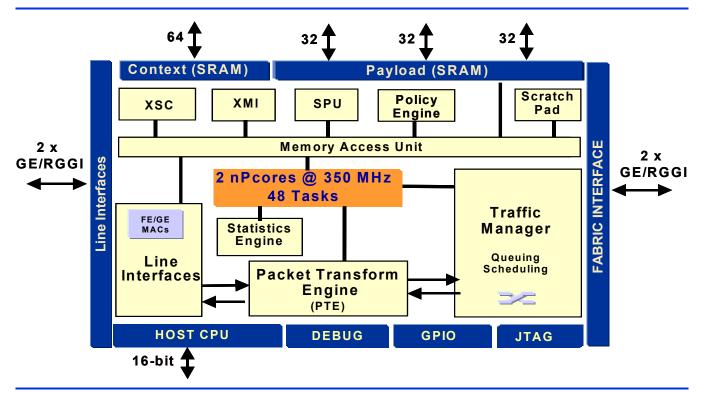

The nP3454 network processing unit consists of two low-power network processing nPcores™

that are based on proven  $nP^{5m}$ -based products. These nPcores, along with specialized Network Service Accelerators such as Policy Engine, Special Purpose Policing Unit, Packet Transform Engine, and Statistics Engine, offer unparalleled performance at line rate.

The superior programmability and flexibility of these cores enable flexible support for existing and future networking protocols. All of the line interfaces on this device are standardscompliant maximizing inter-operability and flexibility.

# **Value Added Services**

The traffic management unit of the nP3454 is based on the proven Per-Stream Queuing<sup>™</sup> and Scheduling architecture allowing guaranteed and measurable services. The nP3454 traffic manager's four classes of service (CoS) enable layered services. The enhanced multicast scheme and programmable memory management provide increased flexibility in traffic management.

### Software Compatibility

With its "run-to-completion" single-image programming model and nPkernel software infrastructure, the nP3454 is softwarecompatible with the nP<sup>5</sup>™-based products. This provides enormous leverage for customers in reusing software from prior generations of design and achieving quick time-to-market.

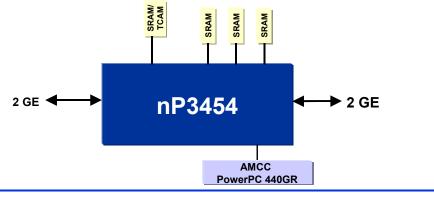

nP3454 Interface Diagram

# PRODUCT BRIEF

# nP3454

# nP3454 Highlights

### Interfaces

- Line and Switch Interfaces

- Two Gigabit Ethernet (GMII) or Reduced Generic Gigabit Interface (RGGI)

AND

- Two Gigabit Ethernet (GMII) or Reduced Generic Gigabit Interface (RGGI)

- External Payload Memory Interfaces

- 96-bit SCD SRAM at 100 MHz

- External Database Memory Interface

64-bit SCD/ZBT SRAM at 100 MHz

- External Search Coprocessor (TCAM) and/or routing table memory

- CPU Interface: Embedded PowerPC

Compatible

- On-Chip debugger: Debug on any hardware system

- JTAG port

- GPIO interface

### **High Performance nPcore**

- Two nPcores<sup>™</sup> at up to 350 MHz

- Over 60% instructions/packet headroom in addition to L2 processing

#### **Integrated Network Accelerators**

- Policy Engine

- Special Purpose Unit (SPU)

- On-Chip Debugger (OCD)

- Packet Transform Engine (PTE)

- Statistics Engine

### **Integrated Traffic Manager**

Based on nP3404 Per-Stream Queuing Technology

### nP3454 Block Diagram

### **nPsoft Services Framework**

Designed to decrease customer time-to-market and increase time-in-market, the feature rich nPsoft Services (nPSS) framework offers application portability, libraries for common nP functionality and reduced software investment for customers. The nPSS software offering provides a well-defined control and data plane source code which allows for easy integration into networking solutions. Application Service Libraries (ASL) provide protocol reference code including IPv4/v6 forwarding, Layer 2 switching, VLAN with 802.1p/q support and MPLS. AMCC also offers a complete suite of development tools consisting of a compiler, an assembler, simulators with performance profiling, and an on-chip debugger.

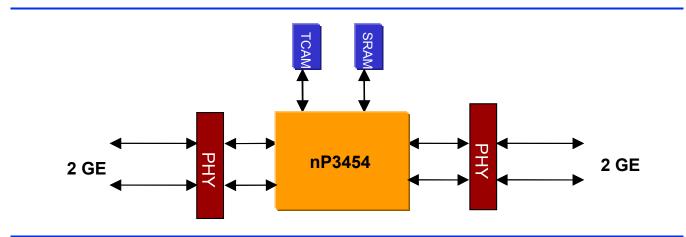

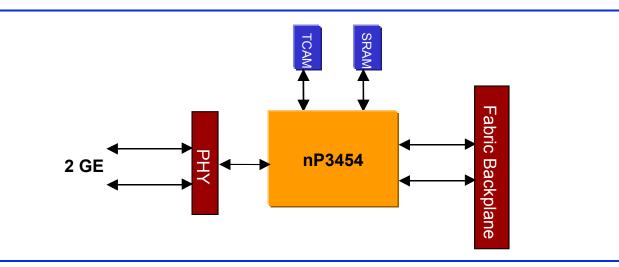

### **System Diagrams**

Standalone CPE — 2 + 2 GE Metro Ethernet Services Switch

2 GE — Integrated WLAN Enterprise Access Appliance

# nP3454

# Specifications

| Network Processing                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configurations                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                    |

| <ul> <li>Ethernet</li> <li>2 Gigabit Ethernet + 2 Gigabit Ethernet</li> <li>2 Gigabit Ethernet + 2 Stack Interfaces (RGGI)</li> <li>3 Gigabit Ethernet + 1 Stack Interface (RGGI)</li> <li>4 RGGI</li> </ul>                                                                                                                      | Can be cascaded with multiples of nP3450 or nP3454 for higher performance                                                                                                                                                                          |

| nPcore Performance                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                    |

| <ul> <li>Two nPcores running at up to 350 MHz</li> <li>24 tasks per nPcore, total 48 tasks</li> <li>8K instructions</li> </ul>                                                                                                                                                                                                    | <ul><li>Dynamic Task Allocation</li><li>Zero Cycle Task Switching</li></ul>                                                                                                                                                                        |

| Integrated Coprocessors                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                    |

| <ul> <li>Policy Engine — Efficient packet classification</li> <li>SPU — Data coherency</li> <li>Enables Single and Dual Leaky Bucket (ITU I.371)</li> <li>Atomic read-modify-write — Per-Flow Statistics</li> </ul>                                                                                                               | <ul> <li>Packet Transform Engine (PTE) — Efficient packet modification</li> <li>Statistics Engine — Programmable statistics collection</li> <li>OCD — On-chip Debug</li> <li>Adds controllability and observability to nPcore for debug</li> </ul> |

| Traffic Management                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                    |

| <ul> <li>Proven Per-Stream Queuing Technology</li> <li>2K Input Streams and 2K Output Flow</li> </ul>                                                                                                                                                                                                                             | <ul> <li>Strict Priority and Weighted Fair Queuing (WFQ)</li> <li>Four Classes of Service (CoS) per port</li> </ul>                                                                                                                                |

| nPsoft Development Environment                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                    |

| <ul> <li>nPsoft Services</li> <li>Simplified multiprocessor programming model</li> <li>Powerful NPU and CPU software and messaging framework</li> <li>nPkernel NPU operating system</li> <li>Open APIs, tracking standards</li> <li>nP Workbench-3454</li> <li>Software development system</li> <li>Modular interfaces</li> </ul> | nPsoft Application Libraries<br>• Reference source code for WAN and LAN protocols<br>nPsoft Toolkit<br>• Code development tools<br>• Graphical simulators<br>• Customizable debugger<br>• Performance analysis                                     |

| Product Availability                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                    |

| <ul> <li>Part Number: nP3454PBxB-yyy (x: C – Commercial, I – Industrial, yyy: 350 – 350 MHz)</li> <li>Availability: Now</li> </ul>                                                                                                                                                                                                | Commercial and Industrial Temperature Rating                                                                                                                                                                                                       |

215 Moffett Park Drive Sunnyvale, CA 94089 P 858 450 9333 F 858 450 9885 www.amcc.com For technical support, please call 1-800-840-6055 or 858-535-6517, or email support@amcc.com.

AMCC reserves the right to make changes to its products, its datasheets, or related documentation, without notice and warrants its products solely pursuant to its terms and conditions of sale, only to substantially comply with the latest available datasheet. Please consult AMCC's Term and Conditions of Sale for its warranties and other terms, conditions and limitations. AMCC may discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information is current. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. AMCC reserves the right to ship devices of higher grade in place of those of lower grade. AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation. PowerPC and the PowerPC logo are registered trademarks of IBM Corporation. All other trademarks are the property of their respective holders. Copyright © 2006 Applied Micro Circuits Corporation. All Rights Reserved. NP3454PBxB\_PB\_v1.1\_20060428