## Vishay Dale

## **Plasma Panel Display Modules**

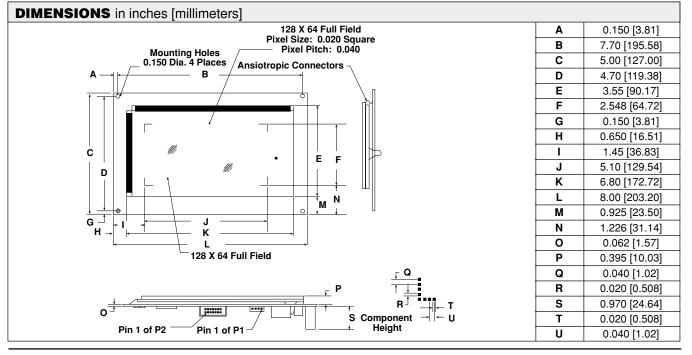

128 x 64 Graphics Display with Video Interface, DC Converter and Drive Circuitry

The APD-128G064D is a dot matrix graphic display with an array of 128 x 64 pixels available. The module is composed of a highly reliable DC plasma display, Video Interface, DC converter and drive circuitry which are assembled to form a rugged, slim profile display sub-system.

Interface to the APD-128G064D is through a video interface. Patented open construction display technology assures a stable, flicker free screen.

| STANDARD ELECTRICAL SPECIFICATIONS |        |      |      |      |       |

|------------------------------------|--------|------|------|------|-------|

| DESCRIPTION                        | SYMBOL | MIN. | TYP. | MAX. | UNITS |

| Panel Supply Voltage               | VDC    | 8.0  | 12.0 | 28.0 | V     |

| Panel Supply Current               | IDC    | 0.15 | 0.4  | 1.5  | А     |

## **ENVIRONMENTAL SPECIFICATIONS**

Operating Temperature: 20°C to + 70°C.

**Storage Temperature:** - 40°C to + 85°C.

Operating Humidity: 95% RH non-condensing.

Mechanical Shock: 30 G.

**Vibration:** 0.018" [0.457mm] displacement amplitude from 10-50Hz, 2 G acceleration from 50 to 2000Hz logarithmic sweep rate.

Mean Time Between Failure: 60,000 hours.

### FEATURES

- 128 x 64 pixel array for bright and vivid graphics.

- Video interface.

- Powerful software commands make display integration simple and efficient.

- + 8 to + 24 VDC display voltage.

## **OPTICAL SPECIFICATIONS**

Pixel Pitch: 0.040.

Pixel Size: 0.020" [0.610] square.

Pixel Array: 128 x 64.

Luminance: 50 foot lamberts typical.

Color: Neon orange.

Refresh Cycle: 120 Hz typical.

Viewing Angle: 150° cone.

Contrast Ratio: 30:1

## **ELECTROSTATIC CAUTION**

Vishay Dale display panels use electrostatic sensitive components. These assemblies should be unpacked and handled in an ESD controlled area only. When shipping use packing materials designed for protection of electrostatic sensitive components.

Vishay Dale believes that the information described in this publication is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this information.

www.vishay.com

# APD-128G064D

Vishay Dale

#### **DESCRIPTION OF INPUT SIGNALS**

DOT CLOCK: This signal enters the SERIAL DATA on each low to high transition. A total of 128 DOT CLOCK transitions must be present for each line of column/anode data.

SERIAL DATA: This signal presents the pixel data in positive logic format. A logic one represents a lit pixel and a logic zero represents an extinguished pixel. Data is entered from right to left. The first pixel data entered will represent the leftmost pixel in the row.

**COLUMN LATCH:** This signal latches the pixel data into the driver outputs. When the COLUMN LATCH signal goes to logic one the data entered previously will fall through to the driver outputs. When the signal returns to a logic zero, the data is latched and the shift register is now ready to accept the next row of data. Must be held low while entering new SERIAL DATA.

**DISPLAY ENABLE:** This signal enables the output drivers. Using a duty cycle control, this signal may also be used for intensity control. The DISPLAY ENABLE must be at logic zero before the COLUMN LATCH signal transitions. To avoid display blurring, the ROW CLOCK signal should also transition while DISPLAY ENABLE is a logic zero. It is recommended that this signal remain low for 10µS minutes.

ROW DATA: This signal is the first line marker for the scan. This input should be held high to correspond to the first row of pixel data.

**ROW CLOCK:** This signal clocks ROW DATA on the falling edge. The ROW CLOCK signal is repetitive and must be present for proper scanning of the display module.

The APD-128G064D has a unique input protection circuit that assures the column drivers stay blanked on power up. The protection circuit unblanks the column drivers when the ROW CLOCK signal begins (i.e. the display begins scanning).

| POWER | SUPPLY: (Recomm    | nended)                 |

|-------|--------------------|-------------------------|

| VDC   | + 12 V $\pm$ 0.6 V | 1.5 A Max.*, 0.4 A Typ. |

\*NOTE: The maximum VDC draw denotes a power up condition when the DC converter starts. Typical duration is 15-30 mS.

| POWER SUPPLY CONNECTION |     |          |  |

|-------------------------|-----|----------|--|

| CONNECTOR               | PIN | SIGNAL   |  |

| J1                      | 1   | + 12 VDC |  |

|                         | 2   | GROUND   |  |

|                         | 3   | GROUND   |  |

|                         | 4   | N/C      |  |

| SIGNA       | L DESCRIPTION             | 1                     |

|-------------|---------------------------|-----------------------|

| PIN         | FUNCTION                  | DESCRIPTION           |

| 1           | DEm                       | Display enable signal |

| 3           | Rdata                     | Row driver data input |

| 5           | Rclk                      | Row clock             |

| 7           | latch                     | Column latch          |

| 9           | Dot CLK                   | Dot clock             |

| 11          | Sdata                     | Serial column data    |

| *           | GND                       | Common Ground         |

| This inform | ation is subject to chang | e without notice      |

This information is subject to change without notice

Document Number: 37055 Revision 05-Dec-00

| LOGIC A                                                          | ND DATA T                                                   | IMING                            |                   |                    |

|------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------|-------------------|--------------------|

| Row Data                                                         |                                                             | $t_4$<br>$t_2$<br>$t_2$<br>$t_3$ |                   | 1                  |

| Row Clock                                                        |                                                             | 2                                | 62 63 0           |                    |

| Display<br>Enable                                                | Display 0 1 2 // 62 63 0 1 F                                |                                  |                   |                    |

|                                                                  |                                                             |                                  |                   |                    |

| Row Clock                                                        |                                                             |                                  |                   |                    |

| Column<br>Latch                                                  |                                                             |                                  |                   |                    |

| Display<br>Enable                                                | 1st Bit of Row Will Appear in Leftmost Column               |                                  |                   |                    |

| Serial Data $0 \times 1 \times 2 \times 2 \times 126 \times 127$ |                                                             |                                  |                   |                    |

| Dot Clock<br>$t_6$ Positive Edge x 192 $t_7$                     |                                                             |                                  |                   |                    |

| PARAMETEI                                                        | R MINIMUM                                                   | TYPICAL                          | MAXIMUM           | UNITS              |

| t <sub>1</sub>                                                   | 130                                                         | 112                              | _                 | nS                 |

| t <sub>2</sub>                                                   | 75                                                          | 1000                             | _                 | uS                 |

| t <sub>3</sub>                                                   | 16.6                                                        | 14.3                             | _                 | uS                 |

| t <sub>4</sub>                                                   | 5                                                           | 20                               | 200               | Hz                 |

| t <sub>5</sub>                                                   | 25                                                          | _                                | _                 | nS                 |

| t <sub>6</sub>                                                   | 75                                                          | _                                | _                 | nS                 |

| t <sub>7</sub>                                                   | 75                                                          | _                                |                   | nS                 |

| ORDERING INFORMATION                                             |                                                             |                                  |                   |                    |

| Non-Glare Fil<br>Video Contro                                    | <u>DN</u><br>Iter (Amber CP)<br>Iler (+ 5V)<br>Iler (+ 12V) |                                  | APD-12<br>28<br>F | 0109-19<br>PDS-500 |

#### APPLICABLE MATING MANUFACTURER PART NUMBER **CONNECTORS** TO POWER INPUT (P1) ...... MOLEX ...... 09-50-3081

|                                                | ,               |                  |

|------------------------------------------------|-----------------|------------------|

| Vishay Dale Power<br>Connector Kit 280108-0    | MOLEX           | 09-06-5087       |

|                                                | 05 AMP          | 640428-8         |

|                                                | METHODE         | 3300-108         |

| TO LOGIC INPUT (P2)                            | MOLEX           | 39-27-1146       |

| Vishay Dale Data<br>Connector Kit<br>280108-05 | ROBINSON NUGENT | IDS-C14PK-TC     |

|                                                | AMP 746         | 6195-2, 746582-2 |

|                                                | 3M 3314-        | 5002, 3314-5202  |

| 200,00 00                                      |                 |                  |

Vishay

# Notice

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.