# ST92196A ST92T196 ST92E196

# 8/16-BIT MCU FOR TV APPLICATIONS WITH UP TO 96K ROM, ON-SCREEN-DISPLAY AND 1 OR 2 DATA SLICERS

- Register file based 8/16 bit Core Architecture with RUN, WFI, and HALT modes

- -10 to 75°C Operating Temperature Range

- 24 MHz Operation @5 V ±10%

- Min. instruction cycle time: 165 ns at 24 MHz

- 32 96 Kbytes ROM, 1 3 Kbytes static RAM

- 256 bytes of Register file

- 384 bytes of display RAM (OSDRAM)

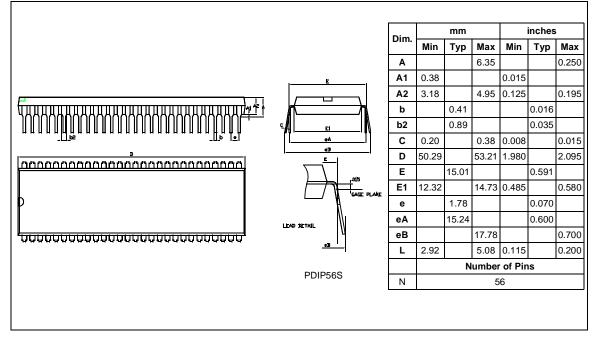

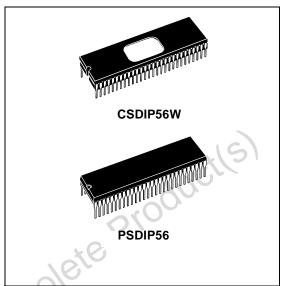

- 56-pin Shrink DIP and TQFP64 packages

- 37 fully programmable I/O pins

- Flexible Clock controller for OSD, Data slicer and Core clocks, running from one single low frequency external crystal

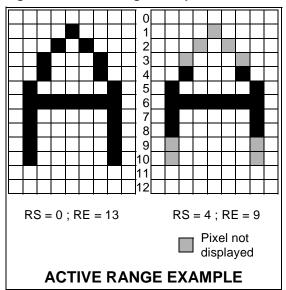

- Enhanced Display Controller with rows of up to 63 characters per row

- 50/60Hz and 100/120 Hz operation

- 525/625 lines operation, 4/3 or 16/9 format

- interlaced and progressive scanning

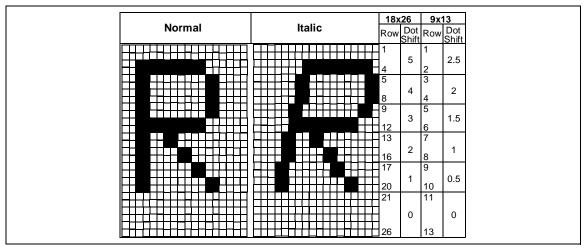

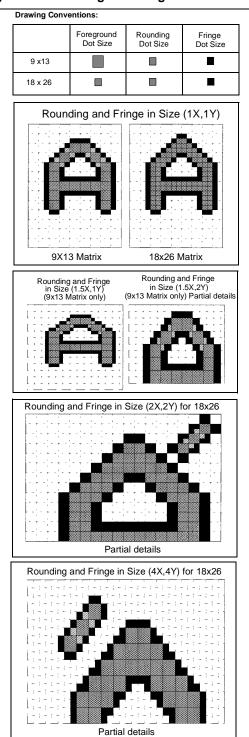

- 18x26 or 9x13 character matrix

- 384 (18x26) characters, or 1536 (9x13) characters definable in ROM by user

- 512 possible colors, in 4x16-entry palettes

- 2 x 16-entry palettes for Foreground, and 2 x 16-entry palettes for Background

- 8 levels of translucency on Fact Branking

- Serial, Parallel and Extended Parallel Attribute modes

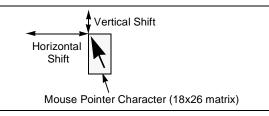

- Mouse pointers user-de inable in ROM

- 7 character sizes in 18x26 mode, 4 in 9x13

Rounding, Fringe, Scrolling, Flashing, Shadowing, Italics, Semi-transparent

- I<sup>2</sup>C Mu<sup>i</sup>t, Master / Slave with 4 channels

- Script Communications Interface (SCI)\*

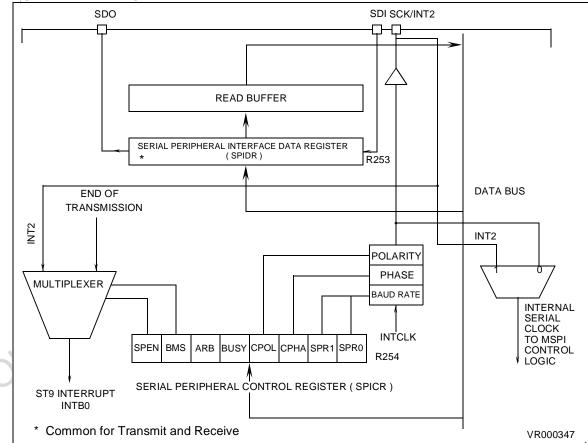

- Scrial Peripheral Interface (SPI)

- 8-channel A/D converter with 6-bit accuracy

- 16-bit Watchdog timer with 8-bit prescaler

- 14-bit Voltage Synthesis for tuning reference voltage with 2 outputs for 2 tuners

- 16-bit standard timer with 8-bit prescaler

- 16-bit Multi-Function timer\*

- Eight 8-bit programmable PWM outputs

- \* On some devices

October 2003

Y

- NMI and 5 external interrupts

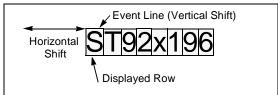

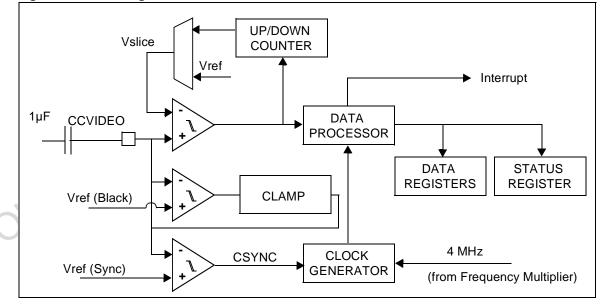

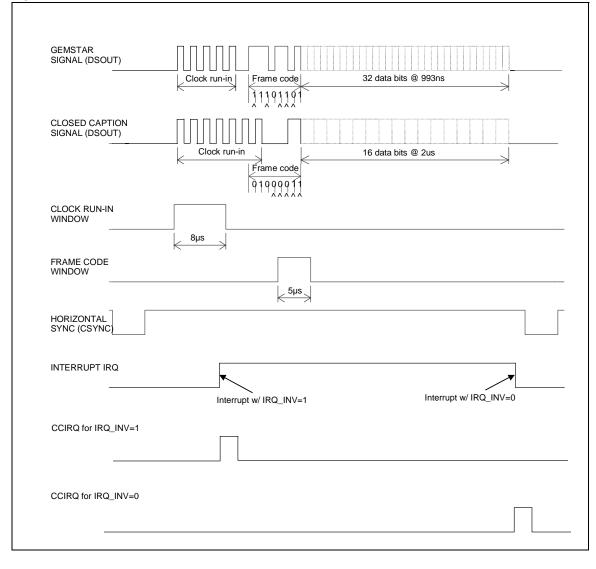

- 1 o 2 data slicers for Closed Captioning and Exunded Data Service data extraction, on 2 independent video sources. Support for FCC V-Chip and Gemstar bitstream decoding

- Infra-Red signal digital pre-processor

- 2-channel Sync error detection with integrated Sync extractor

- Rich instruction set and 14 addressing modes

- Versatile Development Tools, including C-Compiler, Assembler, Linker, Source Level Debugger, Emulator and Real-Time Operating Systems from third-parties

- Windows Based OSD Font and Screen Editor

# DEVICE SUMMARY

| Device    | ROM | RAM | Slicers | SCI | MFT |

|-----------|-----|-----|---------|-----|-----|

| ST92196A7 | 96K | ЗK  | 2       | 1   | 1   |

| ST92196A6 | 301 |     | 2       | 1   | 1   |

| ST92196A4 | 64K | 2K  | 2       | -   | 1   |

| ST92196A3 | 041 |     | 1       | -   | -   |

| ST92196A2 | 48K | 1K  | 1       | -   | -   |

| ST92196A1 | 32K |     | 1       | -   | -   |

| S | T92 | 2196A                                                                                                   |

|---|-----|---------------------------------------------------------------------------------------------------------|

| 1 | GEN | ERAL DESCRIPTION                                                                                        |

|   | 1.1 | INTRODUCTION                                                                                            |

|   |     | 1.1.1 Core Architecture                                                                                 |

|   |     | 1.1.2 Instruction Set                                                                                   |

|   |     | 1.1.3 Operating Modes                                                                                   |

|   | 4.0 | 1.1.4 On-chip Peripherals                                                                               |

|   | 1.2 | PIN DESCRIPTION                                                                                         |

|   |     | 1.2.1         I/O Port Configuration         13           1.2.2         I/O Port Reset State         13 |

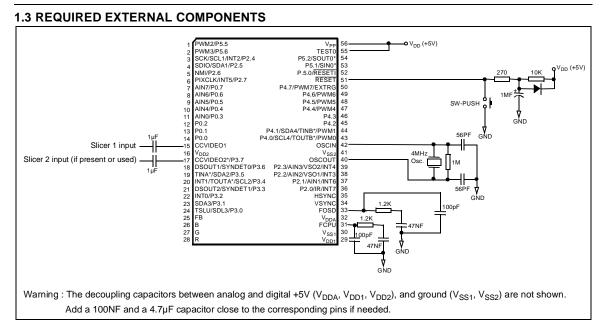

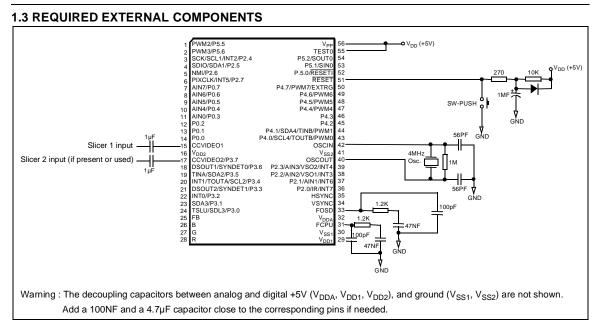

|   | 13  | REQUIRED EXTERNAL COMPONENTS                                                                            |

|   |     | MEMORY MAP                                                                                              |

|   |     | ST92196A REGISTER MAP                                                                                   |

| 2 |     | CE ARCHITECTURE                                                                                         |

| 2 |     | CORE ARCHITECTURE                                                                                       |

|   |     | MEMORY SPACES                                                                                           |

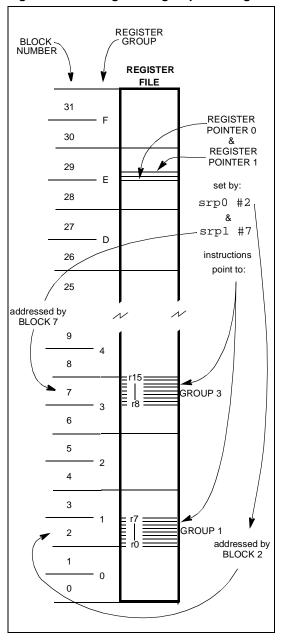

|   | 2.2 | 2.2.1 Register File                                                                                     |

|   |     | 2.2.1         Register File         24           2.2.2         Register Addressing         26           |

|   | 2.3 | SYSTEM REGISTERS                                                                                        |

|   |     | 2.3.1 Central Interrupt Control Register                                                                |

|   |     | 2.3.2 Flag Register                                                                                     |

|   |     | 2.3.3 Register Pointing Techniques                                                                      |

|   |     | 2.3.4 Paged Registers                                                                                   |

|   |     | 2.3.5 Mode Register                                                                                     |

|   | 2.4 | 2.3.6         Stack Pointers         33           MEMORY ORGANIZATION         35                        |

|   |     | MEMORY MANAGEMENT UNIT                                                                                  |

|   | 2.5 |                                                                                                         |

|   | 2.6 | ADDRESS SPACE EXTENSION                                                                                 |

|   |     | 2.6.1Addressing 16-Kbyte Pages372.6.2Addressing 64-Kbyte Segments38                                     |

|   | 27  | MMU REGISTERS                                                                                           |

|   | 2.1 | 2.7.1 DPR[3:0]: Data Page Registers                                                                     |

|   |     | 2.7.2 CSR: Code Segment Register                                                                        |

|   |     | 2.7.3 ISR: Interrupt Segment Register                                                                   |

|   |     | 2.7.4 DMASR: DMA Segment Register 40                                                                    |

|   | 2.8 | MMU USAGE                                                                                               |

|   |     | 2.8.1 Normal Program Execution                                                                          |

|   |     | 2.8.2 Interrupts                                                                                        |

| 2 |     | 2.8.3 DMA                                                                                               |

| 3 |     | INTRODUCTION                                                                                            |

|   |     | INTERRUPT VECTORING                                                                                     |

|   | J.Z |                                                                                                         |

|   |     | 3.2.1 Divide by Zero trap       44         3.2.2 Segment Paging During Interrupt Routines       45      |

|   |     |                                                                                                         |

57

# ST92196A

| 3.3    | INTERRUPT PRIORITY LEVELS                                                                                                      | 45 |

|--------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4    | PRIORITY LEVEL ARBITRATION                                                                                                     | 45 |

|        | 3.4.1 Priority level 7 (Lowest)                                                                                                | 45 |

|        | 3.4.2 Maximum depth of nesting                                                                                                 |    |

|        | 3.4.3 Simultaneous Interrupts                                                                                                  |    |

| 35     | 3.4.4 Dynamic Priority Level Modification         ARBITRATION MODES                                                            |    |

| 0.0    | 3.5.1 Concurrent Mode                                                                                                          |    |

|        | 3.5.2 Nested Mode                                                                                                              |    |

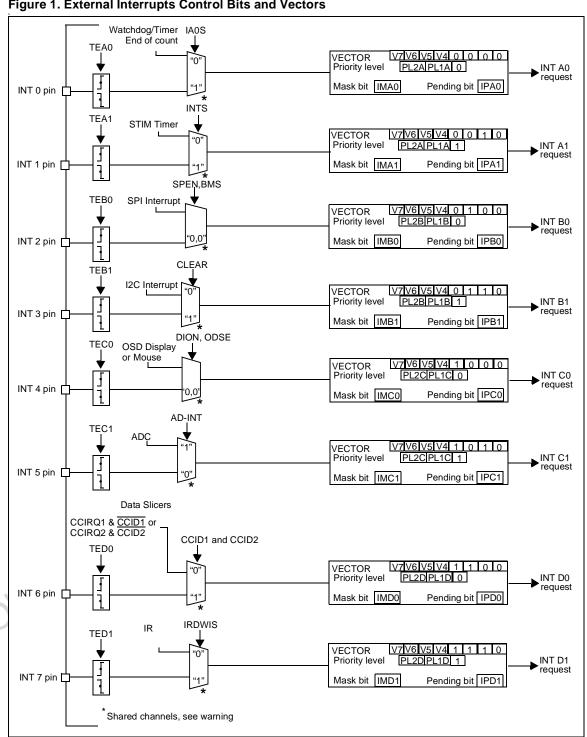

| 3.6    | EXTERNAL INTERRUPTS                                                                                                            |    |

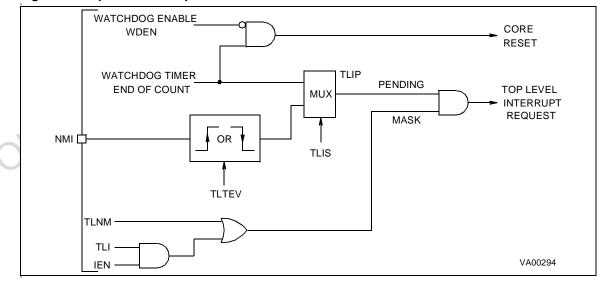

| 3.7    | TOP LEVEL INTERRUPT                                                                                                            | 53 |

| 3.8    | ON-CHIP PERIPHERAL INTERRUPTS                                                                                                  | 53 |

| 3.9    | INTERRUPT RESPONSE TIME                                                                                                        | 54 |

| 3.10   | INTERRUPT REGISTERS                                                                                                            | 55 |

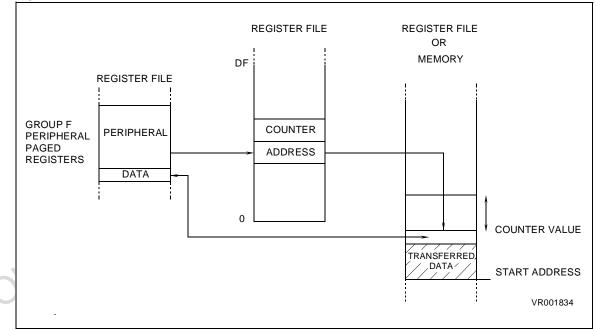

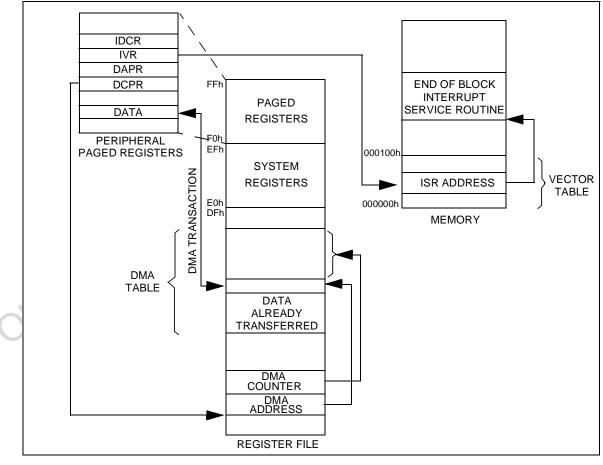

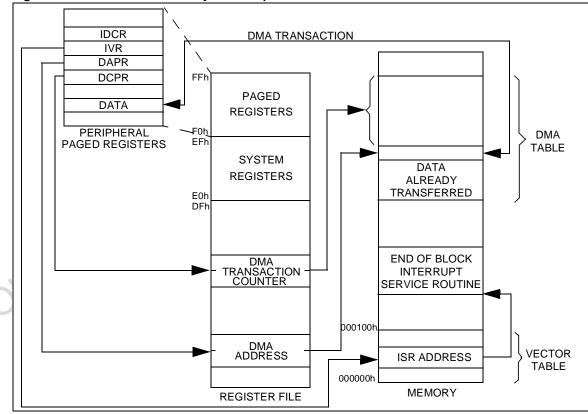

| 4 ON-0 | CHIP DIRECT MEMORY ACCESS (DMA)                                                                                                | 59 |

|        |                                                                                                                                |    |

| 4.2    | DMA PRIORITY LEVELS                                                                                                            | 59 |

| 4.3    | DMA TRANSACTIONS                                                                                                               | 60 |

| 4.4    | DMA CYCLE TIME                                                                                                                 | 62 |

| 4.5    | SWAP MODE                                                                                                                      | 62 |

| 4.6    | DMA REGISTERS                                                                                                                  | 63 |

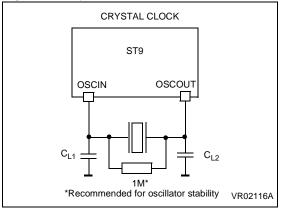

| 5 RESI | ET AND CLOCK CONTROL UNIT (RCCU)                                                                                               | 64 |

| 5.1    | INTRODUCTION                                                                                                                   | 64 |

| 5.2    | CLOCK CONTROL REGISTERS                                                                                                        | 64 |

| 5.3    | OSCILLATOR CHARACTERISTICS                                                                                                     | 65 |

|        | 5.3.1 HALT State                                                                                                               | 65 |

|        | RESET/STOP MANAGER                                                                                                             |    |

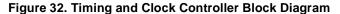

|        | NG AND CLOCK CONTROLLER (TCC)                                                                                                  |    |

|        | FREQUENCY MULTIPLIERS                                                                                                          |    |

|        | REGISTER DESCRIPTION                                                                                                           |    |

|        | ORTS                                                                                                                           |    |

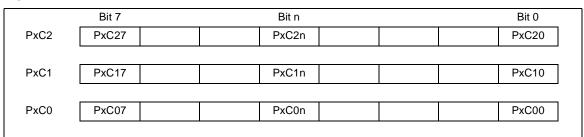

|        | INTRODUCTION                                                                                                                   |    |

|        | SPECIFIC PORT CONFIGURATIONS                                                                                                   |    |

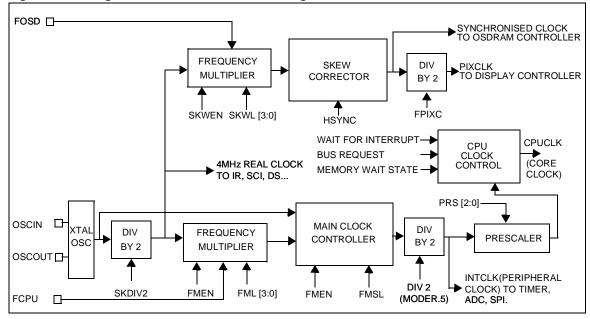

|        | PORT CONTROL REGISTERS                                                                                                         |    |

|        | INPUT/OUTPUT BIT CONFIGURATION                                                                                                 |    |

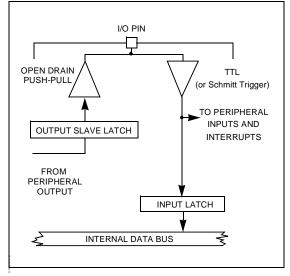

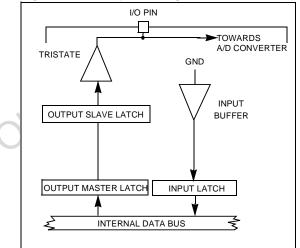

| 7.5    | ALTERNATE FUNCTION ARCHITECTURE                                                                                                |    |

|        | 7.5.1 Pin Declared as I/O                                                                                                      |    |

|        | <ul><li>7.5.2 Pin Declared as an Alternate Function Input</li><li>7.5.3 Pin Declared as an Alternate Function Output</li></ul> |    |

| 7.6    | I/O STATUS AFTER WFI, HALT AND RESET                                                                                           |    |

|        | CHIP PERIPHERALS                                                                                                               |    |

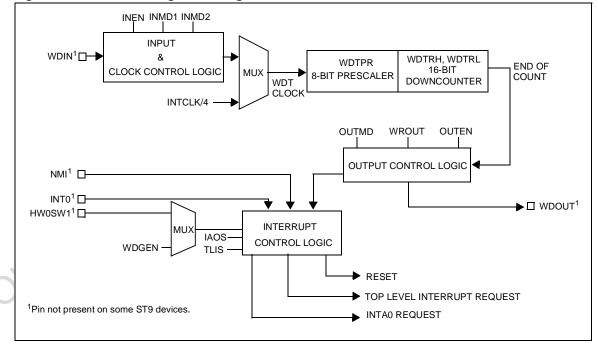

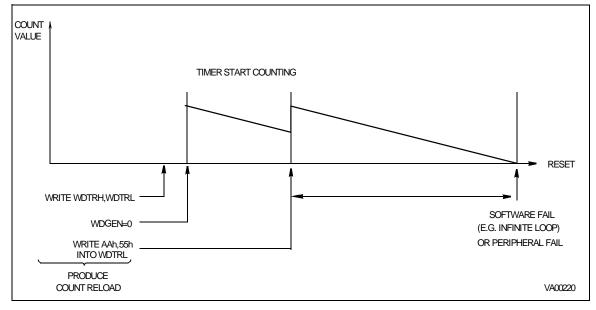

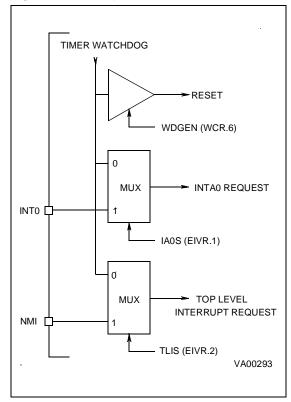

|        | TIMER/WATCHDOG (WDT)                                                                                                           |    |

|        | 8.1.1 Introduction                                                                                                             |    |

|        |                                                                                                                                |    |

|             | 8.1.2<br>8.1.3 | Functional Description                                    |     |

|-------------|----------------|-----------------------------------------------------------|-----|

|             | 8.1.3          | Watchdog Timer Operation      WDT Interrupts              |     |

|             | 8.1.5          | Register Description                                      |     |

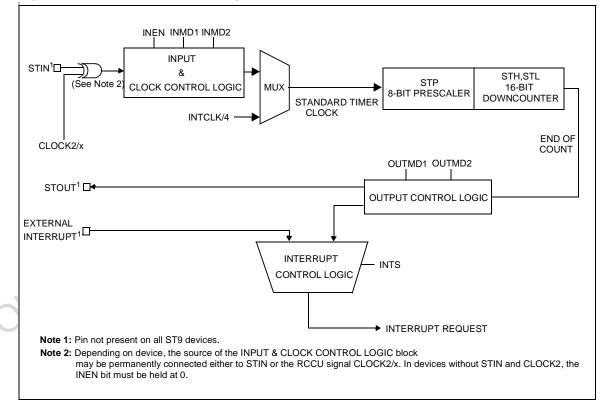

| 8.2         |                | DARD TIMER (STIM)                                         |     |

|             | 8.2.1          |                                                           |     |

|             | 8.2.2          | Functional Description                                    |     |

|             | 8.2.3          | Interrupt Selection                                       |     |

|             | 8.2.4          | Register Mapping                                          |     |

| 0.0         | 8.2.5          |                                                           |     |

| 8.3         |                |                                                           |     |

|             | 8.3.1<br>8.3.2 | Introduction                                              |     |

|             | 8.3.3          | Input Pin Assignment                                      |     |

|             | 8.3.4          | Output Pin Assignment                                     |     |

|             | 8.3.5          | Interrupt and DMA                                         |     |

|             | 8.3.6          | Register Description                                      |     |

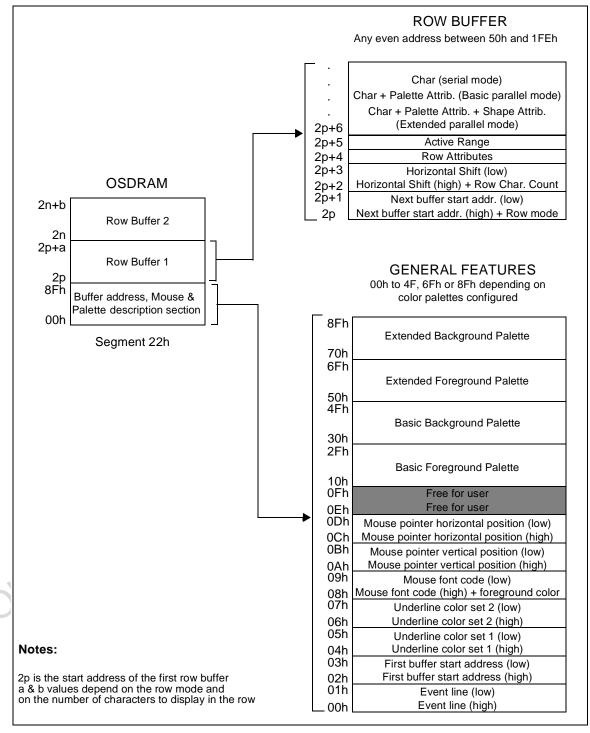

| 8.4         | OSDR           | AM CONTROLLER                                             |     |

|             | 8.4.1          | Introduction                                              |     |

|             | 8.4.2<br>8.4.3 | Functional Description                                    |     |

| 85          | 00             | OSDRAM Controller Reset Configuration                     |     |

| 0.5         | 8.5.1          |                                                           |     |

|             | 8.5.2          | General Features                                          |     |

|             | 8.5.3          | Functional Description                                    |     |

|             | 8.5.4          | Horizontal and Vertical Sync                              |     |

|             | 8.5.5          | Programming the Display                                   |     |

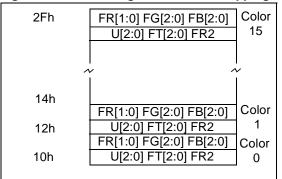

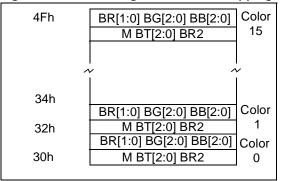

|             | 8.5.6          | Programming the Color Palettes                            |     |

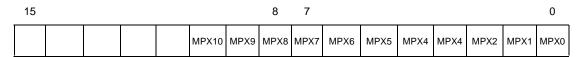

|             | 8.5.7<br>8.5.8 | Programming the Mouse Pointer Programming the Row Buffers |     |

|             | 8.5.9          | Register Description                                      |     |

| 8.6         |                | ED CAPTION DATA SLICER (DS)                               |     |

|             | 8.6.1          | Introduction                                              | 160 |

|             | 8.6.2          | Functional Description                                    |     |

|             | 8.6.3          | Data Slicer Operation                                     |     |

|             | 8.6.4          | Interrupt handling                                        |     |

| <u> 9</u> 7 | 8.6.5          | Register Description       SYNC ERROR DETECTOR (SYNCERR)  |     |

| 0.7         | 8.7.1          |                                                           |     |

|             | 8.7.2          | Register Description                                      |     |

| 8.8         |                | EPROCESSOR (IR)                                           | 169 |

|             | 8.8.1          | Functional Description                                    | 169 |

|             | 8.8.2          | Register Description                                      | 169 |

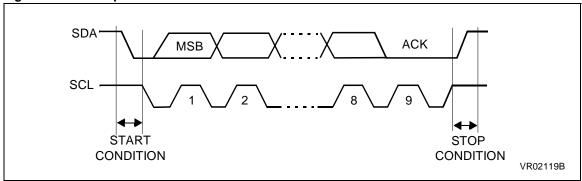

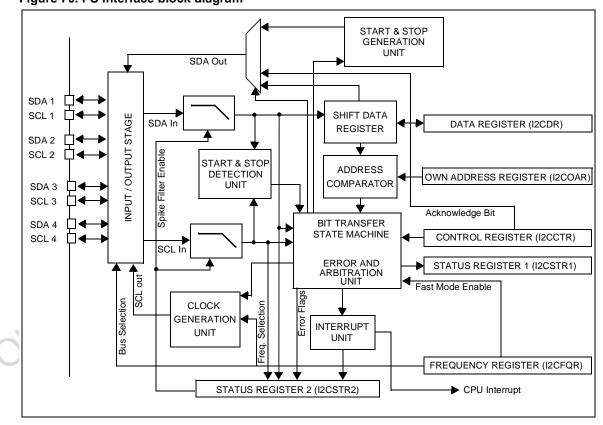

| 8.9         | FOUR           | CHANNEL I <sup>2</sup> C BUS INTERFACE (I2C)              | 170 |

|             | 8.9.1          | Introduction                                              | 170 |

|             | 8.9.2          | General Description                                       | 171 |

|             | 8.9.3          | Functional Description                                    | 172 |

57

# ST92196A

| 8.9.4       | Interrupt Handling                   |     |

|-------------|--------------------------------------|-----|

| 8.9.5       | Error Cases                          |     |

|             | Register Description                 |     |

|             |                                      |     |

|             | Introduction Device-Specific Options |     |

|             | Functional Description               |     |

|             | Interrupt Structure                  |     |

|             | Working With Other Protocols         |     |

|             | I2C-bus Interface                    |     |

|             | S-Bus Interface                      |     |

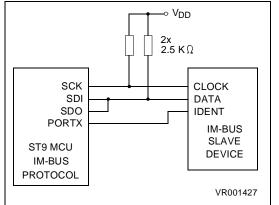

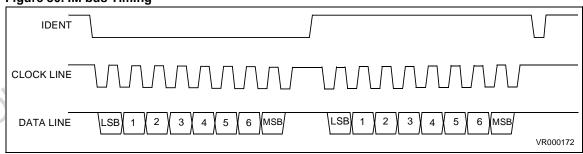

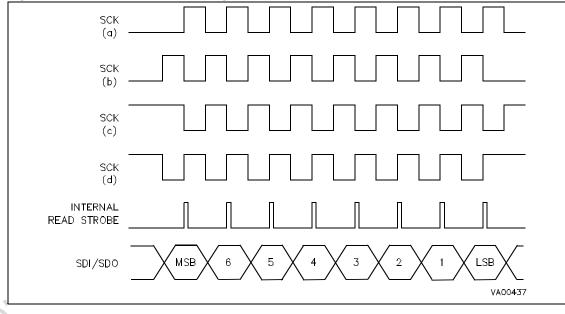

|             | IM-bus Interface                     |     |

|             | Register Description                 |     |

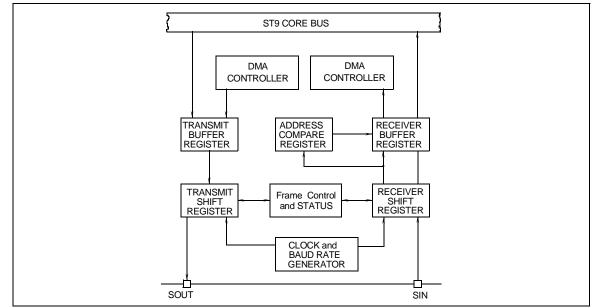

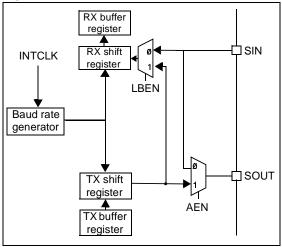

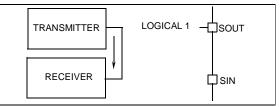

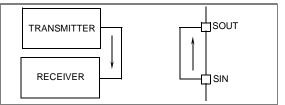

|             | AL COMMUNICATIONS INTERFACE (SCI)    |     |

|             | Introduction                         |     |

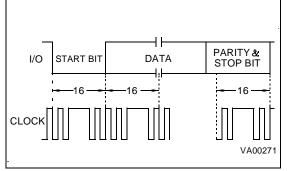

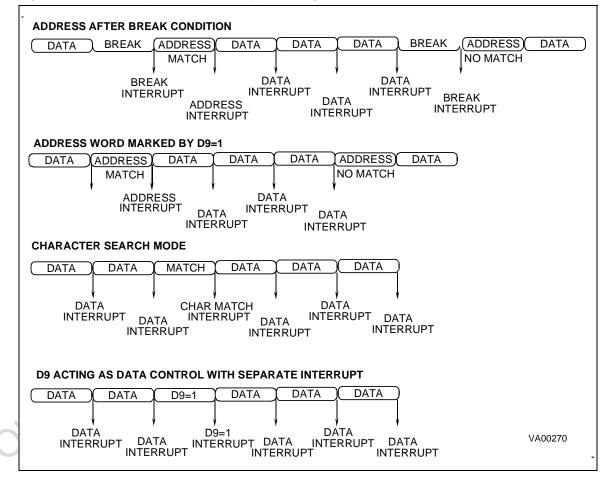

|             | SCI Operation                        |     |

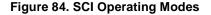

|             | Serial Frame Format                  |     |

| 8.11.4      | Clocks And Serial Transmission Rates | 195 |

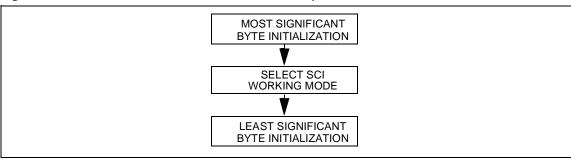

|             | SCI Initialization Procedure         |     |

| 8.11.6      | Input Signals                        | 197 |

|             | Output Signals                       |     |

|             | Interrupts and DMA                   |     |

|             | Register Description                 |     |

|             | AGE SYNTHESIS TUNING CONVERTER (VS)  |     |

|             | Description                          |     |

|             | Output Waveforms                     |     |

|             | Register Description                 |     |

|             | GENERATOR                            |     |

|             | Introduction                         |     |

|             | Register Mapping                     |     |

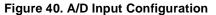

|             | CONVERTER (A/D)                      |     |

|             | Introduction                         |     |

|             | Main Features                        |     |

|             | General Description                  |     |

|             | Register Description                 |     |

|             |                                      |     |

|             | DESCRIPTION                          |     |

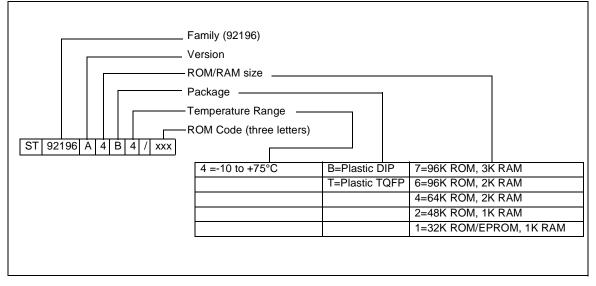

| 11 ORDERING |                                      | 234 |

|             |                                      |     |

| S192E19     | 6A/B & ST92T196A/B                   | 236 |

| 1 GENERAL I | DESCRIPTION                          | 237 |

| 1.1 INTRO   | DUCTION                              | 237 |

| 1.1.1       | Core Architecture                    | 237 |

| 1.1.2       | Instruction Set                      | 237 |

| 1.1.3       | Operating Modes                      | 237 |

|             | On-chip Peripherals                  |     |

| 1.2 PIN D   | ESCRIPTION                           | 240 |

|             |                                      |     |

# ST92196A

| 1.3    | 1.2.2  | I/O Port (<br>I/O Port I<br>IRED EX | Reset St | ate    |      |      |       |     |   | <br> | <br> |     | <br> |     |    | <br>. 241 |

|--------|--------|-------------------------------------|----------|--------|------|------|-------|-----|---|------|------|-----|------|-----|----|-----------|

| 1.4    | MEMC   | ORY MAP                             |          |        |      |      |       |     |   | <br> | <br> |     | <br> |     |    | <br>. 245 |

| 1.5    | ST92E  | 196A/B 8                            | ST92T    | 196A/E | B RE | GIST | rer I | MAP | • | <br> | <br> |     | <br> |     |    | <br>. 246 |

| 2 ELEC | CTRICA |                                     | ACTERI   | STICS  |      |      |       |     |   | <br> | <br> |     | <br> |     |    | <br>252   |

| 3 EPR  | OM/OT  | P PROGR                             |          | G      |      |      |       |     |   | <br> | <br> | • • | <br> |     | •• | <br>. 262 |

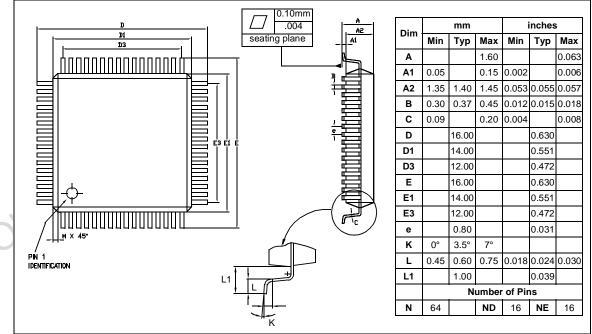

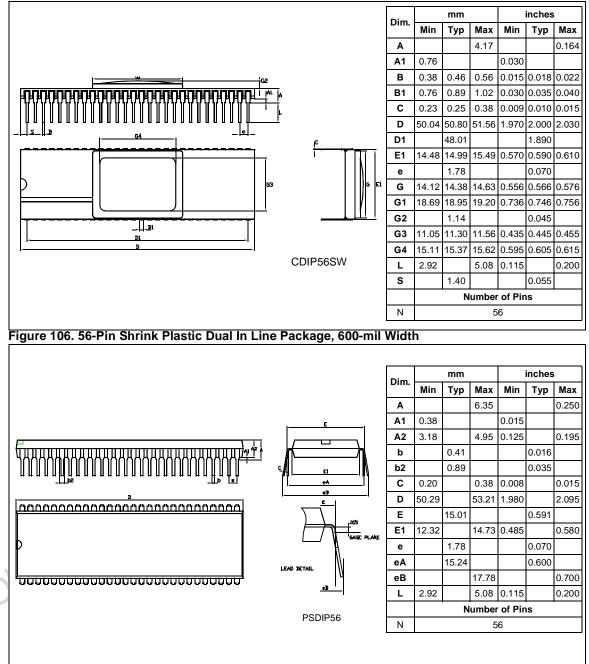

| 4 PAC  | KAGE   | DESCRIP                             | TION     |        |      |      |       |     |   | <br> | <br> |     | <br> |     |    | <br>. 263 |

| 5 ORD  | ERING  | INFORM                              | ATION .  |        |      |      |       |     |   | <br> | <br> |     | <br> | • • |    | <br>. 264 |

| 12 SUN | MMARY  | OF CHA                              | NGES .   |        |      |      |       |     |   | <br> | <br> |     | <br> |     |    | <br>. 266 |

7/<mark>268</mark>

# **1.1 INTRODUCTION**

The ST92196A family brings the enhanced ST9 register-based architecture to a new range of highperformance microcontrollers specifically designed for TV applications. Their performance derives from the use of a flexible 256-register programming model for ultra-fast context switching and real-time event response. The intelligent onchip peripherals offload the ST9 core from I/O and data management processing tasks allowing critical application tasks to get the maximum use of core resources. The ST9 MCU devices support low power consumption and low voltage operation for power-efficient and low-cost embedded systems.

#### **1.1.1 Core Architecture**

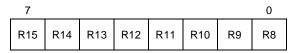

The nucleus of the ST92196A is the enhanced ST9 Core that includes the Central Processing Unit (CPU), the register file, the interrupt and DMA controller.

Three independent buses are controlled by the Core: a 16-bit memory bus, an 8-bit register addressing bus and a 6-bit interrupt/DMA bus which connects the interrupt and DMA controllers in the on-chip peripherals with the core.

This multiple bus architecture makes the ST9 family devices highly efficient for accessing on and off-chip memory and fast exchange of data with the on-chip peripherals.

The general-purpose registers can be used as accumulators, index registers, or address pointers. Adjacent register pairs make up 16-bit registers for addressing or 16-bit processing. Although the ST9 has an 8-bit ALU, the chip handles 16-bit operations, including arithmetic, loads/stores, and memory/register and memory/memory exchanges. Many opcodes specify byte or word operations, the hardware automatically handles 16-bit operations and accesses.

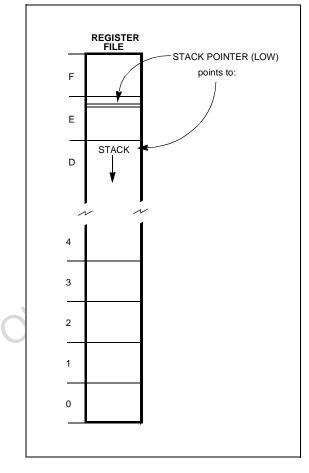

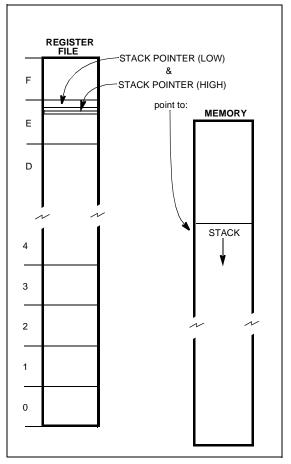

For interrupts or subroutine calls, the CPU uses a system stack in conjunction with the stack pointer (SP). A separate user stack has its own SP. The separate stacks, without size limitations, can be in on-chip RAM (or in Register File) or off-chip memory.

# 1.1.2 Instruction Set

The ST9 instruction set consists of 94 instruction types, including instructions for bit handling, byte (8-bit) and word (16-bit) data, as well as BCD and Boolean formats. Instructions have been added to facilitate large program and data handling through the MMU, as well as to improve the performance and code density of C Function calls. 14 addressing modes are available, including powerful indirect addressing capabilities.

The ST9's bit-manipulation instructions are set, clear, complement, test and set, load, and various logic instructions (AND, OR, and XOR). Math functions include add, subtract, increment, decrement, decimal adjust, multiply, and divide.

# 1.1.3 Operating Modes

To optimize performance versus the power consumption of the device, ST9 devices now support a range of operating modes that can be dynamically selected depending on the performance and functionality requirements of the application at a given moment.

**Run Mode.** This is the full speed execution mode with CPU and peripherals running at the maximum clock speed delivered by the Phase Locked Loop (PLL) of the Clock Control Unit (CCU).

**Slow Mode**. Power consumption can be significantly reduced by running the CPU and the peripherals at reduced clock speed using the CPU Prescaler and CCU Clock Divider.

Wait For Interrupt Mode. The Wait For Interrupt (WFI) instruction suspends program execution until an interrupt request is acknowledged. During WFI, the CPU clock is halted while the peripheral and interrupt controller keep running at a frequency programmable via the CCU. In this mode, the power consumption of the device can be reduced by more than 95% (Low Power WFI).

Halt Mode. When executing the HALT instruction, and if the Watchdog is not enabled, the CPU and its peripherals stop operating and the status of the machine remains frozen (the clock is also stopped). A reset is necessary to exit from Halt mode.

# **INTRODUCTION** (Cont'd)

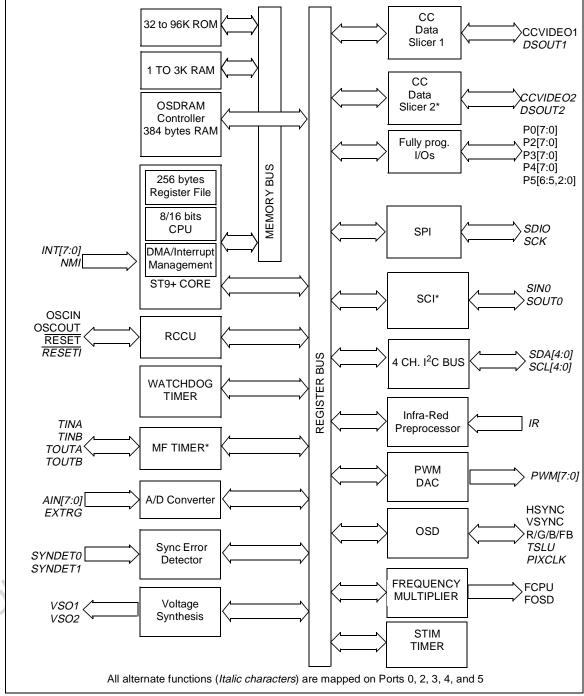

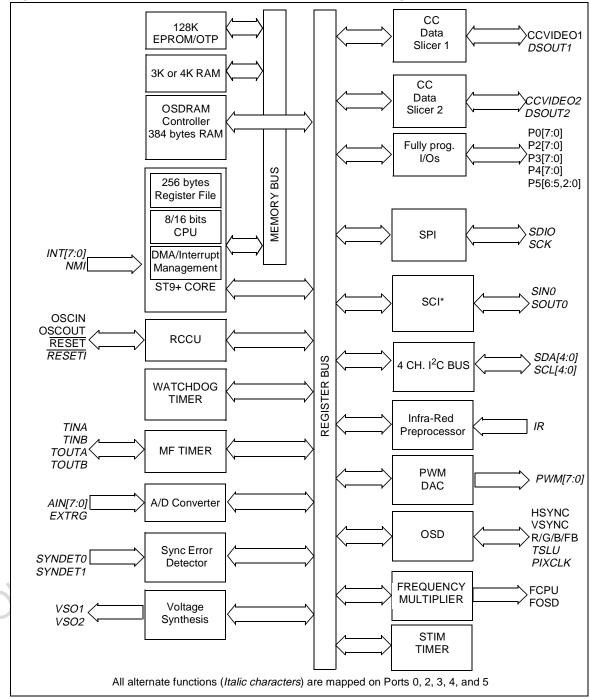

# Figure 1. ST92196A Architectural Block Diagram

\*On some devices only

Note: Not all peripherals are available on all device versions. Please check the Device Summary on page 1.

9/268

# **INTRODUCTION** (Cont'd)

#### 1.1.4 On-chip Peripherals

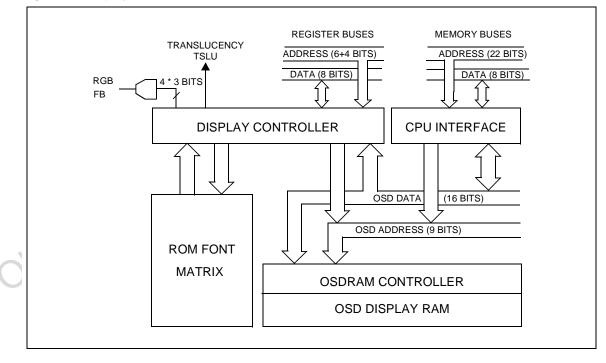

## **OSD** Controller

The On Screen Display displays closed caption or extended service format data received from the on-chip data slicers or any text or menu data generated by the application. Rows of up to 63 characters can be displayed with two user-definable fonts. Colors, character shape and other attributes are software programmable. Support is provided for mouse or other pointing devices.

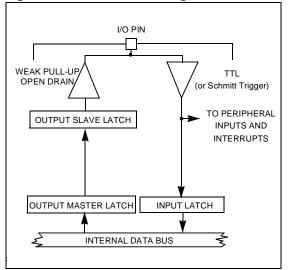

# Parallel I/O Ports

The ST9 is provided with dedicated lines for input/ output. These lines, grouped into 8-bit ports, can be independently programmed to provide parallel input/output or to carry input/output signals to or from the on-chip peripherals and core e.g. SCI and Multifunction Timer. All ports have active pull-ups and pull-down resistors compatible with TTL loads. In addition pull-ups can be turned off for open drain operation and weak pull-ups can be turned on to save chip resistive pull-ups. Input buffers can be either TTL or CMOS compatible.

# **Multifunction Timer**

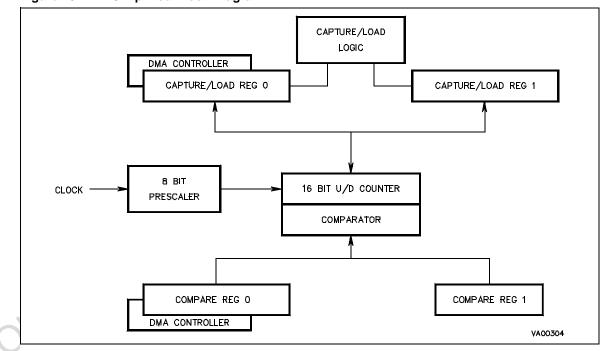

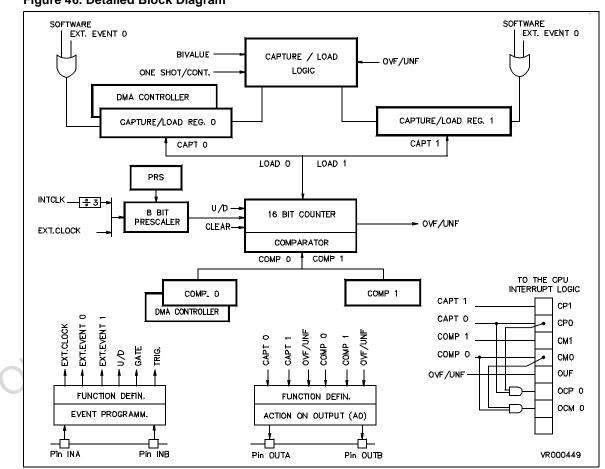

The multifunction timer has a 16-bit Up/Down counter supported by two 16-bit Compare registers and two 16-bit input capture registers. Timing resolution can be programmed using an 8-bit prescaler.

## **Serial Communications Controller**

The SCI provides an asynchronous serial I/O port using two DMA channels. Baud rates and data formats are programmable. Controller applications can further benefit from the self test and address wake-up facility offered by the character search mode.

#### I<sup>2</sup>C Bus Interface

The I<sup>2</sup>C bus is a synchronous serial bus for connecting multiple devices using a data line and a clock line. Multimaster and slave modes are supported. Up to four channels are supported. The I<sup>2</sup>C interface supports 7-bit addressing. It operates in multimaster or slave mode and supports speeds of up to 666.67 kHz. Bus events (Bus busy, slave address recognised) and error conditions are automatically flagged in peripheral registers and interrupts are optionally generated.

## **Analog/Digital Converter**

The ADC provides up to 8 analog inputs with onchip sample and hold. Conversion can be triggered by a signal from the MFT.

# **1.2 PIN DESCRIPTION**

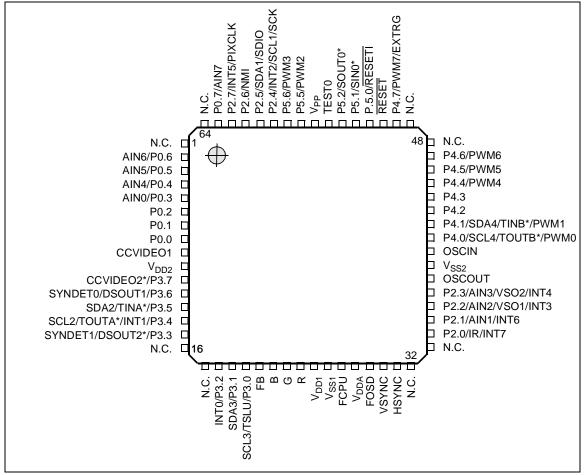

# Figure 2. 64-Pin Thin QFP Package Pin-Out

N.C. = Not connected

\* Not available on some devices.

11/268

## PIN DESCRIPTION (Cont'd)

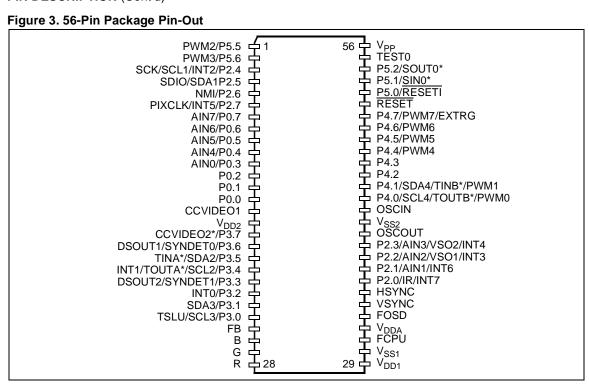

## Figure 3. 56-Pin Package Pin-Out

\* Not available on some devices.

# **Table 1. Power Supply Pins**

| Name             | Function                                                                              | SDIP56 | QFP64 |

|------------------|---------------------------------------------------------------------------------------|--------|-------|

| V <sub>DD1</sub> | Main Power Supply Voltage                                                             | 29     | 25    |

| V <sub>DD2</sub> | (2 pins internally connected)                                                         | 16     | 10    |

| V <sub>SS1</sub> | Analog and Digital Circuit Ground                                                     | 30     | 26    |

| V <sub>SS2</sub> | (2 pins internally connected)                                                         | 41     | 39    |

| V <sub>DDA</sub> | Analog Circuit Supply Voltage                                                         | 32     | 28    |

| V <sub>PP</sub>  | EPROM Programming Voltage.<br>Must be connected to $V_{DD}$ in normal operating mode. | 56     | 56    |

| Name     | Function                                                | SDIP56 | QFP64 |  |  |

|----------|---------------------------------------------------------|--------|-------|--|--|

| OSCIN    | Oscillator input                                        | 42     | 40    |  |  |

| OSCOUT   | Oscillator output                                       | 40     | 38    |  |  |

| RESET    | Reset to initialize the ST9                             | 51     | 51    |  |  |

| HSYNC    | Video Horizontal Sync Input<br>(Schmitt trigger)        | 35     | 31    |  |  |

| VSYNC    | Video Vertical Sync input (Sch-<br>mitt trigger)        |        |       |  |  |

| R        | Red video analog DAC output                             | 28     | 24    |  |  |

| G        | Green video analog DAC output                           | 27     | 23    |  |  |

| В        | Blue video analog DAC output                            | 26     | 22    |  |  |

| FB       | Fast Blanking analog DAC output                         | 25     | 21    |  |  |

| CCVIDEO1 | Closed Caption Composite Video<br>input 1 (2V +/- 3 dB) | 15     | 9     |  |  |

| FCPU     | CPU frequency multiplier filter<br>output               | 31     | 27    |  |  |

| FOSD     | OSD frequency multiplier filter<br>output               | 33     | 29    |  |  |

| TEST0    | Test input (must be tied to V <sub>DD</sub> )           | 55     | 55    |  |  |

**Table 2. Primary Function pins**

#### PIN DESCRIPTION (Cont'd)

#### 1.2.1 I/O Port Configuration

All ports can be individually configured as input, bidirectional, output, or alternate function. Refer to the Port Bit Configuration Table in the I/O Port Chapter.

No I/O pins have any physical weak pull-up capability (they will show no pull-up if they are programmed in the "weak pull-up" software mode).

Input levels can be selected on a bit basis by choosing between TTL or CMOS input levels for I/ O port pin except for P2.(5:4,0), P3.(6:3,1:0), P4.(1:0) which are implemented with a Schmitt trigger function.

All port output configurations can be software selected on a bit basis to provide push-pull or open drain driving capabilities. For all ports, when configured as open-drain, the voltage on the pin must never exceed the  $V_{DD}$  power line value (refer to Electrical characteristics section).

## 1.2.2 I/O Port Reset State

I/Os are reset asynchronously as soon as the  $\overline{\text{RE-}}$  SET pin is asserted low.

All I/O are forced by the Reset in bidirectional, high impedance output due to the lack of physical pullup except P5.0 (refer to the Reset section) which is forced into the "Push-Pull Alternate Function" mode until being reconfigured by software.

#### Warning

When a common pin is declared to be connected to an alternate function input and to an alternate function output, the user must be aware of the fact that the alternate function output signal always inputs to the alternate function module declared as input.

When any given pin is declared to be connected to a digital alternate function input, the user must be aware of the fact that the alternate function input is always connected to the pin. When a given pin is declared to be connected to an analog alternate function input (ADC input for example) and if this pin is programmed in the "AF-OD" mode, the digital input path is disconnected from the pin to prevent any DC consumption.

|              | Input           | Output       | Weak Pull-Up | Reset State      |

|--------------|-----------------|--------------|--------------|------------------|

| Port 0[7:0]  | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

| Port 2.0     | Schmitt trigger | Push-Pull/OD | No           | Bidirectional    |

| Port 2[3:1]  | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

| Port 2[5:4]  | Schmitt trigger | Push-Pull/OD | No           | Bidirectional    |

| Port 2[7:6]  | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

| Port 3.0     | Schmitt trigger | Push-Pull/OD | No           | Bidirectional    |

| Port 3.1     | Schmitt trigger | Push-Pull/OD | No           | Bidirectional    |

| Port 3.2     | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

| Port 3[6:3]  | Schmitt trigger | Push-Pull/OD | No           | Bidirectional    |

| Port 3.7     | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

| Port 4.[1:0] | Schmitt trigger | Push-Pull/OD | No           | Bidirectional    |

| Port 4.[7:2] | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

| Port 5.0     | TTL/CMOS        | Push-Pull/OD | No           | Push-Pull AF Out |

| Port 5[6:1]  | TTL/CMOS        | Push-Pull/OD | No           | Bidirectional    |

#### Table 3. I/O Port Characteristics

Legend: OD = Open Drain, AF = Alternate Function

| Port         | General                               | Pin    | No.    | Alternate Functions |     |                                         |  |  |

|--------------|---------------------------------------|--------|--------|---------------------|-----|-----------------------------------------|--|--|

| Name         | Purpose I/O                           | SDIP56 | TQFP64 |                     |     | Alternate Functions                     |  |  |

| P0.0         |                                       | 14     | 8      |                     | I/O |                                         |  |  |

| P0.1         |                                       | 13     | 7      |                     | I/O |                                         |  |  |

| P0.2         |                                       | 12     | 6      |                     | I/O |                                         |  |  |

| P0.3         |                                       | 11     | 5      | AIN0                | Ι   | A/D Analog Data Input 0                 |  |  |

| P0.4         |                                       | 10     | 4      | AIN4                | Ι   | A/D Analog Data Input 4                 |  |  |

| P0.5         |                                       | 9      | 3      | AIN5                | Ι   | A/D Analog Data Input 5                 |  |  |

| P0.6         |                                       | 8      | 2      | AIN6                | Ι   | A/D Analog Data Input 6                 |  |  |

| P0.7         |                                       | 7      | 63     | AIN7                | Ι   | A/D Analog Data Input 7                 |  |  |

| <b>D</b> 0.0 |                                       |        |        | IR                  | Ι   | IFR Infrared Input                      |  |  |

| P2.0         |                                       | 36     | 34     | INT7                | 1   | External Interrupt 7                    |  |  |

| <b>D</b> 0 4 |                                       |        | 0.5    | AIN1                | Ι   | A/D Analog Data Input 1                 |  |  |

| P2.1         |                                       | 37     | 35     | INT6                | Ι   | External Interrupt 6                    |  |  |

|              |                                       |        | 36     | INT3                | Ι   | External Interrupt 3                    |  |  |

| P2.2         |                                       | 38     |        | AIN2                |     | A/D Analog Data Input 2                 |  |  |

|              |                                       |        |        | VSO1                | 0   | Voltage Synthesis Converter Output 1    |  |  |

|              |                                       |        | 37     | INT4                | Ι   | External Interrupt 4                    |  |  |

| P2.3         |                                       | 39     |        | AIN3                | I   | A/D Analog Data Input 3                 |  |  |

|              | All ports useable<br>for general pur- |        |        | VSO2                | 0   | Voltage Synthesis Converter Output 2    |  |  |

|              | pose I/O (input,                      |        |        | INT2                | I   | External Interrupt 2                    |  |  |

| P2.4         | output or bidi-<br>rectional)         | 3      | 59     | SCL1                | I/O | I <sup>2</sup> C Channel 1 Serial Clock |  |  |

|              | rectionaly                            |        |        | SCK                 | 0   | SPI Serial Clock Output                 |  |  |

| P2.5         |                                       | 4      | 60     | SDIO                | I/O | SPI Serial Data                         |  |  |

| P2.5         |                                       | 4      | 60     | SDA1                | I/O | I <sup>2</sup> C Channel 1 Serial Data  |  |  |

| P2.6         |                                       | 5      | 61     | NMI                 | Ι   | Non Maskable Interrupt Input            |  |  |

| P2.7         |                                       | 6      | 62     | INT5                | Ι   | External Interrupt 5                    |  |  |

| F2./         |                                       | 0      | 02     | PIXCLK              | 0   | Pixel Clock (after divide-by-2) Output  |  |  |

| P3.0         |                                       | 24     | 20     | SCL3                | I/O | I <sup>2</sup> C Channel 3 Serial Clock |  |  |

| F 3.0        |                                       | 24     | 20     | TSLU                | 0   | Translucency Digital Video Output       |  |  |

| P3.1         |                                       | 23     | 19     | SDA3                | I/O | I <sup>2</sup> C Channel 3 Serial Data  |  |  |

| P3.2         | ]                                     | 22     | 18     | INT0                | Ι   | External Interrupt 0                    |  |  |

| P3.3         |                                       | 21     | 15     | SYNDET1             | Ι   | Sync Error Detector Input 1             |  |  |

| 1 0.0        |                                       | 21     | 15     | DSOUT2*             | 0   | Data Slicer Comparator Output 2         |  |  |

|              |                                       |        |        | INT1                | Ι   | External Interrupt 1                    |  |  |

| P3.4         |                                       | 20     | 14     | SCL2                | I/O | I <sup>2</sup> C Channel 2 Serial Clock |  |  |

|              |                                       |        |        | TOUTA*              | 0   | MFT Timer output A                      |  |  |

| P3.5         |                                       | 19     | 13     | TINA*               | Ι   | MFT Timer input A                       |  |  |

| 10.0         |                                       | 13     | 13     | SDA2                | I/O | I <sup>2</sup> C Channel 2 Serial Data  |  |  |

# Table 4. I/O Port Alternate Functions

| Port  | General                             | Pin    | No.    |           |                     | Alternate Functions                                  |  |  |  |

|-------|-------------------------------------|--------|--------|-----------|---------------------|------------------------------------------------------|--|--|--|

| Name  | Purpose I/O                         | SDIP56 | TQFP64 |           | Alternate Functions |                                                      |  |  |  |

| P3.6  |                                     | 18     | 12     | SYNDET0   | Ι                   | Sync Error Detector Input 0                          |  |  |  |

| F 3.0 |                                     | 10     | 12     | DSOUT1    | 0                   | Data Slicer Comparator Output 1                      |  |  |  |

| P3.7  |                                     | 17     | 11     | CCVIDEO2* | I                   | Closed Caption Composite Video input 1 (2V +/- 3 dB) |  |  |  |

|       |                                     |        |        | SCL4      | I/O                 | I <sup>2</sup> C Channel 4 Serial Clock              |  |  |  |

| P4.0  |                                     | 43     | 41     | TOUTB*    | 0                   | MFT Timer output B                                   |  |  |  |

|       |                                     |        |        | PWM0      | 0                   | PWM D/A Converter Output 0                           |  |  |  |

|       |                                     |        |        | TINB*     | Ι                   | MFT Timer input B                                    |  |  |  |

| P4.1  |                                     | 44     | 42     | SDA4      | I/O                 | I <sup>2</sup> C Channel 4 Serial Data               |  |  |  |

|       | All ports useable                   |        |        | PWM1      | 0                   | PWM D/A Converter Output 1                           |  |  |  |

| P4.2  | for general pur-                    | 45     | 43     |           | I/O                 |                                                      |  |  |  |

| P4.3  | pose I/O (input,<br>output or bidi- | 46     | 44     |           | I/O                 |                                                      |  |  |  |

| P4.4  | rectional)                          | 47     | 45     | PWM4      | 0                   | PWM D/A Converter Output 4                           |  |  |  |

| P4.5  |                                     | 48     | 46     | PWM5      | 0                   | PWM D/A Converter Output 5                           |  |  |  |

| P4.6  |                                     | 49     | 47     | PWM6      | 0                   | PWM D/A Converter Output 6                           |  |  |  |

| P4.7  |                                     | 50     | 50     | EXTRG     | Ι                   | A/D Converter External Trigger Input                 |  |  |  |

| F4.7  |                                     | 50     | 50     | PWM7      | 0                   | PWM D/A Converter Output 7                           |  |  |  |

| P5.0  |                                     | 52     | 52     | RESETI    | 0                   | Internal Delayed Reset Output                        |  |  |  |

| P5.1  |                                     | 53     | 53     | SIN0*     | I                   | SCI Serial Comm. Interface Input                     |  |  |  |

| P5.2  |                                     | 54     | 54     | SOUT0*    | 0                   | SCI Serial Comm. Interface Output                    |  |  |  |

| P5.5  |                                     | 1      | 57     | PWM2      | 0                   | PWM D/A Converter Output 2                           |  |  |  |

| P5.6  |                                     | 2      | 58     | PWM3      | 0                   | PWM D/A Converter Output 3                           |  |  |  |

\* Not available on some devices.

15/268

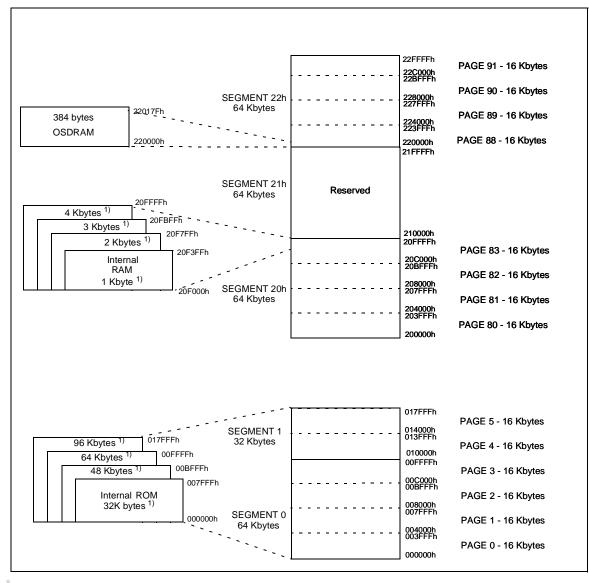

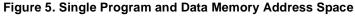

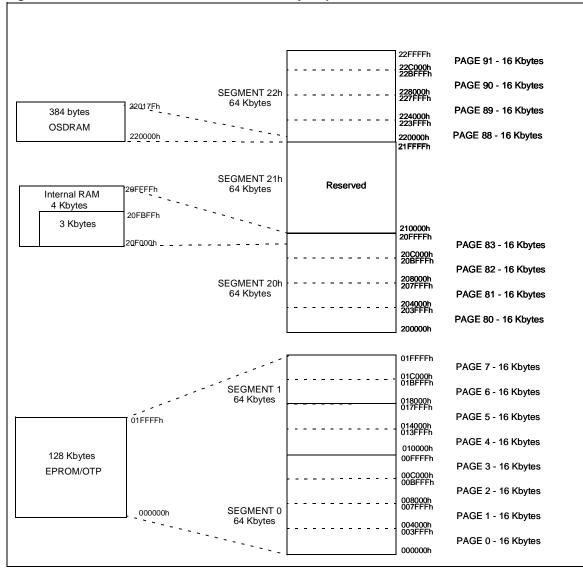

# **1.4 MEMORY MAP**

# Figure 4. ST92196A Memory Map

**Note 1:** ROM and RAM sizes are product dependent, refer to the Ordering Information section on page 234.

17/268

# 1.5 ST92196A REGISTER MAP

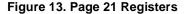

Table 6 contains the map of the group F peripheral pages.

The common registers used by each peripheral are listed in Table 5.

Be very careful to correctly program both:

- The set of registers dedicated to a particular function or peripheral.

- Registers common to other functions.

- In particular, double-check that any registers with "undefined" reset values have been correctly initialised.

**Warning**: Note that in the **EIVR** and each **IVR** register, all bits are significant. Take care when defining base vector addresses that entries in the Interrupt Vector table do not overlap.

# Table 5. Common Registers

| Function or Peripheral | Common Registers                                                   |

|------------------------|--------------------------------------------------------------------|

| SCI, MFT               | CICR + NICR + DMA REGISTERS + I/O PORT REGISTERS                   |

| ADC                    | CICR + NICR + I/O PORT REGISTERS                                   |

| WDT                    | CICR + NICR + EXTERNAL INTERRUPT REGISTERS +<br>I/O PORT REGISTERS |

| I/O PORTS              | I/O PORT REGISTERS + MODER                                         |

| EXTERNAL INTERRUPT     | INTERRUPT REGISTERS + I/O PORT REGISTERS                           |

| RCCU                   | INTERRUPT REGISTERS + MODER                                        |

# ST92196A REGISTER MAP (Cont'd)

# Table 6. Group F Pages Register Map

Resources available on the ST92196A device:

| Register |      |           |           |      |      |      |     | Pa      | ige   |             |      |      |      |      |      |      |  |

|----------|------|-----------|-----------|------|------|------|-----|---------|-------|-------------|------|------|------|------|------|------|--|

|          | 0    | 2         | 3         | 9    | 10   | 11   | 21  | 24      | 42    | 43          | 44   | 45   | 46   | 55   | 59   | 62   |  |

| R255     | Res. | Res.      |           |      |      |      |     |         |       | Res.        |      |      |      |      | VS   |      |  |

| R254     | SPI  |           |           |      |      |      |     | Res.    | тсс   |             |      |      |      | v3   |      |      |  |

| R253     | 591  | Port<br>3 |           |      |      |      |     |         |       | 100         |      |      |      |      | Res. |      |  |

| R252     | WCR  |           |           | Res. |      |      |     |         |       | Res.        |      | Res. | Res. |      |      |      |  |

| R251     |      | Res.      | Res.      |      |      |      |     |         |       | 1.63.       | Res. | 100. |      | Res. |      |      |  |

| R250     | WDT  |           |           |      |      |      |     |         |       | IR/         |      |      |      |      |      |      |  |

| R249     | WBT  | Port<br>2 |           |      |      | Res. |     |         | OSD   | SYNC<br>ERR |      |      |      |      |      | Res. |  |

| R248     |      |           |           | MFT  | MFT  |      | MMU | SCI0    |       | LIUX        |      |      |      |      |      |      |  |

| R247     |      |           |           |      |      |      |     | iiiiiio |       |             |      |      |      |      |      |      |  |

| R246     |      |           |           | Res. |      |      |     |         |       |             |      |      |      |      | PWM  |      |  |

| R245     | EXT  | Res.      | Port<br>5 |      |      |      |     |         |       |             |      |      |      |      |      |      |  |

| R244     | INT  |           |           |      |      |      |     |         |       | Res.        |      | DS0  | DS1  |      |      |      |  |

| R243     |      |           | Res.      |      |      |      |     |         | Res.  |             | I2C  |      |      | RCCU |      |      |  |

| R242     |      |           |           | MFT  |      | STIM |     |         | 1.65. |             | 120  |      |      |      |      |      |  |

| R241     | Res. | Port<br>0 | Port<br>4 |      | STIM |      |     |         |       |             |      |      |      |      |      | ADC  |  |

| R240     | 1.62 |           |           |      |      |      |     |         |       |             |      |      |      |      |      |      |  |

19/268

# ST92196A REGISTER MAP (Cont'd)

# Table 7. Detailed Register Map

| Group F<br>Page Block<br>Dec. |      | Reg.<br>No. | Register<br>Name                | Description                            | Reset<br>Value<br>Hex. | Doc.<br>Page |

|-------------------------------|------|-------------|---------------------------------|----------------------------------------|------------------------|--------------|

|                               |      | R224        | P0DR                            | Port 0 Data Register                   | FF                     |              |

|                               | I/O  | R226        | P2DR                            | Port 2 Data Register                   | FF                     |              |

|                               | Port | R227        | P3DR                            | Port 3 Data Register                   | FF                     | 69           |

|                               | 0:5  | R228        | P4DR                            | Port 4 Data Register                   | FF                     |              |

|                               |      | R229        | P5DR                            | Port 5 Data Register                   | FF                     |              |

|                               |      | R230        | CICR                            | Central Interrupt Control Register     | 87                     | 27           |

|                               |      | R231        | FLAGR                           | Flag Register                          | 00                     | 28           |

| N/A                           |      | R232        | RP0                             | Pointer 0 Register                     | 00                     | 30           |

|                               |      | R233        | RP1                             | Pointer 1 Register                     | 00                     | 30           |

|                               |      | R234        | PPR                             | Page Pointer Register                  | 54                     | 32           |

|                               | Core | R235        | MODER                           | Mode Register                          | E0                     | 32           |

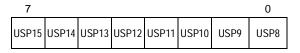

|                               |      | R236        | USPHR                           | User Stack Pointer High Register       | ХХ                     | 34           |

|                               | R237 | USPLR       | User Stack Pointer Low Register | ХХ                                     | 34                     |              |

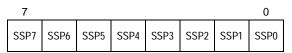

|                               | R238 | SSPHR       | System Stack Pointer High Reg.  | ХХ                                     | 34                     |              |

|                               |      | R239        | SSPLR                           | System Stack Pointer Low Reg.          | ХХ                     | 34           |

|                               |      | R242        | EITR                            | External Interrupt Trigger Register    | 00                     | 56           |

|                               |      | R243        | EIPR                            | External Interrupt Pending Reg.        | 00                     | 56           |

|                               |      | R244        | EIMR                            | External Interrupt Mask-bit Reg.       | 00                     | 56           |

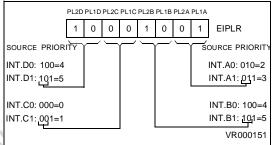

|                               | INT  | R245        | EIPLR                           | External Interrupt Priority Level Reg. | FF                     | 57           |

|                               |      | R246        | EIVR                            | External Interrupt Vector Register     | x6                     | 57           |

|                               |      | R247        | NICR                            | Nested Interrupt Control               | 00                     | 57           |

| 0                             |      | R248        | WDTHR                           | Watchdog Timer High Register           | FF                     | 81           |

|                               |      | R249        | WDTLR                           | Watchdog Timer Low Register            | FF                     | 81           |

|                               | WDT  | R250        | WDTPR                           | Watchdog Timer Prescaler Reg.          | FF                     | 81           |

|                               |      | R251        | WDTCR                           | Watchdog Timer Control Register        | 12                     | 81           |

|                               |      | R252        | WCR                             | Wait Control Register                  | 7F                     | 82           |

|                               |      | R253        | SPIDR                           | SPI Data Register                      | xx                     | 190          |

|                               | SPI  | R254        | SPICR                           | SPI Control Register                   | 00                     | 190          |

|                               | I/O  | R240        | P0C0                            | Port 0 Configuration Register 0        | 00                     |              |

|                               | Port | R241        | P0C1                            | Port 0 Configuration Register 1        | 00                     | 1            |

|                               | 0    | R242        | P0C2                            | Port 0 Configuration Register 2        | 00                     | 1            |

| •                             | I/O  | R248        | P2C0                            | Port 2 Configuration Register 0        | 00                     | 1            |

| 2                             | Port | R249        | P2C1                            | Port 2 Configuration Register 1        | 00                     | 69           |

|                               | 2    | R250        | P2C2                            | Port 2 Configuration Register 2        | 00                     |              |

|                               | I/O  | R252        | P3C0                            | Port 3 Configuration Register 0        | 00                     | 1            |

|                               | Port | R253        | P3C1                            | Port 3 Configuration Register 1        | 00                     | 1            |

|                               | 3    | R254        | P3C2                            | Port 3 Configuration Register 2        | 00                     | 1            |

| Group F<br>Page Block<br>Dec. |       | Reg. Register<br>No. Name |         | Description                       | Reset<br>Value<br>Hex. | Doc.<br>Page |

|-------------------------------|-------|---------------------------|---------|-----------------------------------|------------------------|--------------|

|                               | I/O   | R240                      | P4C0    | Port 4 Configuration Register 0   | 00                     |              |

|                               | Port  | R241                      | P4C1    | Port 4 Configuration Register 1   | 00                     |              |

| 0                             | 4     | R242                      | P4C2    | Port 4 Configuration Register 2   | 00                     |              |

| 3                             | I/O   | R244                      | P5C0    | Port 5 Configuration Register 0   | 00                     | 69           |

|                               | Port  | R245                      | P5C1    | Port 5 Configuration Register 1   | 00                     |              |

|                               | 5     | R246                      | P5C2    | Port 5 Configuration Register 2   | 00                     |              |

|                               |       | R240                      | DCPR    | DMA Counter Pointer Register      | XX                     | 108          |

|                               |       | R241                      | DAPR    | DMA Address Pointer Register      | XX                     | 109          |

| 9                             |       | R242                      | T_IVR   | Interrupt Vector Register         | xx                     | 109          |

|                               |       | R243                      | IDCR    | Interrupt/DMA Control Register    | C7                     | 110          |

|                               |       | R248                      | IOCR    | I/O Connection Register           | FC                     | 110          |

|                               |       | R240                      | REG0HR  | Capture Load Register 0 High      | ХХ                     | 101          |

|                               |       | R241                      | REG0LR  | Capture Load Register 0 Low       | хх                     | 101          |

|                               |       | R242                      | REG1HR  | Capture Load Register 1 High      | XX                     | 101          |

|                               |       | R243                      | REG1LR  | Capture Load Register 1 Low       | ХХ                     | 101          |

|                               |       | R244                      | CMP0HR  | Compare 0 Register High           | 00                     | 101          |

|                               | MFT   | R245                      | CMP0LR  | Compare 0 Register Low            | 00                     | 101          |

|                               |       | R246                      | CMP1HR  | Compare 1 Register High           | 00                     | 101          |

| 10                            |       | R247                      | CMP1LR  | Compare 1 Register Low            | 00                     | 101          |

| 10                            |       | R248                      | TCR     | Timer Control Register            | 0x                     | 102          |

|                               |       | R249                      | TMR     | Timer Mode Register               | 00                     | 103          |

|                               |       | R250                      | T_ICR   | External Input Control Register   | 0x                     | 104          |

|                               |       | R251                      | PRSR    | Prescaler Register                | 00                     | 104          |

|                               |       | R252                      | OACR    | Output A Control Register         | хх                     | 105          |

|                               |       | R253                      | OBCR    | Output B Control Register         | XX                     | 106          |

|                               |       | R254                      | T_FLAGR | Flags Register                    | 00                     | 107          |

|                               |       | R255                      | IDMR    | Interrupt/DMA Mask Register       | 00                     | 108          |

|                               |       | R240                      | STH     | Counter High Byte Register        | FF                     | 86           |

| 4.4                           | OTIM  | R241                      | STL     | Counter Low Byte Register         | FF                     | 86           |

| 11                            | STIM  | R242                      | STP     | Standard Timer Prescaler Register | FF                     | 86           |

|                               |       | R243                      | STC     | Standard Timer Control Register   | 14                     | 86           |

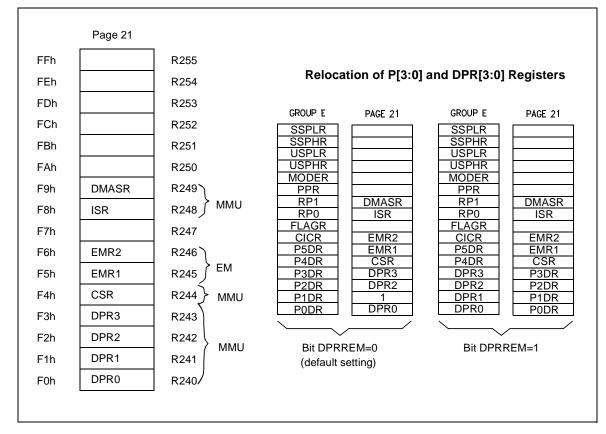

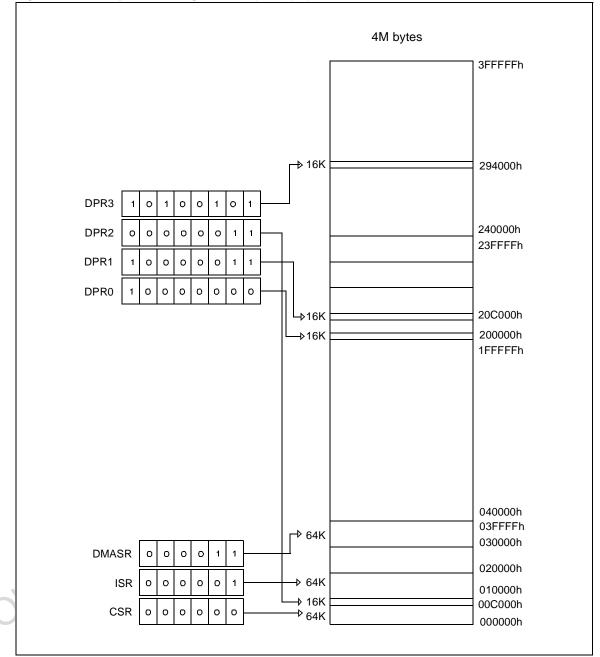

|                               |       | R240                      | DPR0    | Data Page Register 0              | 00                     | 39           |

|                               |       | R241                      | DPR1    | Data Page Register 1              | 01                     | 39           |

|                               |       | R242                      | DPR2    | Data Page Register 2              | 02                     | 39           |

|                               | MMU   | R243                      | DPR3    | Data Page Register 3              | 83                     | 39           |

| 21                            |       | R244                      | CSR     | Code Segment Register             | 00                     | 40           |

|                               |       | R248                      | ISR     | Interrupt Segment Register        | x0                     | 40           |

|                               |       | R249                      | DMASR   | DMA Segment Register              | x0                     | 40           |

|                               | EXTMI | R246                      | EMR2    | External Memory Register 2        | 0F                     | 58           |

| Group F<br>Page<br>Dec. | Block          | Reg. Register<br>No. Name |                                   | Description                                 | Reset<br>Value<br>Hex. | Doc.<br>Page |

|-------------------------|----------------|---------------------------|-----------------------------------|---------------------------------------------|------------------------|--------------|

|                         |                | R240                      | RDCPR                             | Receiver DMA Transaction Counter Pointer    | ХХ                     | 201          |

|                         |                | R241                      | RDAPR                             | Receiver DMA Source Address Pointer         | ХХ                     | 201          |

|                         |                | R242                      | TDCPR                             | Transmitter DMA Transaction Counter Pointer | ХХ                     | 201          |

|                         |                | R243                      | TDAPR                             | Transmitter DMA Destination Address Pointer | xx                     | 201          |

|                         |                | R244                      | S_IVR                             | Interrupt Vector Register                   | ХХ                     | 202          |

|                         |                | R245                      | ACR Address/Data Compare Register |                                             | хх                     | 203          |

|                         |                | R246                      | IMR                               | Interrupt Mask Register                     | x0                     | 203          |

| 24 SCI0                 |                | R247                      | S_ISR                             | Interrupt Status Register                   | ХХ                     | 204          |

|                         |                | R248                      | RXBR                              | Receive Buffer Register                     | xx                     | 205          |

|                         |                | R248                      | TXBR                              | Transmitter Buffer Register                 | хх                     | 205          |

|                         |                | R249                      | IDPR                              | Interrupt/DMA Priority Register             | xx                     | 206          |

|                         |                |                           | CHCR                              | Character Configuration Register            | xx                     | 207          |

|                         |                |                           | CCR                               | Clock Configuration Register                | 00                     | 207          |

|                         |                |                           | BRGHR                             | Baud Rate Generator High Reg.               | xx                     | 208          |

|                         |                | R253                      | BRGLR                             | Baud Rate Generator Low Register            | xx                     | 208          |

|                         |                | R254                      | SICR                              | Input Control                               | 03                     | 208          |

|                         |                | R255 SOCR                 |                                   | Output Control                              | 01                     | 208          |

|                         |                | R246                      | OSDBCR2                           | Border Color Register 2                     | x0                     | 152          |

|                         |                | R247                      | OSDBCR1                           | Border Color Register 1                     | x0                     | 152          |

|                         |                | R248                      | OSDER                             | Enable Register                             | 00                     | 153          |

| 42                      | OSD            | R249                      | OSDDR                             | Delay Register                              | xx                     | 156          |

|                         |                | R250                      | OSDFBR                            | Flag Bit Register                           | xx                     | 157          |

|                         |                | R251                      | OSDSLR                            | Scan Line Register                          | xx                     | 158          |

|                         |                | R252                      | OSDMR                             | Mute Register                               | xx                     | 158          |

|                         |                | R248                      | IRPR                              | Infrared Pulse Register                     | 00                     | 169          |

|                         | IR/SYNC<br>ERR | R249                      | SYNCER                            | Sync Error Register                         | 00                     | 168          |

| 43                      |                | R250                      | IRSCR                             | Infrared / Sync Control Register            | 00                     | 168          |

|                         |                | R253                      | MCCR                              | Main Clock Control Register                 | 00                     | 69           |

|                         | TCC            | R254                      | SKCCR                             | Skew Clock Control Register                 | 00                     | 69           |

|                         |                | R240                      | I2COAR                            | Own Address Register                        | 00                     | 175          |

|                         |                | R241                      | I2CFQR                            | Frequency Register                          | 00                     | 176          |

|                         | 100            | R242                      | I2CCTR                            | Control Register                            | 01                     | 177          |

| 44                      | I2C            | R243                      | I2CDR                             | Data Register                               | 00                     | 178          |

|                         |                | R244                      | I2CSTR2                           | Status Register 2                           | 00                     | 178          |

|                         |                | R245                      | I2CSTR1                           | Status Register 1                           | 00                     | 179          |

| Group F<br>Page<br>Dec. | Block | Reg.<br>No. | Register<br>Name              | Description                    | Reset<br>Value<br>Hex. | Doc.<br>Page |

|-------------------------|-------|-------------|-------------------------------|--------------------------------|------------------------|--------------|

|                         |       | R240        | DS0DR1                        | Data Register 1                | 00                     | 164          |

|                         |       | R241        | DS0DR2                        | Data Register 2                | 00                     | 164          |

|                         |       | R242        | DS0DR3                        | Data Register 3                | 00                     | 164          |

| 45                      | DS0   | R243        | DS0DR4                        | Data Register 4                | 00                     | 165          |

|                         |       | R244        | DS0CR1                        | Control Register 1             | 00                     | 165          |

|                         |       | R245        | 245 DS0CR2 Control Register 2 |                                | 00                     | 165          |

|                         |       | R246        | DS0MR                         | Monitor Register               | 00                     | 166          |

|                         |       | R240        | DS1DR1                        | Data Register 1                | 00                     | 164          |

|                         |       | R241        | DS1DR2                        | Data Register 2                | 00                     | 164          |

|                         |       | R242        | DS1DR3                        | Data Register 3                | 00                     | 164          |

| 46                      | DS1   | R243        | DS1DR4                        | Data Register 4                | 00                     | 165          |

|                         |       | R244        | DS1CR1                        | Control Register 1             | 00                     | 165          |

|                         |       | R245        | DS1CR2                        | Control Register 2             | 00                     | 165          |

|                         |       | R246        | DS1MR                         | Monitor Register               | 00                     | 166          |

|                         |       | R240        | CLKCTL                        | Clock Control Register         | 00                     | 64           |

| 55                      | RCCU  | R242        | CLK_FLAG                      | Clock Flag Register            | 48, 28<br>or 08        | 64           |

|                         |       | R240        | CM0                           | Compare Register 0             | 00                     | 216          |

|                         |       | R241        | CM1                           | Compare Register 1             | 00                     | 216          |

|                         |       | R242        | CM2                           | Compare Register 2             | 00                     | 216          |

|                         |       | R243        | CM3                           | Compare Register 3             | 00                     | 216          |

|                         |       | R244        | CM4                           | Compare Register 4             | 00                     | 216          |

|                         |       | R245        | CM5                           | Compare Register 5             | 00                     | 216          |

|                         | PWM   | R246        | CM6                           | Compare Register 6             | 00                     | 216          |

| 59                      |       | R247        | CM7                           | Compare Register 7             | 00                     | 216          |

|                         |       | R248        | ACR                           | Autoclear Register             | FF                     | 217          |

|                         |       | R249        | CCR                           | Counter Register               | 00                     | 217          |

|                         |       | R250        | PCTL                          | Prescaler and Control Register | 0C                     | 217          |

|                         |       | R251        | OCPL                          | Output Complement Register     | 00                     | 218          |

|                         |       | R252        | OER                           | Output Enable Register         | 00                     | 218          |

|                         |       | R254        | VSDR1                         | Data and Control Register 1    | 00                     | 213          |

|                         | VS    | R255        | VSDR2                         | Data Register 2                | 00                     | 213          |

|                         |       | R240        | ADDTR                         | Channel i Data Register        | хх                     | 221          |

| 62                      | ADC   | R241        | ADCLR                         | Control Logic Register         | 00                     | 221          |

|                         |       | R242        | ADINT                         | AD Interrupt Register          | 01                     | 222          |

Note: xx denotes a byte with an undefined value, however some of the bits may have defined values. Refer to register description for details.

# 2.1 CORE ARCHITECTURE

The ST9 Core or Central Processing Unit (CPU) features a highly optimised instruction set, capable of handling bit, byte (8-bit) and word (16-bit) data, as well as BCD and Boolean formats; 14 addressing modes are available.

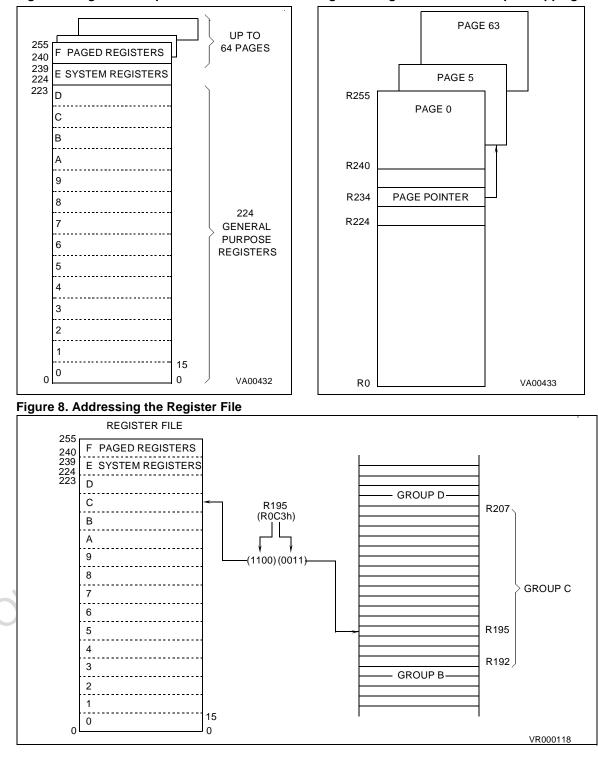

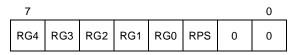

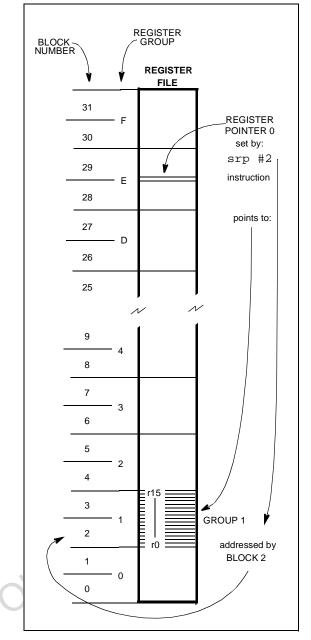

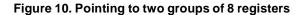

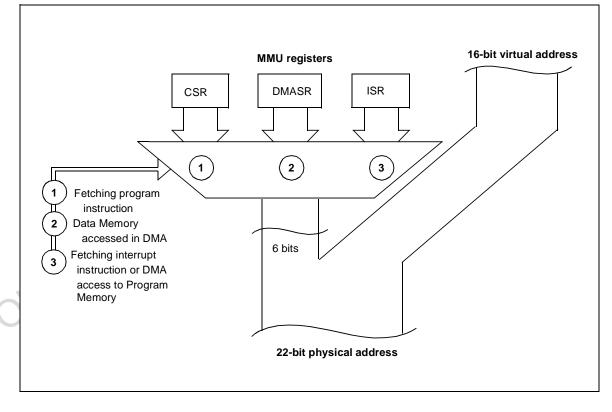

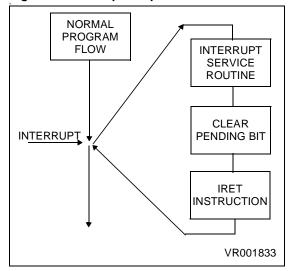

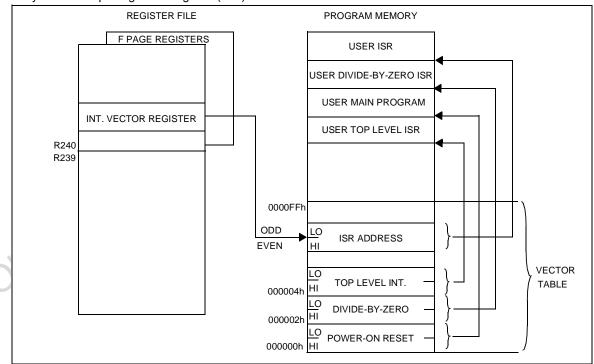

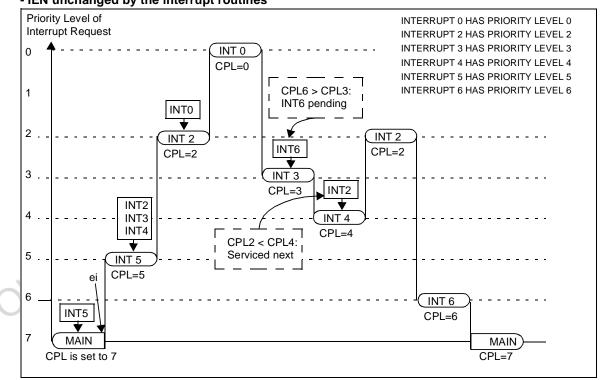

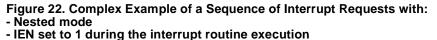

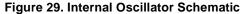

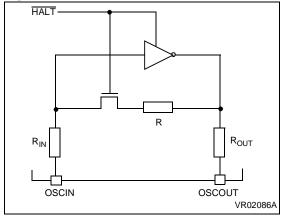

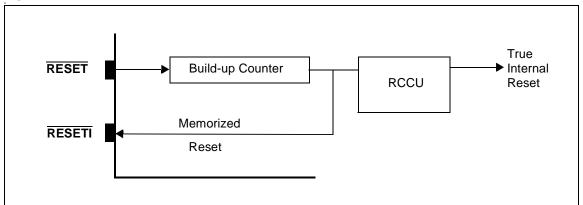

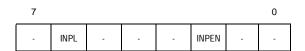

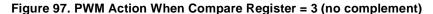

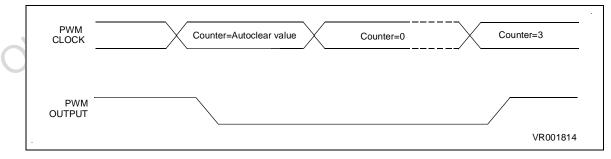

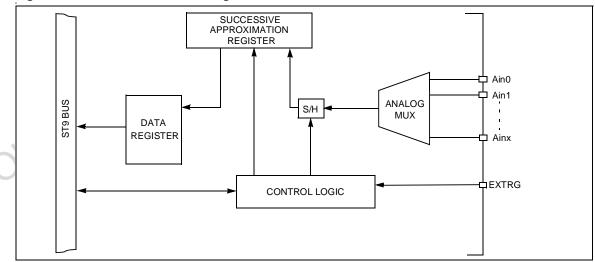

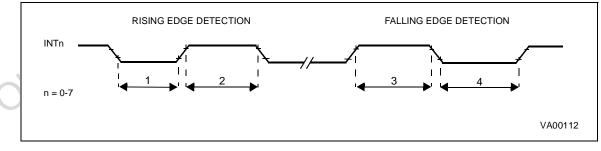

Four independent buses are controlled by the Core: a 16-bit Memory bus, an 8-bit Register data bus, an 8-bit Register address bus and a 6-bit Interrupt/DMA bus which connects the interrupt and DMA controllers in the on-chip peripherals with the Core.