# **QST108**

# Capacitive touch sensor device 8 keys with individual key state outputs or I2C interface

#### **Features**

- Patented charge-transfer design

- Up to 8 independent QTouch<sup>™</sup> keys supported

- Individual key state outputs or I<sup>2</sup>C interface

- Fully "debounced" results

- Patented AKS™ Adjacent Key Suppression

- Self-calibration and auto drift compensation

- Spread-spectrum bursts to reduce EMI

- Up to 5 general-purpose outputs

- ECOPACK® (RoHS compliant) package

### **Applications**

This device specifically targets human interfaces and front panels for a wide range of applications such as PC peripherals, home entertainment systems, gaming devices, lighting and appliance controls, remote controls, etc.

QST devices are designed to replace mechanical switching/control devices and the reduced number of moving parts in the end product provides the following advantages:

- Lower customer service costs

- Reduced manufacturing costs

- Increased product lifetime

# **Description**

The QST108 is the ideal solution for the design of capacitive touch sensing user interfaces.

Touch-sensitive controls are increasingly replacing electromechanical switches in home appliances, consumer and mobile electronics, and in computers and peripherals. Capacitive touch controls allow designers to create stylish, functional, and economical designs which are highly valued by consumers, often at lower cost than the electromechanical solutions they replace.

The QST108 QTouch™ sensor IC is a pure digital solution based on Quantum's patented charge-transfer (QProx™) capacitive technology.

QTouch<sup>™</sup> and QProx<sup>™</sup> are trademarks of the Quantum Research Group.

Table 1. Device summary

| Feature                  | Order code                                                 |

|--------------------------|------------------------------------------------------------|

| reature                  | QST108KT6                                                  |

| Operating supply voltage | 2.4 to 5.5 V                                               |

| Supported interfaces     | Individual key state outputs or I <sup>2</sup> C Interface |

| Operating temperature    | -40° to +85° C                                             |

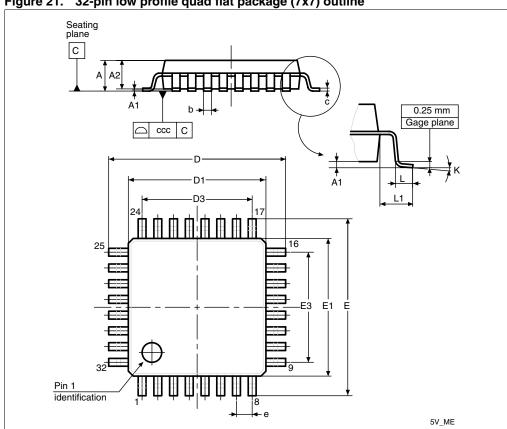

| Package                  | LQFP32 (7x7 mm)                                            |

November 2007 Rev 4 1/47

Contents QST108

# **Contents**

| 1 | Devi  | ce overview5                                                                                                                                                                                                                      |

|---|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Pin d | lescription 6                                                                                                                                                                                                                     |

| 3 | QST   | touch sensing technology 8                                                                                                                                                                                                        |

|   | 3.1   | Functional description 8                                                                                                                                                                                                          |

|   | 3.2   | Spread-spectrum operation                                                                                                                                                                                                         |

|   | 3.3   | Faulty and unused keys 9                                                                                                                                                                                                          |

|   | 3.4   | Detection threshold levels                                                                                                                                                                                                        |

|   | 3.5   | Detection integrator filter                                                                                                                                                                                                       |

|   | 3.6   | Self-calibration                                                                                                                                                                                                                  |

|   | 3.7   | Fast positive recalibration                                                                                                                                                                                                       |

|   | 3.8   | Forced key recalibration                                                                                                                                                                                                          |

|   | 3.9   | Max On-Duration                                                                                                                                                                                                                   |

|   | 3.10  | Drift compensation                                                                                                                                                                                                                |

|   | 3.11  | Adjacent key suppression (AKS™)                                                                                                                                                                                                   |

| 4 | Devi  | ce operating modes                                                                                                                                                                                                                |

|   | 4.1   | Reset and power-up 12                                                                                                                                                                                                             |

|   | 4.2   | Burst operation                                                                                                                                                                                                                   |

|   | 4.3   | Low power mode                                                                                                                                                                                                                    |

|   | 4.4   | Mode selection                                                                                                                                                                                                                    |

|   | 4.5   | Stand-alone mode                                                                                                                                                                                                                  |

|   | 4.6   | 4.5.1       Main features       14         4.5.2       KOUT outputs       15         4.5.3       Option descriptions       16         I2C mode       18                                                                           |

|   |       | 4.6.1       Main features       18         4.6.2       General-purpose outputs       19         4.6.3       IRQ pin       19         4.6.4       Communication packet       19         4.6.5       I2C address selection       20 |

|   | 4.7   | Supported commands 20                                                                                                                                                                                                             |

QST108 Contents

| 5 | Desi | n guidelines                          | 27             |  |  |  |  |

|---|------|---------------------------------------|----------------|--|--|--|--|

|   | 5.1  | C <sub>S</sub> sense capacitor        | 27             |  |  |  |  |

|   | 5.2  | Sensitivity tuning                    | 27             |  |  |  |  |

|   |      | 5.2.1 Increasing sensitivity          | 27<br>27       |  |  |  |  |

|   | 5.3  | Power supply                          |                |  |  |  |  |

|   | 5.4  | ESD protection                        |                |  |  |  |  |

|   | 5.5  | Crosstalk precautions                 | 28             |  |  |  |  |

|   | 5.6  | PCB layout and construction           |                |  |  |  |  |

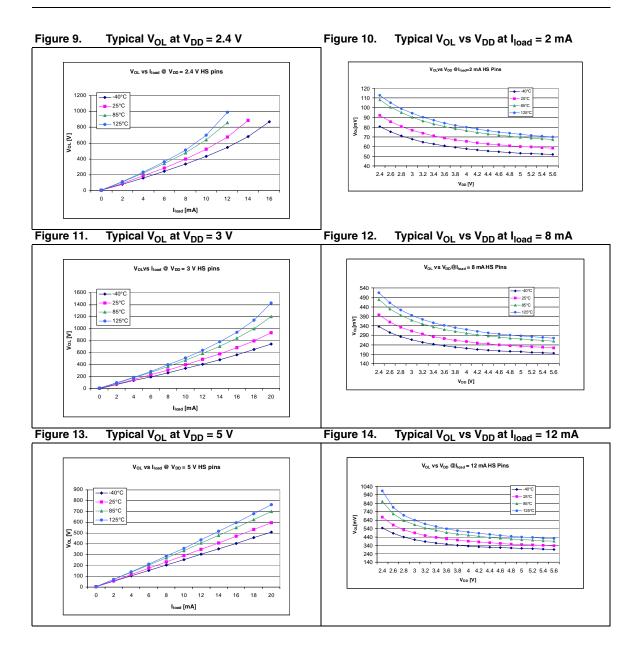

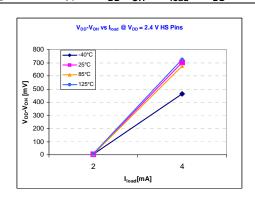

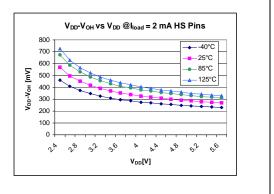

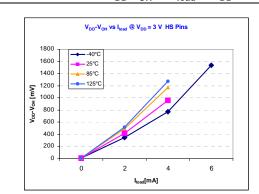

| 6 | Elec | ical characteristics 3                | 0              |  |  |  |  |

|   | 6.1  | Parameter conditions                  | 30             |  |  |  |  |

|   |      | 6.1.1 Minimum and maximum values      | 30<br>30<br>30 |  |  |  |  |

|   | 6.2  | 6.1.5 Pin input voltage               |                |  |  |  |  |

|   | 6.3  | Operating conditions 32               |                |  |  |  |  |

|   | 6.4  | Supply current characteristics 3      | 3              |  |  |  |  |

|   | 6.5  | Capacitive sensing characteristics    | 34             |  |  |  |  |

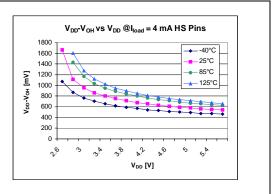

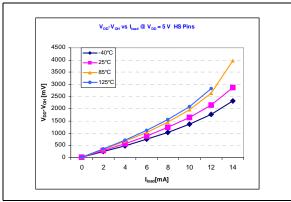

|   | 6.6  | KOUTn/OPTn/GPOn pin characteristics   | 35             |  |  |  |  |

|   | 6.7  | 6.6.1 General characteristics         | 35             |  |  |  |  |

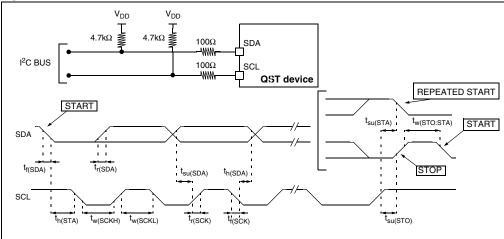

|   | 6.8  | I2C control interface                 |                |  |  |  |  |

| 7 | Pack | ge mechanical data                    | 1              |  |  |  |  |

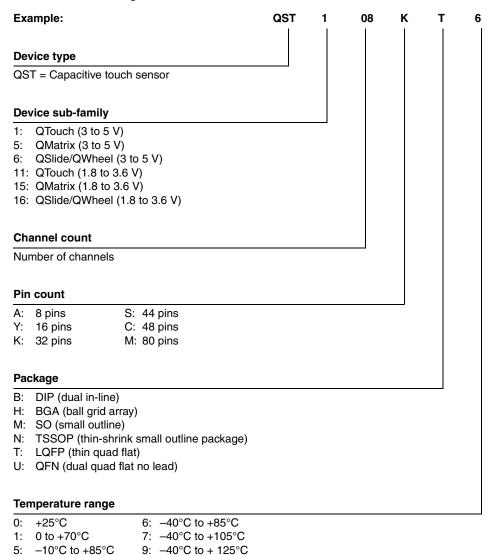

| 8 | Part | umbering 4                            | 3              |  |  |  |  |

| 9 | Devi | e revision information                | 4              |  |  |  |  |

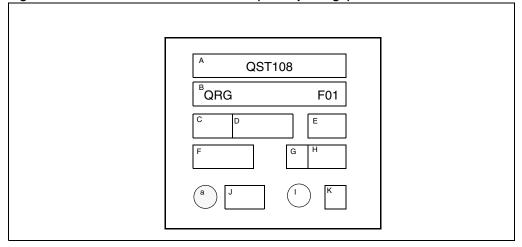

|   | 9.1  | 9.1 Device revision identification 44 |                |  |  |  |  |

|   | 9.2  | Device revision history               | 4              |  |  |  |  |

|   |      | 9.2.1       Revision 2.1              |                |  |  |  |  |

| Contents |                  | QST | 108 |

|----------|------------------|-----|-----|

| 10       | Revision history |     | 46  |

QST108 Device overview

### 1 Device overview

The QST108 capacitive touch sensor IC is a pure digital solution based on Quantum's patented charge-transfer (QProx<sup>™</sup>) capacitive technology.

This technology allows users to create simple touch panel sensing electrode interfaces for conventional or flexible printed circuit boards (PCB/FPCB). Sensing electrodes are part of the PCB layout (copper pattern or printed conductive ink) and may be used in various shapes (circle, rectangular, etc.).

By implementing the QProx<sup>™</sup> charge-transfer algorithm, the QST108 detects finger presence (human touch) near electrodes behind a dielectric (glass, plastic, wood, etc.). Only one external sampling capacitor by channel is used in the measuring circuitry to control the detection.

QST technology also incorporates advanced processing techniques such as drift compensation, auto-calibration, noise filtering, and Quantum's patented Adjacent Key Suppression™ (AKS™) to ensure maximum usability and control integrity.

In order to meet environmental requirements, ST offers this device in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97.

The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Pin description QST108

# 2 Pin description

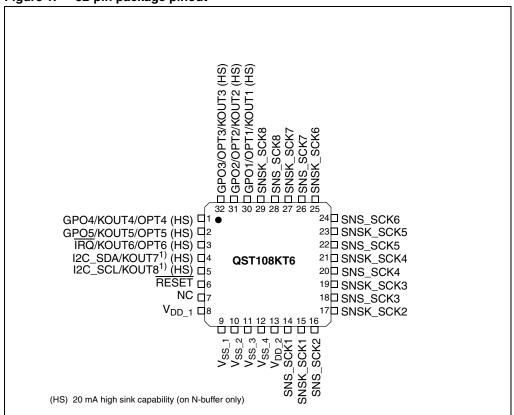

Figure 1. 32-pin package pinout

1. An external pull-up is required on these pins.

Table 2. Device pin description

|     | table 2. Bevice pin description |                     |                                                          |                                                                                   |                         |

|-----|---------------------------------|---------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|

| Pin | Pin name                        | Type <sup>(1)</sup> | Stand-alone mode function                                | I <sup>2</sup> C mode function                                                    | If unused               |

| 1   | GPO4/OPT4/KOUT4 <sup>(2)</sup>  | PP (HS)             | Key 4 output / BCD output 4<br>and MOD_0 option resistor | General purpose output 4<br>and I <sup>2</sup> C address bit 2<br>option resistor | Option resistor         |

| 2   | GPO5/OPT5/KOUT5 <sup>(2)</sup>  | PP (HS)             | Key 5 output and MOD_1 option resistor                   | General purpose output 5                                                          | Open or option resistor |

| 3   | OPT6/KOUT6/ <del>IRQ</del> (2)  | PP/OD<br>(HS)       | Key 6 output and OM_0 option resistor                    | Interrupt line (active low)                                                       | Open or option resistor |

| 4   | KOUT7/I2C_SDA <sup>(3)</sup>    | TOD<br>(HS)         | Key 7 output                                             | I <sup>2</sup> C serial data                                                      | Open                    |

| 5   | KOUT8/I2C_SCL <sup>(3)</sup>    | TOD<br>(HS)         | Key 8 output                                             | I <sup>2</sup> C serial clock                                                     | Open                    |

QST108 Pin description

Table 2. Device pin description (continued)

| Pin | Pin name                       | Type (1) | Stand-alone mode function                              | I <sup>2</sup> C mode function                                                    | If unused                      |

|-----|--------------------------------|----------|--------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|

| 6   | RESET                          | BD       | Reset (active low)                                     |                                                                                   | 10nF<br>capacitor to<br>ground |

| 7   | NC                             |          | Not connected                                          |                                                                                   |                                |

| 8   | V <sub>DD_1</sub>              | S        | Supply voltage                                         |                                                                                   |                                |

| 9   | V <sub>SS_1</sub>              | S        | Ground voltage                                         |                                                                                   |                                |

| 10  | V <sub>SS_2</sub>              | S        | Ground voltage                                         |                                                                                   |                                |

| 11  | V <sub>SS_3</sub>              | S        | Ground voltage                                         |                                                                                   |                                |

| 12  | V <sub>SS_4</sub>              | S        | Ground voltage                                         |                                                                                   |                                |

| 13  | V <sub>DD_2</sub>              | S        | Supply voltage                                         |                                                                                   |                                |

| 14  | SNS_SCK1                       | SNS      | Key 1 sense pin to Cs                                  |                                                                                   | Open                           |

| 15  | SNSK_SCK1                      | SNS      | Key 1 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 16  | SNS_SCK2                       | SNS      | Key 2 sense pin to Cs                                  |                                                                                   | Open                           |

| 17  | SNSK_SCK2                      | SNS      | Key 2 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 18  | SNS_SCK3                       | SNS      | Key 3 sense pin to Cs                                  |                                                                                   | Open                           |

| 19  | SNSK_SCK3                      | SNS      | Key 3 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 20  | SNS_SCK4                       | SNS      | Key 4 sense pin to Cs                                  |                                                                                   | Open                           |

| 21  | SNSK_SCK4                      | SNS      | Key 4 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 22  | SNS_SCK5                       | SNS      | Key 5 sense pin to Cs                                  |                                                                                   | Open                           |

| 23  | SNSK_SCK5                      | SNS      | Key 5 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 24  | SNS_SCK6                       | SNS      | Key 6 sense pin to Cs                                  |                                                                                   | Open                           |

| 25  | SNSK_SCK6                      | SNS      | Key 6 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 26  | SNS_SCK7                       | SNS      | Key 7 sense pin to Cs                                  |                                                                                   | Open                           |

| 27  | SNSK_SCK7                      | SNS      | Key 7 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 28  | SNS_SCK8                       | SNS      | Key 8 sense pin to Cs                                  |                                                                                   | Open                           |

| 29  | SNSK_SCK8                      | SNS      | Key 8 sense pin to Cs/Rs                               |                                                                                   | Open                           |

| 30  | GPO1/OPT1/KOUT1 (2)            | PP (HS)  | Key 1 output / BCD output 1 and MODE option resistor   | General purpose output 1 and MODE option resistor                                 | Option resistor                |

| 31  | GPO2/OPT2/KOUT2 <sup>(2)</sup> | PP (HS)  | Key 2 output / BCD output 2<br>and AKS option resistor | General purpose output 2<br>and I <sup>2</sup> C address bit 0<br>option resistor | Option resistor                |

| 32  | GPO3/OPT3/KOUT3 <sup>(2)</sup> | PP (HS)  | Key 3 output / BCD output 3 and LP option resistor     | General purpose output 3 and I <sup>2</sup> C address bit 1 option resistor       | Option resistor                |

S: supply pin, BD: bidirectional pin, SNS: capacitive sensing pin, PP: Output push-pull, OD: Output open-drain, TOD: Output true open-drain and HS: 20mA high sink (on N-buffer only)

<sup>2.</sup> During the reset phase, these pins are floating and the state depends on the option resistor.

<sup>3.</sup> An external pull-up is required on these pins.

#### QST touch sensing technology 3

#### 3.1 **Functional description**

QST devices employ bursts of charge-transfer cycles to acquire signals. Burst mode permits low power operation, dramatically reduces RF emissions, lowers susceptibility to RF fields, and yet permits excellent speed. Signals are processed using algorithms pioneered by Quantum which are specifically designed to provide reliable, trouble-free operation over the life of the product.

The QST switches and charge measurement hardware functions are all internal to the device. An external C<sub>S</sub> capacitor accumulates the charge from sense-plate C<sub>X</sub>, which is then measured. Larger values of CX cause the charge transferred into CS to rise more rapidly, reducing available resolution. As a minimum resolution is required for proper operation, this can result in dramatically reduced gain. Larger values of CS reduce the rise of differential voltage across it, increasing available resolution by permitting longer QST bursts. The value of C<sub>S</sub> can thus be increased to allow larger values of C<sub>X</sub> to be tolerated. The device is responsive to both  $C_X$  and  $C_S$ , and changes in either can result in substantial changes in sensor gain.

C<sub>T</sub> (~5 pF) Earth SNSK\_SCKn Sense capacitor C<sub>S</sub> (a few nF) SNS SCKn C<sub>x</sub> (~20 pF) Ai12569

Figure 2. QTouch™ measuring circuitry

#### 3.2 Spread-spectrum operation

The bursts operate over a spread of frequencies, so that external fields will have minimal effect on key operation and emissions are very weak. Spread-spectrum operation works with the Detection Integrator mechanism (DI) to dramatically reduce the probability of false detection due to noise.

### 3.3 Faulty and unused keys

Any sensing channel that does not have its sense capacitor ( $C_S$ ) fitted is assumed to be either faulty or unused. This channel takes no further part in operation unless a Master-commanded recalibration operation shows it to have an in-range burst count again. Faulty, unused or disabled keys are still bursted but not processed to avoid modifying the sensitivity of active keys.

This is important for sensing channels that have an open or short circuit fault across  $C_S$ . Such channels would otherwise cause very long acquire bursts, and in consequence would slow the operation of the entire QST device.

To optimize touch response time and device power consumption, if some keys are not used, we recommend to try suppressing the ones which belong to the same burst. Bursts which do not have any keys implemented will then not be processed.

#### 3.4 Detection threshold levels

The key capacitance change induced by the presence of a finger is sensed by the variation in the number of charge transfer pulses to load the capacitor. The difference in the pulse count number is compared to a threshold in order to detect the key as pressed or not.

Two different thresholds, one for detection and one for the end of detection, create an hysteresis in order to prevent erratic behavior.

The default threshold levels and hysteresis values are described in *Section 6.5: Capacitive* sensing characteristics on page 34.

### 3.5 Detection integrator filter

Detect Integrator (DI) filter mechanism works together with spread spectrum operation to dramatically reduce the effects of noise on key states. The DI mechanism requires a specified number of measurements that qualify as detections (and these must occur in a row) or the detection will not be reported.

In a similar manner, the end of a touch (loss of signal) also has to be confirmed over several measurements. This process acts as a type of "debounce" mechanism against noise.

The default DI value for confirming start of touch and end of touch is described in Section 6.5: Capacitive sensing characteristics on page 34.

#### 3.6 Self-calibration

On power-up, all keys are self-calibrated to provide reliable operation under almost any conditions. The calibration phase is used to compute a reference value per key which is then used by the process determining if a key is touched or not. The reference is an average of 8 single acquisitions. As a result, the calibration time of the system can be simply calculated using the following formula:  $t_{CAL} = 8$  \* Burst\_Period. The methodology used to measure the burst period is described in application note AN2547. For a maximum calibration duration ( $t_{CAL}$ ), please refer to *Section 6.5: Capacitive sensing characteristics on page 34*.

5//

### 3.7 Fast positive recalibration

The device autorecalibrates a key when its signal reflects a decrease in capacitance higher than a fixed threshold (PosRecalTh) for a defined number of acquisitions (PoseRecalI).

### 3.8 Forced key recalibration

A recalibration of the device may be issued at any time by sending to the QST device the appropriate I<sup>2</sup>C command or by tying the RESET pin to ground.

It is possible to recalibrate independently any individual key using an I<sup>2</sup>C command.

#### 3.9 Max On-Duration

The device can time out and automatically recalibrate each key independently after a fixed duration of continuous touch detection. This prevents the keys from becoming 'stuck on' due to foreign objects or other sudden influences. This is known as the Max On-Duration feature.

After recalibration, the key will continue to operate normally, even if partially or fully obstructed. Max On-Duration works independently per channel: a timeout on one channel has no effect on another channel.

Infinite timeout is useful in applications where a prolonged detection can occur and where the output must reflect the detection no matter how long. In infinite timeout mode, the designer should take care to ensure that drift in  $C_S$ ,  $C_X$ , and  $V_{DD}$  do not cause the device to remain "stuck on" inadvertently even when the touching object is removed from the sense field. Timeout durations are not accurate and can vary substantially depending on  $V_{DD}$  and temperature values, and should not be relied upon for critical functions.

### 3.10 Drift compensation

Signal drift can occur because of changes in  $C_X$ ,  $C_S$ , and  $V_{DD}$  over time. Depending on the  $C_S$  type and quality, the signal may vary substantially with temperature and veiling. If keys are subject to extremes of temperature or humidity, the signal can also drift. It is crucial that drift be compensated, otherwise false detections, non detections, and sensitivity shifts will follow.

Drift compensation slowly corrects the reference level of each key while no detection is in effect. The rate of reference adjustment must be performed slowly or else legitimate detections can also be ignored. The device compensates drift on each channel independently using a maximum compensation rate to the reference level.

Once a touch is sensed, the drift compensation mechanism ceases since the signal is legitimately high, and therefore should not cause the reference level to change.

The signal drift compensation is "asymmetric": the reference level compensates drift in one direction faster than it does in the other. Specifically, it compensates faster for increasing signals than for decreasing signals. Decreasing signals should not be compensated for quickly, since an approaching finger could be compensated for partially or entirely while approaching the sense electrode. However, an obstruction over the sense pad, for which the sensor has already made full allowance, could suddenly be removed leaving the sensor with an artificially elevated reference level and thus become insensitive to touch. In this latter case, the sensor will compensate for the object's removal very quickly, usually in only a few seconds.

577

Caution:

When only one key is enabled or if keys are very close together, the common drift compensation must be disabled or its rate must be reduced to ensure correct device operation.

### 3.11 Adjacent key suppression (AKS™)

Adjacent key suppression (AKS™) is a Quantum-patented feature which prevents multiple keys from responding to a single touch. This can happen with closely spaced keys, or a scroll wheel that has buttons very near it.

The QST108 supports two AKS modes:

Locking AKS

Once a key is considered as "touched", all other keys are locked in an untouched state. To unlock these keys, the touched key must return to an untouched state. Then, the key having the lowest key ID number is declared as the "touched" one.

Unlocking AKS

On each acquisition, the signal strengths from each key are compared and the key with the highest signal level is declared as the "touched" one.

In I<sup>2</sup>C mode, up to 8 AKS groups can be specified.

Note: All keys belonging to the same AKS group must have the same AKS mode.

# 4 Device operating modes

### 4.1 Reset and power-up

At power-up, the device configures itself according to the pull-up or pull-down option resistors present on pins OPT1 to OPT6. The device start-up and configuration may take up to  $t_{Setup}$ .

When the power is established, it is possible to force a new device configuration by applying a negative pulse on the RESET pin.

The RESET pin is a bidirectional pin with an internal pull-up. The line is forced low when the device resets itself (through an I<sup>2</sup>C command, for example).

A 10nF capacitor is recommended on the  $\overline{\text{RESET}}$  pin to ensure reliable start-up and noise immunity.

### 4.2 Burst operation

The device operates in "Burst" mode. Each key touch is acquired using a burst of charge-transfer sensing pulses whose count varies depending on the value of the sense capacitor  $C_S$  and the load capacitance  $C_X$ . Key touches are acquired using two successive bursts of pulses:

- Burst A: Keys 1, 2, 3, and 4

- Burst B: Keys 5, 6, 7, and 8

Bursts always operate in an A-B sequence. If Keys 5 to 8 are not implemented, the QST device will not perform the Burst B to improve the response time and reduce the power consumption when in Low Power (LP) mode.

In Low Power mode, the device sleeps in an ultra-low current state between bursts to conserve power.

# 4.3 Low power mode

In order to reduce the device power consumption, the QST family include scalable low power modes.

Standard low power mode

When the device is in standard low power mode, a window with very low power consumption is inserted between the acquisition of the last active key and the following acquisition of the first active key.

This window duration is programmable as the 'sleep duration time'.

Note that the sleep window insertion is cancelled in the following conditions:

- If a change is detected on a key, in order to speed up the DI process, the sleep window insertion is skipped until the end of the DI process.

- In I<sup>2</sup>C mode, when a key change is actually detected and reported with a negative pulse on the IRQ pin. In this case, the low power mode is disabled until a command is received from the host.

- Inside an I<sup>2</sup>C command, between the Write and the Read I<sup>2</sup>C frames, the sleep period is skipped.

#### Free run in detect

The behavior in this mode is the same as in the standard low power mode except that the sleep window insertion is always skipped if any of the active keys is detected as touched.

This is useful to improve the wheel response time.

#### Deep Sleep mode

In Deep Sleep mode, the device enters a very low power mode indefinitely. The device resumes its operations after receiving an I<sup>2</sup>C frame with any address or a reset.

#### Caution:

If an I<sup>2</sup>C frame is received while in Sleep or Deep Sleep mode, the device wakes up but does not acknowledge the frame (even if it has an I<sup>2</sup>C frame with the device address). The host must therefore send again the frame until it is taken in account and acknowledged.

#### 4.4 Mode selection

The device options are configured by connecting pull-up or pull-down resistors on OPTn pins. The device operating mode is selected using option pin 1 (OPT1) while the device settings are configured using option pins OPT2 to OPT6 (*Table 3*). Option pins are sampled at power-up and after a reset.

To fit most applications, the QST108 device offers two different operating modes:

#### Stand-alone mode

This mode allows the user to simply replace existing mechanical switches with a capacitive sensing solution. It is designed for maximum flexibility and can accommodate most popular sensing requirements via option resistors (AKS, Low power, Max On-Duration and output modes).

In this mode, the 8 output pins reflect the status of the 8 sensing channels.

#### I<sup>2</sup>C mode

In this mode, which is the most open one, the device is driven using the  $I^2C$  interface. To avoid polling, the QST device features an output interrupt pin ( $\overline{IRQ}$ ). The  $\overline{IRQ}$  line reports all key changes to the Master device. The QST (Slave) device can drive up to five general-purpose outputs.

Table 3. Operating modes

| OPT1: Mode s                 | Option resistor function |      |       |        |        |

|------------------------------|--------------------------|------|-------|--------|--------|

| OF 11. Mode s                | OPT2                     | ОРТ3 | OPT4  | OPT5   | ОРТ6   |

| Pin OPT1 is high at start-up | AKS                      | LP   | MOD_0 | MOD_1  | ОМ     |

| Pin OPT1 is low at start-up  | ADD0                     | ADD1 | ADD2  | Unused | Unused |

#### 4.5 Stand-alone mode

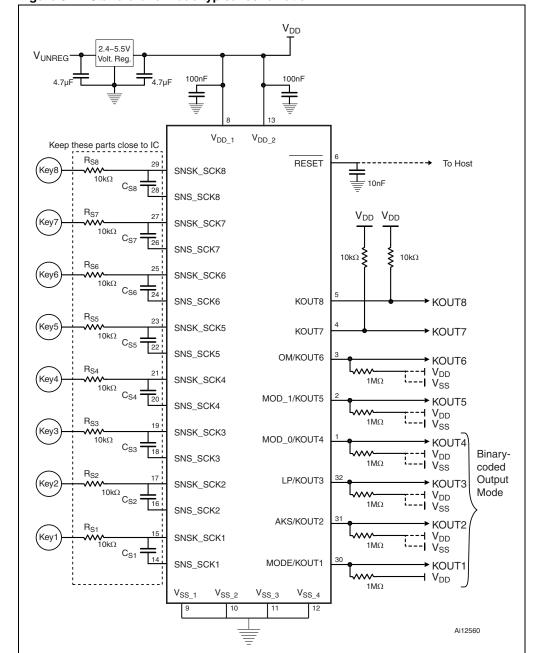

This mode allows the user to simply replace existing mechanical switch interface with a capacitive sensing solution. It is designed for maximum flexibility and can accommodate most popular sensing requirements via option resistors (see *Figure 3*).

### 4.5.1 Main features

- Pins KOUT1 to KOUT8 directly reflect the state of keys

- Selectable global adjacent key suppression (AKS™)

- Selectable sleep duration

- Selectable Max On-Duration values

- Selectable BCD mode

Figure 3. Stand-alone mode typical schematic

### 4.5.2 KOUT outputs

KOUTn outputs directly reflect the state of keys. These pins are push-pull outputs except for pins KOUT7 and KOUT8 which are true open-drain outputs. Under RESET, these pins are floating and their state depends on the option resistors. Pins KOUTn are active high meaning that when a key is "touched", the corresponding KOUT pin outputs a '1'.

5/

#### 4.5.3 Option descriptions

#### Adjacent key suppression (AKS™)

The QST108 features an adjacent key suppression (AKS™) function.

This function is enabled using the AKS option resistor (OPT2) in standard output mode as described in *Table 4*. In BCD output mode, the AKS function is always enabled, regardless of the option resistor configuration.

Table 4. AKS truth table

| OPT2/AKS        | Description                                              |  |

|-----------------|----------------------------------------------------------|--|

| V <sub>SS</sub> | Disabled                                                 |  |

| $V_{DD}$        | V <sub>DD</sub> Global locking AKS on all available keys |  |

#### Low Power mode option

This option resistor (OPT3) selects whether the device is always sensing the keys or if a low power consumption phase is introduced between bursts as described in *Table 5*.

In Low Power mode, a very low consumption (sleep) phase of 100ms is inserted between the Group B burst and the Group A burst. This significantly reduces the overall consumption of the device. Sleep duration is not accurate and can vary substantially depending on  $V_{DD}$  and temperature values.

Note:

In Low Power mode, the response time is increased.

Table 5. Low power (LP) mode truth table

| OPT3/LP         | Description          |  |  |

|-----------------|----------------------|--|--|

| V <sub>SS</sub> | Free running mode    |  |  |

| $V_{DD}$        | 100ms sleep duration |  |  |

#### **Max On-Duration**

There are four recalibration timing options ("Max On-Duration"). The recalibration option resistors (OPT4 and OPT5) control how long it takes for a continuous detection to trigger a recalibration on a key as described in *Table 6*. When such an event occurs, only the "stuck" key is recalibrated.

Table 6. Max On-Duration (MOD) truth table

| OPT4/MOD_0      | OPT5/MOD_1 | Description |

|-----------------|------------|-------------|

| V <sub>SS</sub> | $V_{SS}$   | Infinite    |

| V <sub>SS</sub> | $V_{DD}$   | 60s         |

| $V_{DD}$        | $V_{SS}$   | 20s         |

| $V_{DD}$        | $V_{DD}$   | 10s         |

### **Output mode option**

The QST108 offers several outputs mode to fit any existing application.

Table 7. Output mode (OM) truth table

| OPT6/OM Description |                                                                                       |

|---------------------|---------------------------------------------------------------------------------------|

| V <sub>SS</sub>     | Individual key state output mode: One output per sensing channel                      |

| $V_{DD}$            | BCD output mode: Binary-coded touched key number (see <i>Table 8</i> ) <sup>(1)</sup> |

<sup>1.</sup> In BCD mode, the AKS function is always active.

Table 8. Binary code truth table

| KOUT4 | KOUT3 | KOUT2 | KOUT1 | Description   |

|-------|-------|-------|-------|---------------|

| 0     | 0     | 0     | 0     | All released  |

| 0     | 0     | 0     | 1     | Key 1 pressed |

| 0     | 0     | 1     | 0     | Key 2 pressed |

| 0     | 0     | 1     | 1     | Key 3 pressed |

| 0     | 1     | 0     | 0     | Key 4 pressed |

| 0     | 1     | 0     | 1     | Key 5 pressed |

| 0     | 1     | 1     | 0     | Key 6 pressed |

| 0     | 1     | 1     | 1     | Key 7 pressed |

| 1     | 0     | 0     | 0     | Key 8 pressed |

|       | Other |       |       | Not used      |

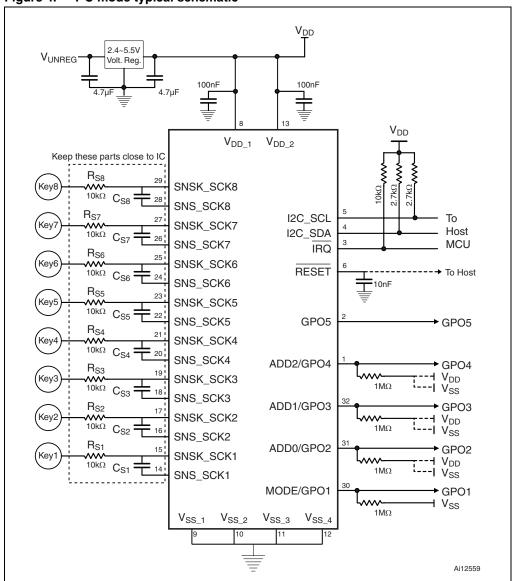

### 4.6 I<sup>2</sup>C mode

The I<sup>2</sup>C mode offers the largest configurability and functionality of the QST108.

#### 4.6.1 Main features

- 5 general-purpose outputs

- Configuration of up to 8 AKS groups

- Additional low power modes

- Accessible internal capacitive sensing parameters

- Continuous range of Max On-Duration

Figure 4. I<sup>2</sup>C mode typical schematic

#### 4.6.2 General-purpose outputs

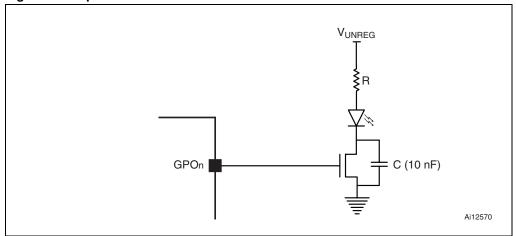

I<sup>2</sup>C mode allows to drive up to 5 general-purpose outputs. These output pins are configured in output push pull mode 0 by default. Their state can be changed using the SET\_GPIO\_STATE I<sup>2</sup>C command.

Figure 5. Optional LED schematic

### 4.6.3 **IRQ** pin

The  $\overline{\text{IRQ}}$  pin is an open drain output with an internal pull-up. It can be used to inform the Master device about any change in the key status. The  $\overline{\text{IRQ}}$  line is pulled low every time the state of any of the enabled keys changes. This includes any change in the touch state of the key, a faulty key or a new calibration of one or more keys. The reported changes may then be accessed by the Master device by using the GET\_KEY\_STATE command.

To improve communication response time, this signal suspends Low Power mode until the Master device has issued a communication with the QST device.

#### 4.6.4 Communication packet

The communication between the Master device and the QST108 (Slave) consists of two standard I<sup>2</sup>C frames.

The first frame is sent by the Master device using the QST108 device address with the write bit set. The data bytes consist of the command byte which is eventually followed by the parameters and a checksum byte.

The second one is sent by the Master device using the QST108 device address with the write bit reset. The QST108 completes the frame with data according to the command previously sent by the Master device. The device finishes the frame by sending a checksum byte for communication integrity verification.

If the read frame is omitted, the command may not be taken into account.

To initiate the communicate with the QST108, the Master device must send the GET\_DEVICE\_INFO command in order to unlock access to all the other commands.

### 4.6.5 I<sup>2</sup>C address selection

The QST108 slave address is programmable using the option resistors mapped on pins OPT2 to OPT4 (see *Table 9*).

Table 9. I<sup>2</sup>C address versus option resistor

| Opti            | on configura    | ation           | I <sup>2</sup> C Address |      |      |      |           |  |

|-----------------|-----------------|-----------------|--------------------------|------|------|------|-----------|--|

| OPT4            | ОРТ3            | OPT2            | ADD[6:3]                 | ADD2 | ADD1 | ADD0 | Hex value |  |

| V <sub>SS</sub> | $V_{SS}$        | $V_{SS}$        |                          | 0    | 0    | 0    | 0x28      |  |

| V <sub>SS</sub> | V <sub>SS</sub> | $V_{DD}$        |                          | 0    | 0    | 1    | 0x29      |  |

| V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> |                          | 0    | 1    | 0    | 0x2A      |  |

| V <sub>SS</sub> | V <sub>DD</sub> | $V_{DD}$        | 0101                     | 0    | 1    | 1    | 0x2B      |  |

| V <sub>DD</sub> | V <sub>SS</sub> | V <sub>SS</sub> | 0101                     | 1    | 0    | 0    | 0x2C      |  |

| V <sub>DD</sub> | V <sub>SS</sub> | $V_{DD}$        |                          | 1    | 0    | 1    | 0x2D      |  |

| V <sub>DD</sub> | V <sub>DD</sub> | V <sub>SS</sub> |                          | 1    | 1    | 0    | 0x2E      |  |

| V <sub>DD</sub> | V <sub>DD</sub> | V <sub>DD</sub> |                          | 1    | 1    | 1    | 0x2F      |  |

# 4.7 Supported commands

Table 10 lists the supported I2C commands and available arguments.

Note:

For more information on the supported commands and l<sup>2</sup>C protocol, please refer to the QST standard communication protocol reference manual.

Table 10. Supported commands

|         | oupported commu                                              |                                                                                                                                                           |  |  |  |

|---------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | I <sup>2</sup> C commands                                    | Description                                                                                                                                               |  |  |  |

| CALIBRA | TE_KEY (All keys)                                            |                                                                                                                                                           |  |  |  |

| Write   | 0x98                                                         | Forces the recalibration of all keys.                                                                                                                     |  |  |  |

| Read    | ErrCode                                                      | ErrCode: Standard Error code (see Table 11)                                                                                                               |  |  |  |

| CALIBRA | TE_KEY (Single key)                                          |                                                                                                                                                           |  |  |  |

| Write   | 0x9B KeyID Checksum                                          | Forces the recalibration of a single key.                                                                                                                 |  |  |  |

| Read    | ErrCode                                                      | Keyld: Binary-coded key number (see Table 14) ErrCode: Standard Error code (see Table 11)                                                                 |  |  |  |

| GET_DEE | BUG_INFO                                                     |                                                                                                                                                           |  |  |  |

| Write   | 0xF7 KeyID Checksum                                          | Returns the debug info of the single KeylD channel.                                                                                                       |  |  |  |

| Read    | 0x0B KeyDbgState<br>RefMSB RefLSB<br>BCMSB BCLSB<br>Checksum | KeyDbgState: Current Key Debug state (see Table 19) RefMSB: Reference Count MSB RefLSB: Reference Count LSB BCMSB: Burst Count MSB BCLSB: Burst Count LSB |  |  |  |

Table 10. Supported commands (continued)

|        | I <sup>2</sup> C commands                                                       | Description                                                                                                                                                                                           |

|--------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GET_DE | EVICE_INFO                                                                      |                                                                                                                                                                                                       |

| Write  | 0x85                                                                            | Returns the QST108 device version and ASCII-coded device name. This command must be sent first to enable the communication flow.                                                                      |

| Read   | 0x15 MainVers SubVers<br>NbSCkey NbMCkey<br>'Q' 'S' 'T' '1' '0' '8'<br>Checksum | MainVers: Device main version SubVer: Device sub-version NbSCkey: 0x08 single-channel keys NbMCkey: 0x00 multi-channel keys QST108: ASCII-coded device name                                           |

| GET_KE | EY_ERROR                                                                        |                                                                                                                                                                                                       |

| Write  | 0xC4                                                                            |                                                                                                                                                                                                       |

| Read   | 0x11 KeyError1<br>KeyError2 KeyError8<br>CheckSum                               | Returns the error information on each key.  KeyErrorN: KeyError byte description (see Table 12)                                                                                                       |

| GET_KE | Y_STATE                                                                         |                                                                                                                                                                                                       |

| Write  | 0xC1                                                                            | Returns the state of all keys.                                                                                                                                                                        |

| Read   | 0x03 AllKeyState<br>KeyError Checksum                                           | AllKeyState: Touched/untouched state for all 8 keys. Refer to Table 13: AllKeyState.  KeyError: Refer to Table 12: KeyError byte description                                                          |

| GET_PR | ROTOCOL_VERSION                                                                 |                                                                                                                                                                                                       |

| Write  | 0x80                                                                            | Returns the QST108 protocol version.                                                                                                                                                                  |

| Read   | 0x07 MainVers SubVer<br>I2CSpeed Checksum                                       | MainVers: Protocol main version SubVer: Protocol sub-version I2CSpeed: 0x00 (100 kHz maximum)                                                                                                         |

| RESET_ | DEVICE                                                                          |                                                                                                                                                                                                       |

| Write  | 0xFD                                                                            | Restarts the device (options Read and Calibration) after                                                                                                                                              |

| Read   | ErrCode                                                                         | reading the ErrCode (see <i>Table 11</i> ).                                                                                                                                                           |

| SET_DE | TECT_INTEGRATORS                                                                |                                                                                                                                                                                                       |

| Write  | 0x03 0x04 0x00 DI EDI<br>PosRecall CheckSum                                     | Sets the detection, End Of Detection and Positive Recalibration Integrators for all keys.                                                                                                             |

| Read   | ErrCode                                                                         | DI: Detection Integrator <sup>1) 3)</sup> EDI: End of Detection Integrator <sup>1) 3)</sup> PosRecalI: Positive Recalibration Integrator <sup>1) 3)</sup> ErrCode: Standard Error code (see Table 11) |

| SET_GP | PIO_STATE                                                                       |                                                                                                                                                                                                       |

| Write  | 0x08 0x01 GPOState<br>Checksum                                                  | Controls the state of the general-purpose outputs.  GPOState: State of general-purpose outputs (see Table 16)                                                                                         |

| Read   | ErrCode                                                                         | ErrCode: Standard Error code (see Table 11)                                                                                                                                                           |

Table 10. Supported commands (continued)

|         | I <sup>2</sup> C commands                                     | Description                                                                                                                                                            |  |  |  |

|---------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SET_KEY | _ACTIVATION (see <i>Note</i>                                  | 4)                                                                                                                                                                     |  |  |  |

| Write   | 0x97 KeyActivation<br>Checksum                                | Enables or disables a single key.  KeyActivation: Byte containing the key number selection and                                                                         |  |  |  |

| Read    | ErrCode                                                       | requested state.  ErrCode: Standard Error code (see Table 11)                                                                                                          |  |  |  |

| SET_KEY | _GROUP                                                        |                                                                                                                                                                        |  |  |  |

| Write   | 0x00 0x09<br>AKSGrpMode Key1Grp<br>Key2GrpKey8Grp<br>CheckSum | Defines the AKS groups for each key.  AKSGrpMode: AKS mode selection of each group (see Table 17)  KeynGrp: AKS group selection for key n (see Table 18)               |  |  |  |

| Read    | ErrCode                                                       | ErrCode: Standard Error code (see Table 11)                                                                                                                            |  |  |  |

| SET_LOW | /_POWER_MODE                                                  |                                                                                                                                                                        |  |  |  |

| Write   | 0x92 LowPowerMode<br>Checksum                                 | Selects standard or Low Power mode.  LowPowerMode: Configure Low Power mode (see Table 15)  ErrCode: Standard Error code (see Table 11)                                |  |  |  |

| Read    | ErrCode                                                       |                                                                                                                                                                        |  |  |  |

| SET_MAX | CON_DURATION                                                  |                                                                                                                                                                        |  |  |  |

| Write   | 0x8A MaxOnDuration<br>Checksum                                | Sets the maximum detected ON time before triggering an automatic recalibration.                                                                                        |  |  |  |

| Read    | ErrCode                                                       | MaxOnDuration: Time, in second (0 for infinite) ErrCode: Standard Error code (see Table 11)                                                                            |  |  |  |

| SET_SCK | EY_PARAMETERS                                                 |                                                                                                                                                                        |  |  |  |

| Write   | 0x01 0x04 0x00 DeTh<br>EofDeTh PosRecalTh<br>Checksum         | Sets the Detection, End Of Detection and Positive Recalibration Thresholds for a single key.  **DeTh: Detection Threshold 1) 2)                                        |  |  |  |

| Read    | ErrCode                                                       | EofDeTh: End of Detection Threshold <sup>1) 2)</sup> PosRecalTh: Positive Recalibration Threshold <sup>1) 2)</sup> ErrCode: Standard Error code (see <i>Table 11</i> ) |  |  |  |

Note: 1 See Section 6.5: Capacitive sensing characteristics on page 34 for default values.

- 2 The value is a signed character (0x80...0x7F <=> -128 ... +128).

- 3 The value is an unsigned number (0x00..0xFF <=> 0 ... 255).

- 4 Enabling or disabling keys triggers a new calibration of all enabled keys.

#### **Error codes**

Table 11 lists the I<sup>2</sup>C error codes.

Table 11. ErrCode

| ErrCode | Description                                                     |

|---------|-----------------------------------------------------------------|

| 0x01    | No Error                                                        |

| 0x83    | Command not supported                                           |

| 0x85    | Parameter not supported                                         |

| 0xA1    | Parity Error                                                    |

| 0xA3    | Checksum Error                                                  |

| 0xE0    | Initialization process (GET_FIRMWARE_INFO command not received) |

#### **KeyError byte description**

Table 12. KeyError byte description

| Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1         | Bit 0 |

|-----------|-------|-------|-------|-------|-------|---------------|-------|

| Key State | 0     | 0     | 0     | 0     | K     | ey error code | es    |

#### Key state (Bit 7)

When set to '1', the corresponding key is touched. This bit is always cleared for the GET\_KEY\_STATE command.

#### Key error codes (Bits 2:0)

When answering the GET\_KEY\_STATE command, the key error code corresponds to the error codes of all the keys ORed toghether. When answering the GET\_KEY\_ERROR command, each key error code describes the errors of one defined key.

Bit 0: When set to '1', calibration in progress

Bit 1: When set to '1', maximum count reached

Bit 2: When set to '1', minimum count not reached

#### All key state description

Table 13. AllKeyState

| Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Key 8 State | Key 7 State | Key 6 State | Key 5 State | Key 4 State | Key 3 State | Key 2 State | Key 1 State |

#### Key n state

When set to '1', the corresponding key is touched.

#### Key activation description

Table 14. KeyActivation

| Bit 7             | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2       | Bit 1      | Bit 0 |

|-------------------|-------|-------|-------|-------|-------------|------------|-------|

| Key<br>Activation | 0     | 0     | 0     |       | Key ID (bin | ary coded) |       |

#### Key activation (Bit 7)

0: Key enabled

1: Key disabled

#### Key identifier (Bits 3:0)

0000: All keys

0101: Key 5

0001: Key 1

0110: Key 6

0010: Key 2

0111: Key 7

0011: Key 3

1000: Key 8

0100: Key 4

#### Low power mode description

Table 15. SetLowPower

| Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3      | Bit 2       | Bit 1 | Bit 0 |

|-------|-----------------------|-------|-------|------------|-------------|-------|-------|

| 0     | Free Run<br>in Detect |       |       | Sleep Dura | tion Factor |       |       |

#### Free Run in Detect (Bit 6)

0: Low Power mode is always enabled, whatever the state of the keys.

1: Low Power mode is automatically suspended when any key is in Detect state.

Low Power mode is automatically resumed when no key is in Detect state.

#### Sleep Duration Factor (Bits 5 to 0)

0x00 or 0x20 to 0x3E: Low power mode is disabled.

0x01 to 0x19: Low Power mode. The sleep duration is 'Sleep Duration Factor' x 20 milliseconds (20 ms to 500 ms)

0x3F: Deep Sleep mode is entered immediately. Only a reset or an I<sup>2</sup>C frame with the correct device address allows exiting Deep Sleep mode.

Note: 1 When the device is in Sleep or Deep Sleep, any  $l^2C$  bus activity will wake-up the device.

2 The I<sup>2</sup>C QST device address is not acknowledged but forces the QST device to exit from Low Power mode. The Master device will have to repeat the command to ensure that it is taken in account.

### **GPO** state description

Table 16. GPOState

| Bit 7 | Bit 6 | Bit 5 | Bit 4          | Bit 3          | Bit 2          | Bit 1          | Bit 0          |

|-------|-------|-------|----------------|----------------|----------------|----------------|----------------|

| 0     | 0     | 0     | GPO 5<br>state | GPO 4<br>state | GPO 3<br>state | GPO 2<br>state | GPO 1<br>state |

#### **GPOState**

Defines the state of the selected general-purpose output pin. For more information, see *Section 4.6.2: General-purpose outputs on page 19*.

0: GPO state is '0'

1: GPO state is '1'

#### AKS group mode description

Table 17. AKSGrpnMode

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| AKSGrp8 | AKSGrp7 | AKSGrp6 | AKSGrp5 | AKSGrp4 | AKSGrp3 | AKSGrp2 | AKSGrp1 |

| Mode    |

#### **AKSGrpnMode**

Defines the type of AKS for the Group n:

0: Locking AKS

First key pressed within the group locks out all other keys.

1: Unlocking AKS

Most heavily pressed key (highest signal level) is selected over all other keys in the group.

#### AKS group selection description

Table 18. KeynGrp

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Grp8  | Grp7  | Grp6  | Grp5  | Grp4  | Grp3  | Grp2  | Grp1  |

#### **Grpx**

The selected key is a member of AKS Group x.

### Key debug state description

Table 19. KeyDbgState

| Value | Description                                  |

|-------|----------------------------------------------|

| 0x01  | On-going calibration                         |

| 0x02  | Key released                                 |

| 0x04  | Key touched                                  |

| 0x08  | Key in error                                 |

| 0x11  | Key calibration filter triggered (PosRecall) |

| 0x14  | Key detection filter triggered (DI)          |

| 0x24  | Key end of detection filter triggered (EDI)  |

QST108 Design guidelines

# 5 Design guidelines

### 5.1 C<sub>S</sub> sense capacitor

The  $C_S$  sense capacitors accumulate the charge from the key electrodes and determine sensitivity. Higher values of  $C_S$  make the corresponding sensing channel more sensitive. The values of  $C_S$  can differ for each channel, permitting differences in sensitivity from key to key or to balance unequal sensitivities. Unequal sensitivities can occur due to key size and placement differences and stray wiring capacitances. More stray capacitance on a sense trace will desensitize the corresponding key. Increasing the  $C_S$  for that key will compensate for the loss of sensitivity.

The  $C_S$  capacitors can be virtually any plastic film or low- to medium-K ceramic capacitor. The normal  $C_S$  range is 1nF to 50nF depending on the sensitivity required: larger values of  $C_S$  require better quality to ensure reliable sensing. In certain circumstances the normal  $C_S$  range may be exceeded. Acceptable capacitor types for most uses include PPS film, polypropylene film, and NP0 and X5R / X7R ceramics. Lower grades than X5R or X7R are not recommended.

### 5.2 Sensitivity tuning

Sensitivity can be altered to suit various applications and situations on a channel-by-channel basis. The easiest and most direct way to impact sensitivity is to alter the value of each  $C_S$ : more  $C_S$  yields higher sensitivity. Each channel has its own  $C_S$  value and can therefore be independently adjusted.

### 5.2.1 Increasing sensitivity

Sensitivity can also be increased by using larger electrode areas, reducing panel thickness, or using a panel material with a higher dielectric constant.

#### 5.2.2 Decreasing sensitivity

In some cases the circuit may be too sensitive. Gain can be lowered further by a number of strategies:

- making the electrode smaller

- making the electrode into a sparse mesh using a high space-to-conductor ratio

- decreasing the C<sub>S</sub> capacitors

#### 5.2.3 Key balance

A number of factors can cause sensitivity imbalances. Notably, SNS wiring to electrodes can have differing stray amounts of capacitance to ground. Increasing load capacitance will cause a decrease in gain. Key size differences, and proximity to other metal surfaces can also impact gain.

The keys may thus require "balancing" to achieve similar sensitivity levels. This can be best accomplished by trimming the values of the  $C_S$  capacitors to achieve equilibrium. The  $R_S$  resistors have no effect on sensitivity and should not be altered. Load capacitances to ground can also be added to overly sensitive channels to reduce their gain.

These should be in the order of a few picofarads.

Design guidelines QST108

### 5.3 Power supply

If the power supply fluctuates slowly with temperature, the QST device compensates automatically for these changes with only minor changes in sensitivity. However, if the supply voltage drifts or shifts quickly, the drift compensation mechanism is not able to keep up, causing sensitivity anomalies or false detections.

The power supply should be locally regulated, using a three-terminal regulator. If the supply is shared with another electronic system, care should be taken to ensure that the supply is free of digital spikes, sags and surges which can cause adverse effects. It is not recommended to include a series inductor in the power supply to the QST device.

For proper operation, a 0.1  $\mu$ F or greater bypass capacitor must be used between  $V_{DD}$  and  $V_{SS}$ . The bypass capacitor should be routed with very short tracks to the device's  $V_{DD}$  and  $V_{SS}$  pins.

The PCB should, if possible, include a copper pour under and around the device, but not extensively under the SNS lines.

### 5.4 ESD protection

In normal environmental conditions, only one series resistor is required for ESD suppression. A 10 kOhm  $\rm R_S$  resistor in series with the sense trace is sufficient in most cases. The dielectric panel (glass or plastic) usually provides a high degree of isolation to prevent ESD discharge from reaching the circuit.  $\rm R_S$  should be placed close to the chip. If the  $\rm C_X$  load is high,  $\rm R_S$  can prevent total charge and transfer and as a result gain can deteriorate. If a reduction in  $\rm R_S$  increases gain noticeably, the lower value should be used. Conversely, increasing the  $\rm R_S$  can result in added ESD and EMC benefits, provided that the increase does not decrease sensitivity.

### 5.5 Crosstalk precautions

Adjacent sense traces might require intervening ground traces in order to reduce capacitive cross bleed if high sensitivity is required or high values of delta- $C_X$  are anticipated (for example, from direct human touch to an electrode connection). In normal touch applications behind plastic panels, this is rarely a problem regardless of how the electrodes are wired.

Higher values of  $R_S$  will make crosstalk problems worse; try to keep  $R_S$  to 22 kOhm or less if possible. In general try to keep the QST device close to the electrodes and reduce the adjacency of the sense wiring to ground planes and other signal traces; this will reduce the  $C_X$  load, reduce interference effects, and increase signal gain. The one and only valid reason to run ground near SNS traces is to provide crosstalk isolation between traces, and then only on an as-needed basis.

# 5.6 PCB layout and construction

The PCB traces, wiring, and any components associated with or in contact with either SNS pin will become touch sensitive and should be treated with caution to limit the touch area to the desired location.

Multiple touch electrodes connected to any sensing channel can be used, for example, to create control surfaces on both sides of an object.

**577**

QST108 Design guidelines

It is important to limit the amount of stray capacitance on the SNS terminals, for example by minimizing trace lengths and widths to allow for higher gain without requiring higher values of  $C_S$ . Under heavy delta- $C_X$  loading of one key, cross coupling to another key's trace can cause the other key to trigger. Therefore, electrode traces from adjacent keys should not be run close to each other over long runs in order to minimize cross-coupling if large values of delta- $C_X$  are expected, for example when an electrode is directly touched. This is not a problem when the electrodes are working through a plastic panel with normal touch sensitivity.

For additional information on PCB layout and construction, please contact your local ST Sales Office for a list of available application notes.

577

Electrical characteristics QST108

### 6 Electrical characteristics

#### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$ °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5$  V (for the 4.5V  $\leq$   $V_{DD} \leq 5.5$  V voltage range) and  $V_{DD} = 3.3$  V (for the 3.0 V  $\leq$   $V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

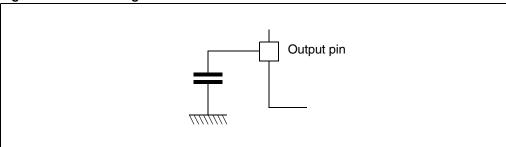

The loading conditions used for pin parameter measurement are shown in Figure 6.

#### 6.1.5 Pin input voltage

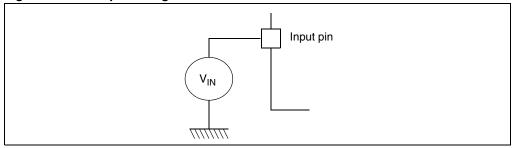

The input voltage measurement on a pin of the device is described in Figure 7.

Figure 7. Pin input voltage

# 6.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 20. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature |             |      |

Table 21. Voltage characteristics

| Symbol                | Ratings                                               | Maximum value                  | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------|------|

| $V_{DD} - V_{SS}$     | Supply voltage                                        | 7.0                            |      |

| V <sub>IN</sub>       | Input voltage on any pin (1)(2)                       | $V_{SS}$ =0.3 to $V_{DD}$ +0.3 | V    |

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human Body Model)    | 2000                           | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge Device Model) | 500                            |      |

- Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7kΩ for RESET, 10kΩ for I/Os).

- I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected.

Electrical characteristics QST108

Table 22. Current characteristics

| Symbol                             | Ratings                                                                 | Maximum value | Unit |

|------------------------------------|-------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                   | Total current into $V_{DD}$ power lines (source) <sup>(1)</sup>         | 75            |      |

| I <sub>VSS</sub>                   | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup> | 150           |      |

|                                    | Output current sunk by RESET pin                                        | 20            |      |

| I <sub>IO</sub>                    | Output current sunk by output pin                                       | 40            | mA   |

|                                    | Output current source by output pin                                     | - 25          | IIIA |

| I <sub>INJ(PIN)</sub> (2)          | Injected current on RESET pin                                           | ± 5           |      |

| (3)                                | Injected current output pin                                             | ± 5           |      |

| $\Sigma I_{\text{INJ(PIN)}}^{(2)}$ | Total injected current (sum of all I/O and control pins)                | ± 20          |      |

- 1. All power  $(V_{DD})$  and ground  $(V_{SS})$  lines must always be connected to the external supply.

- 2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly ensured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the

positive and negative injected currents (instantaneous values). These results are based on

characterisation with ΣI<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

# 6.3 Operating conditions

Table 23. Operating conditions

| Symbol          | Feature                  | Value        | Unit |

|-----------------|--------------------------|--------------|------|

| V <sub>DD</sub> | Operating supply voltage | 2.4 to 5.5   | V    |

| T <sub>A</sub>  | Operating temperature    | -40° to +85° | С    |

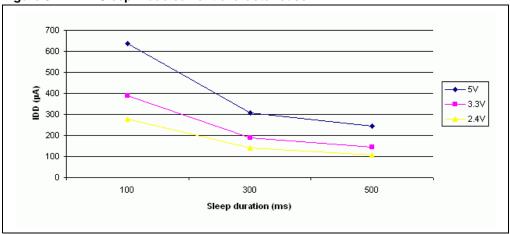

# 6.4 Supply current characteristics

Table 24. Supply current characteristics

| Symbol                    | Parameter                                 | Conditions              | Min. | Typ. <sup>(1)</sup> | Max. | Unit |

|---------------------------|-------------------------------------------|-------------------------|------|---------------------|------|------|

|                           |                                           | V <sub>DD</sub> = 2.4 V |      | 1.71                |      |      |