## **Product Description**

Sirenza Microdevices' SPF-2000 is a high linearity, low noise  $0.25\mu m$  pHEMT. This  $300\mu m$  device is ideally biased at 3V,20mA for lowest noise performance. At 5V,40mA the device delivers excellent output TOI of 32 dBm. It provides ideal performance as driver stages in many commercial, industrial and military LNA applications.

# **SPF-2000**

# Low Noise High Linearity pHEMT GaAs FET 0.1 - 12 GHz Operation

### **Product Features**

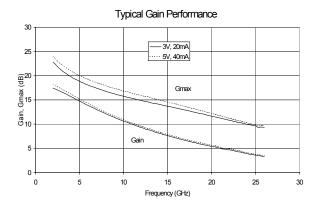

- 15 dB Gmax at 12GHz

- 1.25 dB F<sub>MIN</sub> at 12 GHz

- +32 dBm Output IP3 at 12GHz

- +20 dBm Output Power at 1dB Compression

## **Applications**

- High IP3 LNA for VSAT, LMDS, Cellular Systems and Instrumentation

- Broadband Amplifiers

| Symbol             | Device Characteristics:              | Test Conditions,<br>Vds = 3V, lds = 20mA, T = 25°C<br>(unless otherwise noted)                                                                                                                | Test<br>Frequency                          | U n its                          | M in .   | Тур.                         | Max.        |

|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------|----------|------------------------------|-------------|

| Gmax               | Maximum Available Gain [2]           | $Z_s = Z_s^*, Z_L = Z_L^*$                                                                                                                                                                    | 1.9 GHz<br>4.0 GHz<br>12.0 GHz             | d B<br>d B<br>d B                | 21<br>13 | 25<br>23<br>15               | 25<br>17    |

| S 21               | Insertion Gain [2]                   | $Z_s = Z_L = 50 \text{ Ohms}$                                                                                                                                                                 | 1.9 GHz                                    | d B                              | 16       | 18                           | 20          |

| N F <sub>MIN</sub> | Minimum Noise Figure                 | $Z_s = Gamma-opt, Z_L = Z_L^*$                                                                                                                                                                | 2.0 GHz<br>4.0 GHz<br>12.0 GHz             | d B<br>d B<br>d B                | -        | 0.5<br>0.6<br>1.2            | -           |

| P <sub>1dB</sub>   | Output 1dB Compression Point         | $V_{DS} = 5V, I_{DS} = 40 \text{ mA}$ $V_{DS} = 3V, I_{DS} = 20 \text{ mA}$ $V_{DS} = 5V, I_{DS} = 40 \text{ mA}$ $V_{DS} = 5V, I_{DS} = 40 \text{ mA}$ $V_{DS} = 3V, I_{DS} = 20 \text{ mA}$ | 2.0 GHz<br>2.0 GHz<br>12.0 GHz<br>12.0 GHz | d B m<br>d B m<br>d B m<br>d B m | -        | 20.0<br>15.0<br>21<br>18     | -<br>-<br>- |

| G <sub>1dB</sub>   | Gain at 1dB Compression Point        | $V_{DS} = 5V, I_{DS} = 40 \text{ mA}$ $V_{DS} = 3V, I_{DS} = 20 \text{ mA}$ $V_{DS} = 5V, I_{DS} = 40 \text{ mA}$ $V_{DS} = 5V, I_{DS} = 40 \text{ mA}$ $V_{DS} = 3V, I_{DS} = 20 \text{ mA}$ | 2.0 GHz<br>2.0 GHz<br>12.0 GHz<br>12.0 GHz | d B m<br>d B m<br>d B m<br>d B m | -        | 17.7<br>17.0<br>13.0<br>11.0 | -<br>-<br>- |

| O IP <sub>3</sub>  | Output Third Order Intercept Point   | $\begin{array}{c} V_{DS} = 5V,  I_{DS} = 40\text{m A} \\ V_{DS} = 3V,  I_{DS} = 20\text{m A} \\ V_{DS} = 5V,  I_{DS} = 40\text{m A} \\ V_{DS} = 3V,  I_{DS} = 20\text{m A} \end{array}$       | 2.0 GHz<br>2.0 GHz<br>12.0 GHz<br>12.0 GHz | d B m<br>d B m<br>d B m<br>d B m |          | 32<br>28<br>32<br>30         | -<br>-<br>- |

| I <sub>DSS</sub>   | Saturated Drain Current [2]          |                                                                                                                                                                                               |                                            | m A                              | 30       | 8 5                          | 140         |

| V <sub>P</sub>     | Pinchoff Voltage [1]                 | V <sub>DS</sub> = 2V, I <sub>DS</sub> = 0.150 mA                                                                                                                                              |                                            | V                                | -1.5     | -1.0                         | -0.5        |

| G <sub>M</sub>     | Transconductance                     | V <sub>GS</sub> = -0.25V                                                                                                                                                                      |                                            | m S                              | -        | 112                          | -           |

| B V <sub>g s</sub> | Gate to Source Breakdown Voltage [1] | I <sub>GS</sub> = 0.3 m A, drain open                                                                                                                                                         |                                            | V                                | -        | -17                          | -8          |

| B V <sub>GD</sub>  | Gate to Drain Breakdown Voltage [1]  | $I_{GD} = 0.3  \text{m A}, V_{GS} = -3.0  \text{V}$                                                                                                                                           |                                            | V                                | -        | -17                          | -8          |

| R <sub>TH</sub>    | Thermal Resistance                   |                                                                                                                                                                                               |                                            | C /W                             |          | 110                          |             |

| V <sub>DS</sub>    | Operating Voltage [3]                | Drain-source                                                                                                                                                                                  |                                            | ٧                                |          |                              | 5.5         |

| I <sub>D Q</sub>   | Operating Current [3]                | Drain-source, quiescent                                                                                                                                                                       |                                            | m A                              |          |                              | 55          |

| PDISS              | Power Dissipation [3]                |                                                                                                                                                                                               |                                            | W                                |          |                              | 0.2         |

<sup>[1] 100%</sup> tested - DC parameters tested on wafer.

The information provided herein is believed to be reliable at press time. Sirenza Microdevices assumes no responsibility for inaccuracies or omissions. Sirenza Microdevices assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. Sirenza Microdevices does not authorize or warrant any Sirenza Microdevices product for use in life-support devices and/or systems. Copyright 2001 Sirenza Microdevices, Inc. All worldwide rights reserved.

303 South Technology Court Broomfield, CO 80021 Phone: (800) SMI-MMIC

http://www.sirenza.com

EDS-103295 Rev A

<sup>[2]</sup> Sample tested - Samples pullied from each wafer lot. Sample test specifications are based on statistical data from sample test measurements.

<sup>[3]</sup>  $V_{DS} * I_{DQ} < P_{DISS}$  is recommended for continuous reliable operation.

## Preliminary

### SPF-2000 Low Noise High Linearity FET

### **Absolute Maximum Ratings**

Operation of this device beyond any one of these parameters may cause permanent damage.

MTTF is inversely proportional to the device junction temperature. For junction temperature and MTTF considerations the operating conditions should also satisfy the following experssions:

$$P_{DC} - P_{OUT} < (T_{J} - T_{L}) / R_{TH}$$

where:

$P_{DC} = I_{DS} * V_{DS} (W)$   $P_{OUT} = RF Output Power (W)$   $T_{J} = Junction Temperature (°C)$   $T_{L} = Lead Temperature (pin 4) (°C)$  $R_{TM} = Thermal Resistance (°C/W)$

| Parameter                 | Symbol            | Value            | Unit |

|---------------------------|-------------------|------------------|------|

| Drain Current             | I <sub>DS</sub>   | I <sub>DSS</sub> | mA   |

| Forward Gate Current      | I <sub>GSF</sub>  | 0.3              | mA   |

| Reverse Gate Current      | I <sub>GSR</sub>  | 0.3              | mA   |

| Drain-to-Source Voltage   | V <sub>DS</sub>   | +7               | ٧    |

| Gate-to-Drain Voltage     | V <sub>GD</sub>   | -8               | V    |

| Gate-to-Source Voltage    | V <sub>GS</sub>   | <-5 or >0        | V    |

| RF Input Power            | P <sub>IN</sub>   | 100              | mW   |

| Operating Temperature     | T <sub>OP</sub>   | -40 to +85       | °C   |

| Storage Temperature Range | T <sub>stor</sub> | -40 to +150      | °C   |

| Power Dissipation         | P <sub>DISS</sub> | 600              | mW   |

| Channel Temperature       | T <sub>J</sub>    | +150             | °C   |

## **Assembly Instructions:**

The recommended die attach is conductive epoxy or AuSn (80/20) solder with limited exposure to temperatures at or above 300C. The preferred wirebond method is thermo-compression wedge bond using 0.7 mil gold wire with a maximum stage temperature of 200C. Aluminum wire should not be used.

#### **Design Data:**

Complete design data including S-parameters, noise parameters, and large signal model are available upon request by contacting applications support at baredie-apps@sirenza.com

# Preliminary

## SPF-2000 Low Noise High Linearity FET

#### **Part Number Ordering Information**

| Part Number | Reel Size | Devices/Pack |

|-------------|-----------|--------------|

| SPF-2000    | Gel Pak   | 100          |

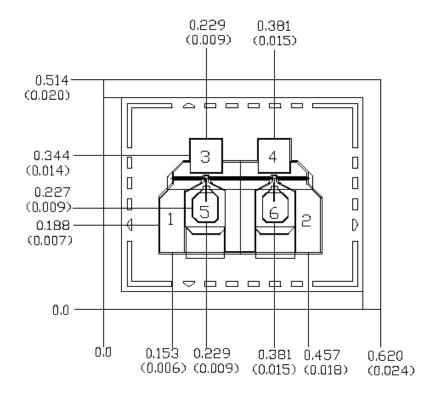

#### **Mechanical Drawing**

Units: millimeters (inches) Thickness: 0.1016 (0.004)

Chip edge to bond pad dimensions are shown to center of bond pad

Chip size tolerance: +/- 0.051 (0.002)

Bond Pad #1,#2 (Source) 0.056 x 0.123 (0.002 x 0.005) Bond Pad #3,#4 (Drain) 0.070 x 0.074 (0.003 x 0.003) Bond Pad #5,#6 (Gate) 0.056 x 0.065 (0.002 x 0.003)

303 South Technology Court, Broomfield, CO 80021

Phone: (800) SMI-MMIC

http://www.sirenza.com EDS-103295 Rev A