INTEGRATED CIRCUITS

Product specification Supersedes data of 1997 Jun 10 File under Integrated Circuits, IC17 1997 Sep 03

### **UMA1015AM**

### FEATURES

- Two fully programmable RF dividers up to 1.1 GHz

- Fully programmable reference divider up to 35 MHz

- 2 : 1 or 1 : 1 ratio of selectable reference frequencies

- Fast three-line serial bus interface

- Adjustable phase comparator gain

- Programmable out-of-lock indication for both loops

- On-chip voltage doubler

- Low current consumption from 3 V supply

- · Separate power-down mode for each synthesizer

- Up to 4 open-drain output ports

- Crystal input frequency signal inverted and buffered output on separate pin.

### **APPLICATIONS**

- Cordless telephone

- Hand-held mobile radio.

### QUICK REFERENCE DATA

### **GENERAL DESCRIPTION**

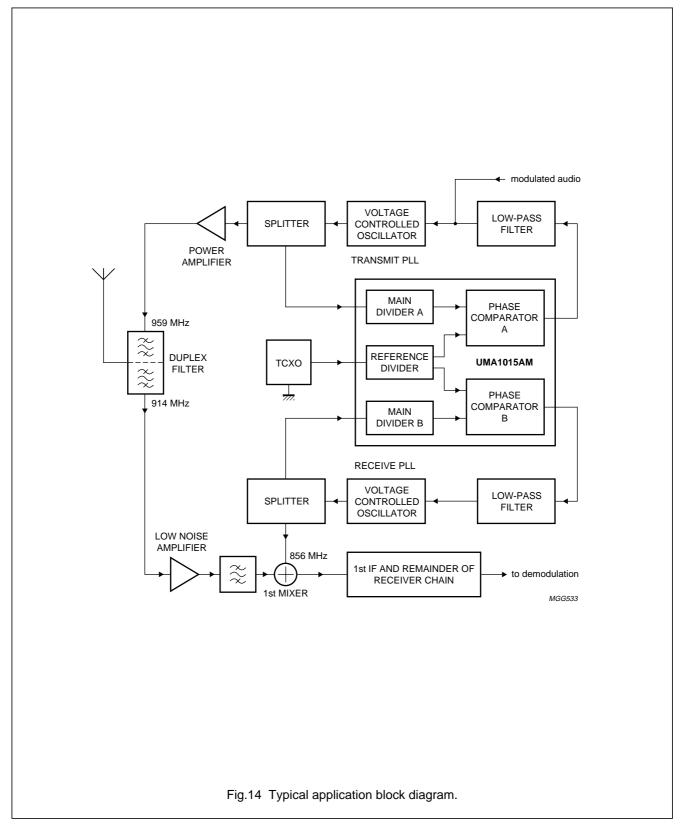

The UMA1015AM is a low-power dual frequency synthesizer for radio communications which operates in the 50 to 1100 MHz frequency range. Each synthesizer consists of a fully programmable main divider, a phase and frequency detector and a charge pump. There is a fully programmable reference divider common to both synthesizers which operates up to 35 MHz.

The device is programmed via a 3-wire serial bus which operates up to 10 MHz. The charge pump currents (gains) are fixed by an external resistance at pin 20 ( $I_{SET}$ ). The BiCMOS device is designed to operate from 2.7 V (3 NiCd cells) to 5.5 V at low current. Digital supplies  $V_{DD1}$  and  $V_{DD2}$  must be at the same potential. The charge pump supply ( $V_{CC}$ ) can be provided by an external source or on-chip voltage doubler.  $V_{CC}$  must be equal to or higher than  $V_{DD1}$ .

Each synthesizer can be powered-down independently via the serial bus to save current. It is also possible to power-down the device via the HPD input (pin 5).

| SYMBOL                                | PARAMETER                                                      | CONDITIONS                                                        | MIN. | TYP.                    | MAX. | UNIT |

|---------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|------|-------------------------|------|------|

| V <sub>DD1</sub> , V <sub>DD2</sub>   | digital supply voltage                                         | $V_{DD1} = V_{DD2}$                                               | 2.7  | -                       | 5.5  | V    |

| V <sub>CC</sub>                       | charge pump supply voltage                                     | external supply; doubler disabled; $V_{CC} \ge V_{DD}$            | 2.7  | -                       | 6.0  | V    |

| V <sub>CCvd</sub>                     | charge pump supply from voltage doubler                        | doubler enabled                                                   | -    | 2V <sub>DD1</sub> - 0.6 | 6.0  | V    |

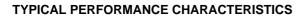

| $I_{DD1} + I_{DD2} + I_{CC}$          | operating supply current                                       | both synthesizers ON; doubler disabled; $V_{DD1} = V_{DD2} = 3 V$ | -    | 8.7                     | -    | mA   |

| I <sub>DDpd</sub> + I <sub>CCpd</sub> | total current in power-down mode                               | doubler disabled;<br>$V_{DD1} = V_{DD2} = 3 V$                    | -    | 3                       | -    | μA   |

| I <sub>DDpd</sub>                     | current in power-down mode from supply $V_{DD1}$ and $V_{DD2}$ | doubler enabled;<br>$V_{DD1} = V_{DD2} = 3 V$                     | -    | 0.25                    | -    | mA   |

| f <sub>RF</sub>                       | RF input frequency for each synthesizer                        |                                                                   | 50   | _                       | 1100 | MHz  |

| f <sub>XTALIN</sub>                   | crystal input frequency                                        |                                                                   | 3    | -                       | 35   | MHz  |

| f <sub>pc(min)</sub>                  | minimum phase comparator frequency                             |                                                                   | -    | 10                      | -    | kHz  |

| f <sub>pc(max)</sub>                  | maximum phase<br>comparator frequency                          |                                                                   | -    | 750                     | _    | kHz  |

| T <sub>amb</sub>                      | operating ambient temperature                                  |                                                                   | -30  | _                       | +85  | °C   |

### UMA1015AM

#### **ORDERING INFORMATION**

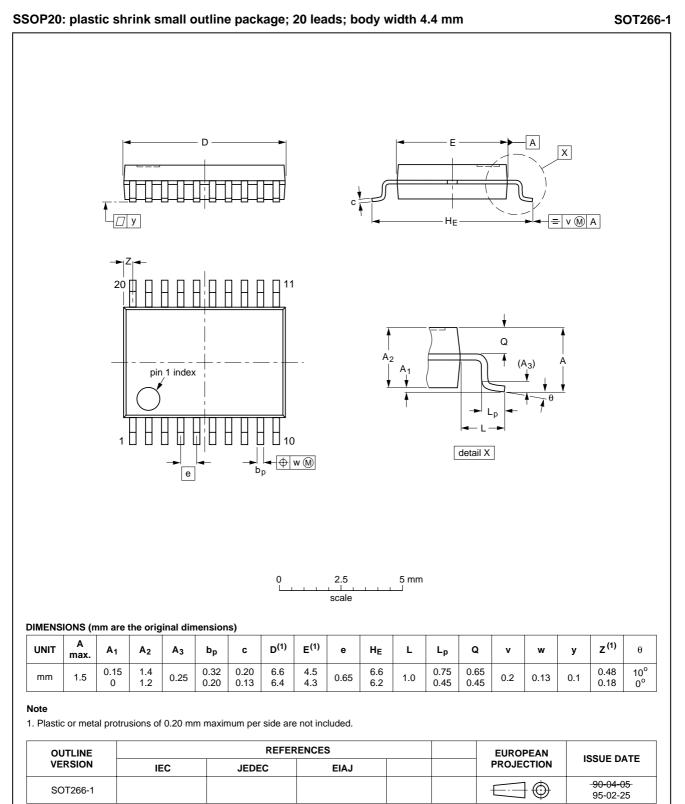

| TYPE NUMBER |        | PACKAGE                                                           |          |

|-------------|--------|-------------------------------------------------------------------|----------|

|             | NAME   | DESCRIPTION                                                       | VERSION  |

| UMA1015AM   | SSOP20 | plastic shrink small outline package; 20 leads; body width 4.4 mm | SOT266-1 |

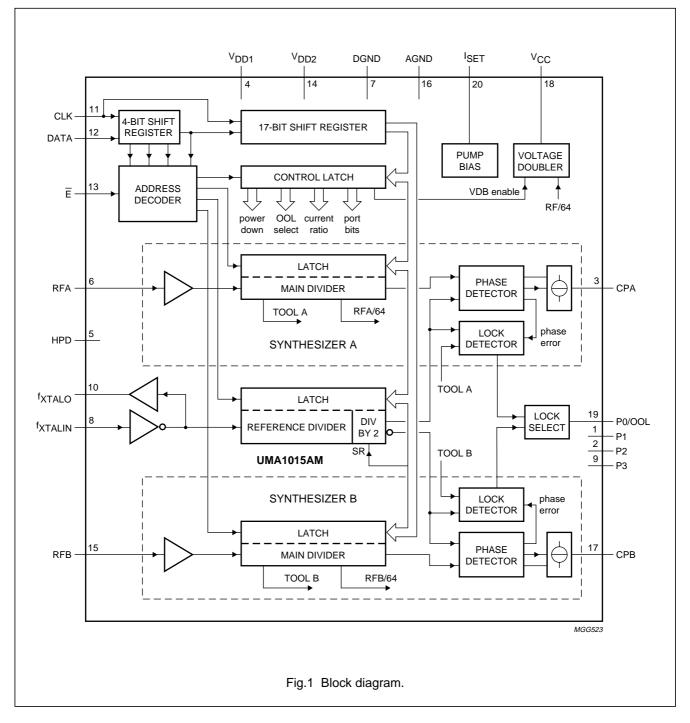

### **BLOCK DIAGRAM**

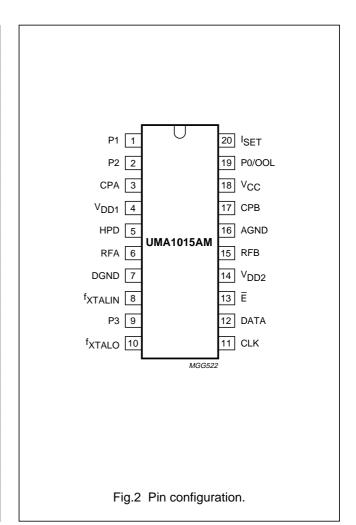

### PINNING

| SYMBOL              | PIN | DESCRIPTION                                                         |

|---------------------|-----|---------------------------------------------------------------------|

| P1                  | 1   | output Port 1                                                       |

| P2                  | 2   | output Port 2                                                       |

| CPA                 | 3   | charge pump output synthesizer A                                    |

| V <sub>DD1</sub>    | 4   | digital supply voltage 1                                            |

| HPD                 | 5   | hardware power-down<br>(input LOW = power-down)                     |

| RFA                 | 6   | RF input synthesizer A                                              |

| DGND                | 7   | digital ground                                                      |

| f <sub>XTALIN</sub> | 8   | common crystal frequency input from TCXO                            |

| P3                  | 9   | output Port 3                                                       |

| f <sub>XTALO</sub>  | 10  | open-drain output of f <sub>XTAL</sub> signal                       |

| CLK                 | 11  | programming bus clock input                                         |

| DATA                | 12  | programming bus data input                                          |

| Ē                   | 13  | programming bus enable input<br>(active LOW)                        |

| V <sub>DD2</sub>    | 14  | digital supply voltage 2                                            |

| RFB                 | 15  | RF input synthesizer B                                              |

| AGND                | 16  | analog ground to charge pumps                                       |

| СРВ                 | 17  | charge pump output synthesizer B                                    |

| V <sub>CC</sub>     | 18  | analog supply to charge pump;<br>external or voltage doubler output |

| P0/OOL              | 19  | Port output 0/out-of-lock output                                    |

| I <sub>SET</sub>    | 20  | regulator pin to set charge pump currents                           |

### FUNCTIONAL DESCRIPTION

#### Main dividers

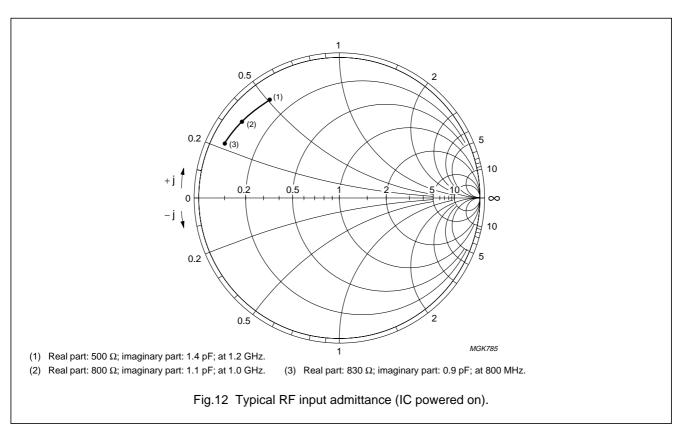

Each synthesizer has a fully programmable 17-bit main divider. The RF input drives a pre-amplifier to provide the clock to the first divider bit. The pre-amplifier has a high input impedance, dominated by pin and pad capacitance. The circuit operates with signal levels from below 50 mV (RMS) up to 250 mV (RMS), and at frequencies up to 1.1 GHz. The high frequency sections of the divider are implemented using bipolar transistors, while the slower section uses CMOS technology. The range of division ratios is 512 to 131071.

### **Reference divider**

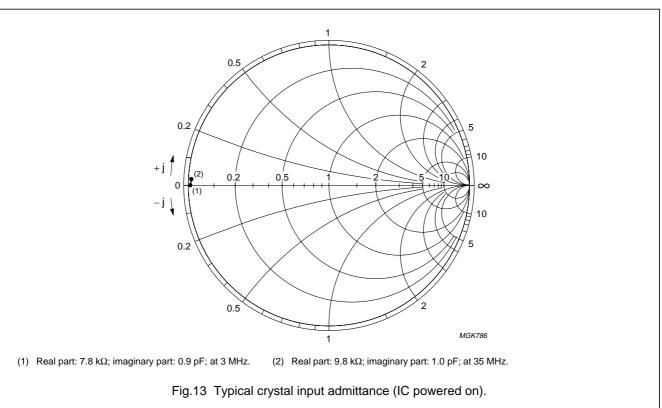

There is a common fully programmable 12-bit reference divider for the two synthesizers. The input  $f_{\text{XTALIN}}$  drives a pre-amplifier to provide the clock input for the reference

divider. This clock signal is also inverted and output on pin  $f_{XTALO}$  (open drain). A crystal connected between  $f_{XTALIN}$  and  $f_{XTALO}$  with suitable feedback components can be used to make an oscillator. An extra divide-by-2 block allows a reference comparison frequency for synthesizer B to be half the frequency of synthesizer A. This feature is selectable using the program bit SR. If the programmed reference divider ratio is R then the ratio for each synthesizer is as given in Table 1.

The range for the division ratio R is 8 to 4095. Opposite edges of the divider output are used to drive the phase detectors to ensure that active edges arrive at the phase detectors of each synthesizer at different times. This minimizes the potential for interference between the charge pumps of each loop. The reference divider consists of CMOS devices operating beyond 35 MHz.

| SR | SYNTHESIZER A | SYNTHESIZER B |

|----|---------------|---------------|

| 0  | R             | R             |

| 1  | R             | 2R            |

| Table 1 | Svnthesizer | ratio of | reference | divider |

|---------|-------------|----------|-----------|---------|

|         | Oynuncoizer | 1000     |           | aiviaci |

#### Phase comparators

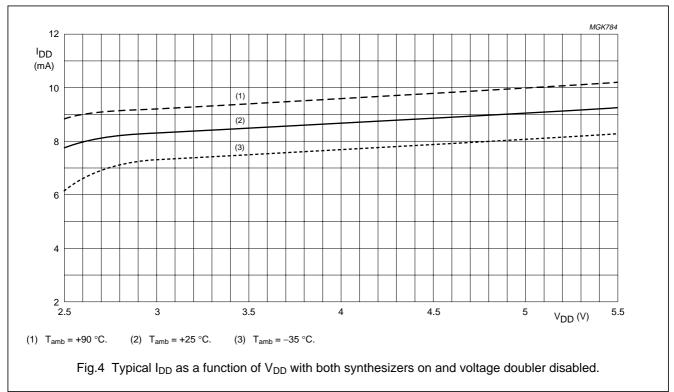

For each synthesizer, the outputs of the main and reference dividers drive a phase comparator where a charge pump produces phase error current pulses for integration in an external loop filter. The charge pump current is set by an external resistance R<sub>SET</sub> at pin I<sub>SET</sub>, where a temperature-independent voltage of 1.1 V is generated. R<sub>SET</sub> should be between 12 and 60 k $\Omega$ . The charge pump current, I<sub>CP</sub>, can be programmed to be either (12  $\times$  I<sub>SET</sub>) or (24  $\times$  I<sub>SET</sub>) with a maximum of 2.3 mA. The dead zone, caused by finite switching of current pulses, is cancelled by an internal delay in the phase detector thus giving improved linearity. The charge pump has a separate supply, V<sub>CC</sub>, which helps to reduce the interference on the charge pump output from other parts of the circuit.  $V_{CC}$  can be higher than  $V_{DD1}$  if a wider range on the VCO input is required. V<sub>CC</sub> must not be less than V<sub>DD1</sub>.

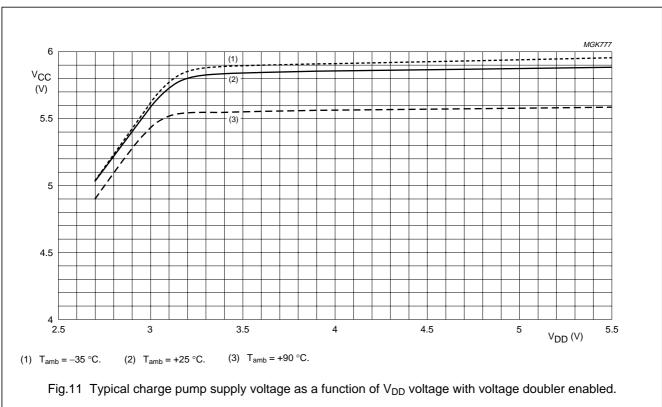

#### Voltage doubler

If required, there is a voltage doubler on-chip to supply the charge pumps at a higher level than the nominal available supply. The doubler operates from the digital supply V<sub>DD1</sub>, and is internally limited to a maximum output of 6 V. An external capacitor is required on pin V<sub>CC</sub> for smoothing, the capacitor required to develop the extra voltage is integrated on-chip. To minimize the noise being introduced to the charge pump output from the voltage doubler, the doubler clock is suppressed (provided both loops are in-lock) for the short time that the charge pumps are active. The doubler clock (RF/64) is derived from whichever main divider is operating (synthesizer A has priority). While both synthesizers are powered down (and the doubler is enabled), the doubler clock is supplied by a low-current internal oscillator. The doubler can be disabled by programming the bit VDON to logic 0, in order to allow an external charge pump supply to be used.

#### Out-of-lock indication/output ports

There is a common lock detector on-chip for the synthesizers. The lock condition of each, or both loops, is output via an open-drain transistor which drives pin P0/OOL (when out-of-lock, the transistor is turned on and therefore the output is forced LOW). The lock condition output is software selectable (see Table 4).

An out-of-lock condition is flagged when the phase error is greater than  $T_{OOL},$  which is approximately 30 ns.

The out-of-lock flag is only released after the first reference cycle where the phase error is less than  $T_{OOL}$ . The out-of-lock function can be disabled, via the serial bus,

and the pin P0/OOL can be used as a port output. Three other port outputs P1, P2 and P3 (open-drain transistors) are also available.

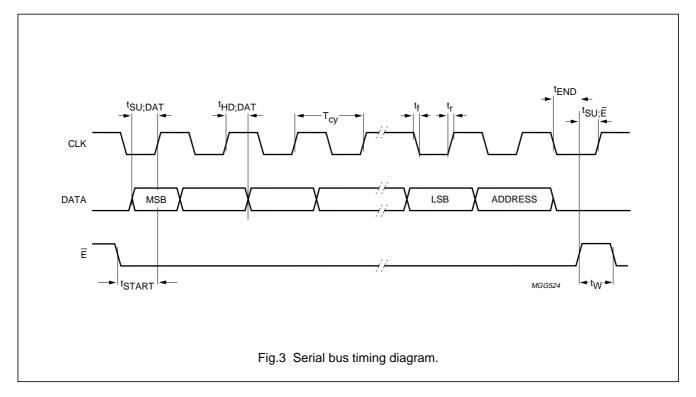

#### Serial programming bus

A simple 3-line unidirectional serial bus is used to program the circuit. The 3 lines are DATA, CLK and  $\overline{E}$  (enable). The data sent to the device is loaded in bursts framed by  $\overline{E}$ . Programming clock edges are ignored until  $\overline{E}$  goes active LOW. The programmed information is loaded into the addressed latch when  $\overline{E}$  returns inactive (HIGH). This is allowed when CLK is in either state without causing any consequences to the register data. Only the last 21 bits serially clocked into the device are retained within the programming register. Additional leading bits are ignored, and no check is made on the number of clock pulses. The fully static CMOS design uses virtually no current when the bus is inactive. It can always capture new programming data even during power-down of both synthesizers.

However when either synthesizer A or synthesizer B or both are powered-on, the presence of a TCXO signal is required at pin 8 ( $f_{XTALIN}$ ) for correct programming.

#### Data format

Data is entered with the most significant bit first. The leading bits make up the data field, while the trailing four bits are an address field. The address bits are decoded on the rising edge of  $\overline{E}$ . This produces an internal load pulse to store the data in the addressed latch. To ensure that data is correctly loaded on first power-up,  $\overline{E}$  should be held LOW and only taken HIGH after having programmed an appropriate register. To avoid erroneous divider ratios, the pulse is inhibited during the period when data is read by the frequency dividers. This condition is guaranteed by respecting a minimum  $\overline{E}$  pulse width after data transfer. The data format and register bit allocations are shown in Table 2.

### Table 2 Bit allocation

1997 Sep 03

| FIRST | T REGISTER BIT ALLOCATION                        |                                          |    |     |     |     |     |     |     |      | LAST |     |     |      |     |     |     |     |     |     |

|-------|--------------------------------------------------|------------------------------------------|----|-----|-----|-----|-----|-----|-----|------|------|-----|-----|------|-----|-----|-----|-----|-----|-----|

| p1    | p2                                               | р3                                       | p4 | p5  | p6  | p7  | p8  | p9  | p10 | p11  | p12  | p13 | p14 | p15  | p16 | p17 | p18 | p19 | p20 | p21 |

| dt16  | dt15 dt14 dt13 dt12 DATA FIELD dt4               |                                          |    |     |     |     | dt4 | dt3 | dt2 | dt1  | dt0  |     | ADE | RESS | 3   |     |     |     |     |     |

| Х     | Х                                                | VDON                                     | PO | OLA | OLB | CRA | CRB | Х   | Х   | sPDA | sPDB | P3  | P2  | P1   | Х   | Х   | 0   | 0   | 0   | 1   |

| MA16  | SYNTHESIZER A MAIN DIVIDER COEFFICIENT MA0 0 1 0 |                                          |    |     |     |     |     |     | 0   |      |      |     |     |      |     |     |     |     |     |     |

| 0     | 0                                                | 0 0 SR R11 REFERENCE DIVIDER COEFFICIENT |    |     |     |     |     |     |     | R0   | 0    | 1   | 0   | 1    |     |     |     |     |     |     |

| MB16  |                                                  | SYNTHESIZER B MAIN DIVIDER COEFFICIENT M |    |     |     |     |     |     | MB0 | 0    | 1    | 1   | 0   |      |     |     |     |     |     |     |

|       | RESERVED FOR TEST <sup>(1)</sup> 0 0 0           |                                          |    |     |     |     |     |     | 0   | 0    |      |     |     |      |     |     |     |     |     |     |

| 0     | 0                                                | 0                                        | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | sPBF | 0   | 0   | 1   | 0   | 0   | 0   |

### Note

S

1. The test register should not be programmed with any other values except all zeros for normal operation.

Table 3

Bit allocation description

| SYMBOL            | DESCRIPTION                                                            |

|-------------------|------------------------------------------------------------------------|

| sPDA, sPDB        | software power-down for synthesizers A and B (0 = power-down)          |

| sPBF              | software power-on for $f_{xtal}$ buffer (1 = buffer on)                |

| P3, P2, P1 and P0 | bits output to pins 1, 2, 9 and 19 (1 = high impedance)                |

| VDON              | voltage doubler enable (1 = doubler enabled)                           |

| OLA, OLB          | out-of-lock select; selects signal output to pin 19 (see Table 4)      |

| CRA, CRB          | charge pump A/B current to I <sub>SET</sub> ratio select (see Table 5) |

| SR                | reference frequency ratio select (see Table 6)                         |

Table 4

Out-of-lock select

| OLA | OLB | OUTPUT AT PIN 19                   |

|-----|-----|------------------------------------|

| 0   | 0   | P0                                 |

| 0   | 1   | lock status of loop B; OOLB        |

| 1   | 0   | lock status of loop A; OOLA        |

| 1   | 1   | logic OR function of loops A and B |

for radio communications

Low-power dual frequency synthesizer

Product specification

#### Table 5 Charge pump current ratio

| CRA/CRB | CURRENT AT PUMP              |

|---------|------------------------------|

| 0       | $I_{CP} = 12 \times I_{SET}$ |

| 1       | $I_{CP} = 24 \times I_{SET}$ |

| Table 6         Reference division ratio | ) |

|------------------------------------------|---|

|------------------------------------------|---|

| SR | SYNTHESIZER A | SYNTHESIZER B |

|----|---------------|---------------|

| 0  | R             | R             |

| 1  | R             | 2R            |

#### Power-down modes

The device can be powered down either via pin HPD (active LOW = power-down) or via the serial bus (bits sPDA and sPDB, logic 0 = power-down).

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

#### The synthesizers are powered up when both hardware and software Power-down signals are at logic 1. When only one synthesizer is powered down, the functions common to both will be maintained (independent of the state of sPBF). When both synthesizers are powered down, the $f_{xtal}$ buffer can be maintained in an active state by setting sPBF to logic 1. This will allow any system clock derived from the $f_{XTALO}$ buffered output to remain on in power-down. Note that sPBF is independent of the state of HPD. When both synthesizers are switched off, the voltage doubler (if enabled) will remain active drawing a reduced current. An internal oscillator will drive the doubler in this situation. If both synthesizers have been in a power-down condition, then when one or both synthesizers are reactivated, the reference and main

dividers restart in such a way as to avoid large random

phase errors at the phase comparator.

| SYMBOL                              | PARAMETER                                                                             | MIN. | MAX.                   | UNIT |

|-------------------------------------|---------------------------------------------------------------------------------------|------|------------------------|------|

| V <sub>DD1</sub> , V <sub>DD2</sub> | DC range of digital power supply voltage with respect to DGND                         | -0.3 | +6.0                   | V    |

| V <sub>CC</sub>                     | DC charge pump supply voltage with respect to AGND                                    | -0.3 | +6.0                   | V    |

| $\Delta V_{CC-DD}$                  | difference in voltage between V <sub>CC</sub> and V <sub>DD1</sub> , V <sub>DD2</sub> | -0.3 | +6.0                   | V    |

| V <sub>n</sub>                      | DC voltage at pins 1, 2, 5, 6, 8 to 15, 19 and 20 with respect to DGND                | -0.3 | V <sub>DD1</sub> + 0.3 | V    |

| V <sub>3, 17</sub>                  | DC voltage at pins 3 and 17 with respect to AGND                                      | -0.3 | V <sub>CC</sub> + 0.3  | V    |

| $\Delta V_{GND}$                    | difference in voltage between AGND and DGND (these pins should be connected together) | -0.3 | +0.3                   | V    |

| T <sub>stg</sub>                    | storage temperature                                                                   | -55  | +125                   | °C   |

| T <sub>amb</sub>                    | operating ambient temperature                                                         | -30  | +85                    | °C   |

#### HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

### Product specification

### UMA1015AM

### CHARACTERISTICS

$V_{DD1}$  =  $V_{DD2}$  = 2.7 to 5.5 V;  $V_{CC}$  = 2.7 to 6.0 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                                     | PARAMETER                                                                                                       | CONDITIONS                                                                                             | MIN.      | TYP.                    | MAX. | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------|-------------------------|------|------|

| Supplies; (                                | V <sub>DD1</sub> , V <sub>DD2</sub> and V <sub>CC</sub> ) voltage                                               | e doubler disabled, external su                                                                        | pply on \ | / <sub>cc</sub>         |      |      |

| V <sub>DD1</sub> , V <sub>DD2</sub>        | digital supply voltage                                                                                          | $V_{DD1} = V_{DD2}$                                                                                    | 2.7       | -                       | 5.5  | V    |

| I <sub>DD1</sub> + I <sub>DD2</sub>        | total digital supply current from $V_{DD1}$ and $V_{DD2}$                                                       | $f_{XTAL} = 12.8 \text{ MHz};$<br>both synthesizers on;<br>$V_{DD1} = V_{DD2} = 3 \text{ V}$           | _         | 8.7                     | -    | mA   |

|                                            |                                                                                                                 | $f_{XTAL}$ = 12.8 MHz;<br>both synthesizers on;<br>$V_{DD1} = V_{DD2} = 5.5 V$                         | _         | -                       | 12.5 | mA   |

| I <sub>DDpda</sub> ,<br>I <sub>DDpdb</sub> | total digital supply current from $V_{DD1}$ and $V_{DD2}$ with one synthesizer in                               | $f_{XTAL}$ = 12.8 MHz; one<br>synthesizer powered down;<br>$V_{DD1} = V_{DD2} = 3 V$                   | _         | 5.0                     | -    | mA   |

| power-down mode                            |                                                                                                                 | $f_{XTAL}$ = 12.8 MHz; one<br>synthesizer powered down;<br>$V_{DD1} = V_{DD2} = 5.5 V$                 | _         | -                       | 7.5  | mA   |

| I <sub>DD(xtal)</sub>                      | digital supply current from<br>V <sub>DD1</sub> with both<br>synthesizers powered<br>down and crystal buffer on | $f_{XTAL} = 12.8 \text{ MHz}; V_{HPD} = 0 \text{ V};$<br>sPBF = 1; $V_{DD1} = V_{DD2} = 3 \text{ V}$   | -         | 0.5                     | _    | mA   |

|                                            |                                                                                                                 | $f_{XTAL} = 12.8 \text{ MHz}; V_{HPD} = 0 \text{ V};$<br>sPBF = 1; $V_{DD1} = V_{DD2} = 5.5 \text{ V}$ | -         | -                       | 1.15 | mA   |

| I <sub>DDpd</sub>                          | digital supply current in<br>power-down mode                                                                    | both synthesizers powered<br>down; V <sub>HPD</sub> = 0 V; sPBF = 0                                    | -         | -                       | 60   | μA   |

| V <sub>CC</sub>                            | charge pump supply voltage                                                                                      | $V_{CC} \ge V_{DD}$                                                                                    | 2.7       | -                       | 6.0  | V    |

| I <sub>CC</sub>                            | charge pump supply current                                                                                      | both synthesizers on and in<br>lock; f <sub>ref</sub> = 12.5 kHz                                       | -         | -                       | 25   | μA   |

| I <sub>CCpd</sub>                          | charge pump supply<br>current in power-down<br>mode                                                             | both synthesizers powered down                                                                         | -         | -                       | 25   | μA   |

| Voltage dou                                | ubler enabled                                                                                                   |                                                                                                        |           |                         | •    |      |

| I <sub>DD</sub>                            | total digital supply current from $V_{DD1}$ and $V_{DD2}$                                                       | $f_{XTAL}$ = 12.8 MHz; both<br>synthesizers on and in lock;<br>$V_{DD1}$ = 3 V; $f_{RF}$ = 900 MHz     | _         | 9.2                     | 12   | mA   |

| I <sub>DDpd</sub>                          | total digital supply current in power-down mode from $V_{\text{DD1}}$ and $V_{\text{DD2}}$                      | both synthesizers powered down; $V_{DD1} = 3 V$ ; $V_{HPD} = 0 V$ ; sPBF = 0                           | -         | 0.25                    | 0.4  | mA   |

| V <sub>CCvd</sub>                          | charge pump supply voltage                                                                                      | DC current drawn from $V_{CC} = 50 \ \mu$ A; f <sub>RF</sub> > 100 MHz                                 | 4.2       | 2V <sub>DD1</sub> - 0.6 | 6.0  | V    |

| SYMBOL                   | PARAMETER                                          | CONDITIONS                                                                                                                                                             | MIN.                | TYP. | MAX.                   | UNIT |

|--------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------------------------|------|

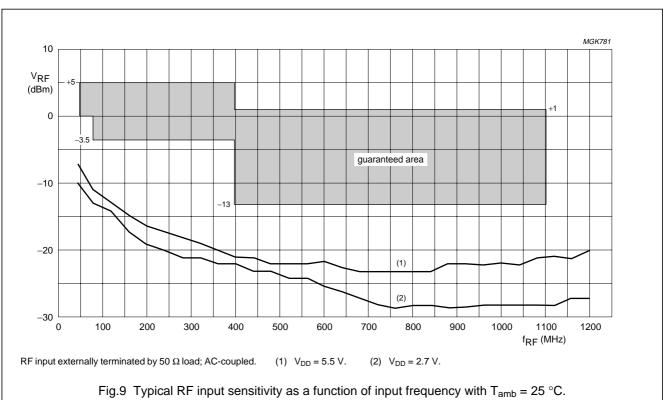

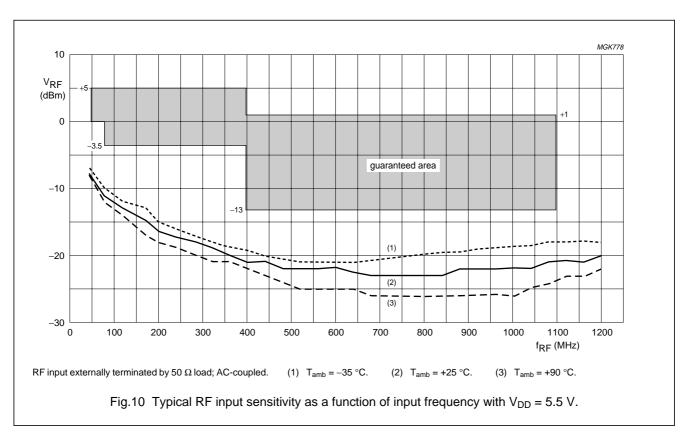

| RF main div              | vider input; RFA and RFB                           |                                                                                                                                                                        |                     | !    | Į                      |      |

| f <sub>RF</sub>          | RF input frequency                                 |                                                                                                                                                                        | 50                  | _    | 1100                   | MHz  |

| V <sub>RF(rms)</sub>     | RF input signal voltage<br>(RMS value; AC coupled) | R <sub>s</sub> = 50 Ω;<br>f <sub>RF</sub> = 400 to 1100 MHz                                                                                                            | 50                  | -    | 250                    | mV   |

|                          |                                                    | $R_{s} = 50 \Omega; f_{RF} = 80 \text{ to } 400 \text{ MHz}$                                                                                                           | 150                 | -    | 400                    | mV   |

|                          |                                                    | $R_s = 50 \Omega; f_{RF} = 50 \text{ to } 80 \text{ MHz}$                                                                                                              | 225                 | -    | 400                    | mV   |

| ZI                       | input impedance<br>(real part)                     | f <sub>RF</sub> = 1 GHz; indicative, not tested                                                                                                                        | -                   | 300  | -                      | Ω    |

| CI                       | input capacitance                                  | indicative, not tested                                                                                                                                                 | -                   | 1    | -                      | pF   |

| R <sub>pm</sub>          | principle main divider ratio                       |                                                                                                                                                                        | 512                 | -    | 131071                 |      |

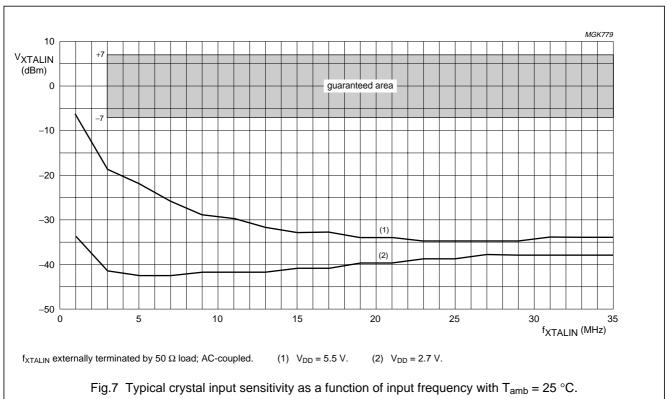

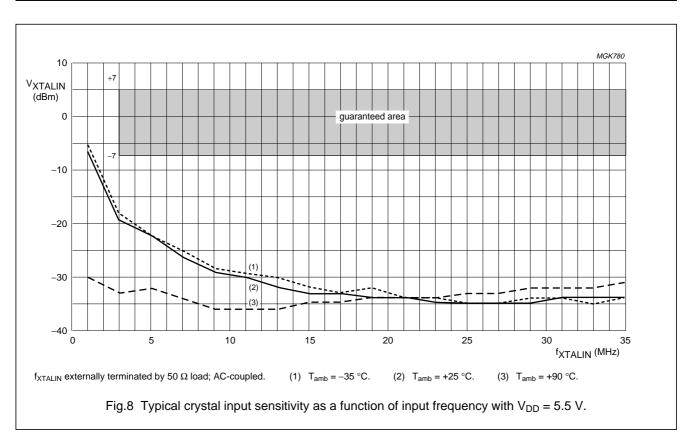

| Reference of             | divider input; f <sub>XTALIN</sub>                 |                                                                                                                                                                        |                     |      |                        |      |

| f <sub>XTALIN</sub>      | reference input frequency from crystal             |                                                                                                                                                                        | 3                   | -    | 35                     | MHz  |

| V <sub>XTALIN(rms)</sub> | sinusoidal input voltage<br>(RMS value)            |                                                                                                                                                                        | 100                 | -    | 500                    | mV   |

| ZI                       | input impedance<br>(real part)                     | $f_{XTALIN} = 12.8 \text{ MHz}; \text{ indicative}, $ not tested                                                                                                       | -                   | 10   | -                      | kΩ   |

| Cl                       | input capacitance                                  | indicative, not tested                                                                                                                                                 | -                   | 1    | -                      | pF   |

| R <sub>rd</sub>          | reference divider ratio                            |                                                                                                                                                                        | 8                   | -    | 4095                   |      |

| Charge pur               | np current setting resistor                        | input; I <sub>SET</sub>                                                                                                                                                |                     |      | -                      |      |

| V <sub>SET</sub>         | voltage output on I <sub>SET</sub>                 | R <sub>SET</sub> = 12 to 60 kΩ                                                                                                                                         | -                   | 1.1  | -                      | V    |

|                          | np outputs; CPA and CPB                            | 1 -                                                                                                                                                                    | 1                   | ļ    | I                      |      |

| I <sub>cp</sub>          | charge pump sink or<br>source current              | $\label{eq:Rset} \begin{array}{l} R_{SET} = 15 \ k\Omega;\\ CRA/CRB = logic \ 1;\\ I_{cp} = I_{SET} \times 24;\\ V_{cp} = 0.4 \ V \ to \ V_{CC} - 0.5 \ V \end{array}$ | 1.3                 | 1.75 | 2.3                    | mA   |

|                          |                                                    | $R_{SET} = 15 \text{ k}\Omega;$ $CRA/CRB = \text{logic 0};$ $I_{cp} = I_{SET} \times 12;$ $V_{cp} = 0.4 \text{ V to } V_{CC} - 0.5 \text{ V}$                          | 0.7                 | 0.9  | 1.2                    | mA   |

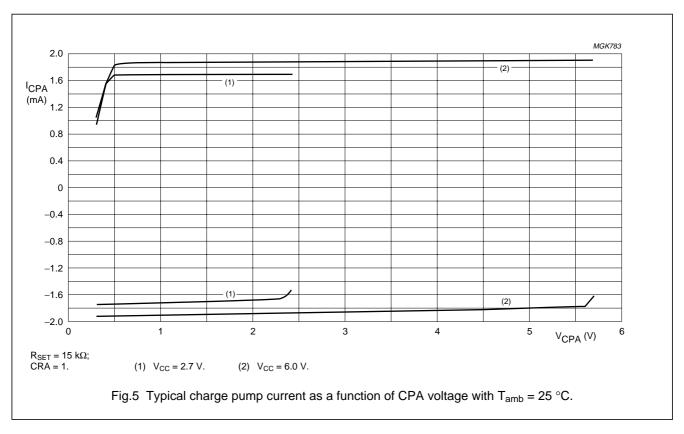

| ILI                      | charge pump off leakage current                    | $V_{cp} = 0.4$ V to $V_{CC} - 0.5$ V                                                                                                                                   | -5                  | ±1   | +5                     | nA   |

| Logic input              | signal levels; DATA, CLK,                          | E and HPD                                                                                                                                                              |                     |      |                        |      |

| V <sub>IH</sub>          | HIGH level input voltage                           | at logic 1                                                                                                                                                             | 0.7V <sub>DD1</sub> | -    | V <sub>DD1</sub> + 0.3 | V    |

| V <sub>IL</sub>          | LOW level input voltage                            | at logic 0                                                                                                                                                             | -0.3                | -    | 0.3V <sub>DD1</sub>    | V    |

| I <sub>bias</sub>        | input bias currents                                | at logic 1 or logic 0                                                                                                                                                  | -5                  | _    | +5                     | μA   |

| CI                       | input capacitance                                  | indicative, not tested                                                                                                                                                 | -                   | 1    | -                      | pF   |

| Port output              | s/Out-of-lock; P0/OOL, P1                          | , P2, P3 and f <sub>XTALO</sub> - open drain                                                                                                                           | outputs             |      |                        |      |

| V <sub>OL</sub>          | LOW level output voltage                           | I <sub>sink</sub> < 0.4 mA                                                                                                                                             | _                   | _    | 0.4                    | V    |

### SERIAL TIMING CHARACTERISTICS

$V_{DD1} = 3 \text{ V}; \text{ T}_{amb} = 25 \text{ °C}; \text{ unless otherwise specified.}$

| SYMBOL                           | PARAMETER                             | MIN. | TYP. | MAX. | UNIT |  |

|----------------------------------|---------------------------------------|------|------|------|------|--|

| Serial prog                      | Serial programming clock; CLK         |      |      |      |      |  |

| t <sub>r</sub> , t <sub>f</sub>  | input rise and fall times             | _    | 10   | 40   | ns   |  |

| T <sub>cy</sub>                  | clock period                          | 100  | _    | -    | ns   |  |

| Enable pro                       | Enable programming; E                 |      |      |      |      |  |

| t <sub>START</sub>               | delay to rising clock edge            | 40   | -    | -    | ns   |  |

| t <sub>END</sub>                 | delay from last falling clock edge    | -20  | _    | -    | ns   |  |

| t <sub>W</sub>                   | minimum inactive pulse width          | 4000 | _    | -    | ns   |  |

| t <sub>SU;Ē</sub>                | enable set-up time to next clock edge | 20   | _    | -    | ns   |  |

| Register serial input data; DATA |                                       |      |      |      |      |  |

| t <sub>SU;DAT</sub>              | input data to clock set-up time       | 20   | -    | _    | ns   |  |

| t <sub>HD;DAT</sub>              | input data to clock hold time         | 20   | _    | -    | ns   |  |

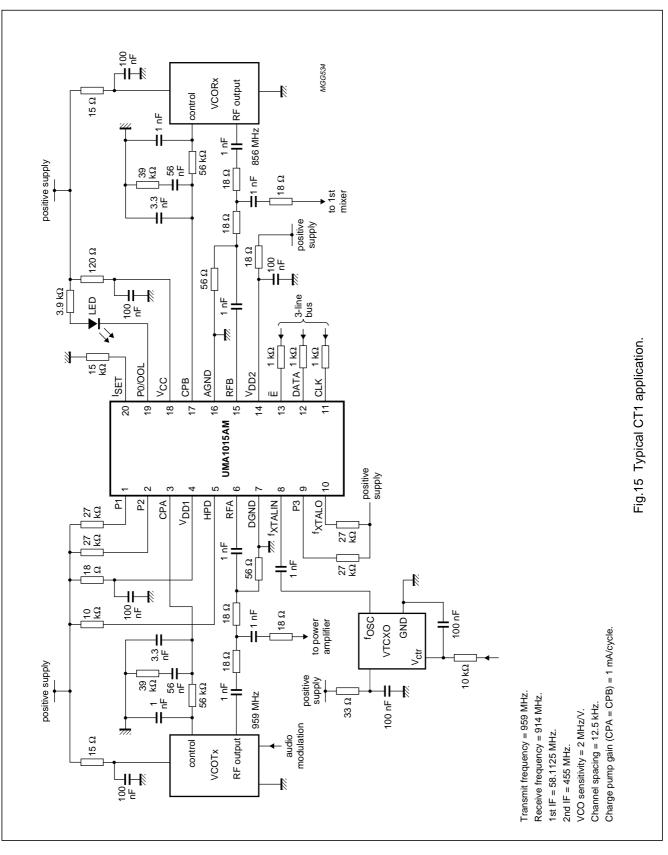

### **APPLICATION INFORMATION**

UMA1015AM

Product specification

#### Product specification

## Low-power dual frequency synthesizer for radio communications

### PACKAGE OUTLINE

### UMA1015AM

### SOLDERING

### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"IC Package Databook"* (order code 9398 652 90011).

#### **Reflow soldering**

Reflow soldering techniques are suitable for all SSOP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45 °C.

#### Wave soldering

Wave soldering is **not** recommended for SSOP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices. If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end.

#### Even with these conditions, only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### **Repairing soldered joints**

Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

#### Product specification

### UMA1015AM

### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |

| Where application information is given, it is advisory and does not form part of the specification.                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |  |  |

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

UMA1015AM

NOTES

UMA1015AM

NOTES

UMA1015AM

NOTES

### Philips Semiconductors – a worldwide company

Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB, Argentina: see South America Tel. +31 40 27 82785, Fax. +31 40 27 88399 Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113, New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND, Tel. +61 2 9805 4455, Fax. +61 2 9805 4466 Tel. +64 9 849 4160, Fax. +64 9 849 7811 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. +43 160 1010, Norway: Box 1, Manglerud 0612, OSLO, Fax. +43 160 101 1210 Tel. +47 22 74 8000, Fax. +47 22 74 8341 Belarus: Hotel Minsk Business Center, Bld. 3, r. 1211, Volodarski Str. 6, 220050 MINSK, Tel. +375 172 200 733, Fax. +375 172 200 773 Philippines: Philips Semiconductors Philippines Inc., 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Belgium: see The Netherlands Metro MANILA, Tel. +63 2 816 6380, Fax. +63 2 817 3474 Brazil: see South America Poland: UI. Lukiska 10, PL 04-123 WARSZAWA, Bulgaria: Philips Bulgaria Ltd., Energoproject, 15th floor, Tel. +48 22 612 2831, Fax. +48 22 612 2327 51 James Bourchier Blvd., 1407 SOFIA, Tel. +359 2 689 211, Fax. +359 2 689 102 Portugal: see Spain Romania: see Italy Canada: PHILIPS SEMICONDUCTORS/COMPONENTS, Tel. +1 800 234 7381 Russia: Philips Russia, UI. Usatcheva 35A, 119048 MOSCOW, Tel. +7 095 755 6918, Fax. +7 095 755 6919 China/Hong Kong: 501 Hong Kong Industrial Technology Centre, 72 Tat Chee Avenue, Kowloon Tong, HONG KONG, Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231, Tel. +852 2319 7888, Fax. +852 2319 7700 Tel. +65 350 2538, Fax. +65 251 6500 Slovakia: see Austria Colombia: see South America Czech Republic: see Austria Slovenia: see Italy Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S, South Africa: S.A. PHILIPS Pty Ltd., 195-215 Main Road Martindale, Tel. +45 32 88 2636, Fax. +45 31 57 0044 2092 JOHANNESBURG, P.O. Box 7430 Johannesburg 2000, Tel. +27 11 470 5911, Fax. +27 11 470 5494 Finland: Sinikalliontie 3, FIN-02630 ESPOO, Tel. +358 9 615800, Fax. +358 9 61580920 South America: Rua do Rocio 220, 5th floor, Suite 51, 04552-903 São Paulo, SÃO PAULO - SP, Brazil, France: 4 Rue du Port-aux-Vins. BP317. 92156 SURESNES Cedex. Tel. +55 11 821 2333, Fax. +55 11 829 1849 Tel. +33 1 40 99 6161, Fax. +33 1 40 99 6427 Spain: Balmes 22 08007 BARCELONA Germany: Hammerbrookstraße 69, D-20097 HAMBURG, Tel. +34 3 301 6312. Fax. +34 3 301 4107 Tel. +49 40 23 53 60, Fax. +49 40 23 536 300 Sweden: Kottbygatan 7, Akalla, S-16485 STOCKHOLM, Greece: No. 15, 25th March Street, GR 17778 TAVROS/ATHENS, Tel. +46 8 632 2000, Fax. +46 8 632 2745 Tel. +30 1 4894 339/239, Fax. +30 1 4814 240 Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH, Hungary: see Austria Tel. +41 1 488 2686, Fax. +41 1 481 7730 India: Philips INDIA Ltd, Band Box Building, 2nd floor, Taiwan: Philips Semiconductors, 6F, No. 96, Chien Kuo N. Rd., Sec. 1, 254-D, Dr. Annie Besant Road, Worli, MUMBAI 400 025, TAIPEI, Taiwan Tel. +886 2 2134 2865, Fax. +886 2 2134 2874 Tel. +91 22 493 8541, Fax. +91 22 493 0966 Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd. Indonesia: see Singapore 209/2 Sanpavuth-Bangna Road Prakanong, BANGKOK 10260, Ireland: Newstead, Clonskeagh, DUBLIN 14, Tel. +66 2 745 4090, Fax. +66 2 398 0793 Tel. +353 1 7640 000, Fax. +353 1 7640 200 Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL, Israel: RAPAC Electronics, 7 Kehilat Saloniki St, PO Box 18053, Tel. +90 212 279 2770, Fax. +90 212 282 6707 TEL AVIV 61180, Tel. +972 3 645 0444, Fax. +972 3 649 1007 Ukraine: PHILIPS UKRAINE, 4 Patrice Lumumba str., Building B, Floor 7, Italy: PHILIPS SEMICONDUCTORS, Piazza IV Novembre 3, 252042 KIEV, Tel. +380 44 264 2776, Fax. +380 44 268 0461 20124 MILANO, Tel. +39 2 6752 2531, Fax. +39 2 6752 2557 United Kingdom: Philips Semiconductors Ltd., 276 Bath Road, Haves. Japan: Philips Bldg 13-37, Kohnan 2-chome, Minato-ku, TOKYO 108, MIDDLESEX UB3 5BX, Tel. +44 181 730 5000, Fax. +44 181 754 8421 Tel. +81 3 3740 5130, Fax. +81 3 3740 5077 United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409, Korea: Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. +1 800 234 7381 Tel. +82 2 709 1412, Fax. +82 2 709 1415 Uruguay: see South America Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR, Vietnam: see Singapore Tel. +60 3 750 5214, Fax. +60 3 757 4880 Yugoslavia: PHILIPS, Trg N. Pasica 5/v, 11000 BEOGRAD, Mexico: 5900 Gateway East, Suite 200, EL PASO, TEXAS 79905, Tel. +381 11 625 344, Fax.+381 11 635 777 Tel. +9-5 800 234 7381

For all other countries apply to: Philips Semiconductors, Marketing & Sales Communications, Building BE-p, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Fax. +31 40 27 24825

© Philips Electronics N.V. 1997

Middle East: see Italy

SCA55

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

437027/1200/03/pp24

Date of release: 1997 Sep 03

Document order number: 9397 750 02704

Let's make things better.

Internet: http://www.semiconductors.philips.com