# RICOH

# **Microprocessor Supervisory Circuit**

**R5106N SERIES**

NO. EA-169-070711

±30%

## OUTLINE

The R5106N Series are CMOS-based  $\mu$  con supervisory circuit, or high accuracy and ultra low supply current voltage detector with built-in delay and watchdog timer. When the supply voltage is down across the threshold, or the watchdog timer does not detect the system clock from the  $\mu$  con, the reset output is generated. The voltage detector circuit is used for the system reset, etc. The detector threshold is fixed internally, and the tolerance is  $\pm 1.0\%$ . The released delay time (Power-on Reset Delay) circuit is built-in, and output delay time is adjustable with an external capacitor. When the supply voltage becomes the released voltage, the reset state will be maintained during the delay time. The time out period of the watchdog timer can be also set with an external capacitor. The output type of the reset is selectable, Nch open-drain, or CMOS. There is a function to stop supervising clock by the watchdog timer (INH function). The package is small SOT-23-6.

## **FEATURES**

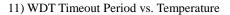

Built-in a watchdog timer's time out period accuracy

• Timeout period for watchdog and generating a reset signal can be set by an external capacitor

- Detector Threshold Voltage ...... 0.1V stepwise setting in the range from 1.5V to 5.5V

- Supply current ...... Typ. 11µA

- High Accuracy Output Voltage of Detector Threshold ...... ±1.0%

- Power-on Reset Delay Time accuracy ...... ±20%

- Power-on reset delay time of the voltage detector can be set with an external capacitor.

- Small Package ..... SOT-23-6

## APPLICATION

• Supervisory circuit for equipment with using microprocessors.

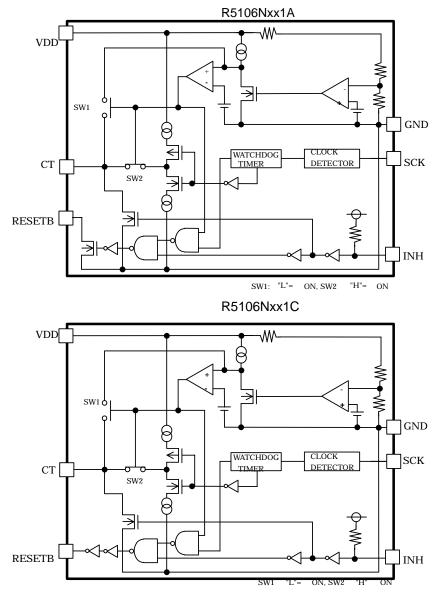

## **BLOCK DIAGRAMS**

## **SELECTION GUIDE**

The selection can be made with designating the part number as shown below:

R5106N<u>xx</u>1x-TR ←part Number

$\uparrow \uparrow \uparrow \uparrow$

a bcd

| Code | Descriptions                                                                                                          |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| а    | Designation of Package Type;<br>N: SOT-23-6 (2.8mmx2.9mm)                                                             |  |  |

| b    | Designation of Detector Threshold Voltage (-VDET)<br>0.1V stepwise setting is possible in the range from 1.5V to 5.5V |  |  |

| с    | Designation of the output type of RESETB<br>A: Nch open-drain output<br>C: CMOS output                                |  |  |

| d    | Designation of Taping Type                                                                                            |  |  |

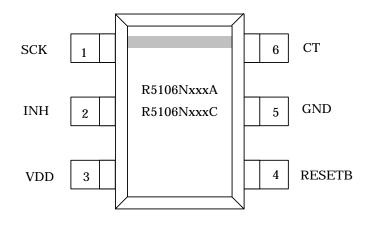

## **PIN CONFIGURATION**

SOT-23-6

## **PIN DESCRIPTION**

| Pin No | Symbol | Pin Description                                                                                                                                  |  |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | SCK    | Clock Input Pin from Microprocessor                                                                                                              |  |

| 2      | INH    | Inhibit Pin ("L": Inhibit the watchdog timer)                                                                                                    |  |

| 3      | Vdd    | Power supply Pin                                                                                                                                 |  |

| 4      | RESETB | Output Pin for Reset signal of Watchdog timer and Voltage<br>Detector. (Output "L" at detecting Detector Threshold and<br>Watchdog Timer Reset.) |  |

| 5      | GND    | Ground Pin                                                                                                                                       |  |

| 6      | СТ     | External Capacitor Pin for Setting Reset and Watchdog Timeout<br>Periods and delay time of Voltage Detector                                      |  |

# **ABSOLUTE MAXIMUM RATINGS**

|         |                             |                       | Topt=25°C, Vss=0V |      |  |

|---------|-----------------------------|-----------------------|-------------------|------|--|

| Symbol  | Item                        |                       | Rating            | Unit |  |

| Vin     | Supply Voltage              |                       | -0.3~7.0          | V    |  |

| Vст     | - Output Voltage            | Voltage of C⊤ Pin     | -0.3~VIN+0.3      | V    |  |

| Vresetb |                             | Voltage of RESETB Pin | -0.3~7.0          | V    |  |

| Vsck    | - Input Voltage             | Voltage of SCK Pin    | -0.3~7.0          | V    |  |

| VINH    |                             | Voltage of INH Pin    | -0.3~7.0          | V    |  |

| RESETB  | Output Current              | Current of RESETB Pin | 20                | mA   |  |

| PD      | Power Dissipation           |                       | 250               | mW   |  |

| Topt    | Operating Temperature Range |                       | -40~+105          | °C   |  |

| Tstg    | Storage Temperature Range   |                       | -55~+125          | °C   |  |

## **ELECTRICAL CHARACTERISTICS**

**R5106NxxxA/C** Unless otherwise specified, VIN=6.0V, CT=0.1uF, Rpull-up=100kΩ

Topt=25°C

| Symbol                        | ltem                                          | Conditions                                                        | Min.                    | Тур.             | Max.                    | Unit       |

|-------------------------------|-----------------------------------------------|-------------------------------------------------------------------|-------------------------|------------------|-------------------------|------------|

| Vin                           | Operating Voltage                             |                                                                   | 0.9                     |                  | 6.0                     | V          |

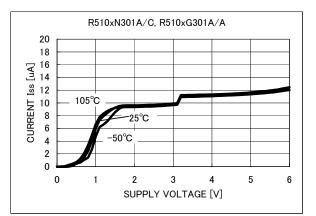

| lss                           | Supply Current                                | V <sub>IN</sub> =(-VDET)+0.5V<br>Clock pulse input                |                         | 11               | 15                      | μA         |

|                               |                                               | Voltage Detector                                                  |                         |                  |                         |            |

| -VDET                         | Detector Threshold                            | VIN pin Threshold                                                 | x0.990<br><b>x0.972</b> |                  | x1.010<br><b>x1.015</b> | V          |

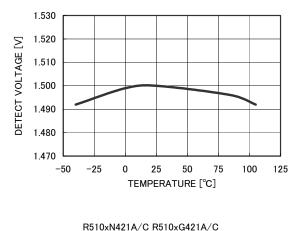

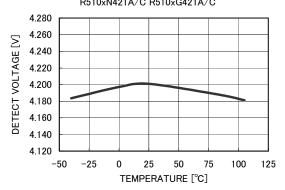

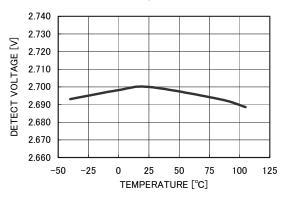

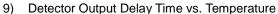

| ∆-V <sub>DET</sub> /<br>∆Topt | Detector Threshold<br>Temperature Coefficient | -40°C≤Topt≤105°C                                                  |                         | ±100             |                         | ppm/<br>°C |

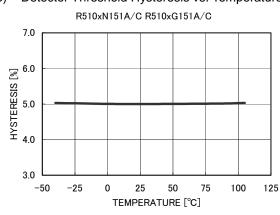

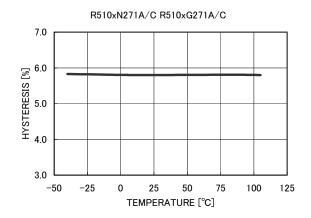

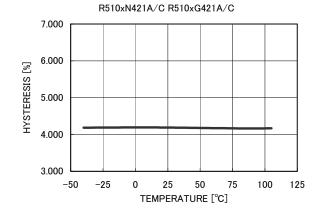

| VHYS                          | Detector Threshold<br>Hysteresis              |                                                                   | (-VDET)<br>x0.03        | (-Vdet)<br>x0.05 | (-Vdet)<br>x0.07        | V          |

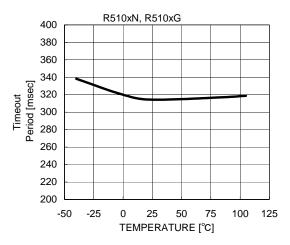

| tр∟н                          | Output Delay Time                             | Cτ=0.1μF                                                          | 340                     | 370              | 467                     | ms         |

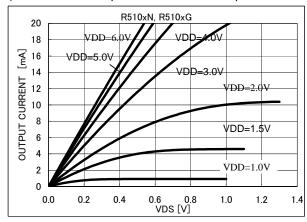

| DOUTN                         | Output Current (RESETB<br>Output pin)         | Nch, VDD=1.2V, VDS=0.1V                                           | 0.38                    | 0.80             |                         | mA         |

| DOUTP                         | Output Current (RESETB<br>Output pin)         | Pch, V <sub>DD</sub> =6.0V, V <sub>DS</sub> =0.5V<br>(R5106NxxxC) | 0.65                    | 0.90             |                         | mA         |

|                               |                                               | Watchdog Timer                                                    |                         |                  |                         |            |

| Twd                           | Watchdog Timeout period                       | C⊤=0.1uF                                                          | 230                     | 310              | 450                     | ms         |

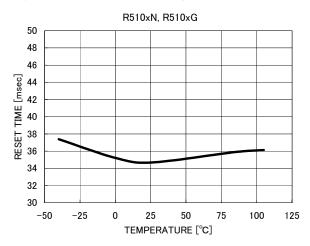

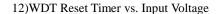

| Twr                           | Reset Hold Time of WDT                        | C⊤=0.1uF                                                          | 29                      | 34               | 48                      | ms         |

| Vscкн                         | SCK Input "H"                                 |                                                                   | VINx0.8                 |                  | 6.0                     | V          |

| VSCKL                         | SCK Input "L"                                 |                                                                   | 0.0                     |                  | VINx0.2                 | V          |

| VINHH                         | INH Input "H"                                 |                                                                   | 1.0                     |                  | 6.0                     | V          |

| VINHL                         | INH Input "L"                                 |                                                                   | 0.00                    |                  | 0.35                    | V          |

| RINH                          | INH pull-up Resistance                        |                                                                   | 60                      | 110              | 164                     | kΩ         |

| Тѕски                         | SCK Input Pulse Width                         | V <sub>SCKL</sub> =VINx0.2,<br>VSCKH=VINx0.8                      | 500                     |                  |                         | ns         |

The bold type values are guaranteed by design.

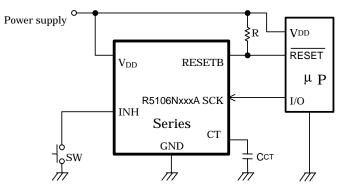

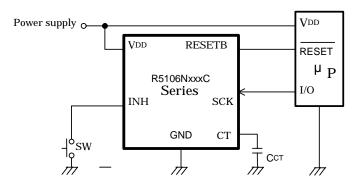

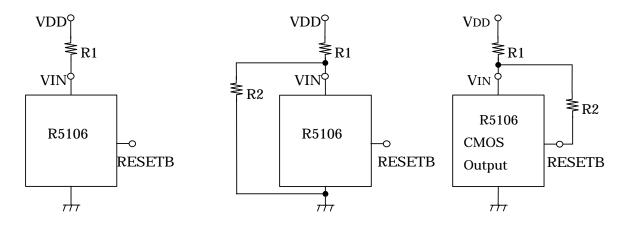

## **TYPICAL APPLICATIONS**

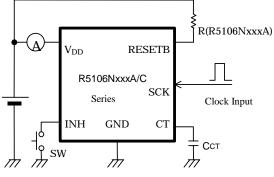

## **TEST CIRCUIT**

Supply Current Test Circuit

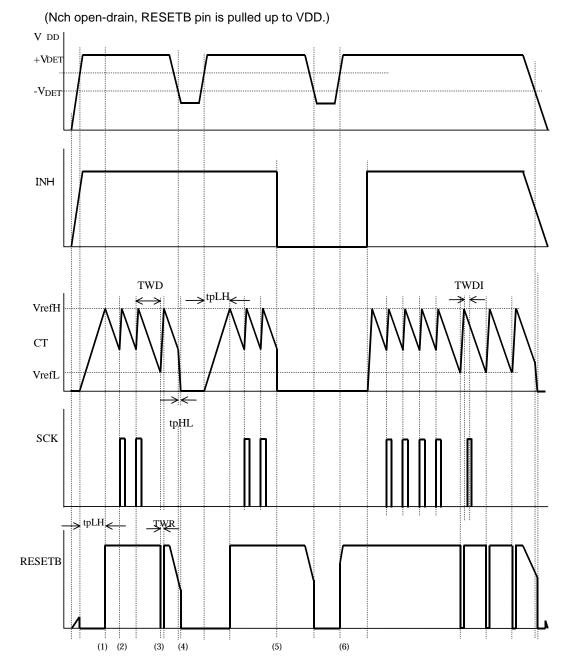

# TIMING DIAGRAM (R5106NxxxA/R5106NxxxC)

## OPERATION

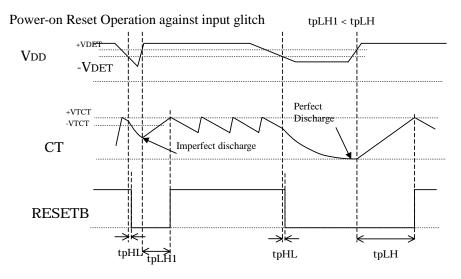

- <sup>①</sup> When the power supply, VDD pin voltage becomes more than the released voltage (+V<sub>DET</sub>), after the released delay time (or the power on reset time tpLH), the output of RESETB becomes "H" level.

- ② When the SCK pulse is input, the watchdog timer is cleared, and CT pin mode changes from discharge mode to charge mode. When the CT pin voltage becomes higher than VREFH, the mode will change into discharge, and next watchdog time count starts.

- ③ Unless the SCK pulse is input, WDT will not be cleared, and during the charging period of CT pin, RESETB="L".

- ④ When the VDD pin becomes lower than the detector threshold voltage, RESETB outputs "L".

- ⑤ If "L" signal is input to the INH pin, the RESETB outputs "H", regardless the SCK clock state.

- <sup>®</sup> During the "L" period of INH pin, the voltage detector monitors the supply voltage.

- ⑦ When the signal to the INH pin is set from "L" to "H", the watchdog starts supervising the system clock, or charge cycle to the CT pin starts, the capacitor connected to the CT pin is charged with the current of setting Reset time of WDT

\* Watchdog Timeout period/Reset hold time

The watchdog timeout period and reset hold time can be set with an external capacitor to CT pin.

The next equations describe the relation between the watchdog timeout period and the external capacitor value, or the reset hold time and the external capacitor value.

$t_{WD(s)} = 3.1 \times 10^6 \times C(F)$

tWR(s)=tWD/9

The watchdog timer (WDT) timeout period is determined with the discharge time of the external capacitor.

During the watchdog timeout period, if the clock pulse from the system is detected, WDT is cleared and the capacitor is charged. When the charge of the capacitor completes, another watchdog timeout period starts again. During the watchdog timeout period, if the clock pulse from the system is not detected, during the next reset hold time RESETB pin outputs "L".

After starting the watchdog timeout period, (just after from the discharge of the external capacitor) even if the clock pulse is input during the time period "TWDI", the clock pulse is ignored. TWDI[s]=TWD/10

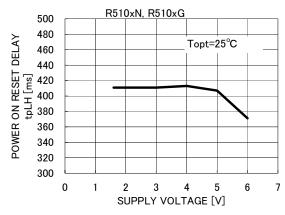

Released Delay Time (Power-on Reset delay time)

The released delay time can be set with an external capacitor connected to the CT pin. The next equation describes the relation between the capacitance value and the released delay time (tpLH).  $tpLH(s)=3.7\times10^6\times C(F)$

The capacitor connected to CT pin determines TWD, TWR, and tpLH.

#### Minimum Operating Voltage (VINL)

We specified the minimum operating voltage as the minimum input voltage in which the condition of RESETB pin being 0.1V or lower than 0.1V. (Herein, pull-up resistance is set as  $100k\Omega$  in the case of the Nch open-drain output type.

#### Inhibit (INH) Function

If INH pin is set at "L", the watchdog timer stops monitoring the clock, and the RESETB output will be dominant by the voltage detector's operation. Therefore, if the supply voltage is set at more than the detector threshold level, RESETB outputs "H" regardless the clock pulse. INH pin is pulled up with a resistor (TYP.110k $\Omega$ ) internally.

#### **RESETB** Output

RESETB pin's output type is selectable either the Nch open-drain output or CMOS output. If the Nch open-drain type output is selected, the RESETB pin is pulled up with an external resistor to an appropriate voltage source.

#### Clock Pulse Input

Built-in watchdog timer is cleared with the SCK clock pulse within the watchdog timeout period.

#### **APPLICATION NOTES**

If a resistor is connected to the VDD pin, the operation might be unstable with the supply current of IC itself.

Connection examples affected by the conduction current

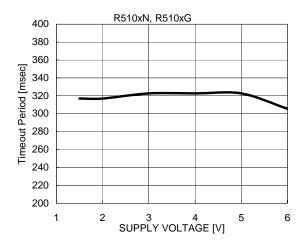

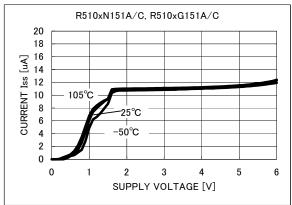

## **TYPICAL CHARACTERISTICS**

1) Supply Current vs. Input Voltage

R510xN271A/C, R510xG271A/C

4) Nch Driver Output Current vs. VDS Topt=25°C

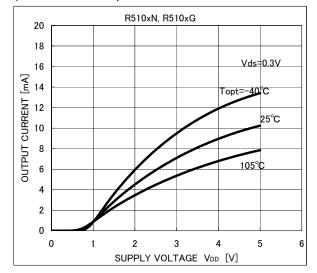

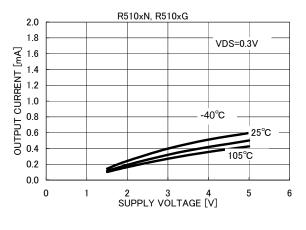

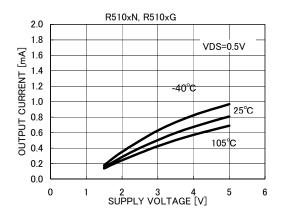

5) Nch Driver Output Current vs. VDD

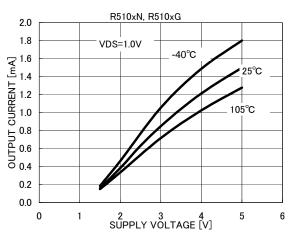

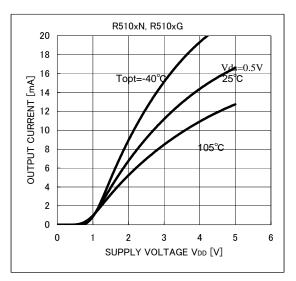

6) Pch Driver Output Current vs. VDD

#### 7) Released Delay Time vs. Input Voltage

13) WDT Timeout Period vs. Input Voltage