## DALLAS JUINKI

### DS2250(T) Soft Microcontroller Module

### www.maxim-ic.com

### DESCRIPTION

The DS2250(T) soft microcontroller module is a fully 8051-compatible 8-bit CMOS microcontroller that offers "softness" in all aspects of its application. This is accomplished through the comprehensive use of nonvolatile technology to preserve all information in the absence of system  $V_{CC}$ . The program/data memory internal space is implemented using 8, 32, or 64kbytes of nonvolatile CMOS SRAM. Furthermore, internal data registers and key configuration registers are also nonvolatile. An optional real-time clock gives permanently powered timekeeping. The clock keeps time to a hundredth of a second using an on-board crystal. nonvolatile memory and resources are All maintained for over 10 years at room temperature in the absence of power.

### **PIN CONFIGURATION**

### **ORDERING INFORMATION**

### FEATURES

- 8-Bit 8051-Compatible Microcontroller Adapts to Task-At-Hand

- 8, 32, or 64kbytes of Nonvolatile RAM for Program and/or Data Memory Storage

Initial Downloading of Software in End System via On-Chip Serial Port

- Capable of Modifying its Own Program and/or Data Memory in End Use

- High-Reliability Operation Maintains All Nonvolatile Resources Up to 10 Years in the Absence of V<sub>CC</sub> at Room Temperature Power-Fail Reset

Early Warning Power-Fail Interrupt Watchdog Timer

- Software Security Feature

Executes Encrypted Software to Prevent

Unauthorized Disclosure

- On-Chip, Full-Duplex Serial I/O Ports

- Two On-Chip Timer/Event Counters

- 32 Parallel I/O Lines

- Compatible with Industry Standard 8051 Instruction Set

- Permanently Powered Real-Time Clock

Operating information is contained in the Secure Microcontroller User's Guide. This data sheet provides ordering information, pinout, and electrical specifications.

| PART                  | RAM SIZE (kB) | MAX CRYSTAL SPEED (MHz) | TIMEKEEPING? |

|-----------------------|---------------|-------------------------|--------------|

| <b>DS2250</b> -32-16  | 32            | 16                      | No           |

| DS2250-32-16+         | 32            | 16                      | No           |

| DS2250-64-16          | 64            | 16                      | No           |

| DS2250-64-16#         | 64            | 16                      | No           |

| <b>DS2250T</b> -32-16 | 32            | 16                      | Yes          |

| DS2250T-32-16+        | 32            | 16                      | Yes          |

| DS2250T-64-16         | 64            | 16                      | Yes          |

| DS2250T-64-16+        | 64            | 16                      | Yes          |

|                       |               |                         |              |

+ Denotes lead-free/RoHS-compliant package

# Denotes RoHS-compliant device that may contain lead exempt under the RoHS requirements.

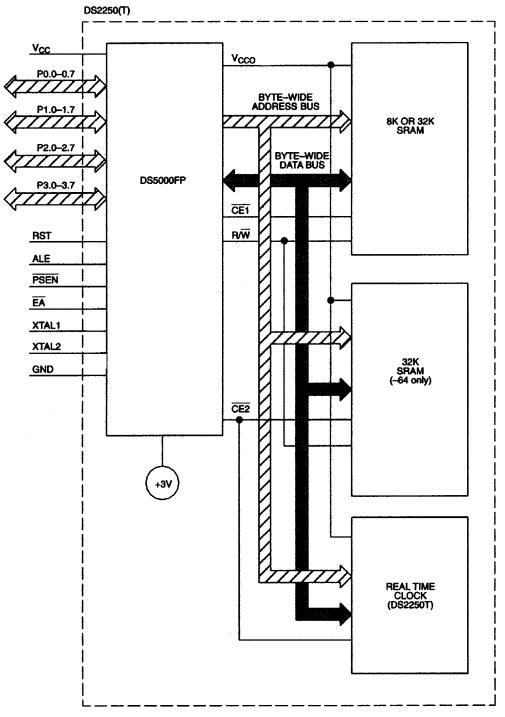

### DS2250(T) BLOCK DIAGRAM Figure 1

### **PIN DESCRIPTION**

| PIN                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7, 9,<br>11, 13, 15      | P1.0 - P1.7. General purpose I/O Port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17                                | <b>RST</b> - Active high reset input. A logic 1 applied to this pin will activate a reset state.<br>This pin is pulled down internally so this pin can be left unconnected if not used. An RC power-on reset circuit is not needed and is not recommended.                                                                                                                                                                                                                                  |

| 19                                | <b>P3.0 RXD.</b> General purpose I/O port pin 3.0. Also serves as the receive signal for the on board UART. This pin should not be connected directly to a PC COM port.                                                                                                                                                                                                                                                                                                                     |

| 21                                | <b>P3.1 TXD.</b> General purpose I/O port pin 3.1. Also serves as the transmit signal for the on board UART. This pin should not be connected directly to a PC COM port.                                                                                                                                                                                                                                                                                                                    |

| 23                                | <b>P3.2 INTO</b> . General purpose I/O port pin 3.2. Also serves as the active low External Interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                    |

| 25                                | <b>P3.3 INT1.</b> General purpose I/O port pin 3.3. Also serves as the active low External Interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                     |

| 27                                | <b>P3.4 T0.</b> General purpose I/O port pin 3.4. Also serves as the Timer 0 input.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29                                | <b>P3.5 T1.</b> General purpose I/O port pin 3.5. Also serves as the Timer 1 input.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31                                | <b>P3.6</b> $\overline{\mathbf{WR}}$ . General purpose I/O port pin. Also serves as the write strobe for Expanded bus operation.                                                                                                                                                                                                                                                                                                                                                            |

| 33                                | <b>P3.7 RD</b> . General purpose I/O port pin. Also serves as the read strobe for Expanded bus operation.                                                                                                                                                                                                                                                                                                                                                                                   |

| 35, 37                            | <b>XTAL2, XTAL1.</b> Used to connect an external crystal to the internal oscillator. XTAL1 is the input to an inverting amplifier and XTAL2 is the output.                                                                                                                                                                                                                                                                                                                                  |

| 39                                | GND - Logic ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 26, 28, 30, 32,<br>34, 36, 38, 40 | <b>P2.7-P2.0.</b> General purpose I/O Port 2. Also serves as the MSB of the Expanded Address bus.                                                                                                                                                                                                                                                                                                                                                                                           |

| 24                                | <b>PSEN</b> - Program Store Enable. This active low signal is used to enable an externalprogram memory when using the Expanded bus. It is normally an output and shouldbe unconnected if not used. PSEN also is used to invoke the Bootstrap Loader. At thistime, PSEN will be pulled down externally. This should only be done once theDS2250(T) is already in a reset state. The device that pulls down should be open-drainsince it must not interfere with PSEN under normal operation. |

| 22                                | <b>ALE</b> - Address Latch Enable. Used to de-multiplex the multiplexed Expanded Address/Data bus on Port 0. This pin is normally connected to the clock input on a '373 type transparent latch. When using a parallel programmer, this pin also assumes the PROG function for programming pulses.                                                                                                                                                                                          |

| 20                                | $\overline{\text{EA}}$ - External Access. This pin forces the DS2250(T) to behave like an 8031. No internal memory (or clock) will be available when this pin is at a logic low. Since this pin is pulled down internally, it should be connected to +5V to use NV RAM. In a parallel programmer, this pin also serves as V <sub>PP</sub> for super voltage pulses.                                                                                                                         |

| 4, 6, 8, 10, 12,<br>14, 16, 18    | <b>P0.0-P0.7.</b> General purpose I/O Port 0. This port is open-drain and can not drive a logic 1. It requires external pullups. Port 0 is also the multiplexed Expanded Address/Data bus. When used in this mode, it does not require pullups.                                                                                                                                                                                                                                             |

| 2                                 | $V_{CC}$ + - 5 volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### INSTRUCTION SET

The DS2250(T) executes an instruction set which is object code-compatible with the industry standard 8051 microcontroller. As a result, software development packages which have been written for the 8051 are compatible with the DS2250(T), including cross-assemblers, high-level language compilers, and debugging tools. Note that the DS2250(T) is functionally identical to the DS5000(T) except for package and the 64k memory option.

A complete description for the DS2250(T) instruction set is available in the Secure Microcontroller User's Guide.

### MEMORY ORGANIZATION

Figure 2 illustrates the address spaces which are accessed by the DS2250(T). As illustrated in the figure, separate address spaces exist for program and data memory. Since the basic addressing capability of the machine is 16 bits, a maximum of 64 kbytes of program memory and 64 kbytes of data memory can be accessed by the DS2250(T) CPU. The 8- or 32-kbyte RAM area inside of the DS2250(T) can be used to contain both program and data memory. A second 32k RAM is available for data only.

The Real Time Clock (RTC) in the DS2250(T) is reached in the memory map by setting a SFR bit. The MCON.2 bit (ECE2) is used to select an alternate data memory map. While ECE2=1, all MOVXs will be routed to this alternate memory map. The real time clock is a serial device that resides in this area. A full description of the RTC access and example software is given in the Secure Microcontroller User's Guide.

# PROGRAM MEMORY ECE-0 ECE-1 64K 8000h <

### DS2250(T) MEMORY MAP Figure 2

### PROGRAM LOADING

The Program Load Modes allow initialization of the NV RAM Program/Data Memory. This initialization may be performed in one of two ways:

- 1. Serial Program Loading which is capable of performing Bootstrap Loading of the DS2250(T). This feature allows the loading of the application program to be delayed until the DS2250(T) is installed in the end system.

- 2. Parallel Program Load cycles which perform the initial loading from parallel address/data information presented on the I/O port pins. This mode is timing set-compatible with the 87C51H microcontroller programming mode.

The DS2250(T) is placed in its Program Load configuration by simultaneously applying a logic 1 to the RST pin and forcing the PSEN line to a logic 0 level. Immediately following this action, the DS2250(T) will look for a parallel Program Load pulse, or a serial ASCII carriage return (0DH) character received at 9600, 2400, 1200, or 300 bps over the serial port.

The hardware configurations used to select these modes of operation are illustrated in Figure 3.

### GND GND Vcc Vcc DS2250 DS2250 ROGRAM P1.7-P1.0 P0.7-P1.7--P1.0 P0.7 DATA IN/VERIEY AO TA OUT P3.7-P3.2 P2.3-P2.0 P3.7 P3 P2.5-PROGRAM A15-A12 DORESS EA/V<sub>PP</sub> Ô P2.6 TXD DRIVE/ ALE/PROG RS232C RCV 0 P2.7 RXD PROGRAM P2.7 P2.6 \$ R<2K P2.5 R<2K 11.059 MHz RST RST XTAL1 XTAL1 PSEN PSEN XTAL2 XTAL2 SERIAL LOADING PARALLEL I OADING

### **PROGRAM LOADING CONFIGURATIONS** Figure 3

### SERIAL BOOTSTRAP LOADER

The Serial Program Load Mode is the easiest, fastest, most reliable, and most complete method of initially loading application software into the DS2250(T) nonvolatile RAM. Communication can be performed over a standard asynchronous serial communications port. A typical application would use a simple RS232C serial interface to program the DS2250(T) as a final production procedure. The hardware configuration which is required for the Serial Program Load Mode is illustrated in Figure 3. Port pins 2.7 and 2.6 must be either open or pulled high to avoid placing the device in a parallel load cycle. Although an 11.0592 MHz crystal is shown in Figure 3, a variety of crystal frequencies and loader baud rates are supported, shown in Table 2. The serial loader is designed to operate across a 3-wire interface from a standard UART. The receive, transmit, and ground wires are all that are necessary to establish communication with the DS2250(T).

The Serial Bootstrap Loader implements an easy-to-use command line interface which allows an application program in an Intel hex representation to be loaded into and read back from the device. Intel hex is the typical format which existing 8051 cross-assemblers output. The serial loader responds to single character commands which are summarized below:

| <u>COMMAND</u> | <b>FUNCTION</b>                             |

|----------------|---------------------------------------------|

| С              | Return CRC-16 checksum of embedded RAM      |

| D              | Dump Intel hex File                         |

| F              | Fill embedded RAM block with constant       |

| Κ              | Load 40-bit encryption key                  |

| L              | Load Intel hex file                         |

| R              | Read MCON register                          |

| Т              | Trace (Echo) incoming Intel hex data        |

| U              | Clear Security Lock                         |

| V              | Verify Embedded RAM with incoming Intel hex |

| W              | Write MCON register                         |

| Ζ              | Set security lock                           |

| Р              | Put a value to a port                       |

| G              | Get a value from a port                     |

Table 1 summarizes the selection of the available Parallel Program Load cycles. The timing associated with these cycles is illustrated in the electrical specs.

### PARALLEL PROGRAM LOAD CYCLES Table 1

| MODE                       | RST | PSEN | PROG | EA              | P2.7 | P2.6 | P2.5 |

|----------------------------|-----|------|------|-----------------|------|------|------|

| Program                    | 1   | 0    | 0    | $V_{PP}$        | 1    | 0    | Х    |

| Security Set               | 1   | 0    | 0    | V <sub>PP</sub> | 1    | 1    | Х    |

| Verify                     | 1   | X    | Х    | 1               | 0    | 0    | Х    |

| Prog Expanded              | 1   | 0    | 0    | $V_{PP}$        | 0    | 1    | 0    |

| Verify Expanded            | 1   | 0    | 1    | 1               | 0    | 1    | 0    |

| Prog MCON or Key registers | 1   | 0    | 0    | V <sub>PP</sub> | 0    | 1    | 1    |

| Verify MCON registers      | 1   | 0    | 1    | 1               | 0    | 1    | 1    |

The Parallel Program cycle is used to load a byte of data into a register or memory location within the DS2250(T). The Verify cycle is used to read this byte back for comparison with the originally loaded value to verify proper loading. The Security Set cycle may be used to enable and the software security feature. One may also enter bytes for the MCON register or for the five encryption registers using the Program MCON cycle. When using this cycle, the absolute register address must be presented at Ports 1 and 2 as in the normal program cycle (Port 2 should be 00H). The MCON contents can likewise be verified using the Verify MCON cycle.

When the DS2250(T) first detects a Parallel Program Strobe pulse or a Security Set Strobe pulse while in the Program Load Mode following a power-on reset, the internal hardware of the device is initialized so that an existing 4-kbyte program can be programmed into a DS2250(T) with little or no modification. This initialization automatically sets the range address for 8 kbytes and maps the lowest 4-kbyte bank of embedded RAM as program memory. The next 4 kbytes of embedded RAM are mapped as data memory.

In order to program more than 4 kbytes of program code, the Program/Verify Expanded cycles can be used. Up to 32 kbytes of program code can be entered and verified. Note that the expanded 32 kbyte Program/Verify cycles take much longer than the normal 4 kbyte Program/Verify cycles.

A typical parallel loading session would follow this procedure. First, set the contents of the MCON register with the correct range and partition only if using expanded programming cycles. Next, the encryption registers can be loaded to enable encryption of the program/data memory (not required). Then, program the DS2250(T) using either normal or expanded program cycles and check the memory contents using Verify cycles. The last operation would be to turn on the security lock feature by either a Security Set cycle or by explicitly writing to the MCON register and setting MCON.0 to a 1.

| CRYSTAL FREQ | BAUD RATE |      |      |      |       |       |  |

|--------------|-----------|------|------|------|-------|-------|--|

| (MHz)        | 300       | 1200 | 2400 | 9600 | 19200 | 57600 |  |

| 14.7456      |           | Y    | Y    | Y    | Y     |       |  |

| 11.0592      | Y         | Y    | Y    | Y    | Y     | Y     |  |

| 9.21600      | Y         | Y    | Y    | Y    |       |       |  |

| 7.37280      | Y         | Y    | Y    | Y    |       |       |  |

| 5.52960      | Y         | Y    | Y    | Y    |       |       |  |

| 1.84320      | Y         | Y    | Y    | Y    |       |       |  |

### SERIAL LOADER BAUD RATES FOR DIFFERENT CRYSTAL FREQUENCIES Table 2

### ADDITIONAL INFORMATION

A complete description for all operational aspects of the DS2250(T) is provided in the Secure Microcontroller User's Guide.

### **DEVELOPMENT SUPPORT**

The DS89C450-K00 evaluation kit can be used to develop and test user code. It allows the user to download Intel hex formatted code to the DS2250(T) from a PC. The user must purchase the DS2250 and DS9072-40V mechanical adapter separately. Refer to the Secure Microcontroller User's Guide for further details.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground |                                      |

|---------------------------------------------|--------------------------------------|

| Operating Temperature Range                 | $\dots 0^{\circ}C$ to $+70^{\circ}C$ |

| Storage Temperature                         | 40°C to $+70°C$                      |

| Soldering Temperature                       | +260°C for 10 seconds                |

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### **DC CHARACTERISTICS**

### $(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                                                                      | SYMBOL             | MIN  | ТҮР  | MAX                  | UNITS | NOTES |

|--------------------------------------------------------------------------------|--------------------|------|------|----------------------|-------|-------|

| Input Low Voltage                                                              | V <sub>IL</sub>    | -0.3 |      | +0.8                 | V     | 1     |

| Input High Voltage                                                             | $V_{\rm IH1}$      | 2.0  |      | V <sub>CC</sub> +0.3 | V     | 1     |

| Input High Voltage RST, XTAL1                                                  | V <sub>IH2</sub>   | 3.5  |      | V <sub>CC</sub> +0.3 | V     | 1     |

| Output Low Voltage<br>@ I <sub>OL</sub> =1.6 mA (Ports 1, 2, 3)                | V <sub>OL1</sub>   |      | 0.15 | 0.45                 | V     |       |

| Output Low Voltage<br>@ I <sub>OL</sub> =3.2 mA (Ports 0, ALE, PSEN)           | V <sub>OL2</sub>   |      | 0.15 | 0.45                 | V     | 1     |

| Output High Voltage<br>@ I <sub>OH</sub> =-80 μA (Ports 1, 2, 3)               | V <sub>OH1</sub>   | 2.4  | 4.8  |                      | V     | 1     |

| Output High Voltage<br>@ $I_{OH}$ =-400 µA (Ports 0, ALE, PSEN)                | V <sub>OH2</sub>   | 2.4  | 4.8  |                      | V     | 1     |

| Input Low Current $V_{IN} = 0.45V$<br>(Ports 1, 2, 3)                          | I <sub>IL</sub>    |      |      | -50                  | μΑ    |       |

| Transition Current; 1 to 0<br>$V_{IN}$ =2.0V (Ports 1, 2, 3)                   | I <sub>TL</sub>    |      |      | -500                 | μΑ    |       |

| Input Leakage Current $0.45 < V_{IN} < V_{CC}$ (Port 0)                        | IL                 |      |      | ±10                  | μΑ    |       |

| RST, EA Pulldown Resistor                                                      | R <sub>RE</sub>    | 40   |      | 125                  | kΩ    |       |

| Stop Mode Current                                                              | I <sub>SM</sub>    |      |      | 80                   | μΑ    | 4     |

| Power Fail Warning Voltage                                                     | V <sub>PFW</sub>   | 4.15 | 4.6  | 4.75                 | V     | 1     |

| Minimum Operating Voltage                                                      | V <sub>CCmin</sub> | 4.05 | 4.5  | 4.65                 | V     | 1     |

| Programming Supply Voltage<br>(Parallel Program Mode)                          | $V_{PP}$           | 12.5 |      | 13                   | V     | 1     |

| Program Supply Current                                                         | I <sub>PP</sub>    |      | 15   | 20                   | mA    |       |

| Operating Current DS2250-8k<br>DS2250-32k @ 12 MHz<br>DS2250(T)-64-16 @ 16 MHz | I <sub>CC</sub>    |      |      | 43<br>48<br>54       | mA    | 2     |

| Idle Mode Current @ 8 MHz                                                      | I <sub>CC</sub>    |      |      | 6.2                  | mA    | 3     |

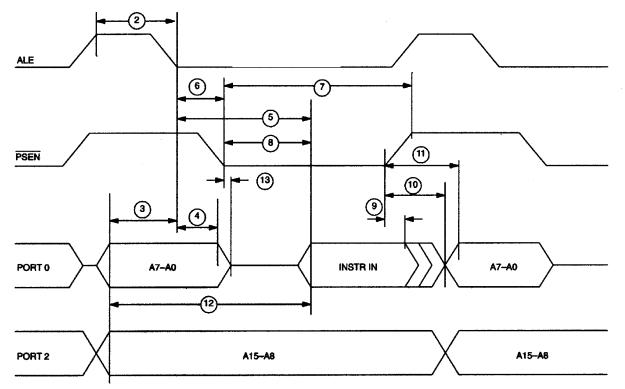

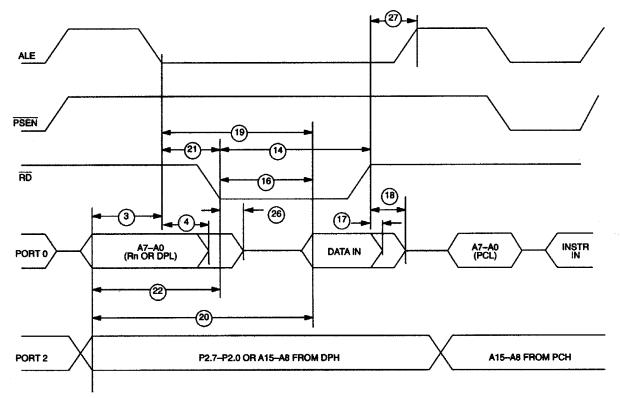

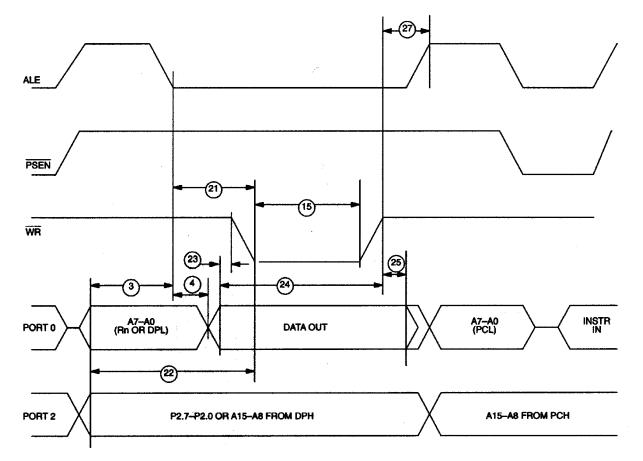

# AC CHARACTERISTICS—EXPANDED BUS MODE TIMING SPECIFICATIONS $(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                                                         | SYMBOL                | MIN                                             | MAX                                              | UNITS    |

|----|-------------------------------------------------------------------|-----------------------|-------------------------------------------------|--------------------------------------------------|----------|

| 1  | Oscillator Frequency                                              | 1/t <sub>CLK</sub>    | 1.0                                             | 16 (-16)                                         | MHz      |

| 2  | ALE Pulse Width                                                   | t <sub>ALPW</sub>     | 2t <sub>CLK</sub> -40                           |                                                  | ns       |

| 3  | Address Valid to ALE Low                                          | t <sub>AVALL</sub>    | t <sub>CLK</sub> -40                            |                                                  | ns       |

| 4  | Address Hold After ALE Low                                        | t <sub>AVAAV</sub>    | t <sub>CLK</sub> -35                            |                                                  | ns       |

| 5  | ALE Low to Valid Instr. In<br>@ 12 MHz<br>@ 16 MHz                | t <sub>ALLVI</sub>    |                                                 | 4t <sub>CLK</sub> -150<br>4t <sub>CLK</sub> -90  | ns       |

| 6  | ALE Low to PSEN Low                                               | $t_{\mathrm{ALLPSL}}$ | t <sub>CLK</sub> -25                            |                                                  | ns       |

| 7  | PSEN Pulse Width                                                  | $t_{\rm PSPW}$        | 3t <sub>CLK</sub> -35                           |                                                  | ns       |

| 8  | PSENLow to Valid Instr. In@ 12 MHz@ 16 MHz                        | t <sub>PSLVI</sub>    |                                                 | 3t <sub>CLK</sub> -150<br>3t <sub>CLK</sub> -90  | ns<br>ns |

| 9  | Input Instr. Hold after PSEN Going High                           | t <sub>PSIV</sub>     | 0                                               |                                                  | ns       |

| 10 | Input Instr. Float after PSEN Going High                          | t <sub>PSIX</sub>     |                                                 | t <sub>CLK</sub> -20                             | ns       |

| 11 | Address Hold after PSEN Going High                                | t <sub>PSAV</sub>     | t <sub>CLK</sub> -8                             |                                                  | ns       |

| 12 | Address Valid to Valid Instr. In @ 12 MHz<br>@ 16 MHz             | t <sub>AVVI</sub>     |                                                 | 5t <sub>CLK</sub> -150<br>5t <sub>CLK</sub> -90  | ns<br>ns |

| 13 | PSEN Low to Address Float                                         | t <sub>PSLAZ</sub>    | 0                                               |                                                  | ns       |

| 14 | RD Pulse Width                                                    | t <sub>RDPW</sub>     | 6t <sub>CLK</sub> -100                          |                                                  | ns       |

| 15 | WR Pulse Width                                                    | t <sub>WRPW</sub>     | 6t <sub>CLK</sub> -100                          |                                                  | ns       |

| 16 | RDLow to Valid Data In@ 12 MHz@ 16 MHz                            | t <sub>RDLDV</sub>    |                                                 | 5t <sub>CLK</sub> -165<br>5t <sub>CLK</sub> -105 | ns<br>ns |

| 17 | Data Hold after RD High                                           | t <sub>RDHDV</sub>    | 0                                               |                                                  | ns       |

| 18 | Data Float after RD High                                          | t <sub>RDHDZ</sub>    |                                                 | 2t <sub>CLK</sub> -70                            | ns       |

| 19 | ALE Low to Valid Data In @ 12 MHz<br>@ 16 MHz                     | t <sub>ALLVD</sub>    |                                                 | 8 <sub>CLK</sub> -150<br>8t <sub>CLK</sub> -90   | ns<br>ns |

| 20 | Valid Addr. to Valid Data In @ 12 MHz<br>@ 16 MHz                 | t <sub>AVDV</sub>     |                                                 | 9t <sub>CLK</sub> -165<br>9t <sub>CLK</sub> -105 | ns<br>ns |

| 21 | ALE Low to $\overline{RD}$ or $\overline{WR}$ Low                 | t <sub>ALLRDL</sub>   | 3t <sub>CLK</sub> -50                           | $3t_{CLK} + 50$                                  | ns       |

| 22 | Address Valid to $\overline{RD}$ or $\overline{WR}$ Low           | t <sub>AVRDL</sub>    | 4t <sub>CLK</sub> -130                          |                                                  | ns       |

| 23 | Data Valid to WR Going Low                                        | t <sub>DVWRL</sub>    | t <sub>CLK</sub> -60                            |                                                  | ns       |

| 24 | Data Valid to WR High@ 12 MHz@ 16 MHz                             | t <sub>dvwrh</sub>    | 7t <sub>CLK</sub> -150<br>7t <sub>CLK</sub> -90 |                                                  | ns<br>ns |

| 25 | Data Valid after WR High                                          | t <sub>WRHDV</sub>    | t <sub>CLK</sub> -50                            |                                                  | ns       |

| 26 | $\overline{RD}$ Low to Address Float                              | t <sub>RDLAZ</sub>    |                                                 | 0                                                | ns       |

| 27 | $\overline{\text{RD}}$ or $\overline{\text{WR}}$ High to ALE High | t <sub>RDHALH</sub>   | t <sub>CLK</sub> -40                            | t <sub>CLK</sub> +50                             | ns       |

### **EXPANDED PROGRAM MEMORY READ CYCLE**

### **EXPANDED DATA MEMORY READ CYCLE**

### **EXPANDED DATA MEMORY WRITE CYCLE**

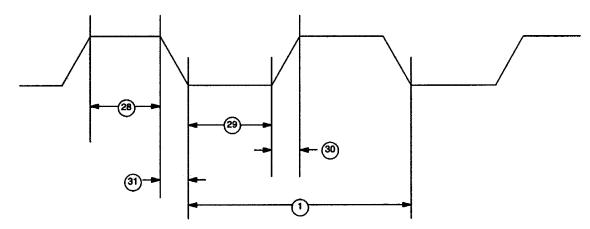

### **EXTERNAL CLOCK TIMING**

### AC CHARACTERISTICS—EXTERNAL CLOCK DRIVE

$(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| 1.00 |                          | /        | r                   |     | 1   |       |

|------|--------------------------|----------|---------------------|-----|-----|-------|

| #    | PARAMETER                |          | SYMBOL              | MIN | MAX | UNITS |

| 28   | External Clock High Time | @ 12 MHz | t <sub>CLKHPW</sub> | 20  |     | ns    |

|      |                          | @ 16 MHz |                     | 15  |     | ns    |

| 29   | External Clock Low Time  | @ 12 MHz | t <sub>CLKLPW</sub> | 20  |     | ns    |

|      |                          | @ 16 MHz |                     | 15  |     | ns    |

| 30   | External Clock Rise Time | @ 12 MHz | t <sub>CLKR</sub>   |     | 20  | ns    |

|      |                          | @ 16 MHz |                     |     | 15  | ns    |

| 31   | External Clock Fall Time | @ 12 MHz | t <sub>CLKF</sub>   |     | 20  | ns    |

|      |                          | @ 16 MHz |                     |     | 15  | ns    |

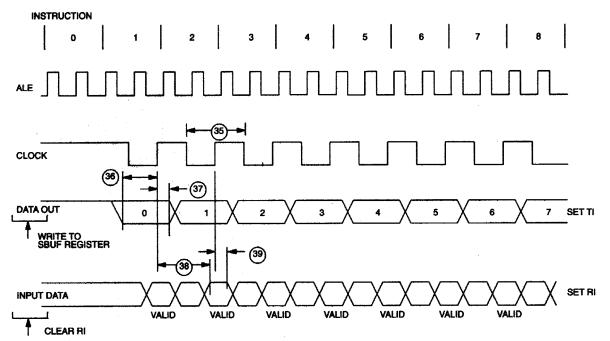

### AC CHARACTERISTICS—SERIAL PORT TIMING: MODE 0

| (  | $V_{CC} =$ | 5V  | +5%.        | T <sub>^</sub> = | 0°C to | +70°C.) |

|----|------------|-----|-------------|------------------|--------|---------|

| ١. | ¥ (,(,     | Ο ν | $\pm 0.00,$ | IA               |        |         |

| #  | PARAMETER                                | SYMBOL             | MIN                     | MAX                     | UNITS |

|----|------------------------------------------|--------------------|-------------------------|-------------------------|-------|

| 35 | Serial Port Cycle Time                   | t <sub>SPCLK</sub> | $12t_{CLK}$             |                         | μs    |

| 36 | Output Data Setup to Rising Clock Edge   | t <sub>DOCH</sub>  | 10t <sub>CLK</sub> -133 |                         | ns    |

| 37 | Output Data Hold after Rising Clock Edge | t <sub>CHDO</sub>  | 2t <sub>CLK</sub> -117  |                         | ns    |

| 38 | Clock Rising Edge to Input Data Valid    | t <sub>CHDV</sub>  |                         | 10t <sub>CLK</sub> -133 | ns    |

| 39 | Input Data Hold after Rising Clock Edge  | t <sub>CHDIV</sub> | 0                       |                         | ns    |

### SERIAL PORT TIMING: MODE 0

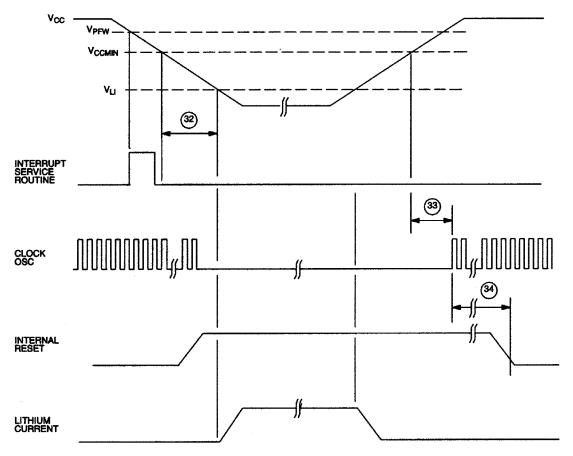

### AC CHARACTERISTICS—POWER CYCLING TIMING

| $(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } +70)$ | 70°C.) |  |

|-----------------------------------------------------------|--------|--|

|-----------------------------------------------------------|--------|--|

| #  | PARAMETER                            | SYMBOL           | MIN | MAX      | UNITS            |

|----|--------------------------------------|------------------|-----|----------|------------------|

| 32 | Slew Rate from $V_{CCmin}$ to $3.3V$ | t <sub>F</sub>   | 40  |          | μs               |

| 33 | Crystal Start-up Time                | t <sub>CSU</sub> |     | (Note 5) |                  |

| 34 | Power-On Reset Delay                 | t <sub>POR</sub> |     | 21504    | t <sub>CLK</sub> |

### POWER CYCLE TIMING

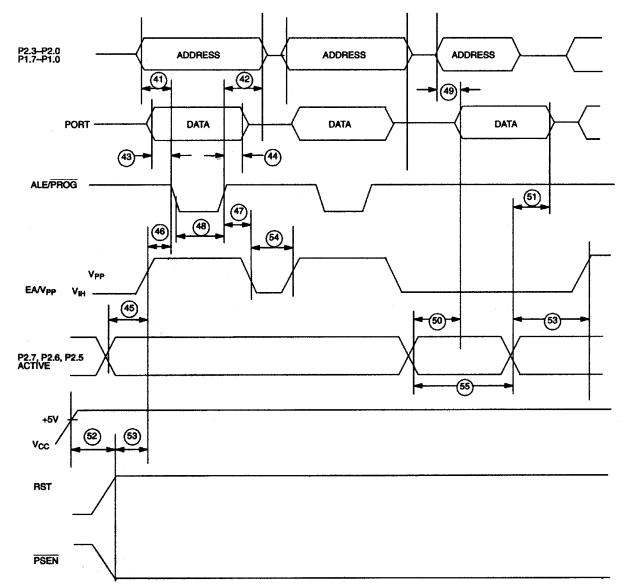

### AC CHARACTERISTICS—PARALLEL PROGRAM LOAD TIMING

$(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| #  | PARAMETER                                                                                                                          | SYMBOL              | MIN         | MAX         | UNITS            |

|----|------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|-------------|------------------|

| 40 | Oscillator Frequency                                                                                                               | $1/t_{CLK}$         | 1.0         | 12.0        | MHz              |

| 41 | Address Setup to PROG Low                                                                                                          | t <sub>AVPRL</sub>  | 0           |             |                  |

| 42 | Address Hold after PROG High                                                                                                       | t <sub>PRHAV</sub>  | 0           |             |                  |

| 43 | Data Setup to PROG Low                                                                                                             | t <sub>DVPRL</sub>  | 0           |             |                  |

| 44 | Data Hold after PROG High                                                                                                          | t <sub>PRHDV</sub>  | 0           |             |                  |

| 45 | P2.7, 2.6, 2.5 Setup to V <sub>PP</sub>                                                                                            | t <sub>P27HVP</sub> | 0           |             |                  |

| 46 | $V_{PP}$ Setup to $\overline{PROG}$ Low                                                                                            | t <sub>VPHPRL</sub> | 0           |             |                  |

| 47 | $V_{PP}$ Hold after $\overline{PROG}$ Low                                                                                          | t <sub>PRHVPL</sub> | 0           |             |                  |

| 48 | PROG Width Low                                                                                                                     | t <sub>PRW</sub>    | 2400        |             | t <sub>CLK</sub> |

| 49 | Data Output from Address Valid                                                                                                     | t <sub>AVDV</sub>   |             | 48<br>1800* | t <sub>CLK</sub> |

| 50 | Data Output from P2.7 Low                                                                                                          | t <sub>DVP27L</sub> |             | 48<br>1800* | t <sub>CLK</sub> |

| 51 | Data Float after P2.7 High                                                                                                         | t <sub>P27HDZ</sub> | 0           | 48<br>1800* | t <sub>CLK</sub> |

| 52 | Delay to Reset/ PSEN Active after Power On                                                                                         | t <sub>PORPV</sub>  | 21504       |             | t <sub>CLK</sub> |

| 53 | $\begin{array}{l} \hline Reset/\overline{\text{PSEN}} & \text{Active (or Verify Inactive) to} \\ V_{PP} & \text{High} \end{array}$ | t <sub>RAVPH</sub>  | 1200        |             | t <sub>CLK</sub> |

| 54 | V <sub>PP</sub> Inactive (Between Program Cycles)                                                                                  | t <sub>VPPPC</sub>  | 1200        |             | t <sub>CLK</sub> |

| 55 | Verify Active Time                                                                                                                 | t <sub>VFT</sub>    | 48<br>2400* |             | t <sub>CLK</sub> |

\*Second set of numbers refers to expanded memory programming up to 32kbytes.

### PARALLEL PROGRAM LOAD TIMING

### CAPACITANCE

### (Test Frequency = 1MHz, $T_A = +25^{\circ}C$ .)

| PARAMETER          | SYMBOL | MIN | ТҮР | MAX | UNITS | NOTES |

|--------------------|--------|-----|-----|-----|-------|-------|

| Output Capacitance | Co     |     |     | 10  | pF    |       |

| Input Capacitance  | CI     |     |     | 10  | pF    |       |

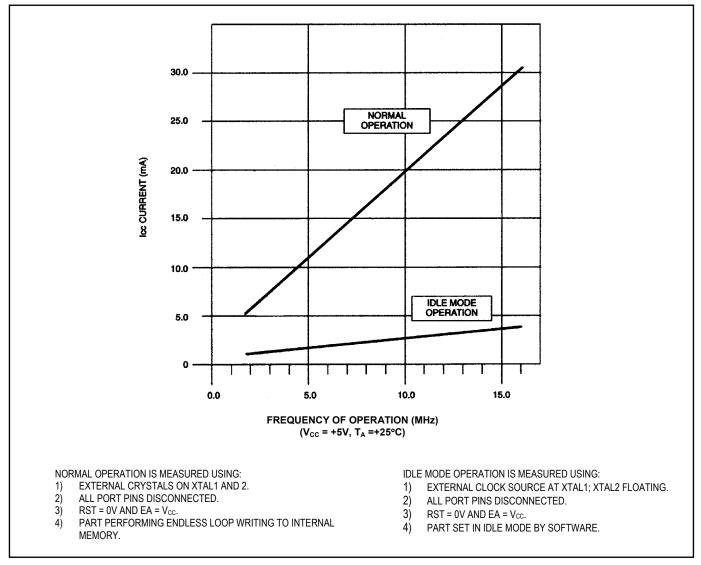

### DS2250(T) TYPICAL Icc VS. FREQUENCY

### NOTES:

- 1. All voltages are referenced to ground.

- 2. Maximum operating  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $t_{CLKR}$ ,  $t_{CLKF} = 10$  ns,  $V_{IL} = 0.5V$ ; XTAL2 disconnected;  $\overline{EA} = RST = PORT0 = V_{CC}$ .

- 3. Idle mode I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven at 8 MHz with  $t_{CLKR}$ ,  $t_{CLKF} = 10$  ns,  $V_{IL} = 0.5V$ ; XTAL2 disconnected;  $\overline{EA} = PORT0 = V_{CC}$ ,  $RST = V_{SS}$ .

- 4. Stop mode  $I_{CC}$  is measured with all output pins disconnected;  $\overline{EA} = PORT0 = V_{CC}$ ; XTAL2 not connected;  $RST = V_{SS}$ .

- 5. Crystal start-up time is the time required to get the mass of the crystal into vibrational motion from the time that power is first applied to the circuit until the first clock pulse is produced by the on-chip oscillator. The user should check with the crystal vendor for the worst-case spec on this time.

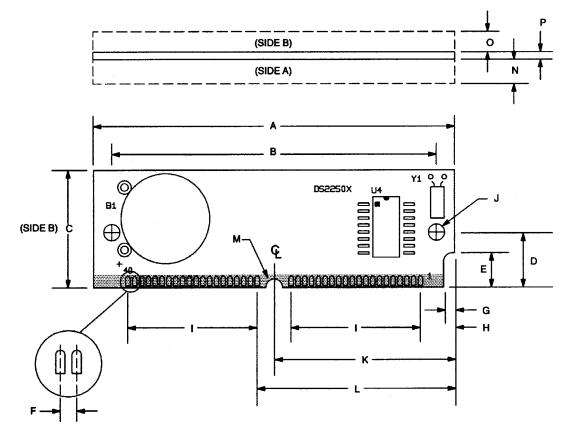

### PACKAGE DRAWING

| PKG | INCHES    |       |  |

|-----|-----------|-------|--|

| DIM | MIN       | MAX   |  |

| Α   | 2.645     | 2.655 |  |

| В   | 2.379     | 2.389 |  |

| С   | 0.845     | 0.855 |  |

| D   | 0.395     | 0.405 |  |

| E   | 0.245     | 0.255 |  |

| F   | 0.050 BSC |       |  |

| G   | 0.075     | 0.085 |  |

| Н   | 0.245     | 0.255 |  |

| I   | 0.950 BSC |       |  |

| J   | 0.120     | 0.130 |  |

| к   | 1.320     | 1.330 |  |

| L   | 1.445     | 1.455 |  |

| м   | 0.057     | 0.067 |  |

| N   | -         | 0.160 |  |

| 0   | -         | 0.195 |  |

| Р   | 0.047     | 0.054 |  |

### DATA SHEET REVISION SUMMARY

The following represent the key differences between 12/13/95 and 08/16/96 version of the DS2250(T) data sheet. Please review this summary carefully.

- 1. Correct Figure 3 to show RST active high.

- 2. Add minimum value to PCB thickness.

The following represent the key differences between 11/20/99 and 06/09/06 version of the DS2250(T) data sheet. Please review this summary carefully.

- 1. Updated reference (Features) to 10-year NV RAM data life to include room temperature caveat.

- 2. Added lead-free package information to the Ordering Information table.

- 3. Removed 8kB package versions from Ordering Information table.

- 4. Removed references to "Secure Microcontroller Data Book" and changed them to "Secure Microcontroller User's Guide."

- 5. Removed references to DS5000TK.

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600** © 2006 Maxim Integrated Products • Printed USA

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor Corporation.