# 5-BIT PROGRAMMABLE DELAY LINE (SERIES PDU15F)

PIN DESCRIPTIONS

OUT/ Inverted Output

+5 Volts

A0-A4 Address Bits

GND Ground

**Delay Line Input**

**Output Enable**

Non-inverted Output

# FEATURES

- Digitally programmable in 32 delay steps

- Monotonic delay-versus-address variation

- Two separate outputs: inverting & non-inverting

- Precise and stable delays

- Input & outputs fully TTL interfaced & buffered

- 10 T<sup>2</sup>L fan-out capability

- Fits standard 24-pin DIP socket

- Auto-insertable

# PACKAGES

| OUT/ |            | 24 | VCC |                      |

|------|------------|----|-----|----------------------|

| OUT  | <b></b> 2  | 23 | A0  |                      |

| EN/  | □3         | 22 | A1  | PDU15F-xx            |

| GND  | □4         | 21 | A2  | DIP<br>PDU15F-xxA4   |

| N/C  | □5         | 20 | VCC | Gull-Wing            |

| IN   | ₫6         | 19 | N/C | PDU15F-xxB4          |

| N/C  | <b>d</b> 7 | 18 | N/C | J-Lead<br>PDU15F-xxM |

| GND  | 8          | 17 | N/C | Military DIP         |

| N/C  | <u> </u>   | 16 | VCC | PDU15F-xxMC4         |

| N/C  | <u> </u>   | 15 | A3  | Military Gull-Wing   |

| EN/  | 11         | 14 | A4  |                      |

| GND  | 12         | 13 | N/C |                      |

IN

OUT

EN/

VCC

### FUNCTIONAL DESCRIPTION

The PDU15F-series device is a 5-bit digitally programmable delay line. The delay,  $TD_A$ , from the input pin (IN) to the output pins (OUT, OUT/) depends on the address code (A4-A0) according to the following formula:

$$TD_A = TD_0 + T_{INC} * A$$

where A is the address code,  $T_{INC}$  is the incremental delay of the device, and  $TD_0$  is the inherent delay of the device. The incremental delay is

specified by the dash number of the device and can range from 0.5ns through 20ns, inclusively. The enable pins (EN/) are held LOW during normal operation. These pins must always be in the same state and may be tied together externally. When these signals are brought HIGH, OUT and OUT/ are forced into LOW and HIGH states, respectively. The address is not latched and must remain asserted during normal operation.

### SERIES SPECIFICATIONS

- Total programmed delay tolerance: 5% or 1ns, whichever is greater

- Inherent delay (TD<sub>0</sub>): 9ns typical (OUT) 8ns typical (OUT/)

- Setup time and propagation delay: Address to input setup (T<sub>AIS</sub>): 5ns Disable to output delay (T<sub>DISO</sub>): 6ns typ. (OUT)

- Operating temperature: 0° to 70° C

- **Temperature coefficient:** 100PPM/°C (excludes TD<sub>0</sub>)

- Supply voltage V<sub>cc</sub>: 5VDC ± 5%

- Supply current: I<sub>CCH</sub> = 74ma

- I<sub>CCL</sub> = 30ma

- Minimum pulse width: 10% of total delay

©1997 Data Delay Devices

Downloaded from Elcodis.com electronic components distributor

### DASH NUMBER SPECIFICATIONS

| Part<br>Number | Incremental Delay<br>Per Step (ns) | Total Delay<br>Change (ns) |  |  |

|----------------|------------------------------------|----------------------------|--|--|

| PDU15F5        | .5 ± .3                            | $15.5\pm1.0$               |  |  |

| PDU15F-1       | 1 ± .5                             | 31 ± 1.6                   |  |  |

| PDU15F-2       | 2 ± .5                             | $62\pm3.1$                 |  |  |

| PDU15F-3       | 3 ± 1.0                            | $93\pm4.7$                 |  |  |

| PDU15F-4       | 4 ± 1.0                            | $124 \pm 6.2$              |  |  |

| PDU15F-5       | 5 ± 1.0                            | $155\pm7.8$                |  |  |

| PDU15F-6       | 6 ± 1.0                            | $186\pm9.3$                |  |  |

| PDU15F-8       | 8 ± 1.0                            | $248 \pm 12.4$             |  |  |

| PDU15F-10      | 10 ± 1.5                           | $310 \pm 15.5$             |  |  |

| PDU15F-12      | $12 \pm 1.5$                       | $372 \pm 18.6$             |  |  |

| PDU15F-15      | 15 ± 1.5                           | $465\pm23.3$               |  |  |

| PDU15F-20      | $20\pm2.0$                         | $620\pm31.0$               |  |  |

NOTE: Any dash number between .5 and 20 not shown is also available.

# **APPLICATION NOTES**

### ADDRESS UPDATE

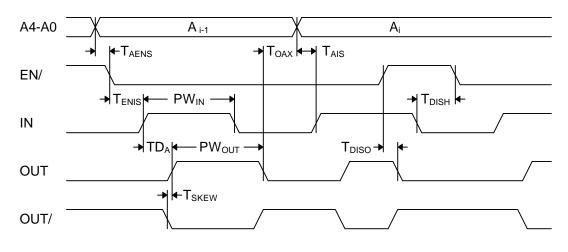

The PDU15F is a memory device. As such, special precautions must be taken when changing the delay address in order to prevent spurious output signals. The timing restrictions are shown in Figure 1.

After the last signal edge to be delayed has appeared on the OUT pin, a minimum time,  $T_{OAX}$ , is required before the address lines can change. This time is given by the following relation:

$$T_{OAX} = max \{ (A_i - A_{i-1}) * T_{INC}, 0 \}$$

where A<sub>i-1</sub> and A<sub>i</sub> are the old and new address codes, respectively. Violation of this constraint may, depending on the history of the input signal, cause spurious signals to appear on the OUT pin. The possibility of spurious signals persists until the required  $T_{OAX}$  has elapsed.

A similar situation occurs when using the EN/ signal to disable the output while IN is active. In this case, the unit must be held in the disabled state until the device is able to "clear" itself. This is achieved by holding the EN/ signal high and the IN signal low for a time given by:

$T_{DISH} = A_i * T_{INC}$

Downloaded from Elcodis.com electronic components distributor

Violation of this constraint may, depending on the history of the input signal, cause spurious signals to appear on the OUT pin. The possibility of spurious signals persists until the required  $T_{\text{DISH}}$  has elapsed.

### INPUT RESTRICTIONS

There are three types of restrictions on input pulse width and period listed in the **AC Characteristics** table. The **recommended** conditions are those for which the delay tolerance specifications and monotonicity are guaranteed. The **suggested** conditions are those for which signals will propagate through the unit without significant distortion. The **absolute** conditions are those for which the unit will produce some type of output for a given input.

When operating the unit between the recommended and absolute conditions, the delays may deviate from their values at low frequency. However, these deviations will remain constant from pulse to pulse if the input pulse width and period remain fixed. In other words, the delay of the unit exhibits frequency and pulse width dependence when operated beyond the recommended conditions. Please consult the technical staff at Data Delay Devices if your application has specific high-frequency requirements.

Please note that the increment tolerances listed represent a design goal. Although most delay increments will fall within tolerance, they are not guaranteed throughout the address range of the unit. Monotonicity is, however, guaranteed over all addresses.

Figure 1: Timing Diagram

# **DEVICE SPECIFICATIONS**

| PARAM                    | SYMBOL            | MIN               | TYP      | UNITS |                  |

|--------------------------|-------------------|-------------------|----------|-------|------------------|

| Total Programmable Delay |                   | TDT               |          | 31    | T <sub>INC</sub> |

| Inherent Delay           |                   | TD <sub>0</sub>   |          | 9.0   | ns               |

| Output Skew              |                   | T <sub>SKEW</sub> |          | 1.5   | ns               |

| Disable to Output Lo     | ow Delay          | T <sub>DISO</sub> |          | 6.0   | ns               |

| Address to Enable S      | Setup Time        | T <sub>AENS</sub> | 2.0      |       | ns               |

| Address to Input Se      | T <sub>AIS</sub>  | 5.0               |          | ns    |                  |

| Enable to Input Setu     | T <sub>ENIS</sub> | 2.5               |          | ns    |                  |

| Output to Address C      | T <sub>OAX</sub>  | See Text          |          |       |                  |

| Disable Hold Time        |                   | T <sub>DISH</sub> | See Text |       |                  |

| Input Period             | Absolute          | PERIN             | 20       |       | % of $TD_T$      |

|                          | Suggested         | PERIN             | 40       |       | % of $TD_T$      |

|                          | Recommended       | PERIN             | 200      |       | % of $TD_T$      |

|                          | Absolute          | PWIN              | 10       |       | % of $TD_T$      |

| Input Pulse Width        | Suggested         | PWIN              | 20       |       | % of $TD_T$      |

|                          | Recommended       | PWIN              | 100      |       | % of $TD_T$      |

### TABLE 1: AC CHARACTERISTICS

#### TABLE 2: ABSOLUTE MAXIMUM RATINGS

| PARAMETER           | SYMBOL            | MIN  | MAX                  | UNITS | NOTES  |

|---------------------|-------------------|------|----------------------|-------|--------|

| DC Supply Voltage   | V <sub>cc</sub>   | -0.3 | 7.0                  | V     |        |

| Input Pin Voltage   | V <sub>IN</sub>   | -0.3 | V <sub>DD</sub> +0.3 | V     |        |

| Storage Temperature | T <sub>STRG</sub> | -55  | 150                  | С     |        |

| Lead Temperature    | T <sub>LEAD</sub> |      | 300                  | С     | 10 sec |

# TABLE 3: DC ELECTRICAL CHARACTERISTICS

(0C to 70C, 4.75V to 5.25V)

| PARAMETER                    | SYMBOL           | MIN | TYP  | MAX  | UNITS | NOTES                        |

|------------------------------|------------------|-----|------|------|-------|------------------------------|

| High Level Output Voltage    | V <sub>OH</sub>  | 2.5 | 3.4  |      | V     | $V_{CC} = MIN, I_{OH} = MAX$ |

|                              |                  |     |      |      |       | $V_{IH} = MIN, V_{IL} = MAX$ |

| Low Level Output Voltage     | V <sub>OL</sub>  |     | 0.35 | 0.5  | V     | $V_{CC} = MIN, I_{OL} = MAX$ |

|                              |                  |     |      |      |       | $V_{IH} = MIN, V_{IL} = MAX$ |

| High Level Output Current    | I <sub>OH</sub>  |     |      | -1.0 | mA    |                              |

| Low Level Output Current     | I <sub>OL</sub>  |     |      | 20.0 | mA    |                              |

| High Level Input Voltage     | V <sub>IH</sub>  | 2.0 |      |      | V     |                              |

| Low Level Input Voltage      | V <sub>IL</sub>  |     |      | 0.8  | V     |                              |

| Input Clamp Voltage          | VIK              |     |      | -1.2 | V     | $V_{CC} = MIN, I_I = I_{IK}$ |

| Input Current at Maximum     | I <sub>IHH</sub> |     |      | 0.1  | mA    | $V_{CC} = MAX, V_I = 7.0V$   |

| Input Voltage                |                  |     |      |      |       |                              |

| High Level Input Current     | Iн               |     |      | 20   | μA    | $V_{CC} = MAX, V_I = 2.7V$   |

| Low Level Input Current      | I <sub>IL</sub>  |     |      | -0.6 | mA    | $V_{CC} = MAX, V_{I} = 0.5V$ |

| Short-circuit Output Current | I <sub>OS</sub>  | -60 |      | -150 | mA    | $V_{CC} = MAX$               |

| Output High Fan-out          |                  |     |      | 25   | Unit  |                              |

| Output Low Fan-out           |                  |     |      | 12.5 | Load  |                              |

Doc #97003 1/13/97

#### DATA DELAY DEVICES, INC. 3 Mt. Prospect Ave. Clifton, NJ 07013

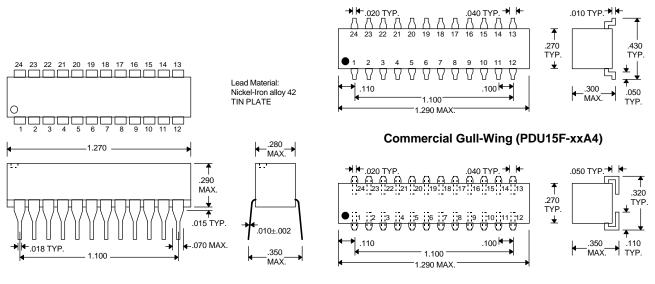

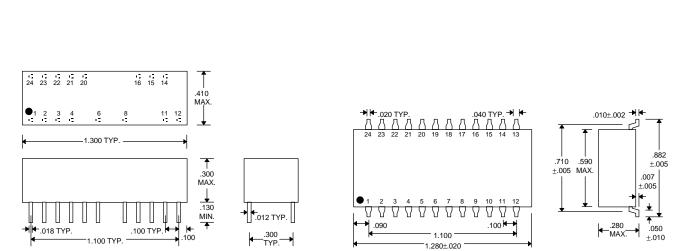

# PACKAGE DIMENSIONS

Commercial DIP (PDU15F-xx)

Military DIP (PDU15F-xxM)

Military Gull-Wing (PDU15F-xxMC4)

Commercial J-Lead (PDU15F-xxB4)

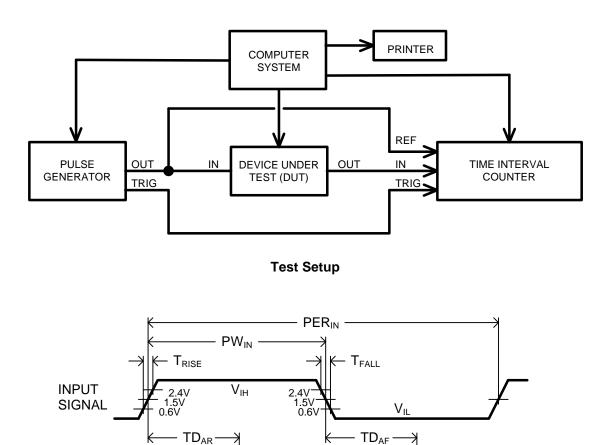

# DELAY LINE AUTOMATED TESTING

### **TEST CONDITIONS**

| INPUT:                |                                       | OUTPUT:             |                         |

|-----------------------|---------------------------------------|---------------------|-------------------------|

| Ambient Temperature:  | $\pm 25^{\circ}C \pm 3^{\circ}C$      | Load:               | 1 FAST-TTL Gate         |

| Supply Voltage (Vcc): | $5.0V \pm 0.1V$                       | C <sub>load</sub> : | 5pf ± 10%               |

| Input Pulse:          | $High = 3.0V \pm 0.1V$                | Threshold:          | 1.5V (Rising & Falling) |

|                       | $Low = 0.0V \pm 0.1V$                 |                     |                         |

| Source Impedance:     | 50Ω Max.                              |                     |                         |

| Rise/Fall Time:       | 3.0 ns Max. (measured                 |                     |                         |

|                       | between 0.6V and 2.4V)                |                     |                         |

| Pulse Width:          | PW <sub>IN</sub> = 1.5 x Total Delay  |                     |                         |

| Period:               | PER <sub>IN</sub> = 4.5 x Total Delay |                     |                         |

NOTE: The above conditions are for test only and do not in any way restrict the operation of the device.

Timing Diagram For Testing

OUTPUT

SIGNAL

$V_{OL}$