# **Optical disc ICs**

# 4-channel PWM driver for CD and MD use BH6512FS / BH6513FS

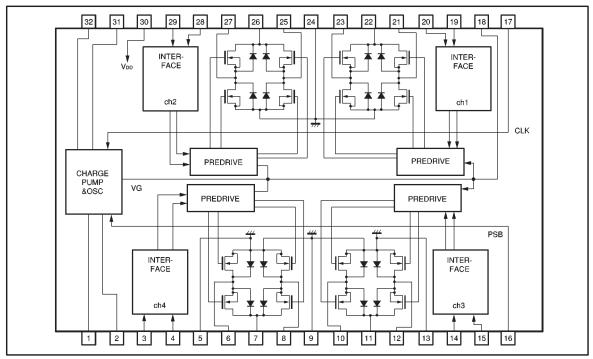

The BH6512FS/BH6513FS are 4-channel PWM drivers for driving the motors and actuators in CD and MD players. MOSFET output stages are employed to keep power consumption down, and a charge pump circuit is included to multiply the VG voltage.

#### Applications

CD and MD players (portable units)

#### Features

- 1) Four power MOS H-bridges.

- 2) Charge pump  $(\times 3)$ .

- 3) PWM input.

- 4) Low on-resistance.

- 5) Low power consumption.

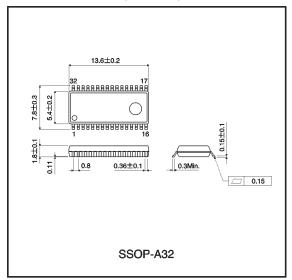

- 6) Compact SSOP-A32 package.

### ●Absolute maximum ratings (Ta = 25°C)

| Parameter                            | Symbol          | Limits            | Unit |  |

|--------------------------------------|-----------------|-------------------|------|--|

| H-bridge power supply voltage        | VM              | 9                 | V    |  |

| Control circuit power supply voltage | V <sub>DD</sub> | 9                 | V    |  |

| Pre-driver power supply voltage      | VG (pin18)      | 12                | V    |  |

| Driver output current                | lo (ch3, ch4)   | 500               | mA   |  |

|                                      | lo (ch1, ch2)   | 300*1             |      |  |

| Power dissipation                    | Pd              | 850* <sup>2</sup> | mW   |  |

| Operating temperature                | Topr            | <b>−20~+85</b>    | င    |  |

| Storage temperature                  | Tstg            | <b>−55∼+150</b>   | ొ    |  |

**<sup>\*1</sup>** 500ms.

#### ● Recommended operating conditions (Ta = 25°C)

| Parameter                            | Symbol          | Min.                     | Тур.  | Max. | Unit |

|--------------------------------------|-----------------|--------------------------|-------|------|------|

| H-bridge power supply voltage        | VM              | 1.6                      | 2.5   | 5.5  | V    |

| Control circuit power supply voltage | V <sub>DD</sub> | 2.4<br>2.7* <sup>3</sup> | 3.0   | 5.5  | V    |

| Pre-driver power supply voltage      | VG (pin18)      | VM+3.0                   | 9     | 11.5 | V    |

| Ambient temperature                  | Та              | -35                      | 25    | 85   | °C   |

| Pulse input frequency                | fin             | _                        | 176.4 | 200  | kHz  |

<sup>\*3</sup> When VG is supplied externally.

ROHM

695

<sup>\*2</sup> Reduced by 6.8mW for each increase in Ta of 1°C over 25°C.

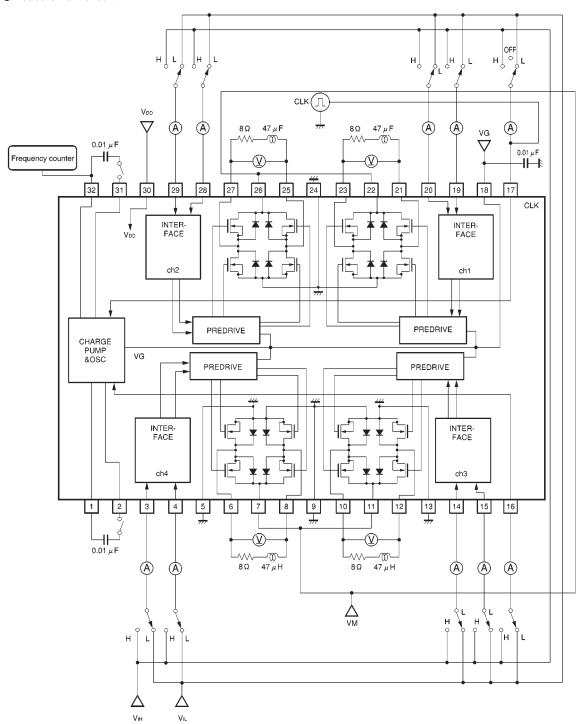

## Block diagram

# ●Pin descriptions

| Pin No. | Pin name                           | Function                           | Pin No. | Pin name                | Function                                            |  |

|---------|------------------------------------|------------------------------------|---------|-------------------------|-----------------------------------------------------|--|

| 1 C2M   | Negative connection pin for charge | 17                                 | CLK     | Synchronous clock input |                                                     |  |

| _ '     | 1 OZIVI                            | pump capacitor 2                   |         | VG                      | Charge pump output                                  |  |

| 2       | 2 C2P                              | Positive connection pin for charge | 19      | IN1R                    | Channel 1 reverse input                             |  |

|         | OZI                                | pump capacitor 2                   |         | IN1F                    | Channel 1 forward input                             |  |

| 3       | IN4R                               | Channel 4 reverse input            | 21      | OUT1F                   | Channel 1 forward output                            |  |

| 4       | IN4F                               | Channel 4 forward input            | 22      | VM1                     | Channel 1 power block power supply                  |  |

| 5       | GND4                               | Channel 4 GND and pre block GND    | 23      | OUT1R                   | Channel 1 reverse output                            |  |

| 6       | OUT4F                              | Channel 4 forward output           | 24      | GND12                   | Channels 1 and 2 power GND                          |  |

| 7       | VM4                                | Channel 4 power block power supply | 25      | OUT2R                   | Channel 2 reverse output                            |  |

| 8       | OUT4R                              | Channel 4 reverse output           | 26      | VM2                     | Channel 2 power block power supply                  |  |

| 9       | GND34                              | Channels 3 and 4 power GND         | 27      | OUT2F                   | Channel 2 forward output                            |  |

| 10      | OUT3R                              | Channel 3 reverse output           | 28      | IN2F                    | Channel 2 forward input                             |  |

| 11      | VM3                                | Channel 3 power block power supply | 29      | IN2R                    | Channel 2 reverse input                             |  |

| 12      | OUT3F                              | Channel 3 forward output           | 30      | V <sub>DD</sub>         | Pre block power supply                              |  |

| 13      | GND3                               | Channel 3 power GND                | 31      | C1M                     | Negative connection pin for charge                  |  |

| 14      | IN3F                               | Channel 3 forward input            | ] "     | CTIVI                   | pump capacitor 1                                    |  |

| 15      | IN3R                               | Channel 3 reverse input            | 32      | C1P                     | Positive connection pin for charge pump capacitor 1 |  |

| 16      | PSB                                | Power off                          | ] 32    | OIF                     |                                                     |  |

696

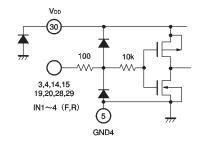

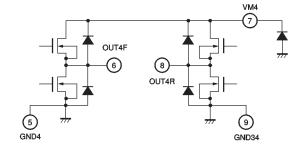

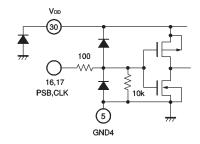

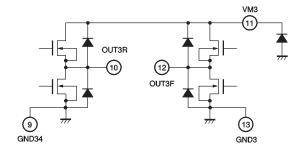

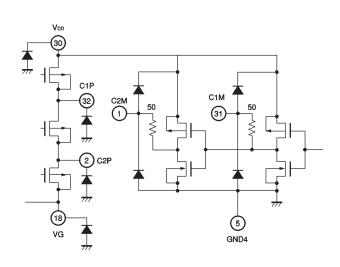

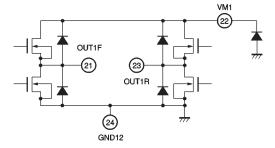

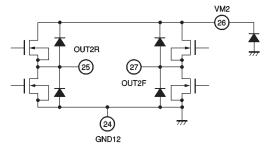

## ●Input / output circuits

Fig.1

• Electrical characteristics (unless otherwise noted, Ta = 25 °C, VM = 2.5 V, VDD = 3 V, VG is the internally pumped output,  $f_{IN}$  = 176kHz, and RL = 8 $\Omega$  - 47 $\mu$ H)

| Parameter                       | Symbol  | Min.                 | Тур. | Max. | Unit | Conditions                                   |  |

|---------------------------------|---------|----------------------|------|------|------|----------------------------------------------|--|

| (H-bridge power supply current) |         |                      |      | •    |      |                                              |  |

| No input                        | IMST    | _                    | _    | 1    | μΑ   | _                                            |  |

| Control circuit power supply cu | rent〉   |                      |      | 1    |      |                                              |  |

| Standby                         | IDDST   | _                    | _    | 1    | μΑ   | PSB=L                                        |  |

| No signal                       | IDDO    | _                    | 0.6  | 1    | mA   | PSB=H, all inputs Low                        |  |

| Operation                       | IDDA    | _                    | 3.3  | 6.5  | mA   | PSB=H, all channels driven together          |  |

| Pre-drive power supply voltage  | >       |                      |      | 1    |      |                                              |  |

| No input                        | IG1     | 7.5                  | 8.9  | 10   | V    | PSB=H, all inputs Low                        |  |

| Operation                       | IG2     | 6.0                  | 7.2  | 9.5  | V    | PSB=H, all channels driven together          |  |

| (Logic input characteristics)   |         |                      |      |      |      |                                              |  |

| Input high level voltage        | VIH     | V <sub>DD</sub> -0.6 | _    | _    | V    | _                                            |  |

| Input low level voltage         | VIL     | _                    | _    | 0.6  | V    | _                                            |  |

| Input high level current 1      | IIH1    | _                    | _    | 1    | μΑ   | V <sub>IN</sub> = 3V, each driver input      |  |

| Input low level current 1       | IIL1    | -1                   | _    | _    | μΑ   | V <sub>IN</sub> = 0V, each driver input      |  |

| Input high level current 2      | IIH2    | _                    | 300  | 600  | μА   | V <sub>IN</sub> = 3V, CLK, PSB pins          |  |

| Input low level current 2       | IIL2    | -1                   | _    | _    | μΑ   | V <sub>IN</sub> = 0V, CLK, PSB pins          |  |

|                                 | RON3, 4 | _                    | 0.8  | 1.2  |      | Balance of top and bottom resistors VG = 10V |  |

| Output on-resistance            | RON1, 2 | _                    | 1.2  | 2.0  | Ω    |                                              |  |

| Output transmission             | tRISE   | _                    | 0.2  | 1    | μsec | _                                            |  |

| delay time                      | tFALL   | _                    | 0.2  | 1    | μsec | _                                            |  |

| Minimum input pulse width       | tmin    | 200                  | _    | _    | nsec | Output pulse width 2 / 3 tmin or more        |  |

| Oscillator circuit>             |         | '                    |      | •    | •    |                                              |  |

| Free-running frequency          | fosc    | 150                  | 300  | 400  | kHz  | Pin 32 waveform monitor                      |  |

| Clock period range              | fsync   | 100                  | _    | 500  | kHz  | Input from CLK input                         |  |

ONot designed for radiation resistance.

## Driver truth table

| PSB* | IN1∼4F | IN1∼4R | OUT1∼3F | OUT1∼3R | OUT4F  | OUT4R  |

|------|--------|--------|---------|---------|--------|--------|

| Н    | L      | L      | L       | L       | L      | L      |

| Н    | L      | н      | L       | Н       | L      | Н      |

| Н    | Н      | L      | Н       | L       | L      | L      |

| Н    | Н      | Н      | L       | L       | Н      | L      |

| L    | ×      | ×      | High-Z  | High-Z  | High-Z | High-Z |

$<sup>\</sup>begin{tabular}{ll} $\ast$ When PSB is Low, all outputs are high impedance, regardless of the state of the inputs. \\ Also, the voltage multiplier circuit oscillator stops oscillating. \\ \end{tabular}$

698

## Measurement circuit

Fig.2

ROHM

## Operation notes

- (1) The charge pump circuit is a  $\times$  3 multiplier that uses the voltage on pin 30 as its reference. Therefore, set the voltage (VDD) on pin 30 so that the VG does not exceed its rating.

- (2) If you will use an externally-supplied VG, disconnect the capacitors between pins 31 and 32 and pins 1 and 2

- (3) The charge pump oscillator circuit runs freely when the CLK pin is connected to either V<sub>DD</sub> or GND. Also, as there is a pull-down resistor on the chip, it will also free run if CLK is left floating.

To synchronize with an external clock, input the clock pulses from the CLK pin.

### External dimensions (Units: mm)