Data Sheet July 2003 FN2988.2

## 256 x 4 CMOS RAM

The HM-6551/883 is a 256 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation. On chip latches are provided for address and data outputs allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

The HM-6551/883 is a fully static RAM and may be maintained in any state for an indefinite period of time. Data retention supply voltage and supply current are guaranteed over temperature.

# **Ordering Information**

| PACKAGE | TEMP.<br>RANGE     | 220ns         | 300ns        | PKG.<br>DWG.# |

|---------|--------------------|---------------|--------------|---------------|

| CERDIP  | -55°C to<br>+125°C | HM1-6551B/883 | HM1-6551/883 | F22.4         |

## **Pin Descriptions**

| PIN | DESCRIPTION   |  |  |  |  |

|-----|---------------|--|--|--|--|

| A   | Address Input |  |  |  |  |

| Ē   | Chip Enable   |  |  |  |  |

| W   | Write Enable  |  |  |  |  |

| S   | Chip Select   |  |  |  |  |

| D   | Data Input    |  |  |  |  |

| Q   | Data Output   |  |  |  |  |

### **Features**

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Data Retention . . . . . . . . . . . . . . . . at 2.0V Min

- TTL Compatible Input/Output

- High Output Drive 1 TTL Load

- · Internal Latched Chip Select

- · High Noise Immunity

- On-Chip Address Register

- · Latched Outputs

- · Three-State Output

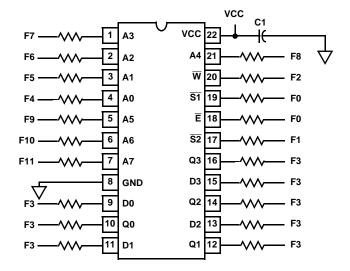

## **Pinout**

#### **HM-6551/883 (CERDIP)** TOP VIEW

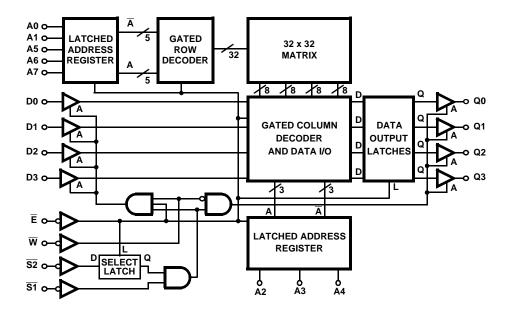

# **Functional Diagram**

#### NOTES:

- 1. Select Latch: L Low  $\rightarrow$  Q = D and Q latches on rising edge of L.

- 2. Address Latches And Gated Decoders: Latch on falling edge of  $\overline{\mathsf{E}}$  and gate on falling edge of  $\overline{\mathsf{E}}$ .

- 3. All lines positive logic-active high.

- 4. Three-State Buffers: A high  $\rightarrow$  output active.

- 5. Data Latches: L High  $\rightarrow$  Q = D and Q latches on falling edge of L.

## HM-6551/883

## **Absolute Maximum Ratings**

| Supply Voltage               |                        |

|------------------------------|------------------------|

| Input, Output or I/O Voltage | GND -0.3V to VCC +0.3V |

| ESD Classification           | Class 1                |

## **Operating Conditions**

| Operating Voltage Range     | +4.5V to +5.5V   |

|-----------------------------|------------------|

| Operating Temperature Range | 55°C to +125°C   |

| Input Low Voltage           |                  |

| nput High Voltage           | VCC -2.0V to VCC |

| Input Rise and Fall Time    | 40ns Max.        |

## **Thermal Information**

| Thermal Resistance                     | $\theta_{\sf JA}$ | $_{	extsf{	heta}}$ JC |   |

|----------------------------------------|-------------------|-----------------------|---|

| CERDIP Package                         | 60°C/W            | 15°C/W                |   |

| Maximum Storage Temperature Range      |                   | 65°C to +150°         | С |

| Maximum Junction Temperature           |                   | +175°                 | С |

| Maximum Lead Temperature (Soldering 10 | s)                | +300°                 | С |

## **Die Characteristics**

| Gate Count | 1930 | Gates |

|------------|------|-------|

|------------|------|-------|

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

### TABLE 1. HM-6551/883 DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

|                                  | (NOTE 1) GROUP A |                                                                               |                                                    | LIN                                          | MITS |      |       |

|----------------------------------|------------------|-------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------|------|------|-------|

| PARAMETER                        | SYMBOL           | CONDITIONS                                                                    | SUBGROUPS                                          | TEMPERATURE                                  | MIN  | MAX  | UNITS |

| Output Low Voltage               | VOL              | VCC = 4.5V<br>IOL = 1.6mA                                                     | 1, 2, 3                                            | $-55$ °C $\leq$ T <sub>A</sub> $\leq$ +125°C | -    | 0.4  | V     |

| Output High Voltage              | VOH              | VCC = 4.5V<br>IOH = -0.4mA                                                    | 1, 2, 3 $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ |                                              | 2.4  | -    | V     |

| Input Leakage Current            | II               | VCC = 5.5V,<br>VI = GND or VCC                                                | 1, 2, 3                                            | $-55$ °C $\leq$ T <sub>A</sub> $\leq$ +125°C | -1.0 | +1.0 | μА    |

| Output Leakage<br>Current        | IOZ              | VCC = 5.5 V,<br>VO = GND or VCC                                               | 1, 2, 3                                            | $-55$ °C $\leq$ T <sub>A</sub> $\leq$ +125°C | -1.0 | +1.0 | μА    |

| Data Retention Supply<br>Current | ICCDR            | VCC = 2.0V, <del>E</del> = VCC<br>IO = 0mA,<br>VI = VCC or GND                | 1, 2, 3                                            | -55°C ≤ T <sub>A</sub> ≤ +125°C              | -    | 10   | μА    |

| Operating Supply<br>Current      | ICCOP            | VCC = 5.5V, (Note 2)<br>$\overline{E} = 1MHz$ , $IO = 0mA$<br>VI = VCC or GND | 1, 2, 3                                            | 1, 2, 3 -55°C ≤ T <sub>A</sub> ≤ +125°C      |      | 4    | mA    |

| Standby Supply<br>Current        | ICCSB            | VCC = 5.5V,<br>IO = 0mA<br>VI = VCC or GND                                    | 1, 2, 3                                            | 1, 2, 3 -55°C ≤ T <sub>A</sub> ≤ +125°C      |      | 10   | μА    |

#### NOTES:

- 1. All voltages referenced to device GND.

- 2. Typical derating 1.5mA/MHz increase in ICCOP.

### HM-6551/883

### TABLE 2. HM-6551/883 A.C. ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

|                                         |                           |        |                            | LIMITS    |                                              |       |        |     |     |       |

|-----------------------------------------|---------------------------|--------|----------------------------|-----------|----------------------------------------------|-------|--------|-----|-----|-------|

|                                         | (NOTES 1, 2) GROUP A SUB- |        |                            | HM-65     | 51B/883                                      | HM-65 | 51/883 |     |     |       |

| PARAMETER                               | 5                         | SYMBOL | CONDITIONS                 | GROUPS    | TEMPERATURE                                  | MIN   | MAX    | MIN | MAX | UNITS |

| Chip Enable<br>Access Time              | (1)                       | TELQV  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | -     | 220    | -   | 300 | ns    |

| Address Access<br>Time                  | (2)                       | TAVQV  | VCC = 4.5 and 5.5V, Note 3 | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | -     | 220    | -   | 300 | ns    |

| Chip Select 1<br>Output Enable Time     | (3)                       | TS1LQX | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 5     | -      | 5   | -   | ns    |

| Write Enable<br>Output Disable Time     | (4)                       | TWLQZ  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | -     | 130    | -   | 150 | ns    |

| Chip Select 1<br>Output Disable Time    | (5)                       | TS1HQZ | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | -     | 130    | -   | 150 | ns    |

| Chip Enable Pulse<br>Negative Width     | (6)                       | TELEH  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 220   | -      | 300 | -   | ns    |

| Chip Enable Pulse<br>Positive Width     | (7)                       | TEHEL  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 100   | -      | 100 | -   | ns    |

| Address Setup Time                      | (8)                       | TAVEL  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55$ °C $\leq$ T <sub>A</sub> $\leq$ +125°C | 0     | -      | 0   | -   | ns    |

| Chip Select 2<br>Setup Time             | (9)                       | TS2LEL | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 0     | -      | 0   | -   | ns    |

| Address Hold Time                       | (10)                      | TELAX  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 40    | -      | 50  | -   | ns    |

| Chip Select 2 Hold<br>Time              | (11)                      | TELS2X | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 40    | -      | 50  | -   | ns    |

| Data Setup Time                         | (12)                      | TDVWH  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 100   | -      | 150 | -   | ns    |

| Data Hold Time                          | (13)                      | TWHDX  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 0     | -      | 0   | -   | ns    |

| Chip Select 1 Write<br>Pulse Setup Time | (14)                      | TWLS1H | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$   | 120   | -      | 180 | -   | ns    |

| Chip Enable Write<br>Pulse Setup Time   | (15)                      | TWLEH  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 120   | -      | 180 | -   | ns    |

| Chip Select 1 Write<br>Pulse Hold Time  | (16)                      | TS1LWH | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 120   | -      | 180 | -   | ns    |

| Chip Enable Write<br>Pulse Hold Time    | (17)                      | TELWH  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_A \le +125^{\circ}C$     | 120   | -      | 180 | -   | ns    |

| Write Enable Pulse<br>Width             | (18)                      | TWLWH  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \leq T_{A} \leq +125^{\circ}C$ | 120   | -      | 180 | -   | ns    |

| Read or Write<br>Cycle Time             | (19)                      | TELEL  | VCC = 4.5 and 5.5V         | 9, 10, 11 | $-55^{\circ}C \le T_{A} \le +125^{\circ}C$   | 320   | -      | 400 | -   | ns    |

## NOTES:

- 1. All voltages referenced to device GND.

- 2. Input pulse levels: 0.8V to VCC-2.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: IOL = 1.6mA, IOH = -0.4mA, CL = 50pF (min) for CL greater than 50pF, access time is derated by 0.15ns per pF.

- 3. TAVQV = TELQV + TAVEL.

## HM-6551/883

TABLE 3. HM-6551B/883 AND HM-6551/883 ELECTRICAL PERFORMANCE SPECIFICATIONS

|                    |        |                                                                          |      | LIMITS                 |     | LIMITS |       |

|--------------------|--------|--------------------------------------------------------------------------|------|------------------------|-----|--------|-------|

| PARAMETER          | SYMBOL | CONDITIONS                                                               | NOTE | TEMPERATURE            | MIN | MAX    | UNITS |

| Input Capacitance  | CI     | VCC = Open, f = 1MHz, All<br>Measurements Referenced to<br>Device Ground | 1    | T <sub>A</sub> = +25°C | -   | 10     | pF    |

| Output Capacitance | CO     | VCC = Open, f = 1MHz, All<br>Measurements Referenced to<br>Device Ground | 1    | T <sub>A</sub> = +25°C | -   | 12     | pF    |

#### NOTE:

### **TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | 1, 7, 9                       |

| PDA                | 100%/5004    | 1                             |

| Final Test         | 100%/5004    | 2, 3, 8A, 8B, 10, 11          |

| Group A            | Samples/5005 | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C & D       | Samples/5005 | 1, 7, 9                       |

<sup>1.</sup> The parameters listed in Table 3 are controlled via design or process parameters are characterized upon initial design and after major process and/or design changes.

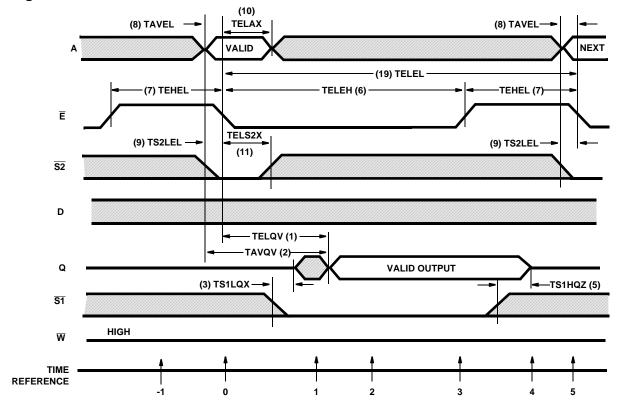

# **Timing Waveforms**

FIGURE 1. READ CYCLE

#### **TRUTH TABLE**

| TIME      |     |    | INP       | UTS | OUTPUTS |   |   |                                                            |

|-----------|-----|----|-----------|-----|---------|---|---|------------------------------------------------------------|

| REFERENCE | Ē   | S1 | <u>S2</u> | w   | Α       | D | Q | FUNCTION                                                   |

| -1        | Н   | Н  | Х         | Х   | Х       | Х | Z | Memory Disabled                                            |

| 0         | 7_  | Х  | L         | Н   | V       | Х | Z | Addresses and \$\overline{\S2}\$ are Latched, Cycle Begins |

| 1         | L   | L  | Х         | Н   | Х       | Х | Х | Output Enabled but Undefined                               |

| 2         | L   | L  | Х         | Н   | Х       | Х | V | Data Output Valid                                          |

| 3         | _7_ | L  | Х         | Н   | Х       | Х | V | Outputs Latched, Valid Data,<br>S2 Unlatches               |

| 4         | Н   | Н  | Х         | Х   | Х       | Х | Z | Prepare for Next Cycle (Same as -1)                        |

| 5         | 7_  | Х  | L         | Н   | V       | Х | Z | Cycle Ends, Next Cycle Begins (Same as 0)                  |

The HM-6551/883 Read Cycle is initiated by the falling edge of  $\overline{\mathbb{E}}$ . This signal latches the input address word and  $\overline{S2}$  into on-chip registers providing the minimum setup and hold times are met. After the required hold time, these inputs may change state without affecting device operation.  $\overline{S2}$  acts as a high order address and simplifies decoding. For the output to be read,  $\overline{\mathbb{E}}$ ,  $\overline{S1}$  must be low and  $\overline{\mathbb{W}}$  must be high.  $\overline{S2}$  must have been latched low on the falling edge of  $\overline{\mathbb{E}}$ . The output data will be valid at access time (TELQV). The HM-6551/883

has output data latches that are controlled by  $\overline{E}$ . On the rising edge of  $\overline{E}$  the present data is latched and remains in that state until  $\overline{E}$  falls. Also on the rising edge of  $\overline{E}$ ,  $\overline{S2}$  unlatches and controls the outputs along with  $\overline{S1}$ . Either or both  $\overline{S1}$  or  $\overline{S2}$  may be used to force the output buffers into a high impedance state.

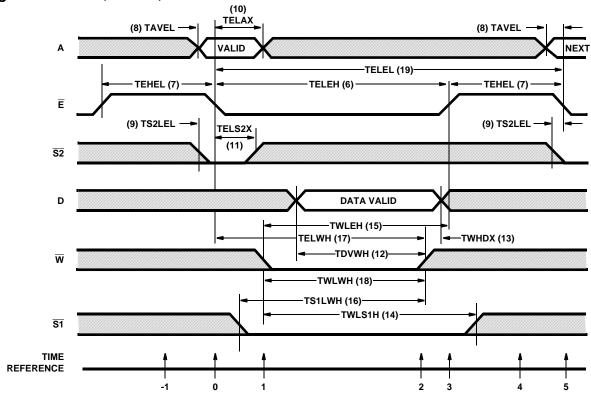

## Timing Waveforms (Continued)

FIGURE 2. WRITE CYCLE TRUTH TABLE

| TIME      |    |    | INP       | OUTPUTS |   |   |   |                                                            |

|-----------|----|----|-----------|---------|---|---|---|------------------------------------------------------------|

| REFERENCE | Ē  | S1 | <u>S2</u> | w       | Α | D | Q | FUNCTION                                                   |

| -1        | Н  | Н  | Х         | Х       | Х | Х | Z | Memory Disabled                                            |

| 0         | 7_ | Х  | L         | Х       | V | Х | Z | Cycle Begins, Addresses and \$\overline{\S2}\$ are Latched |

| 1         | L  | L  | Х         | 7       | Х | Х | Z | Write Period Begins                                        |

| 2         | L  | L  | Х         |         | Х | V | Z | Data In is Written                                         |

| 3         |    | Х  | Х         | Н       | Х | Х | Z | Write is Completed                                         |

| 4         | Н  | Н  | Х         | Х       | Х | Х | Z | Prepare for Next Cycle (Same as -1)                        |

| 5         | 7_ | Х  | L         | Х       | V | Х | Z | Cycle Ends, Next Cycle Begins (Same as 0)                  |

In the Write Cycle the falling edge of  $\overline{E}$  latches the addresses and  $\overline{S2}$  into on-chip registers.  $\overline{S2}$  must be latched in the low state to enable the device. The write portion of the cycle is defined as  $\overline{E}$ ,  $\overline{W}$ ,  $\overline{S1}$  being low and  $\overline{S2}$  being latched simultaneously. The  $\overline{W}$  line may go low at any time during the cycle providing that the write pulse setup times (TWLEH and TWLS1H) are met. The write portion of the cycle is terminated on the first rising edge of either  $\overline{E}$ ,  $\overline{W}$ , or  $\overline{S1}$ .

If a series of consecutive write cycles are to be executed, the  $\overline{W}$  line may be held low until all desired locations have been written. If this method is used, data setup and hold times must be referenced to the first rising edge of  $\overline{E}$  or  $\overline{S1}$ . By positioning the write pulse at different times within the  $\overline{E}$  and  $\overline{S1}$  low time

(TELEH), various types of write cycles may be performed. If the  $\overline{S1}$  low time (TS1LS1H) is greater than the  $\overline{W}$  pulse, plus an output enable time (TS1LQX), a combination read-write cycle is executed. Data may be modified an indefinite number of times during any write cycle (TELEH).

The HM-6551/883 may be used on a common I/O bus structure by tying the input and output pins together. The multiplexing is accomplished internally by the  $\overline{W}$  line. In the write cycle, when  $\overline{W}$  goes low, the output buffers are forced to a high impedance state. One output disable time delay (TWLQZ) must be allowed before applying input data to the bus.

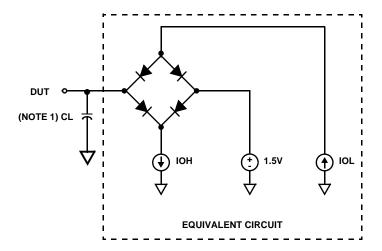

## **Test Load Circuit**

#### NOTE:

1. Test head capacitance includes stray and jig capacitance.

## **Burn-In Circuit**

#### HM-6551/883 CERDIP

### NOTES:

All resistors 47k $\Omega$  ±5%.

$F0 = 100kHz \pm 10\%$ .

$F1 = F0 \div 2$ ,  $F2 = F1 \div 2$ ,  $F3 = F2 \div 2 \dots F12 = F11 \div 2$ .

$VCC = 5.5V \pm 0.5V.$

$VIH = 4.5V \pm 10\%$ .

VIL = -0.2V to +0.4V.

$C1 = 0.01 \mu F$  Min.

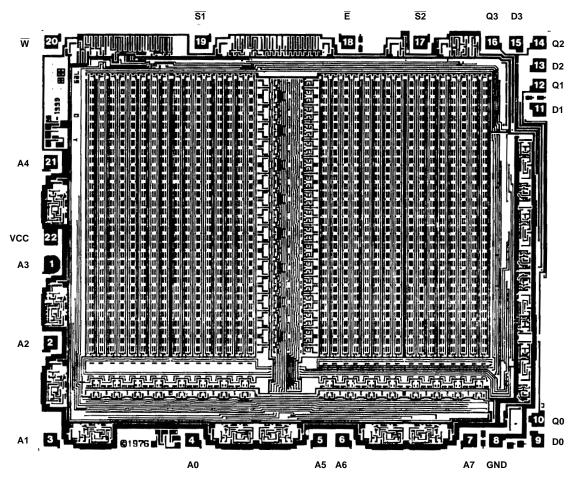

## Die Characteristics

**DIE DIMENSIONS:**

$132 \times 160 \times 19 \pm 1 \text{mils}$

**METALLIZATION:**

Type: Si - Al

Thickness: 11kÅ ±2kÅ

**GLASSIVATION:**

Type: SiO<sub>2</sub>

Thickness: 8kÅ ±1kÅ

WORST CASE CURRENT DENSITY:

1.337 x 10<sup>5</sup> A/cm<sup>2</sup>

**LEAD TEMPERATURE** (10s soldering):

≤300°C

# Metallization Mask Layout

HM-6551/883

NOTE: Pin numbers correspond to DIP Package only.

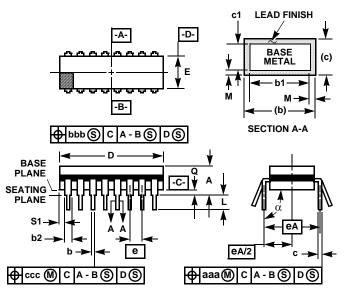

# Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

#### NOTES:

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 3. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

F22.4 MIL-STD-1835 GDIP1-T22 (D-7, CONFIGURATION A) 22 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INCHES    |                  | MILLIMETERS |                  |       |

|--------|-----------|------------------|-------------|------------------|-------|

| SYMBOL | MIN       | MAX              | MIN         | MAX              | NOTES |

| Α      | -         | 0.225            | -           | 5.72             | -     |

| b      | 0.014     | 0.026            | 0.36        | 0.66             | 2     |

| b1     | 0.014     | 0.023            | 0.36        | 0.58             | 3     |

| b2     | 0.045     | 0.065            | 1.14        | 1.65             | -     |

| b3     | 0.023     | 0.045            | 0.58        | 1.14             | 4     |

| С      | 0.008     | 0.018            | 0.20        | 0.46             | 2     |

| c1     | 0.008     | 0.015            | 0.20        | 0.38             | 3     |

| D      | -         | 1.111            | -           | 28.22            | 5     |

| Е      | 0.350     | 0.410            | 8.89        | 10.41            | 5     |

| е      | 0.100 BSC |                  | 2.54 BSC    |                  | -     |

| eA     | 0.400 BSC |                  | 10.16 BSC   |                  | -     |

| eA/2   | 0.200 BSC |                  | 5.08 BSC    |                  | -     |

| L      | 0.125     | 0.200            | 3.18        | 5.08             | -     |

| Q      | 0.015     | 0.070            | 0.38        | 1.78             | 6     |

| S1     | 0.005     | -                | 0.13        | -                | 7     |

| α      | 90°       | 105 <sup>0</sup> | 90°         | 105 <sup>0</sup> | -     |

| aaa    | -         | 0.015            | =           | 0.38             | -     |

| bbb    | -         | 0.030            | -           | 0.76             | -     |

| ccc    | -         | 0.010            | -           | 0.25             | -     |

| М      | -         | 0.0015           | =           | 0.038            | 2, 3  |

| N      | 22        |                  | 22          |                  | 8     |

Rev. 0 6/13/95

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com