## LMZ14203

# 3A SIMPLE SWITCHER® Power Module with 42V Maximum Input Voltage

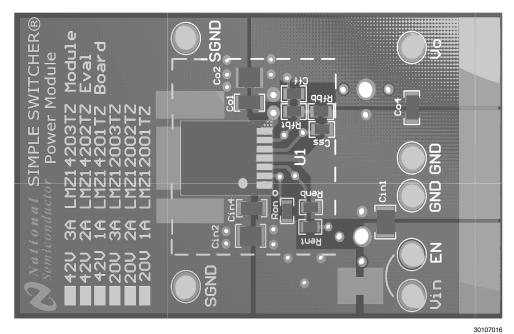

Easy to use 7 pin package

Top View

**Bottom View**

301070

TO-PMOD 7 Pin Package 10.16 x 13.77 x 4.57 mm (0.4 x 0.542 x 0.18 in)  $\theta_{JA} = 20^{\circ}\text{C/W}, \, \theta_{JC} = 1.9^{\circ}\text{C/W}$  RoHS Compliant

## **Electrical Specifications**

- 18W maximum total output power

- Up to 3A output current

- Input voltage range 6V to 42V

- Output voltage range 0.8V to 6V

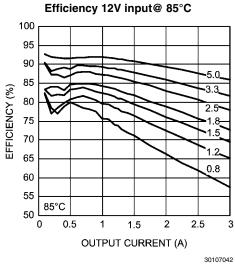

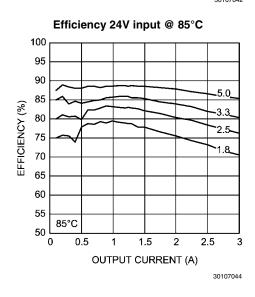

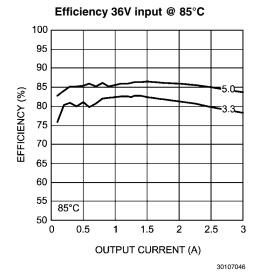

- Efficiency up to 90%

### **Key Features**

- Integrated shielded inductor

- Simple PCB layout

- Flexible startup sequencing using external soft-start and precision enable

- Protection against inrush currents and faults such as input UVLO and output short circuit

- -40°C to 125°C junction temperature range

- Single exposed pad and standard pinout for easy mounting and manufacturing

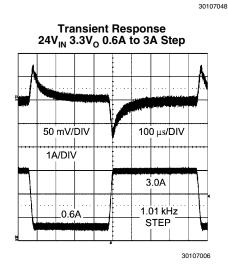

- Fast transient response for powering FPGAs and ASICs

- Low output voltage ripple

- Pin-to-pin compatible family:

LMZ14203/2/1 (42V max 3A, 2A, 1A)

LMZ12003/2/1 (20V max 3A, 2A, 1A)

- Fully enabled for Webench® Power Designer

## **Applications**

- Point of load conversions from 12V and 24V input rail

- Time critical projects

- Space constrained / high thermal requirement applications

- Negative output voltage applications (See AN-2027)

#### **Performance Benefits**

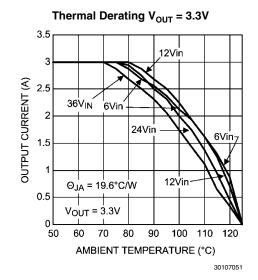

- Operates at high ambient temperature with no thermal derating

- High efficiency reduces system heat generation

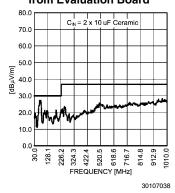

- Low radiated emissions (EMI) complies with EN55022 class B standard

- Passes 10V/m radiated immunity EMI test standard EN61000 4-3

## **System Performance**

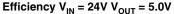

30107036

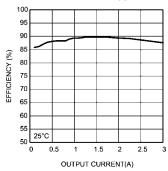

# Thermal derating curve $V_{IN} = 24V$ , $V_{OUT} = 5.0V$ ,

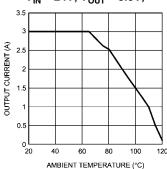

30107037

# Radiated Emissions (EN 55022 Class B) from Evaluation Board

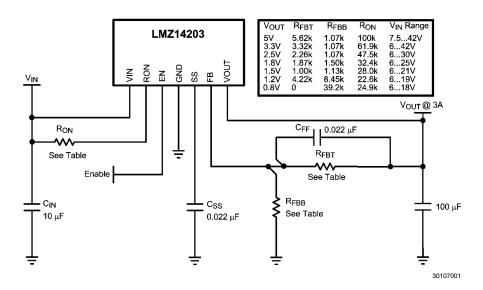

## **Simplified Application Schematic**

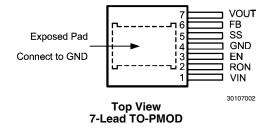

## **Connection Diagram**

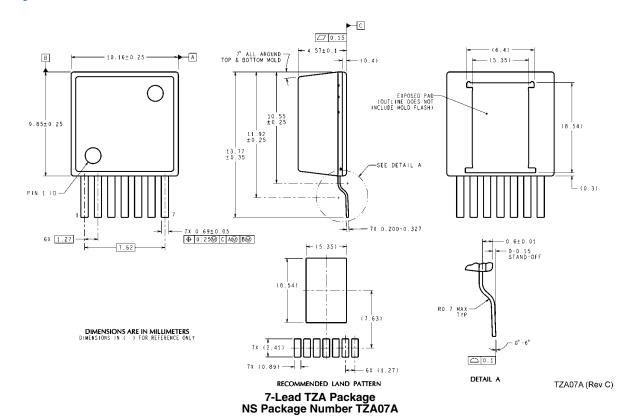

## **Ordering Information**

| Order Number    | Package Type | NSC Package Drawing | Supplied As                |  |

|-----------------|--------------|---------------------|----------------------------|--|

| LMZ14203TZ-ADJ  | TO-PMOD-7    | TZA07A              | 250 Units on Tape and Reel |  |

| LMZ14203TZX-ADJ | TO-PMOD-7    | TZA07A              | 500 Units on Tape and Reel |  |

| LMZ14203TZE-ADJ | TO-PMOD-7    | TZA07A              | 45 Units in a Rail         |  |

## **Pin Descriptions**

| Pin | Name | Description                                                                                                                                                                                                                                                |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VIN  | Supply input — Nominal operating range is 6V to 42V. A small amount of internal capacitance is contained within the package assembly. Additional external input capacitance is required between this pin and exposed pad.                                  |

| 2   | RON  | On Time Resistor — An external resistor from $V_{IN}$ to this pin sets the on-time of the application. Typical values range from 25k to 124k ohms.                                                                                                         |

| 3   | EN   | Enable — Input to the precision enable comparator. Rising threshold is 1.18V nominal; 90 mV hysteresis nominal. Maximum recommended input level is 6.5V.                                                                                                   |

| 4   | GND  | Ground — Reference point for all stated voltages. Must be externally connected to EP.                                                                                                                                                                      |

| 5   | SS   | Soft-Start — An internal 8 µA current source charges an external capacitor to produce the soft-start function. This node is discharged at 200 µA during disable, over-current, thermal shutdown and internal UVLO conditions.                              |

| 6   | FB   | Feedback — Internally connected to the regulation, over-voltage, and short-circuit comparators. The regulation reference point is 0.8V at this input pin. Connected the feedback resistor divider between the output and ground to set the output voltage. |

| Pin | Name | Description                                                                                                                                                             |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VOUT | Output Voltage — Output from the internal inductor. Connect the output capacitor between this pin and exposed pa                                                        |

| EP  | EP   | Exposed Pad — Internally connected to pin 4. Used to dissipate heat from the package during operation. Must be electrically connected to pin 4 external to the package. |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

|     |      |                                                                                                                                                                         |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

VIN, RON to GND -0.3V to 43.5V EN, FB, SS to GND -0.3V to 7V Junction Temperature 150°C Storage Temperature Range -65°C to 150°C

ESD Susceptibility(Note 2)

For soldering specifications: see product folder at www.national.com and www.national.com/ms/MS-SOLDERING.pdf

## **Operating Ratings** (Note 1)

$V_{\text{IN}}$  6V to 42V EN 0V to 6.5V Operation Junction Temperature  $-40\,^{\circ}\text{C}$  to 125 $^{\circ}\text{C}$

Min

± 2 kV

May

**Electrical Characteristics** Limits in standard type are for  $T_J = 25^{\circ}\text{C}$  only; limits in boldface type apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 24V$ , Vout = 3.3V

| Symbol                       | Parameter                                  | Conditions                                                                     |       | Typ<br>(Note 4) | Max<br>(Note 3) | Units            |

|------------------------------|--------------------------------------------|--------------------------------------------------------------------------------|-------|-----------------|-----------------|------------------|

| SYSTEM PAR                   | AMETERS                                    |                                                                                | ,     | , ,             | ,               | 1                |

| Enable Contro                | ı                                          |                                                                                |       |                 |                 |                  |

| V <sub>EN</sub>              | EN threshold trip point                    | V <sub>EN</sub> rising                                                         | 1.1   | 1.18            | 1.25            | ٧                |

| V <sub>EN-HYS</sub>          | EN threshold hysteresis                    | V <sub>EN</sub> falling                                                        |       | 90              |                 | mV               |

| Soft-Start                   | -                                          | , -:-                                                                          |       | Į.              |                 |                  |

| I <sub>SS</sub>              | SS source current                          | V <sub>SS</sub> = 0V                                                           | 5     | 8               | 11              | μA               |

| I <sub>SS-DIS</sub>          | SS discharge current                       |                                                                                |       | -200            |                 | μΑ               |

| Current Limit                | •                                          |                                                                                |       | !               |                 |                  |

| I <sub>CL</sub>              | Current limit threshold                    | d.c. average<br>V <sub>IN</sub> = 12V to 24V                                   | 3.2   | 4.2             | 5.25            | А                |

| ON/OFF Timer                 | •                                          |                                                                                |       |                 |                 |                  |

| t <sub>ON-MIN</sub>          | ON timer minimum pulse width               |                                                                                |       | 150             |                 | ns               |

| t <sub>OFF</sub>             | OFF timer pulse width                      |                                                                                |       | 260             |                 | ns               |

| Regulation an                | d Over-Voltage Comparator                  |                                                                                |       | •               |                 |                  |

| $V_{FB}$                     | In-regulation feedback voltage             | $V_{SS} > + 0.8V$ $T_{J} = -40^{\circ}C \text{ to } 125^{\circ}C$ $I_{O} = 3A$ | 0.784 | 0.804           | 0.825           | V                |

|                              |                                            | $V_{SS} >+ 0.8V$ $T_J = 25$ °C $I_O = 10 \text{ mA}$                           | 0.786 | 0.802           | 0.818           | V                |

| $V_{FB-OV}$                  | Feedback over-voltage protection threshold |                                                                                |       | 0.92            |                 | V                |

| I <sub>FB</sub>              | Feedback input bias current                |                                                                                |       | 5               |                 | nA               |

| IQ                           | Non Switching Input Current                | V <sub>FB</sub> = 0.86V                                                        |       | 1               |                 | mA               |

| I <sub>SD</sub>              | Shut Down Quiescent Current                | V <sub>EN</sub> = 0V                                                           |       | 25              |                 | μΑ               |

| Thermal Chara                | acteristics                                |                                                                                |       |                 |                 |                  |

| T <sub>SD</sub>              | Thermal Shutdown                           | Rising                                                                         |       | 165             |                 | °C               |

| T <sub>SD-HYST</sub>         | Thermal shutdown hysteresis                | Falling                                                                        |       | 15              |                 | °C               |

| $\theta_{JA}$                | Junction to Ambient                        | 4 layer JEDEC Printed Circuit Board,<br>100 vias, No air flow                  |       | 19.3            |                 | °C/W             |

|                              |                                            | 2 layer JEDEC Printed Circuit Board, No air flow                               |       | 21.5            |                 | °C/W             |

| $\theta_{JC}$                | Junction to Case                           | No air flow                                                                    |       | 1.9             |                 | °C/W             |

|                              | CE PARAMETERS                              | 1                                                                              |       |                 |                 |                  |

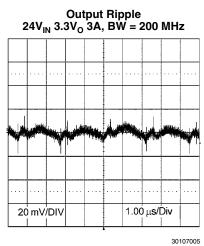

| ΔV <sub>O</sub>              | Output Voltage Ripple                      |                                                                                |       | 8               |                 | mV <sub>PF</sub> |

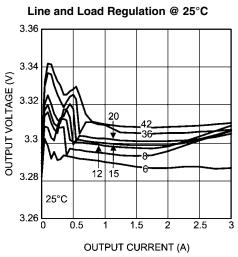

| $\Delta V_{O}/\Delta V_{IN}$ | Line Regulation                            | V <sub>IN</sub> = 12V to 42V, I <sub>O</sub> = 3A                              |       | .01             |                 | %                |

| U/ TIN                       | Load Regulation                            | V <sub>IN</sub> = 24V                                                          |       | 1.5             | <del> </del>    | mV/A             |

| Symbol | Parameter  | Conditions                             | Min<br>( <i>Note 3</i> ) | Typ<br>(Note 4) | Max<br>( <i>Note 3</i> ) | Units |

|--------|------------|----------------------------------------|--------------------------|-----------------|--------------------------|-------|

| η      | Efficiency | $V_{IN} = 24V V_O = 3.3V I_O = 1A$     |                          | 92              |                          | %     |

| η      | Efficiency | $V_{IN} = 24V V_{O} = 3.3V I_{O} = 3A$ |                          | 85              |                          | %     |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: The human body model is a 100pF capacitor discharged through a 1.5 kΩ resistor into each pin. Test method is per JESD-22-114.

**Note 3:** Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 4: Typical numbers are at 25°C and represent the most likely parametric norm.

Note 5: EN 55022:2006, +A1:2007, FCC Part 15 Subpart B: 2007. See AN-2024 and layout for information on device under test.

Note 6: Theta JA measured on a 1.705" x 3.0" four layer board, with one ounce copper, thirty five 12 mil thermal vias, no air flow, and 1W power dissipation. Refer to PCB layout diagrams

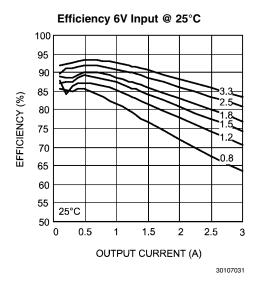

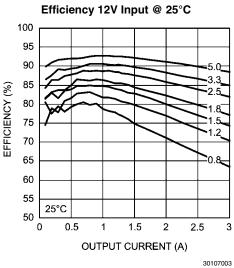

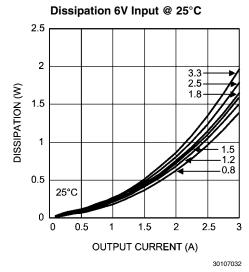

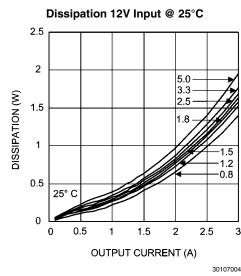

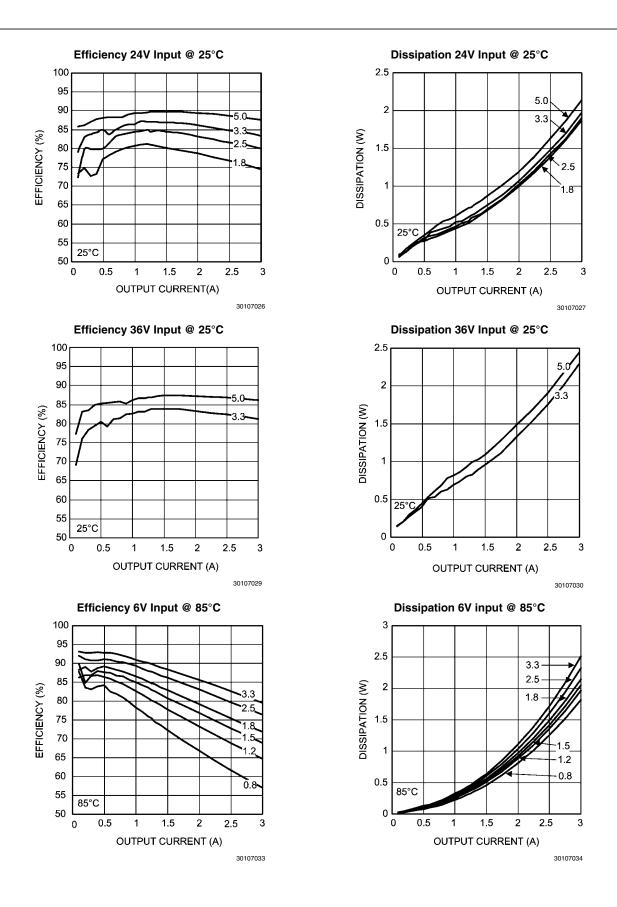

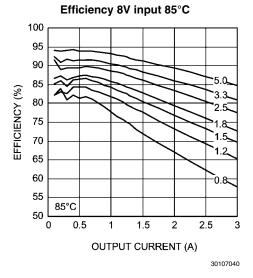

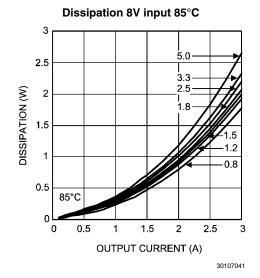

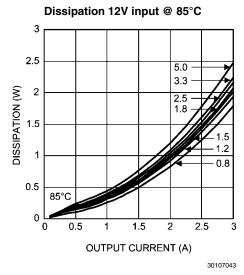

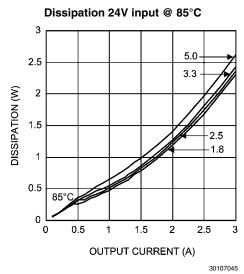

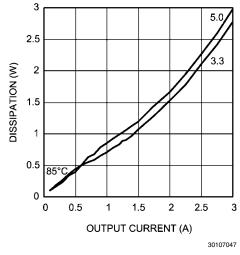

## **Typical Performance Characteristics**

Unless otherwise specified, the following conditions apply:  $V_{IN} = 24V$ ; Cin = 10uF X7R Ceramic;  $C_O = 100uF$  X7R Ceramic; Tambient = 25 C for efficiency curves and waveforms.

Dissipation 36V input @ 85°C

### **Application Block Diagram**

#### **COT Control Circuit Overview**

Constant On Time control is based on a comparator and an on-time one shot, with the output voltage feedback compared with an internal 0.8V reference. If the feedback voltage is below the reference, the main MOSFET is turned on for a fixed on-time determined by a programming resistor  $R_{\rm ON}.\ R_{\rm ON}$  is connected to  $V_{\rm IN}$  such that on-time is reduced with increasing input supply voltage. Following this on-time, the main MOSFET remains off for a minimum of 260 ns. If the voltage on the feedback pin falls below the reference level again the on-time cycle is repeated. Regulation is achieved in this manner.

# **Design Steps for the LMZ14203 Application**

The LMZ14203 is fully supported by Webench® and offers the following: Component selection, electrical and thermal simulations as well as the build-it board for a reduction in design time. The following list of steps can be used to manually design the LMZ14203 application.

- Select minimum operating V<sub>IN</sub> with enable divider resistors

- Program V<sub>O</sub> with divider resistor selection

- Program turn-on time with soft-start capacitor selection

- Select C<sub>O</sub>

- Select C<sub>IN</sub>

- Set operating frequency with RON

- Determine module dissipation

- Layout PCB for required thermal performance

#### ENABLE DIVIDER, R<sub>ENT</sub> AND R<sub>ENB</sub> SELECTION

The enable input provides a precise 1.18V band-gap rising threshold to allow direct logic drive or connection to a voltage divider from a higher enable voltage such as  $V_{\rm IN}$ . The enable input also incorporates 90 mV (typ) of hysteresis resulting in a falling threshold of 1.09V. The maximum recommended voltage into the EN pin is 6.5V. For applications where the midpoint of the enable divider exceeds 6.5V, a small zener can be added to limit this voltage.

30107008

The function of this resistive divider is to allow the designer to choose an input voltage below which the circuit will be disabled. This implements the feature of programmable under voltage lockout. This is often used in battery powered systems to prevent deep discharge of the system battery. It is also useful in system designs for sequencing of output rails or to prevent early turn-on of the supply as the main input voltage rail rises at power-up. Applying the enable divider to the main input rail is often done in the case of higher input voltage systems such as 24V AC/DC systems where a lower boundary of operation should be established. In the case of sequencing supplies, the divider is connected to a rail that becomes active earlier in the power-up cycle than the LMZ14203 output rail. The two resistors should be chosen based on the following ratio:

$$R_{ENT} / R_{ENB} = (V_{IN \ UVLO} / 1.18V) - 1$$

(1)

The LMZ14203 demonstration and evaluation boards use  $11.8k\Omega$  for  $R_{ENB}$  and  $68.1k\Omega$  for  $R_{ENT}$  resulting in a rising UV-LO of 8V. This divider presents 6.25V to the EN input when the divider input is raised to 42V.

#### **OUTPUT VOLTAGE SELECTION**

Output voltage is determined by a divider of two resistors connected between  $\rm V_{\rm O}$  and ground. The midpoint of the divider is connected to the FB input. The voltage at FB is compared to a 0.8V internal reference. In normal operation an on-time cycle is initiated when the voltage on the FB pin falls below 0.8V. The main MOSFET on-time cycle causes the output voltage to rise and the voltage at the FB to exceed 0.8V. As long as the voltage at FB is above 0.8V, on-time cycles will not occur.

The regulated output voltage determined by the external divider resistors RFBT and RFBB is:

$$V_O = 0.8V * (1 + R_{FBT} / R_{FBB})$$

(2)

Rearranging terms; the ratio of the feedback resistors for a desired output voltage is:

$$R_{FBT} / R_{FBB} = (V_O / 0.8V) - 1$$

(3)

These resistors should be chosen from values in the range of 1.0 kohm to 10.0 kohm.

For  $V_{\rm O}=0.8V$  the FB pin can be connected to the output directly so long as an output preload resistor remains that draws more than 20uA. Converter operation requires this minimum load to create a small inductor ripple current and maintain proper regulation when no load is present.

A feed-forward capacitor is placed in parallel with  $R_{\rm FBT}$  to improve load step transient response. Its value is usually determined experimentally by load stepping between DCM and CCM conduction modes and adjusting for best transient response and minimum output ripple.

A table of values for  $R_{\text{FBT}}$  ,  $R_{\text{FBB}}$  ,  $C_{\text{FF}}$  and  $R_{\text{ON}}$  is included in the applications schematic.

#### SOFT-START CAPACITOR SELECTION

Programmable soft-start permits the regulator to slowly ramp to its steady state operating point after being enabled, thereby reducing current inrush from the input supply and slowing the output voltage rise-time to prevent overshoot.

Upon turn-on, after all UVLO conditions have been passed, an internal 8uA current source begins charging the external soft-start capacitor. The soft-start time duration to reach steady state operation is given by the formula:

$$t_{SS} = V_{REF} * C_{SS} / Iss = 0.8V * C_{SS} / 8uA$$

(4)

This equation can be rearranged as follows:

$$C_{SS} = t_{SS} * 8 \mu A / 0.8 V$$

(5)

Use of a 0.022µF capacitor results in 2.2 msec soft-start duration. This is recommended as a minimum value.

As the soft-start input exceeds 0.8V the output of the power stage will be in regulation. The soft-start capacitor continues charging until it reaches approximately 3.8V on the SS pin. Voltage levels between 0.8V and 3.8V have no effect on other circuit operation. Note that the following conditions will reset the soft-start capacitor by discharging the SS input to ground with an internal 200  $\mu\text{A}$  current sink.

- The enable input being "pulled low"

- Thermal shutdown condition

- Over-current fault

- Internal Vcc UVLO (Approx 4V input to V<sub>IN</sub>)

#### Co SELECTION

None of the required C $_{\rm O}$  output capacitance is contained within the module. At a minimum, the output capacitor must meet the worst case minimum ripple current rating of 0.5 \* I $_{\rm LR~P-P}$ , as calculated in equation (19) below. Beyond that, additional capacitance will reduce output ripple so long as the ESR is low enough to permit it. A minimum value of 10  $\mu$ F is generally required. Experimentation will be required if attempting to operate with a minimum value. Ceramic capacitors or other low ESR types are recommended. See AN-2024 for more detail.

The following equation provides a good first pass approximation of  ${\rm C}_{\rm O}$  for load transient requirements:

$$C_O \ge I_{STEP}^* V_{FB}^* L^* V_{IN} / (4^* V_O^* (V_{IN} - V_O)^* V_{OUT-TRAN})$$

(6)

Solvina:

$$C_0 \ge 3A^*0.8V^*6.8\mu H^*24V / (4^*3.3V^*(24V - 3.3V)^*33mV)$$

$\ge 43\mu F (7)$

The LMZ14203 demonstration and evaluation boards are populated with a 100 uF 6.3V X5R output capacitor. Locations for extra output capacitors are provided.

#### **CIN SELECTION**

The LMZ14203 module contains an internal 0.47 µF input ceramic capacitor. Additional input capacitance is required ex-

ternal to the module to handle the input ripple current of the application. This input capacitance should be located in very close proximity to the module. Input capacitor selection is generally directed to satisfy the input ripple current requirements rather than by capacitance value. Worst case input ripple current rating is dictated by the equation:

$$I(C_{IN(RMS)}) \approx 1/2 * I_O * \sqrt{(D/1-D)}$$

(8)

where D  $\cong$  V<sub>O</sub> / V<sub>IN</sub>

(As a point of reference, the worst case ripple current will occur when the module is presented with full load current and when  $V_{\rm IN}=2$  \*  $V_{\rm O}$ ).

Recommended minimum input capacitance is 10uF X7R ceramic with a voltage rating at least 25% higher than the maximum applied input voltage for the application. It is also recommended that attention be paid to the voltage and temperature deratings of the capacitor selected. It should be noted that ripple current rating of ceramic capacitors may be missing from the capacitor data sheet and you may have to contact the capacitor manufacturer for this rating.

If the system design requires a certain minimum value of input ripple voltage  $\Delta V_{IN}$  be maintained then the following equation may be used.

$$C_{IN} \ge I_O * D * (1-D) / f_{SW-CCM} * \Delta V_{IN}$$

(9)

If  $\Delta V_{IN}$  is 1% of  $V_{IN}$  for a 24V input to 3.3V output application this equals 240 mV and  $f_{SW}=400$  kHz.

$$C_{IN} \ge 3A * 3.3V/24V * (1-3.3V/24V) / (400000 * 0.240 V)$$

$\ge 3.7 \mu F$

Additional bulk capacitance with higher ESR may be required to damp any resonant effects of the input capacitance and parasitic inductance of the incoming supply lines.

#### **RON RESISTOR SELECTION**

Many designs will begin with a desired switching frequency in mind. For that purpose the following equation can be used.

$$f_{SW(CCM)} \approx V_O / (1.3 * 10^{-10} * R_{ON})$$

(10)

This can be rearranged as

$$R_{ON} \approx V_O / (1.3 * 10^{-10} * f_{SW(CCM)})$$

(11)

The selection of RON and  $f_{SW(CCM)}$  must be confined by limitations in the on-time and off-time for the COT control section. The on-time of the LMZ14203 timer is determined by the resistor  $R_{ON}$  and the input voltage  $V_{IN}$ . It is calculated as follows:

$$t_{ON} = (1.3 * 10^{-10} * R_{ON}) / V_{IN}$$

(12)

The inverse relationship of  $t_{ON}$  and  $V_{IN}$  gives a nearly constant switching frequency as  $V_{IN}$  is varied.  $R_{ON}$  should be selected such that the on-time at maximum  $V_{IN}$  is greater than 150 ns. The on-timer has a limiter to ensure a minimum of 150 ns for  $t_{ON}$ . This limits the maximum operating frequency, which is governed by the following equation:

$$f_{SW(MAX)} = V_O / (V_{IN(MAX)} * 150 \text{ nsec})$$

(13)

This equation can be used to select  $R_{ON}$  if a certain operating frequency is desired so long as the minimum on-time of 150 ns is observed. The limit for  $R_{ON}$  can be calculated as follows:

$$R_{ON} \ge V_{IN(MAX)} * 150 \text{ nsec} / (1.3 * 10^{-10})$$

(14)

If  $R_{ON}$  calculated in (11) is less than the minimum value determined in (14) a lower frequency should be selected. Alternatively,  $V_{IN(MAX)}$  can also be limited in order to keep the frequency unchanged.

Additionally note, the minimum off-time of 260 ns limits the maximum duty ratio. Larger  $\rm R_{ON}$  (lower  $\rm F_{SW})$  should be selected in any application requiring large duty ratio.

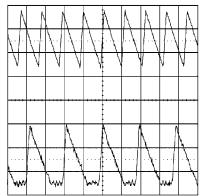

# **Discontinuous Conduction and Continuous Conduction Modes**

At light load the regulator will operate in discontinuous conduction mode (DCM). With load currents above the critical conduction point, it will operate in continuous conduction mode (CCM). When operating in DCM the switching cycle begins at zero amps inductor current; increases up to a peak value, and then recedes back to zero before the end of the off-time. Note that during the period of time that inductor current is zero, all load current is supplied by the output capacitor. The next on-time period starts when the voltage on the at the FB pin falls below the internal reference. The switching frequency is lower in DCM and varies more with load current as compared to CCM. Conversion efficiency in DCM is maintained since conduction and switching losses are reduced with the smaller load and lower switching frequency. Operating frequency in DCM can be calculated as follows:

f<sub>SW(DCM)</sub>≅V<sub>O</sub>\*(V<sub>IN</sub>-1)\*6.8µH\*1.18\*10<sup>20\*</sup>I<sub>O</sub>/(V<sub>IN</sub>-V<sub>O</sub>)\*R<sub>ON</sub><sup>2</sup> (15) In CCM, current flows through the inductor through the entire switching cycle and never falls to zero during the off-time. The switching frequency remains relatively constant with load current and line voltage variations. The CCM operating frequency can be calculated using equation 7 above.

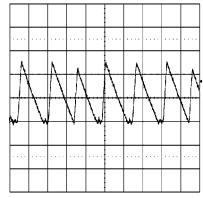

Following is a comparison pair of waveforms of the showing both CCM (upper) and DCM operating modes.

CCM and DCM Operating Modes  $\rm V_{IN} = 24V, \, V_O = 3.3V, \, I_O = 3A/0.4A \, 2 \, \mu sec/div$

30107012

The approximate formula for determining the DCM/CCM boundary is as follows:

$$I_{DCB} \cong V_O^*(V_{IN} - V_O)/(2*6.8 \ \mu H^* f_{SW(CCM)}^* V_{IN})$$

(16)

Following is a typical waveform showing the boundary condition.

Transition Mode Operation  $V_{IN}$  = 24V,  $V_O$  = 3.3V,  $I_O$  = 0.5 A 2  $\mu sec/div$

3010701

The inductor internal to the module is 6.8  $\mu$ H. This value was chosen as a good balance between low and high input voltage applications. The main parameter affected by the inductor is the amplitude of the inductor ripple current (I<sub>LR</sub>). I<sub>LR</sub> can be calculated with:

$$I_{LR P-P} = V_O^* (V_{IN} - V_O) / (6.8 \mu H^* f_{SW}^* V_{IN})$$

(17)

Where  $V_{\rm IN}$  is the maximum input voltage and  $f_{\rm SW}$  is determined from equation 10.

If the output current  $I_O$  is determined by assuming that  $I_O = I_L$ , the higher and lower peak of  $I_{LR}$  can be determined. Be aware that the lower peak of  $I_{LR}$  must be positive if CCM operation is required.

# POWER DISSIPATION AND BOARD THERMAL REQUIREMENTS

For the design case of  $V_{\rm IN}=24V,~V_{\rm O}=3.3V,~I_{\rm O}=3A,~T_{\rm AMB}$   $_{\rm (MAX)}=85^{\circ}{\rm C}$ , and  $T_{\rm JUNCTION}=125^{\circ}{\rm C}$ , the device must see a thermal resistance from case to ambient of:

$$\theta_{CA} < (T_{J-MAX} - T_{AMB(MAX)}) / P_{IC-LOSS} - \theta_{JC}$$

(18)

Given the typical thermal resistance from junction to case to be 1.9 °C/W. Use the 85°C power dissipation curves in the Typical Performance Characteristics section to estimate the  $P_{\rm IC-LOSS}$  for the application being designed. In this application it is 2.25W.

$$\theta_{CA} < (125 - 85) / 2.25W - 1.9 = 15.8$$

To reach  $\theta_{CA}$  = 15.8, the PCB is required to dissipate heat effectively. With no airflow and no external heat, a good estimate of the required board area covered by 1 oz. copper on both the top and bottom metal layers is:

Board Area\_cm<sup>2</sup> > 500°C x cm<sup>2</sup>/W /

$$\theta_{CA}$$

(19)

As a result, approximately 31.5 square cm of 1 oz copper on top and bottom layers is required for the PCB design. The PCB copper heat sink must be connected to the exposed pad. Approximately thirty six, 10mils (254  $\mu$ m) thermal vias spaced 59mils (1.5 mm) apart must connect the top copper to the bottom copper. For an example of a high thermal performance PCB layout, refer to the Evaluation Board application note AN-2024.

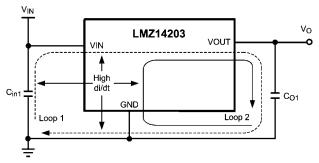

#### PC BOARD LAYOUT GUIDELINES

PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce and resistive voltage drop in the traces. These can send erroneous signals to the DC-DC converter resulting

in poor regulation or instability. Good layout can be implemented by following a few simple design rules.

#### 30107011

#### 1. Minimize area of switched current loops.

From an EMI reduction standpoint, it is imperative to minimize the high di/dt paths during PC board layout. The high current loops that do not overlap have high di/dt content that will cause observable high frequency noise on the output pin if the input capacitor (Cin1) is placed at a distance away from the LMZ14203. Therefore place  $C_{\rm IN1}$  as close as possible to the LMZ14203 VIN and GND exposed pad. This will minimize the high di/dt area and reduce radiated EMI. Additionally, grounding for both the input and output capacitor should consist of a localized top side plane that connects to the GND exposed pad (EP).

#### 2. Have a single point ground.

The ground connections for the feedback, soft-start, and enable components should be routed to the GND pin of the device. This prevents any switched or load currents from flowing in the analog ground traces. If not properly handled, poor grounding can result in degraded load regulation or erratic output voltage ripple behavior. Provide the single point ground connection from pin 4 to EP.

#### 3. Minimize trace length to the FB pin.

Both feedback resistors,  $R_{FBT}$  and  $R_{FBB}$ , and the feed forward capacitor  $C_{FF}$ , should be located close to the FB pin. Since the FB node is high impedance, maintain the copper area as small as possible. The trace are from  $R_{FBT}$ ,  $R_{FBB}$ , and  $C_{FF}$  should be routed away from the body of the LMZ14203 to minimize noise.

# 4. Make input and output bus connections as wide as possible.

This reduces any voltage drops on the input or output of the converter and maximizes efficiency. To optimize voltage accuracy at the load, ensure that a separate feedback voltage sense trace is made to the load. Doing so will correct for voltage drops and provide optimum output accuracy.

#### 5. Provide adequate device heat-sinking.

Use an array of heat-sinking vias to connect the exposed pad to the ground plane on the bottom PCB layer. If the PCB has a plurality of copper layers, these thermal vias can also be employed to make connection to inner layer heat-spreading ground planes. For best results use a 6 x 6 via array with minimum via diameter of 10mils (254  $\mu m$ ) thermal vias spaced 59mils (1.5 mm). Ensure enough copper area is used for heat-sinking to keep the junction temperature below 125°C.

#### **Additional Features**

#### **OUTPUT OVER-VOLTAGE COMPARATOR**

The voltage at FB is compared to a 0.92V internal reference. If FB rises above 0.92V the on-time is immediately terminated. This condition is known as over-voltage protection (OVP). It can occur if the input voltage is increased very suddenly or if the output load is decreased very suddenly. Once OVP is activated, the top MOSFET on-times will be inhibited until the condition clears. Additionally, the synchronous MOSFET will remain on until inductor current falls to zero.

#### **CURRENT LIMIT**

Current limit detection is carried out during the off-time by monitoring the current in the synchronous MOSFET. Referring to the Functional Block Diagram, when the top MOSFET is turned off, the inductor current flows through the load, the PGND pin and the internal synchronous MOSFET. If this current exceeds 4.2A (typical) the current limit comparator disables the start of the next on-time period. The next switching cycle will occur only if the FB input is less than 0.8V and the inductor current has decreased below 4.2A. Inductor current is monitored during the period of time the synchronous MOSFET is conducting. So long as inductor current exceeds 4.2A, further on-time intervals for the top MOSFET will not occur. Switching frequency is lower during current limit due to the longer off-time. It should also be noted that current limit is dependent on both duty cycle and temperature.

#### THERMAL PROTECTION

The junction temperature of the LMZ14203 should not be allowed to exceed its maximum ratings. Thermal protection is implemented by an internal Thermal Shutdown circuit which activates at 165 °C (typ) causing the device to enter a low power standby state. In this state the main MOSFET remains off causing  $\rm V_{\rm O}$  to fall, and additionally the CSS capacitor is discharged to ground. Thermal protection helps prevent catastrophic failures for accidental device overheating. When the junction temperature falls back below 145 °C (typ Hyst = 20 °C) the SS pin is released,  $\rm V_{\rm O}$  rises smoothly, and normal operation resumes.

Applications requiring maximum output current especially those at high input voltage may require application derating at elevated temperatures.

#### **ZERO COIL CURRENT DETECTION**

The current of the lower (synchronous) MOSFET is monitored by a zero coil current detection circuit which inhibits the synchronous MOSFET when its current reaches zero until the next on-time. This circuit enables the DCM operating mode, which improves efficiency at light loads.

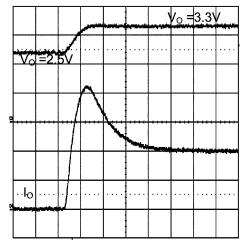

#### **PRE-BIASED STARTUP**

The LMZ14203 will properly start up into a pre-biased output. This startup situation is common in multiple rail logic applications where current paths may exist between different power rails during the startup sequence. The following scope capture shows proper behavior during this event.

#### **Pre-Biased Startup**

30107025

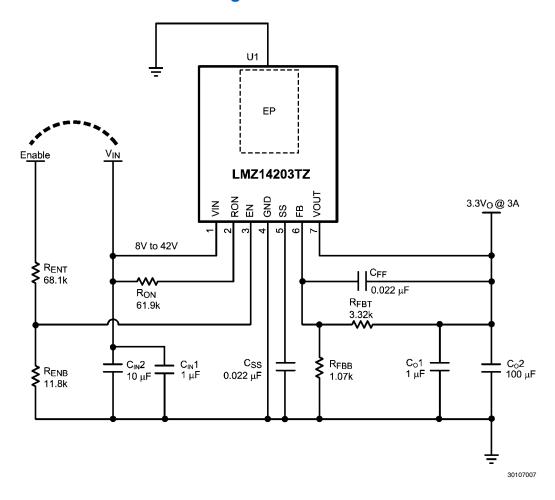

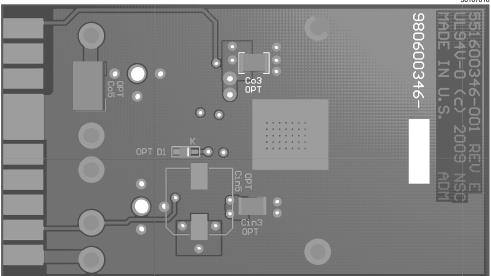

## **Evaluation Board Schematic Diagram**

| Ref Des          | Description           | Case Size | Case Size              | Manufacturer P/N |

|------------------|-----------------------|-----------|------------------------|------------------|

| U1               | SIMPLE SWITCHER ®     | TO-PMOD-7 | National Semiconductor | LMZ14203TZ       |

| C <sub>in1</sub> | 1 μF, 50V, X7R        | 1206      | Taiyo Yuden            | UMK316B7105KL-T  |

| C <sub>in2</sub> | 10 μF, 50V, X7R       | 1210      | Taiyo Yuden            | UMK325BJ106MM-T  |

| C <sub>O1</sub>  | 1 μF, 50V, X7R        | 1206      | Taiyo Yuden            | 'UMK316B7105KL-T |

| C <sub>O2</sub>  | 100 μF, 6.3V, X7R     | 1210      | Taiyo Yuden            | JMK325BJ107MM-T  |

| R <sub>FBT</sub> | 3.32 kΩ               | 0603      | Vishay Dale            | CRCW06033K32FKEA |

| R <sub>FBB</sub> | 1.07 kΩ               | 0603      | Vishay Dale            | CRCW06031K07FKEA |

| R <sub>ON</sub>  | 61.9 kΩ               | 0603      | Vishay Dale            | CRCW060361k9FKEA |

| R <sub>ENT</sub> | 68.1 kΩ               | 0603      | Vishay Dale            | CRCW060368k1FKEA |

| R <sub>ENB</sub> | 11.8 kΩ               | 0603      | Vishay Dale            | CRCW060311k8FKEA |

| C <sub>FF</sub>  | 22 nF, ±10%, X7R, 16V | 0603      | TDK                    | C1608X7R1H223K   |

| C <sub>SS</sub>  | 22 nF, ±10%, X7R, 16V | 0603      | TDK                    | C1608X7R1H223K   |

30107017

## Physical Dimensions inches (millimeters) unless otherwise noted

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pro                            | oducts                       | Design Support               |                                |  |

|--------------------------------|------------------------------|------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools               | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                    | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs            | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                      | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                  | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                    | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance             | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                 | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability      | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support             | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy             | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                     | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                  | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com