# **DATA SHEET**

| Part No.         | AN26260A       |  |  |

|------------------|----------------|--|--|

| Package Code No. | ULGA054-W-5234 |  |  |

# Contents

| ■ Overview                       | 3 |

|----------------------------------|---|

| ■ Features                       | 3 |

| ■ Applications                   | 3 |

| ■ Package                        | 3 |

| ■ Type                           | 3 |

| ■ Application Circuit Example    | 4 |

| ■ Test Circuit Diagram           | 5 |

| ■ Pin Out                        |   |

| ■ Pin Descriptions               | 7 |

| ■ Absolute Maximum Ratings       | 9 |

| ■ Operating Supply Voltage Range | 9 |

# AN26260A

# Receive RF IC for WCDMA (Dual Band)

#### Overview

- AN26260A is WCDMA receive RFIC that is planned to use for dual band WCDMA in Japan.

AN26260A is consisted of RF amplifiers (i.e. LNA2), direct conversion demodulators, VCOs, synthesizer and baseband path.

There is able to build the WCDMA receive RF block with external LNA and RF-filter.

- This IC is expecting to use with the WCDMA transmit RFIC; AN26261A.

#### ■ Features

- Direct conversion receive RFIC for dual band WCDMA with the on-chip VCOs.

- Receive frequencies: 2 110 MHz to 2 170 MHz, 875 MHz to 900 MHz.

- Current consumption: 29.9 mA(typ.)-2 GHz mode, 28.8 mA(typ.)-800 MHz mode.

#### Applications

• WCDMA single, dual band terminals.

#### Package

• Wafer level chip size package (WLCSP). Size: 3.37 × 5.17 × 0.8 mm<sup>3</sup>

#### ■ Type

• SiGe monolithic Bi-CMOS IC.

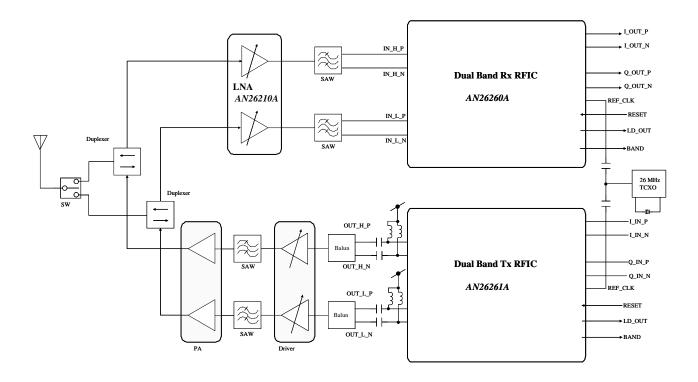

# ■ Application Circuit Example

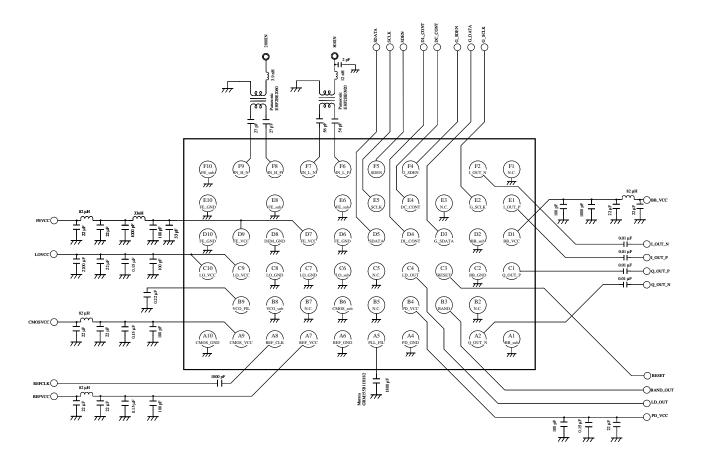

## ■ Test Circuit Diagram (Top View)

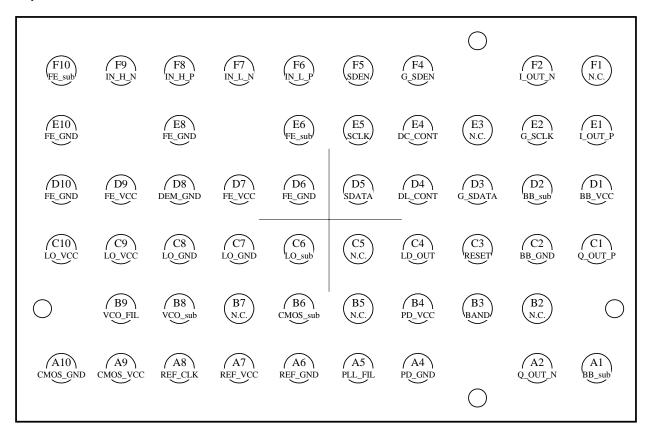

### ■ Pin Out

The figure below shows pin layout is 'top view'.

Top view

# ■ Pin Descriptions

| Pin No. | Pin name | Туре   | Description                        |  |  |  |

|---------|----------|--------|------------------------------------|--|--|--|

| A1      | BB_sub   | Ground | Baseband substrate                 |  |  |  |

| A2      | Q_OUT_N  | Out    | channel baseband negative output   |  |  |  |

| A3      | _        | _      | No pin                             |  |  |  |

| A4      | PD_GND   | Ground | Phase detector ground              |  |  |  |

| A5      | PLL_FIL  | InOut  | PLL loop filter                    |  |  |  |

| A6      | REF_GND  | Ground | Reference clock amplifier ground   |  |  |  |

| A7      | REF_VCC  | Supply | Reference clock amplifier supply   |  |  |  |

| A8      | REF_CLK  | In     | Reference clock input              |  |  |  |

| A9      | CMOS_VCC | Supply | CMOS logic supply                  |  |  |  |

| A10     | CMOS_GND | Ground | CMOS logic ground                  |  |  |  |

| B1      | _        | _      | No pin                             |  |  |  |

| B2      | N.C.     | _      | No connection or ground            |  |  |  |

| В3      | BAND     | Out    | Band selector output               |  |  |  |

| B4      | PD_VCC   | Supply | Phase detector supply              |  |  |  |

| В5      | N.C.     | _      | No connection or ground            |  |  |  |

| В6      | CMOS_sub | Ground | CMOS logic substrate               |  |  |  |

| В7      | N.C.     | _      | No connection or ground            |  |  |  |

| В8      | VCO_sub  | Ground | VCO substrate                      |  |  |  |

| В9      | VCO_FIL  | InOut  | VCO ripple filter                  |  |  |  |

| B10     | _        | _      | No pin                             |  |  |  |

| C1      | Q_OUT_P  | Out    | Q channel baseband positive output |  |  |  |

| C2      | BB_GND   | Ground | Baseband ground                    |  |  |  |

| СЗ      | RESET    | In     | Reset signal input                 |  |  |  |

| C4      | LD_OUT   | Out    | Synthesizer lock detector output   |  |  |  |

| C5      | N.C.     | _      | No connection or ground            |  |  |  |

| C6      | LO_sub   | Ground | Local substrate                    |  |  |  |

| C7      | LO_GND   | Ground | Local ground                       |  |  |  |

| C8      | LO_GND   | Ground | Local ground                       |  |  |  |

| C9      | LO_VCC   | Supply | Local supply                       |  |  |  |

| C10     | LO_VCC   | Supply | Local supply                       |  |  |  |

# ■ Pin Descriptions (continued)

| Pin No. | Pin name | Type   | Description                          |  |  |  |

|---------|----------|--------|--------------------------------------|--|--|--|

| D1      | BB_VCC   | Supply | Baseband supply                      |  |  |  |

| D2      | BB_sub   | Ground | Baseband substrate                   |  |  |  |

| D3      | G_SDATA  | In     | erial data input for gain control    |  |  |  |

| D4      | DL_CONT  | In     | synthesizer double latch switch      |  |  |  |

| D5      | SDATA    | In     | Serial data input                    |  |  |  |

| D6      | FE_GND   | Ground | Front-end ground                     |  |  |  |

| D7      | FE_VCC   | Supply | Front-end supply                     |  |  |  |

| D8      | DEM_GND  | Ground | Demodulator ground                   |  |  |  |

| D9      | FE_VCC   | Supply | Front-end supply                     |  |  |  |

| D10     | FE_GND   | Ground | Front-end ground                     |  |  |  |

| E1      | I_OUT_P  | Out    | I channel baseband positive output   |  |  |  |

| E2      | G_SCLK   | In     | Serial clock input for gain control  |  |  |  |

| E3      | N.C.     | _      | No connection or ground              |  |  |  |

| E4      | DC_CONT  | Out    | DC offset removal detector output    |  |  |  |

| E5      | SCLK     | In     | Serial clock input                   |  |  |  |

| E6      | FE_sub   | Ground | Front-end substrate                  |  |  |  |

| E7      | _        | _      | No pin                               |  |  |  |

| E8      | FE_GND   | Ground | Front-end Ground                     |  |  |  |

| E9      | _        | _      | No pin                               |  |  |  |

| E10     | FE_GND   | Ground | Front-end Ground                     |  |  |  |

| F1      | N.C.     | _      | No connection or ground              |  |  |  |

| F2      | I_OUT_N  | Out    | I channel baseband negative output   |  |  |  |

| F3      | _        | _      | No pin                               |  |  |  |

| F4      | G_SDEN   | In     | Serial enable input for gain control |  |  |  |

| F5      | SDEN     | In     | Serial enable                        |  |  |  |

| F6      | IN_L_P   | In     | 800 MHz band positive input          |  |  |  |

| F7      | IN_L_N   | In     | 800 MHz band negative input          |  |  |  |

| F8      | IN_H_P   | In     | 2 GHz band positive input            |  |  |  |

| F9      | IN_H_N   | In     | 2 GHz band negative input            |  |  |  |

| F10     | FE_sub   | Ground | Front-end substrate                  |  |  |  |

### ■ Absolute Maximum Ratings

| A<br>No. | Parameter                     | Symbol           | Rating                                | Unit | Notes  |

|----------|-------------------------------|------------------|---------------------------------------|------|--------|

| 1        | Supply voltage                | V <sub>CC</sub>  | 0 to 3.6                              | V    | *1     |

| 2        | Supply current                | $I_{CC}$         | 40                                    | mA   | _      |

| 3        | Power dissipation             | $P_{\mathrm{D}}$ | 69.3                                  | mW   | *2     |

| 4        | Operating ambient temperature | $T_{opr}$        | −25 to +85                            | °C   | *3     |

| 5        | Storage temperature           | T <sub>stg</sub> | -55 to +125                           | °C   | *3     |

| 6        | DC input voltage              | VI               | 0 to $V_{CC}$ + 0.3 and less than 3.6 | V    | *1, *4 |

Notes) \*1: The supply voltage is shown the value under the condition which not exceeds the absolute maximum ratings and the power dissipation.

## ■ Operating supply voltage range

| Parameter            | Symbol          | Range      | Unit | Notes |

|----------------------|-----------------|------------|------|-------|

| Supply voltage range | V <sub>CC</sub> | 2.7 to 3.0 | V    | _     |

<sup>\*2 :</sup> The power dissipation is shown the value at  $T_a = 85^{\circ}$ C for the independent (non-mounted) IC package without a heat sink. In case of use this IC, please refer to the  $P_D$ - $T_a$  diagram of the package standard and use under the condition not exceeding the allowable value.

<sup>\*3</sup>: Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for  $T_a = 25$  °C.

<sup>\*4:</sup> Tolerable input voltages of logical input SCLK, SDATA, SDEN, G-SCLK, G-SDATA, G-SDEN, RESET, DL-CONT pins

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd. Industrial Co., Ltd.