## AN2546FH-A

## Automotive LCD TV signal processor IC

#### Overview

The AN2546FH-A is a video signal processing IC built-in a 5-volt power-supply source driver for TFT color LCD (normally white type), and it supports the NTSC, PAL and PAL-M/PAL-N systems. The main circuitry of this IC includes video-signal processing circuit, color signal processing circuit, interface circuit, synchronizing circuit and many color quality adjusting circuits. This IC converts the composite video signal or separated Y/C signal or RGB signals into RGB signals available for TFT color LCD.

#### ■ Features

- Supply voltage: 3 V/5 V/7.5 V

- Built-in a 5-volt power-supply source driver for TFT type LCD

- Low consumption power (typ. 200 mW)

- Supporting the NTSC, PAL, PAL-M and PAL-N systems

- Supporting composite, component and color differential signal input

- Video signal, analog RGB (2 systems) One is for OSD (analog/digital).

- Each mode setting is possible with I<sup>2</sup>C Bus control.

- Electronic volume (D/A converter) built in

- Contrast/Brightness/y correction circuit built in

- Horizontal and vertical display position adjustment are possible by serial control.

- Improvement of weak electric field characteristics (Compared to AN2526FH/AN2526NFH: -5 dB)

- At reverse stop, built-in output gain down function

#### Applications

4 inches to 7 inches middle size TFT LCD equipment of normally white, of such as an in-car TV and an LCD monitor for car navigation system.

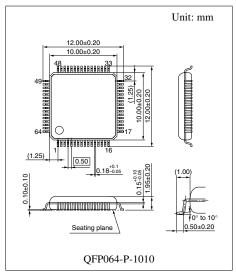

Note) The package of this product will be changed to lead-free type (QFP064-P-1010A). See the new package dimensions section later of this datasheet.

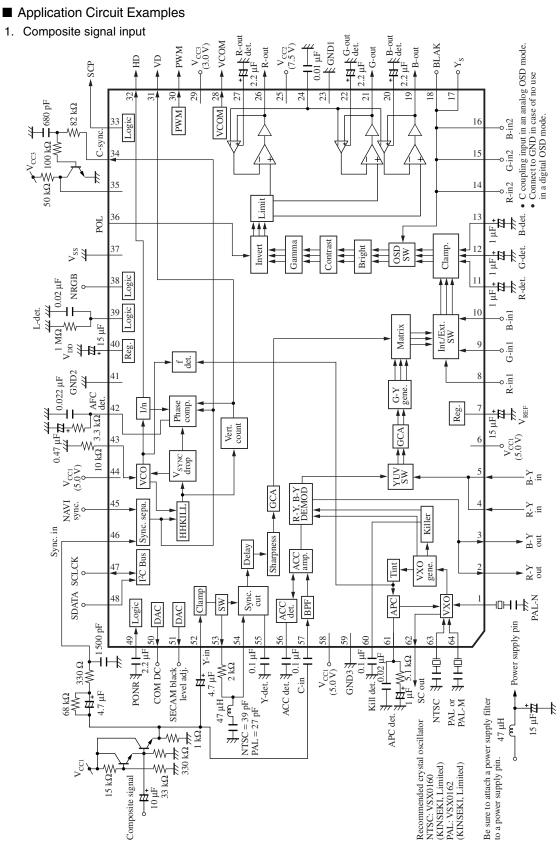

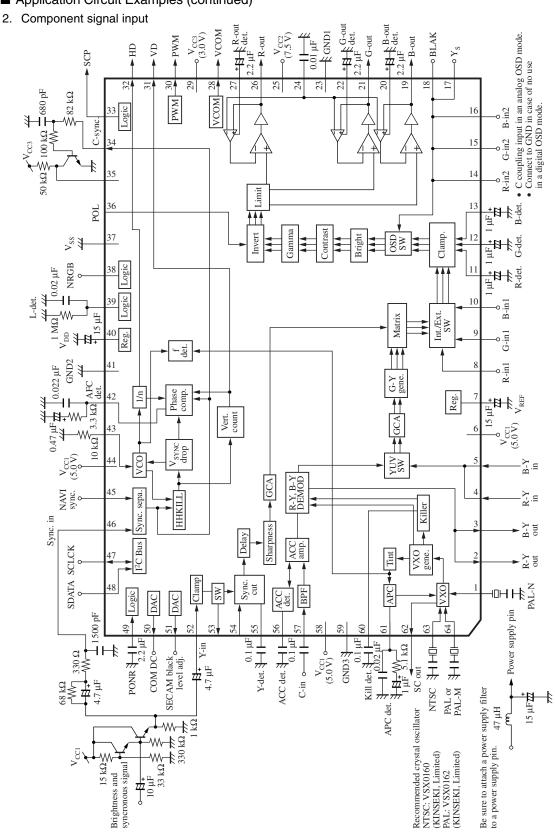

### ■ Application Circuit Examples (continued)

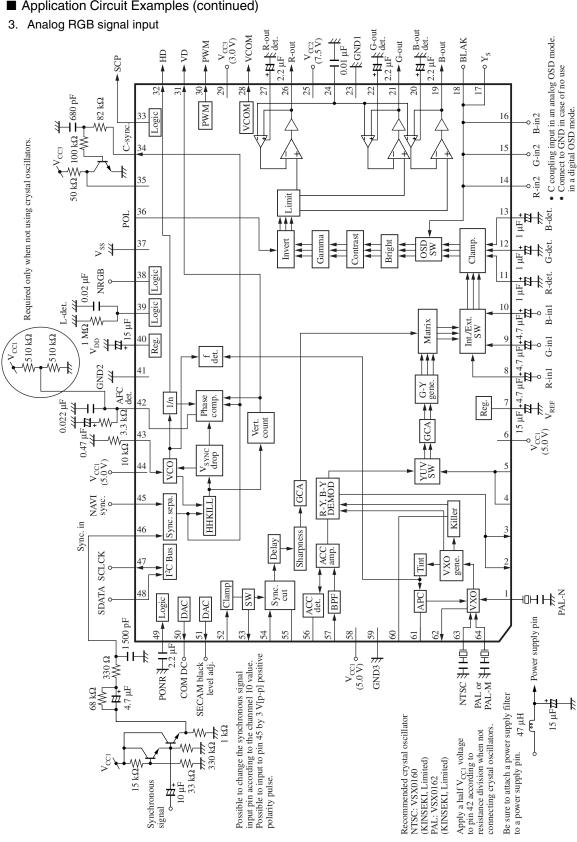

### ■ Application Circuit Examples (continued)

## Panasonic AN2546FH-A

### ■ Pin Descriptions

| Pin No. | Description                                             | Pin No. | Description                                     |

|---------|---------------------------------------------------------|---------|-------------------------------------------------|

| 1       | Crystal oscillator connecting pin 3 (PAL-N)             | 33      | Sand castle pulse output pin                    |

| 2       | R-Y output pin                                          | 34      | Composite synchronous signal output pin         |

| 3       | B-Y output pin                                          | 35      | Vertical synchronous signal input pin           |

| 4       | R-Y input pin                                           | 36      | 1H reverse signal input pin                     |

| 5       | B-Y input pin                                           | 37      | Clock-system GND (V <sub>SS</sub> )             |

| 6       | Signal processing system power supply                   | 38      | Analog imposing control signal input pin        |

|         | $(V_{CC1} = 5.0 \text{ V})$                             | 39      | Horizontal clock detection pin                  |

| 7       | Internal reference power supply detection               | 40      | Clock-system power supply (3.0 V)               |

|         | pin (2.0 V)                                             | 41      | GND 2                                           |

| 8       | R-ch. analog signal input pin                           | 42      | AFC loop filter connecting pin                  |

| 9       | G-ch. analog signal input pin                           | 43      | VCO frequency adjustment pin                    |

| 10      | B-ch. analog signal input pin                           | 44      | Synchronous system power supply                 |

| 11      | R-ch. clamp detection pin                               |         | $(V_{CC1} = 5.0 \text{ V})$                     |

| 12      | G-ch. clamp detection pin                               | 45      | NAVI signal synchronous signal input pin        |

| 13      | B-ch. clamp detection pin                               | 46      | Synchronous signal input pin                    |

| 14      | R-ch. OSD input pin                                     | 47      | Serial data shift clock input pin               |

| 15      | G-ch. OSD input pin                                     | 48      | Serial data input pin                           |

| 16      | B-ch. OSD input pin                                     | 49      | Power-on reset detection pin                    |

| 17      | Character picking up pulse input pin                    | 50      | Common DC adjustment voltage output pin         |

| 18      | Side black control signal input pin                     | 51      | DAC output pin                                  |

| 19      | B-ch. output pin                                        | 52      | Luminance signal input pin                      |

| 20      | B-ch. output DC feedback detection pin                  | 53      | Chrominance signal trap filter connection pin 1 |

| 21      | G-ch. output pin                                        | 54      | Chrominance signal trap filter connection pin 2 |

| 22      | G-ch. output DC feedback detection pin                  | 55      | Y-system clamp detection pin                    |

| 23      | GND 1                                                   | 56      | ACC detection pin                               |

| 24      | Drive output reference voltage input pin                | 57      | Chrominance signal input pin                    |

| 25      | Drive system power supply ( $V_{CC2} = 7.5 \text{ V}$ ) | 58      | Chrominance processing system power supply      |

| 26      | R-ch. output pin                                        |         | $(V_{CC1} = 5.0 \text{ V})$                     |

| 27      | R-ch. output DC feedback detection pin                  | 59      | GND 3                                           |

| 28      | Common reverse signal output pin                        | 60      | Chrominance killer detection pin                |

| 29      | Pulse output system power supply                        | 61      | APC detection pin                               |

|         | $(V_{CC3} = 3.0 \text{ V})$                             | 62      | Subcarrier output pin                           |

| 30      | PWM output pin                                          | 63      | Crystal oscillator connecting pin 1 (NTSC)      |

| 31      | Vertical synchronous signal output pin                  | 64      | Crystal oscillator connecting pin 2             |

| 32      | Horizontal synchronous signal output pin                |         | (PAL/PAL-M)                                     |

**Panasonic**

### ■ Absolute Maximum Ratings

| Parameter                        | Symbol             | Rating      | Unit |

|----------------------------------|--------------------|-------------|------|

| Supply voltage                   | V <sub>CC1</sub>   | 5.5         | V    |

|                                  | V <sub>CC2</sub>   | 8.5         |      |

|                                  | V <sub>CC3</sub>   | 5.2         |      |

| Supply current                   | $I_{CC}$           | _           | mA   |

| Power dissipation *2             | $P_{\mathrm{D}}$   | 423         | mW   |

| Operating ambient temperature *1 | $T_{\mathrm{opr}}$ | -30 to +85  | °C   |

| Storage temperature *1           | T <sub>stg</sub>   | -55 to +150 | °C   |

Note) \*1: Except for the operating ambient temperature and storage temperature, all ratings are for  $T_a = 25$ °C.

### ■ Recommended Operating Range

| Parameter      | Symbol           | Range      | Unit |

|----------------|------------------|------------|------|

| Supply voltage | V <sub>CC1</sub> | 4.7 to 5.3 | V    |

|                | $V_{CC2}$        | 7.0 to 8.0 |      |

|                | V <sub>CC3</sub> | 2.7 to 3.3 |      |

## $\blacksquare$ Electrical Characteristics at $T_a=25^{\circ}C$

| Parameter                                    | Parameter Symbol Conditions |                            | Min  | Тур | Max  | Unit    |

|----------------------------------------------|-----------------------------|----------------------------|------|-----|------|---------|

| DC                                           |                             |                            |      |     |      |         |

| V <sub>CC1</sub> -system current consumption | I <sub>TOTAL1</sub>         | Refer to product standards | 32   | _   | 44   | mA      |

| V <sub>CC2</sub> -system current consumption | I <sub>TOTAL2</sub>         | Refer to product standards | 1.0  | _   | 9.0  | mA      |

| V <sub>CC3</sub> -system current consumption | I <sub>TOTAL3</sub>         | Refer to product standards | _    | _   | 2.0  | mA      |

| Chrominance system                           |                             |                            |      |     |      |         |

| R-Y standard gain                            | $G_{RY}$                    | Refer to product standards | 9.0  | _   | 15   | dB      |

| R-Y/G-Y relative gain                        | $G_{RYGY}$                  | Refer to product standards | -5.0 | _   | -1.0 | dB      |

| B-Y standard gain                            | $G_{BY}$                    | Refer to product standards | 9.0  | _   | 15   | dB      |

| B-Y/G-Y relative gain                        | $G_{BYGY}$                  | Refer to product standards | -15  | _   | -9.0 | dB      |

| High-level APC pull-in                       | AP <sub>H</sub>             | Refer to product standards | 500  | _   | 540  | Hz      |

| Low-level APC pull-in                        | $AP_L$                      | Refer to product standards | -540 | _   | -500 | Hz      |

| ACC output characteristic 1                  | G <sub>ACC1</sub>           | Refer to product standards | -1.0 | _   | 1.0  | dB      |

| ACC output characteristic 2                  | G <sub>ACC2</sub>           | Refer to product standards | -1.0 | _   | 1.0  | dB      |

| Chrominance killer characteristic 1          | V <sub>KILL1</sub>          | Refer to product standards | 400  | _   | _    | mV[p-p] |

| Chrominance killer characteristic 2          | V <sub>KILL2</sub>          | Refer to product standards | -    | _   | 600  | mV[p-p] |

| Subcarrier amplitude                         | SCV                         | Refer to product standards | 400  | _   | _    | mV[p-p] |

| Y-system                                     |                             |                            |      |     |      |         |

| Sharpness control characteristic             | $G_{SH}$                    | Refer to product standards | 1.0  | _   | _    | dB      |

| Sharpness frequency characteristic 1         | f <sub>SH1</sub>            | Refer to product standards | 4.0  | _   | _    | dB      |

| R-ch. contrast adjustment range 1            | CTR <sub>R1</sub>           | Refer to product standards | 1.5  | _   | _    | dB      |

<sup>\*2:</sup> The power dissipation shown is the value in free air for  $T_{opr} = 85^{\circ}C$ .

# Panasonic AN2546FH-A

## $\blacksquare$ Electrical Characteristics at $T_a = 25^{\circ} C$ (continued)

| Parameter                         | Symbol               | Conditions                 | Min  | Тур | Max  | Unit   |

|-----------------------------------|----------------------|----------------------------|------|-----|------|--------|

| Y-system (continued)              |                      |                            |      |     |      |        |

| G-ch. contrast adjustment range 1 | CTR <sub>G1</sub>    | Refer to product standards | 1.5  | _   | _    | dB     |

| B-ch. contrast adjustment range 1 | CTR <sub>B1</sub>    | Refer to product standards | 1.5  | _   | _    | dB     |

| R-ch. contrast adjustment range 2 | CTR <sub>R2</sub>    | Refer to product standards | _    | _   | -2.5 | dB     |

| G-ch. contrast adjustment range 2 | CTR <sub>G2</sub>    | Refer to product standards | _    | _   | -2.5 | dB     |

| B-ch. contrast adjustment range 2 | CTR <sub>B2</sub>    | Refer to product standards | _    | _   | -2.5 | dB     |

| R-ch. pedestal amplitude minimum  | V <sub>PEDRmin</sub> | Refer to product standards | _    | _   | 2.0  | V[p-p] |

| G-ch. pedestal amplitude minimum  | V <sub>PEDGmin</sub> | Refer to product standards | _    | _   | 2.0  | V[p-p] |

| B-ch. pedestal amplitude minimum  | V <sub>PEDBmin</sub> | Refer to product standards | _    | _   | 2.0  | V[p-p] |

| R-ch. pedestal amplitude maximum  | V <sub>PEDRmax</sub> | Refer to product standards | 3.0  | _   | _    | V[p-p] |

| G-ch. pedestal amplitude maximum  | V <sub>PEDGmax</sub> | Refer to product standards | 3.0  | _   | _    | V[p-p] |

| B-ch. pedestal amplitude maximum  | V <sub>PEDBmax</sub> | Refer to product standards | 3.0  | _   | _    | V[p-p] |

| G-ch. output DC voltage           | $V_{GDC}$            | Refer to product standards | 2.35 | _   | 2.85 | V[p-p] |

| R-ch. gamma characteristic 1      | G <sub>GAMR1</sub>   | Refer to product standards | -9.0 | _   | -3.0 | dB     |

| G-ch. gamma characteristic 1      | G <sub>GAMG1</sub>   | Refer to product standards | -9.0 | _   | -3.0 | dB     |

| B-ch. gamma characteristic 1      | G <sub>GAMB1</sub>   | Refer to product standards | -9.0 | _   | -3.0 | dB     |

| R-ch. gamma characteristic 2      | G <sub>GAMR2</sub>   | Refer to product standards | -8.0 | _   | _    | dB     |

| G-ch. gamma characteristic 2      | $G_{GAMG2}$          | Refer to product standards | -8.0 | _   | _    | dB     |

| B-ch. gamma characteristic 2      | G <sub>GAMB2</sub>   | Refer to product standards | -8.0 | _   | _    | dB     |

| R-ch. gamma characteristic 3      | G <sub>GAMR3</sub>   | Refer to product standards | -5.0 | _   | 0    | dB     |

| G-ch. gamma characteristic 3      | G <sub>GAMG3</sub>   | Refer to product standards | -5.0 | _   | 0    | dB     |

| B-ch. gamma characteristic 3      | G <sub>GAMB3</sub>   | Refer to product standards | -5.0 | _   | 0    | dB     |

| R-ch. white limiter high-level    | V <sub>WRRH</sub>    | Refer to product standards |      | _   | 3.0  | V[p-p] |

| G-ch. white limiter high-level    | V <sub>WRGH</sub>    | Refer to product standards | _    | _   | 3.0  | V[p-p] |

| B-ch. white limiter high-level    | V <sub>WRBH</sub>    | Refer to product standards | _    | _   | 3.0  | V[p-p] |

| R-ch. white limiter low-level     | V <sub>WRRL</sub>    | Refer to product standards | 3.2  | _   | _    | V[p-p] |

| G-ch. white limiter low-level     | V <sub>WRGL</sub>    | Refer to product standards | 3.2  | _   | _    | V[p-p] |

| B-ch. white limiter low-level     | V <sub>WRBL</sub>    | Refer to product standards | 3.2  | _   | _    | V[p-p] |

| R-ch. black limiter low-level     | V <sub>BRRL</sub>    | Refer to product standards | 3.0  | _   | _    | V      |

| G-ch. black limiter low-level     | V <sub>BRGL</sub>    | Refer to product standards | 3.0  | _   | _    | V      |

| B-ch. black limiter low-level     | V <sub>BRBL</sub>    | Refer to product standards | 3.0  | _   | _    | V      |

| R-ch. black limiter high-level    | V <sub>BRRH</sub>    | Refer to product standards |      | _   | 2.7  | V      |

| G-ch. black limiter high-level    | V <sub>BRGH</sub>    | Refer to product standards | _    | _   | 2.7  | V      |

| B-ch. black limiter high-level    | V <sub>BRBH</sub>    | Refer to product standards |      | _   | 2.7  | V      |

| R-ch. Y <sub>S</sub> threshold 1  | V <sub>tYSR1</sub>   | Refer to product standards | 0.8  |     | _    | V[p-p] |

| G-ch. Y <sub>S</sub> threshold 1  | V <sub>tYSG1</sub>   | Refer to product standards | 0.8  | _   |      | V[p-p] |

| B-ch. Y <sub>S</sub> threshold 1  | V <sub>tYSB1</sub>   | Refer to product standards | 0.8  | _   |      | V[p-p] |

## $\blacksquare$ Electrical Characteristics at $T_a = 25^{\circ}C$ (continued)

|                                              |                    | · ·                        |        |     |      |        |

|----------------------------------------------|--------------------|----------------------------|--------|-----|------|--------|

| Parameter                                    | Symbol             | Conditions                 | Min    | Тур | Max  | Unit   |

| Y-system (continued)                         |                    |                            |        |     |      | •      |

| R-ch. Y <sub>S</sub> threshold 2             | V <sub>tYSR2</sub> | Refer to product standards | _      | _   | 0.5  | V[p-p] |

| G-ch. Y <sub>S</sub> threshold 2             | V <sub>tYSG2</sub> | Refer to product standards | _      | _   | 0.5  | V[p-p] |

| B-ch. Y <sub>S</sub> threshold 2             | V <sub>tYSB2</sub> | Refer to product standards | _      | _   | 0.5  | V[p-p] |

| R-ch. black level                            | CHR <sub>RB</sub>  | Refer to product standards | -1.0   | _   | 1.0  | V      |

| G-ch. black level                            | CHR <sub>GB</sub>  | Refer to product standards | -1.0   | _   | 1.0  | V      |

| B-ch. black level                            | CHR <sub>BB</sub>  | Refer to product standards | -1.0   | _   | 1.0  | V      |

| R-ch. black level width                      | WCHR <sub>RB</sub> | Refer to product standards | 2.0    | _   | 4.0  | μs     |

| G-ch. black level width                      | WCHR <sub>GB</sub> | Refer to product standards | 2.0    | _   | 4.0  | μs     |

| B-ch. black level width                      | WCHR <sub>BB</sub> | Refer to product standards | 2.0    | _   | 4.0  | μs     |

| R-ch. CHR threshold 1                        | V <sub>tCHR1</sub> | Refer to product standards | 1.5    | _   | _    | V[p-p] |

| G-ch. CHR threshold 1                        | V <sub>tCHG1</sub> | Refer to product standards | 1.5    | _   | _    | V[p-p] |

| B-ch. CHR threshold 1                        | V <sub>tCHB1</sub> | Refer to product standards | 1.5    | _   | _    | V[p-p] |

| R-ch. CHR threshold 2                        | V <sub>tCHR2</sub> | Refer to product standards | 3.0    | _   | _    | V[p-p] |

| G-ch. CHR threshold 2                        | V <sub>tCHG2</sub> | Refer to product standards | 3.0    | _   | _    | V[p-p] |

| B-ch. CHR threshold 2                        | V <sub>tCHB2</sub> | Refer to product standards | 3.0    | _   | _    | V[p-p] |

| R-ch. white level                            | CHR <sub>RW</sub>  | Refer to product standards | 2.0    | _   | _    | V[p-p] |

| G-ch. white level                            | CHR <sub>GW</sub>  | Refer to product standards | 2.0    | _   | _    | V[p-p] |

| B-ch. white level                            | CHR <sub>BW</sub>  | Refer to product standards | 2.0    | _   | _    | V[p-p] |

| R-ch. white level width                      | WCHR <sub>RW</sub> | Refer to product standards | 2.0    | _   | 4.0  | μs     |

| G-ch. white level width                      | WCHR <sub>GW</sub> | Refer to product standards | 2.0    | _   | 4.0  | μs     |

| B-ch. white level width                      | WCHR <sub>BW</sub> | Refer to product standards | 2.0    | _   | 4.0  | μs     |

| R-ch. RGB2 relative amplitude                | V <sub>RGB2R</sub> | Refer to product standards | - 0.45 | _   | 0.45 | V[p-p] |

| B-ch. RGB2 relative amplitude                | V <sub>RGB2B</sub> | Refer to product standards | - 0.45 | _   | 0.45 | V[p-p] |

| Synchronous system                           |                    |                            |        |     |      |        |

| Horizontal sync. pulse low-level             | V <sub>HDL</sub>   | Refer to product standards | _      | _   | 0.4  | V      |

| Horizontal sync. pulse amplitude             | $V_{HD}$           | Refer to product standards | 2.4    | _   | _    | V[p-p] |

| Horizontal sync. pulse width                 | t <sub>HD</sub>    | Refer to product standards | 3.6    | _   | 6.0  | μs     |

| Vertical sync. pulse low-level               | V <sub>VDL</sub>   | Refer to product standards | _      | _   | 0.4  | V      |

| Vertical sync. pulse amplitude               | V <sub>VD</sub>    | Refer to product standards | 2.4    | _   | _    | V[p-p] |

| Horizontal sync. separation pulse high-level | V <sub>HSSH</sub>  | SG2 (NTSC)                 | 2.4    | _   | _    | V      |

| Horizontal sync. separation pulse amplitude  | V <sub>HSS</sub>   | SG2 (NTSC)                 | 2.4    | _   | _    | V[p-p] |

| Horizontal sync. separation pulse width      | t <sub>HSS</sub>   | SG2 (NTSC)                 | 3.6    | _   | 6.0  | μs     |

## **Panasonic**

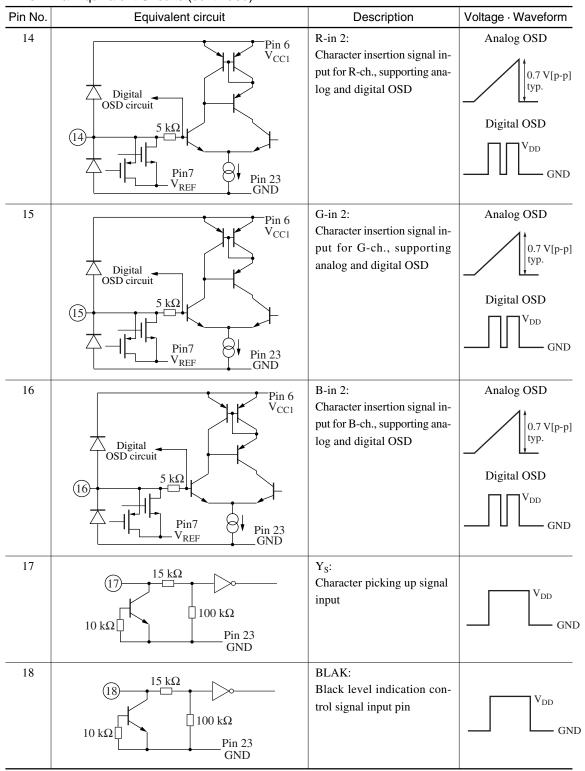

## ■ Terminal Equivalent Circuits

| Pin No. | Equivalent circuit                                                                                                                                           | Description                                                                                                                                   | Voltage · Waveform |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1       | Pin 58 $V_{CC1}$ $190 \Omega$ $1 k\Omega$ Pin 59 GND                                                                                                         | VXO3: PAL-N crystal oscillator connecting pin Use the capacitor with temperature characteristics (N750) to connect to the crystal oscillator. | _                  |

| 2       | $\begin{array}{c c} \text{Pin } 58 \\ \text{V}_{\text{CC1}} & 2 \text{ k}\Omega \end{array}$ $\begin{array}{c c} \text{Pin } 59 \\ \text{GND} & \end{array}$ | R-Y out:<br>Output pin of R-Y signal de-<br>modulated from video signal                                                                       | R-Y signal         |

| 3       | $\begin{array}{c c} Pin 58 \\ V_{CC1} \\ \hline \\ 2 \text{ k}\Omega \\ \hline \\ Pin 59 \\ GND \\ \end{array}$                                              | B-Y out:<br>Output pin of B-Y signal de-<br>modulated from video signal                                                                       | B-Y signal         |

| 4       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                        | R-Y in: R-Y signal input pin in a color difference mode and in the standard PAL                                                               | R-Y signal         |

| Pin No. | Equivalent circuit                                                                                                                                                                         | Description                                                                     | Voltage · Waveform               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------|

| 5       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                      | B-Y in: B-Y signal input pin in a color difference mode and in the standard PAL | B-Y signal                       |

| 6       |                                                                                                                                                                                            | V <sub>CC1</sub> : Drive block 5.0 V-system power supply pin                    | _                                |

| 7       | $\begin{array}{c c} & \text{Pin 6} \\ & \text{V}_{\text{CC1}} \\ \hline \end{array}$                                                                                                       | V <sub>REF</sub> : Reference voltage output pin 2.0 V typ.                      | _                                |

| 8       | $ \begin{array}{c c} & \text{Pin 6} \\ V_{\text{CC1}} \\ \hline & \text{Pin 7} \\ & \text{V}_{\text{REF}} \end{array} $ $ \begin{array}{c c} & \text{Pin 23} \\ & \text{GND} \end{array} $ | R-in 1:<br>Analog R signal input                                                | Analog R signal  0.7 V[p-p] typ. |

| 9       | $\begin{array}{c c} Pin \ 6 \\ V_{CC1} \\ \hline \\ Pin \ 7 \\ V_{REF} \\ \hline \end{array} \begin{array}{c} Pin \ 23 \\ GND \\ \end{array}$                                              | G-in 1:<br>Analog G signal input                                                | Analog G signal  0.7 V[p-p] typ. |

| Pin No. | Equivalent circuit                                                                                                                                                                    | Description                                       | Voltage · Waveform               |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------|

| 10      | $\begin{array}{c c} & \text{Pin 6} \\ V_{\text{CC1}} \\ \hline \\ & \text{Pin 7} \\ V_{\text{REF}} \\ \hline \end{array} \begin{array}{c} \text{Pin 23} \\ \text{GND} \\ \end{array}$ | B-in 1:<br>Analog B signal input                  | Analog B signal  0.7 V[p-p] typ. |

| 11      | $\begin{array}{c c} & \text{Pin 6} \\ \hline 1 \text{ k}\Omega & \text{I k}\Omega \\ \hline \end{array}$                                                                              | R-ch. det.: R-ch. clamping capacitor coupling pin |                                  |

| 12      | $\begin{array}{c c} & \text{Pin 6} \\ \hline 1 \text{ k}\Omega & \text{I k}\Omega \\ \hline \end{array}$                                                                              | G-ch. det.: G-ch. clamping capacitor coupling pin | _                                |

| 13      | $\begin{array}{c c} & \text{Pin 6} \\ \hline \\ 1 \text{ k}\Omega & 1 \text{ k}\Omega \\ \hline \\ & \text{Fin 23} \\ \text{GND} \\ \end{array}$                                      | B-ch. det.: B-ch. clamping capacitor coupling pin | _                                |

## **Panasonic**

| Pin No. | Equivalent circuit                                                                                                             | Description                                                  | Voltage · Waveform |

|---------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| 19      | $\begin{array}{c c} \text{Pin 6} \\ \text{V}_{\text{CC1}} & \text{Pin 25} \\ \text{V}_{\text{CC2}} \end{array}$                | B-out:<br>B signal output pin                                |                    |

| 20      | $\begin{array}{c c} & \text{Pin 6} \\ V_{CC1} \\ \hline \\ 20 \\ \hline \\ 2 \text{ k}\Omega \\ \hline \end{array}$            | B-ch. AVE det.: B-ch. output DC feedback detection pin       | _                  |

| 21      | $\begin{array}{c c} Pin 6 \\ V_{CC1} \\ \hline \\ 100 \Omega \\ \end{array} \begin{array}{c} Pin 25 \\ V_{CC2} \\ \end{array}$ | G-out:<br>G signal output pin                                |                    |

| 22      | $\begin{array}{c c} & \text{Pin 6} \\ V_{CC1} \\ \hline \\ 2 \text{k} \Omega \\ \hline \end{array}$                            | G-ch. AVE det.:<br>G-ch. output DC feedback<br>detection pin | _                  |

| 23      | _                                                                                                                              | GND 1:<br>Drive circuits system GND                          | _                  |

|         | Faultalent circuit (continued)                                                                                         | Description                                                                       | Voltage Moveform     |

|---------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|

| Pin No. | Equivalent circuit $\begin{array}{c} \text{Pin 6} \\ \text{V}_{\text{CC1}} \\ \text{Pin 23} \\ \text{GND} \end{array}$ | AVE: R,G,B output DC reference voltage pin                                        | Voltage · Waveform — |

| 25      | _                                                                                                                      | V <sub>CC2</sub> : 7.5 V system power supply                                      | _                    |

| 26      | $\begin{array}{c c} Pin \ 6 \\ V_{CC1} & Pin \ 25 \\ V_{CC2} \\ \hline \end{array}$                                    | R-out:<br>R signal output pin                                                     |                      |

| 27      | $\begin{array}{c c} & \text{Pin 6} \\ V_{CC1} \\ \hline \end{array}$                                                   | R-ch. AVE det.:<br>R-ch. output DC feedback<br>detection pin                      |                      |

| 28      | Pin 25<br>V <sub>CC2</sub><br>28<br>100 kΩ<br>Pin 23<br>GND                                                            | Common out: Voltage output pin for common. Output impedance; Approx. 150 $\Omega$ |                      |

AN2546FH-A

## ■ Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                                | Description                                                                   | Voltage · Waveform                                                                             |

|---------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 29      | _                                                                                                 | V <sub>CC3</sub> :<br>Logic output circuits system<br>power supply 3.0 V typ. | _                                                                                              |

| 30      | Pin 29<br>V <sub>CC3</sub><br>Pin 37<br>V <sub>SS</sub> Pin 23<br>GND                             | PWM:<br>PWM signal output pin                                                 | Output waveform  V <sub>CC3</sub> 0 V                                                          |

| 31      | Pin 29<br>V <sub>CC3</sub><br>Pin 37<br>V <sub>SS</sub> Pin 23<br>GND                             | VD:<br>Vertical synchronous signal<br>output pin                              | Output waveform  V <sub>CC3</sub> 0 V                                                          |

| 32      | Pin 29<br>V <sub>CC3</sub><br>Pin 37<br>V <sub>SS</sub> Pin 23<br>GND                             | HD:<br>Horizontal synchronous sig-<br>nal output pin                          | Output waveform  V <sub>CC3</sub> 0 V                                                          |

| 33      | $\begin{array}{c c} & \text{Pin } 44 \\ \hline 100 \ \Omega & 100 \ \Omega \\ \hline \end{array}$ | SCP out:<br>Sand castle pulse output pin                                      | 4.0 V[p-p]  1.0 V[p-p] |

| 34      | Pin 29<br>V <sub>CC3</sub><br>Pin 37<br>V <sub>SS</sub> Pin 23<br>GND                             | HSS:<br>Composite synchronous sig-<br>nal output pin                          | Output waveform  V <sub>CC3</sub> 0 V                                                          |

| Pin No. | Equivalent circuit                                                                                                                                                | Description                                                                                                               | Voltage · Waveform |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------|

| 35      | 35<br>10 kΩ Pin 23<br>GND                                                                                                                                         | VDB in:<br>Vertical synchronous pulse<br>input pin                                                                        | High or Low        |

| 36      | 36<br>15 kΩ<br>100 kΩ<br>Pin 23<br>GND                                                                                                                            | Ext. pol.:<br>1H reverse signal input pin                                                                                 | High or Low        |

| 37      | _                                                                                                                                                                 | V <sub>SS</sub> : MOS system GND                                                                                          |                    |

| 38      | 38<br>15 kΩ<br>100 kΩ<br>Pin 23<br>GND                                                                                                                            | PRGB: Analog OSD signal input Mode start-up signal input pin Valid only in the analog OSD mode High = Analog OSD start up | High or Low        |

| 39      | $\begin{array}{c c} \hline 200 \Omega & Pin 44 \\ \hline V_{CC1} & \\ \hline 60 \Omega & 10 k\Omega \\ \hline 12 k\Omega & Pin 41 \\ \hline GND & \\ \end{array}$ | LDET: Capacitor coupling pin for the horizontal unlock detecting circuit                                                  | _                  |

| 40      | _                                                                                                                                                                 | V <sub>DD</sub> : Capacitor connection pin for MOS part power supply 3.0 V typ.                                           | _                  |

| 41      | _                                                                                                                                                                 | GND 2: Pulse system GND                                                                                                   | _                  |

| 42      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                             | AFC det.: AFC filter connecting pin Input impedance; $100 \ k\Omega$ or more                                              | 1H                 |

# **Panasonic**

## ■ Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                                                                                                         | Description                                                                                                              | Voltage · Waveform                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 43      | $\begin{array}{c c} & \text{Pin } 44 \\ \text{V}_{\text{CC1}} \\ \text{5 pF} \\ \hline \end{array}$                                                                        | H f <sub>O</sub> :<br>VCO oscillation frequency<br>adjusting resistor connection<br>pin                                  | _                                  |

| 44      | _                                                                                                                                                                          | V <sub>CC1</sub> : Pulse system power supply 5.0 V                                                                       | _                                  |

| 45      | $\begin{array}{c c} 45 \\ \hline 15 \text{ k}\Omega \\ \hline \end{array}$                                                                                                 | NAVI sync-in:<br>Synchronous signal input pin<br>for the signal of car naviga-<br>tion system<br>Negative polarity input | V <sub>DD</sub>                    |

| 46      | Pin 44    21.7 kΩ   32.5 kΩ V <sub>CC1</sub>   850 Ω   50 kΩ    Pin 41   GND                                                                                               | HSS in: Sync. signal input pin Separates a sync. signal from luminance signal (video signal)                             | Input signal example: Video signal |

| 47      | 10 kΩ Pin 23 GND                                                                                                                                                           | SCLK:<br>Serial clock input pin                                                                                          |                                    |

| 48      | $\begin{array}{c c} & \text{Pin } 44 \\ V_{CC4} \\ \hline \\ 10 \text{ k}\Omega \\ \hline \\ 100 \text{ k}\Omega \\ \hline \\ \text{Pin } 23 \\ \text{GND} \\ \end{array}$ | DAT:<br>Serial data input pin                                                                                            |                                    |

| Pin No. | Equivalent circuit                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                           | Voltage · Waveform                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 49      | $\begin{array}{c c} \hline 5 \text{ k}\Omega \\ \hline 500 \Omega \end{array}$ $\begin{array}{c} \text{Pin 44} \\ \text{V}_{\text{CC1}} \end{array}$ $\begin{array}{c} 50 \text{ k}\Omega \\ \hline \text{Pin 41} \\ \text{GND} \end{array}$ $\begin{array}{c} \text{Pin 37} \\ \text{V}_{\text{SS}} \end{array}$ | RST:<br>Capacitor coupling pin for<br>power-on reset                                                                                                                  |                                    |

| 50      | 1.5 pF 46 kΩ Pin 41 GND                                                                                                                                                                                                                                                                                           | Com. DC: DC voltage output pin                                                                                                                                        | DC                                 |

| 51      | Pin 44 $V_{CC1}$ $1.5 \text{ pF}$ $140 \text{ k}\Omega$ $136 \text{ k}\Omega$ Pin 41 GND                                                                                                                                                                                                                          | DAC-out:<br>DC voltage output pin                                                                                                                                     | DC                                 |

| 52      | $\begin{array}{c c} \hline  & 50 \text{ k}\Omega \\ \hline  & 50 \text{ k}\Omega \end{array}$                                                                                                                                                                                                                     | Y-in:<br>Luminance signal input pin<br>Input luminance signal (video<br>signal)                                                                                       | Input signal example: Video signal |

| 53      | 2 kΩ 53 Pin 59 GND                                                                                                                                                                                                                                                                                                | Trap-out: Trap connecting pin Trapping a chrominance signal by connecting external inductor and capacitor. Not necessary in case that an input signal is a component. | _                                  |

## **Panasonic**

## ■ Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                                                                                                                       | Description                                                                                     | Voltage · Waveform                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------|

| 54      | Pin 58<br>V <sub>CC1</sub><br>Pin 59<br>GND                                                                                                                                              | Trap-in: Trap connecting pin The pair with pin 53                                               | _                                  |

| 55      | $ \begin{array}{c c} \operatorname{Pin} 58 \\ 1 \text{ k}\Omega & 1 \text{ k}\Omega^{V_{CC1}} \end{array} $ $ \begin{array}{c} \operatorname{Pin} 59 \\ \operatorname{GND} \end{array} $ | Y-det.: Capacitor coupling pin for luminance signal clamping                                    |                                    |

| 56      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                    | ACC det.: ACC capacitor connecting pin, adjusting the amplitude of a burst signal automatically | _                                  |

| 57      | Pin 58<br>V <sub>CC1</sub><br>50 kΩ<br>Pin 59<br>GND                                                                                                                                     | C-in: Chrominance signal input pin Input chrominance signal (video signal)                      | Input signal example: Video signal |

| 58      |                                                                                                                                                                                          | V <sub>CC1</sub> : Power supply 5.0 V typ. Chrominance and luminance signal processing system.  | _                                  |

| 59      | _                                                                                                                                                                                        | GND 3:<br>GND for chrominance and luminance signal processing system                            | _                                  |

| Pin No. | Equivalent circuit                                           | Description                                                                                                                                                                                        | Voltage · Waveform         |

|---------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 60      | Pin 58<br>V <sub>CC1</sub><br>72 kΩ<br>Pin 59<br>GND         | Kill det.: Killer capacitor coupling pin To prevent degradation of image in a small amplitude of a burst signal, this pin stops a chrominance signal and the mode changes to black and white mode. | _                          |

| 61      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$        | APC det.: APC capacitor coupling pin Matching the phase of a crystal oscillation to that of burst signal                                                                                           | _                          |

| 62      | Pin 58<br>V <sub>CC1</sub><br>10 kΩ<br>Pin 59<br>GND         | SCP out:<br>Subcarrier pulse output pin                                                                                                                                                            | NTSC 3.58 MHz PAL 4.43 MHz |

| 63      | Pin 58<br>V <sub>CC1</sub><br>190 Ω<br>1 kΩ<br>Pin 59<br>GND | VXO1: NTSC crystal oscillator connecting pin Use the capacitor with temperature characteristics (N750) to connect to the crystal oscillator.                                                       | _                          |

| Pin No. | Equivalent circuit                                 | Description                                                                                                                                           | Voltage · Waveform |

|---------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 64      | Pin 58<br>V <sub>CC1</sub> 190 Ω  1 kΩ  Pin 59 GND | VXO2: PAL and PAL-M crystal oscillator connecting pin Use the capacitor with temperature characteristics (N750) to connect to the crystal oscillator. | _                  |

### ■ Usage Notes

- The supply voltage applied to pin 6, pin 25, pin 29, pin 44, and pin 58 must be brought up at the same time.

- The crystal oscillator used must be evaluated thoroughly, because chrominance signal processing system characteristics change by the crystal oscillator type.

- The conversion of the analog RGB signals and the analog OSD signals with synchronous signals is not supported.

- Input the analog RGB signals and the analog OSD signals after filtering the pedestal parts of these signals.

- Evaluated thoroughly on the application of this device in PAL.

#### ■ Technical Data

#### 1. Serial interface description

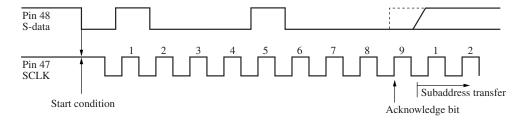

#### 1) I<sup>2</sup>C bus control mode

A serial data is capable of transferring 9-bit unit of 8-bit transfer data and 1-bit answering data using two kinds of signal lines of data and shift clock.

When a slave address after setting a start condition matches the address on the IC side, you can receive the data to be transmitted from then. Once the stop condition is set up, the next transmitting data will be ignored until the start condition is set up.

There are two kinds of transfer mode: an auto-increment mode which does not transmit subaddress, and data upgrade mode which transmits subaddress + data by 2 bytes.

The typical models of communication sequence are shown below:

#### (1) Start condition

When the S-data changes from high level to low level at SCLK = high level, a data receiving mode becomes available.

#### (2) Slave address transfer

The slave address of the AN2546FH-A is 88h.

AN2546FH-A Panasonic

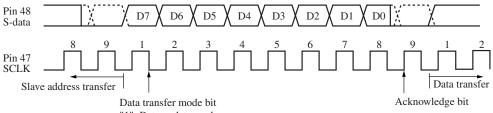

### ■ Technical Data (continued)

### 1. Serial interface description (continued)

- 1) I<sup>2</sup>C bus control mode (continued)

- (3) Subaddress transfer

When a data transfer mode bit is 0, all the serial data columns transferred until a stop condition is set is regarded as the data block.

"1": Data update mode

"0": Auto increment mode

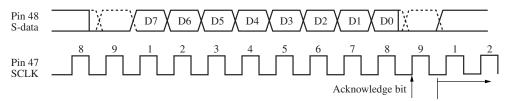

### (4) Data transfer

At auto increment mode: Data transfer At data update mode: Stop condition

(5) Stop condition

When S-data changes from low level to high level at SCLK = high level, data reception is halted.

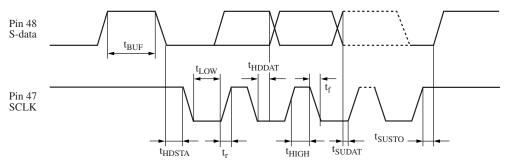

(6) Pulse timing

Timing chart expanded diagram

| Parameter                                            | Symbol             | Min | Тур | Max | Unit |

|------------------------------------------------------|--------------------|-----|-----|-----|------|

| SCLK clock frequency                                 | t <sub>SCL</sub>   | 0   | _   | 400 | kHz  |

| Bus free-time for stop condition and start condition | t <sub>BUF</sub>   | 1.3 | _   | _   | μs   |

| Hold time start condition                            | t <sub>HDSTA</sub> | 0.6 | _   | _   | μs   |

| SCLK clock low-state hold time                       | t <sub>LOW</sub>   | 1.3 | _   | _   | μs   |

| SCLK clock high-state hold time                      | t <sub>HIGH</sub>  | 0.6 | _   | _   | μs   |

| Data hold time                                       | t <sub>HDDAT</sub> | 0   | _   | _   | μs   |

| Data setup time                                      | t <sub>SUDAT</sub> | 100 | _   | _   | ns   |

| S-data and SCLK signal rise time                     | t <sub>r</sub>     | _   | _   | 300 | ns   |

| S-data and SCLK signal fall time                     | $t_{\mathrm{f}}$   | _   | _   | 300 | ns   |

| Stop condition setup time                            | t <sub>SUSTO</sub> | 0.6 | _   | _   | μs   |

### ■ Technical Data (continued)

- 1. Serial interface description (continued)

- 2) Mode setting channel bits table

| ch. | Sub-<br>address | Initial value<br>(HEX) | D7                                             | D6               | D5           | D4           | D3          | D2             | D1                | D0           |  |  |  |

|-----|-----------------|------------------------|------------------------------------------------|------------------|--------------|--------------|-------------|----------------|-------------------|--------------|--|--|--|

| 1   | 01              | 80                     | 4                                              | Common amplitude |              |              |             |                |                   |              |  |  |  |

| 2   | 02              | 80                     | 4                                              | Luminance gain — |              |              |             |                |                   |              |  |  |  |

| 3   | 03              | 80                     | 4                                              |                  |              | - Colo       | r gain -    |                |                   | <b>&gt;</b>  |  |  |  |

| 4   | 04              | 80                     | ◄                                              |                  |              | — н          | ue —        |                |                   | <b>&gt;</b>  |  |  |  |

| 5   | 05              | 40                     | HGA                                            | •                |              | - Black      | limiter -   |                |                   | -            |  |  |  |

| 6   | 06              | 80                     | ◀                                              |                  |              | – Brigh      | itness -    |                |                   | -            |  |  |  |

| 7   | 07              | 80                     | DBOSC                                          | 4                |              | — Ape        | rture –     |                |                   | -            |  |  |  |

| 8   | 08              | 80                     | •                                              |                  |              | R-ch. sub-   | brightness  |                |                   | -            |  |  |  |

| 9   | 09              | 80                     | <b>-</b>                                       |                  |              | B-ch. sub-   | brightness  |                |                   | -            |  |  |  |

| 10  | 0A              | C0                     | DCLP                                           | •                |              | White pe     | ak limiter  |                |                   | -            |  |  |  |

| 11  | 0B              | 80                     | 4                                              |                  |              | — Gam        | ma 1 —      |                |                   | -            |  |  |  |

| 12  | 0C              | 80                     | 4                                              |                  |              | — Gam        | ma 2 —      |                |                   |              |  |  |  |

| 13  | 0D              | 80                     | ◀                                              |                  |              | — Con        | trast —     |                |                   | -            |  |  |  |

| 14  | 0E              | 80                     | ◄                                              |                  |              | R-ch. sub    | o-contrast  |                |                   | -            |  |  |  |

| 15  | 0F              | 80                     | 4                                              |                  |              | B-ch. sub    | o-contrast  |                |                   |              |  |  |  |

| 16  | 10              | 80                     | 4                                              |                  |              | VCO fre      | ee-run *1   |                |                   | <b>&gt;</b>  |  |  |  |

| 17  | 11              | 03                     | DFVD                                           | DFSC             | DPALM        | DPALN        | DSECAM      | DVMODE         | DUV               | DCINT        |  |  |  |

| 18  | 12              | 00                     | MACRON                                         | <b>→</b> PL      | L stop posit | tion adjustm | ent -       | ✓ Vertical     | position ad       | justment -   |  |  |  |

| 19  | 13              | 80                     | HOSEI                                          | PWMT4            | KOTEI        | -            | – Horizonta | al position ac | djustment -       | -            |  |  |  |

| 20  | 14              | 80                     | <b>→</b> PV                                    | VM frequen       | cy adjustmo  | ent -        | BLAK        | → Burst cleani | ng pulse positior | adjustment - |  |  |  |

| 21  | 15              | 80                     | 4                                              | PWM duty         |              |              |             |                |                   |              |  |  |  |

| 22  | 16              | 7F                     | EXTTEST DHTS EXCHFI POLSW DMOSD DSC DCPS DQPAL |                  |              |              |             |                |                   |              |  |  |  |

| 23  | 17              | 80                     | 4                                              |                  |              | - Commo      | n DC *2 -   |                |                   | -            |  |  |  |

| 24  | 18              | 80                     | <b>→</b>                                       |                  |              | DC output    | adjustment  |                |                   |              |  |  |  |

Note) \*1: VCO free-run adjustment; ch.23 = 02h or more, EXTTEST = High

<sup>\*2:00</sup>h,01h are prohibition of use because of test mode.

### ■ Technical Data (continued)

- 1. Serial interface description (continued)

- 2) Mode setting channel bits table (continued)

- (1) ch.5: Black limiter adjustment

| Sub-<br>address | D7<br>HGA | D6          | D5          | D4 | D3 | D2 | D1 | D0 |

|-----------------|-----------|-------------|-------------|----|----|----|----|----|

| 05              | 0         | Output gain | n down mode | e  |    |    |    |    |

|                 | 1         | Gain mode   |             |    |    |    |    |    |

### (2) ch.7: Aperture adjustment

| Sub-<br>address | D7<br>DCLP | D6         | D5          | D4          | D3     | D2 | D1 | D0 |

|-----------------|------------|------------|-------------|-------------|--------|----|----|----|

| 07              | 0          | VD free-ru | n: NTSC = 2 | 265H, PAL = | :315H  |    |    |    |

|                 | 1          | VD free-ru | n:NTSC=     | 263H, PAL = | = 313H |    |    |    |

### (3) ch.10: White peak limiter adjustment

| Sub-<br>address | D7<br>DCLP | D6         | D5                       | D4  | D3 | D2 | D1 | D0 |  |

|-----------------|------------|------------|--------------------------|-----|----|----|----|----|--|

| 0A              | 0          | NAVI sync  | IAVI sync. mode (Pin 45) |     |    |    |    |    |  |

|                 | 1          | Video sync | . mode (Pin              | 46) |    |    |    |    |  |

### (4) ch.17: Mode setup 1

| Sub-<br>address | D7   | D6   | D5    | D4    | D3     | D2     | D1  | D0    |

|-----------------|------|------|-------|-------|--------|--------|-----|-------|

| 11              | DFVD | DFSC | DPALM | DPALN | DSECAM | DVMODE | DUV | DCINT |

| Mode   |                      | Function                      |  |  |  |

|--------|----------------------|-------------------------------|--|--|--|

| DFVD   | 0                    | VD cycle: 60 Hz               |  |  |  |

|        | 1                    | VD cycle: 50 Hz               |  |  |  |

| DFSC   | 0                    | Subcarrier: 3.58 MHz          |  |  |  |

|        | 1                    | Subcarrier: 4.43 MHz          |  |  |  |

| DPALM  | High                 | High = PALM mode on           |  |  |  |

| DPALN  | High = PALN mode on  |                               |  |  |  |

| DSECAM | High = SECAM mode on |                               |  |  |  |

| DVMODE | High                 | n = Burst swing off           |  |  |  |

| DUV    | 0                    | Chrominance input             |  |  |  |

|        | 1                    | Color difference signal input |  |  |  |

| DCINT  | 0                    | RGB signal input              |  |  |  |

|        | 1                    | Video signal input            |  |  |  |

- at NTSC selection

DFVD/DFSC/DPALM/DPALN/DSECAM = Low

DVMODE = High

- at PAL selection

DFVD/DFSC = High

DPALM/DPALN/DSECAM/DVMODE = Low

- at PALM selection

DPALM/DFVD = High

DPALN/DSECAM/DVMODE = Low

- at PALN selection

DPALN = High

DPALM/DSECAM/DVMODE/DFVD = Low

### (5) ch.18: PLL stop position and vertical sync. output position adjustment

| Sub-    | D7     | D6                                                    | D5                               | D4 | D3 | D2 | D1 | D0      |  |

|---------|--------|-------------------------------------------------------|----------------------------------|----|----|----|----|---------|--|

| address | MACRON | PLL stop position adjustment Vertical position adjust |                                  |    |    |    |    | ustment |  |

| 12      | 0      | AFC norma                                             | AFC normal operation             |    |    |    |    |         |  |

|         | 1      | Copy guard                                            | Copy guard signal correspondence |    |    |    |    |         |  |

### ■ Technical Data (continued)

- 1. Serial interface description (continued)

- 2) Mode setting channel bits table (continued)

- (5) ch.18: PLL stop position and vertical sync. position adjustment (continued)

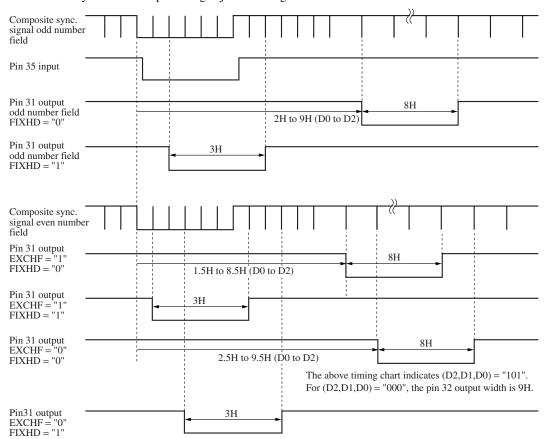

<Vertical synchronous output timing adjustment range>

The pin 31 timing is synchronous with the pin 35 input timing. The above timing chart is just for reference

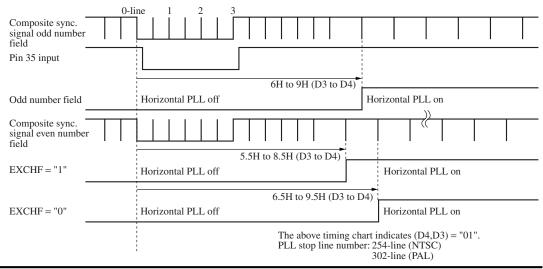

### <Horizontal PLL start position adjustment range>

AN2546FH-A Panasonic

### ■ Technical Data (continued)

- 1. Serial interface description (continued)

- 2) Mode setting channel bits table (continued)

- (6) ch.19: Horizontal sync. output position adjustment

| Sub-<br>address | D7<br>HOSEI | D6<br>PWMT4                  | D5<br>KOTEI                 | D4                         | D3 | D2 | D1 | D0 |  |  |

|-----------------|-------------|------------------------------|-----------------------------|----------------------------|----|----|----|----|--|--|

| 13              |             |                              | 0                           | Sync. output variable mode |    |    |    |    |  |  |

|                 |             |                              | 1                           | Sync. output fixation mode |    |    |    |    |  |  |

|                 |             | _                            | PWM freq                    | requency adjustment        |    |    |    |    |  |  |

|                 | 0           | VCO automatic adjustment off |                             |                            |    |    |    |    |  |  |

|                 | 1           | VCO autor                    | VCO automatic adjustment on |                            |    |    |    |    |  |  |

The delay time of pin 34 output to video signal is likely to vary according to an external constant connected to pin 46. For an external constant, the characteristics in weak electric field must be evaluated adequately.

Though the horizontal sync. signal output adjustment range is designed by referring to the center of pin 34 output pulse, there would be some error according to VCO free-run frequency.

(7) ch.20: PWM frequency and burst cleaning pulse width adjustment

| Sub-    | D7                       | D6 | D5 | D4   | D3                              | D2         | D1            | D0  |

|---------|--------------------------|----|----|------|---------------------------------|------------|---------------|-----|

| address | PWM frequency adjustment |    |    | BLAK | Burst cleaning pulse adjustment |            |               |     |

| 14      |                          |    |    |      | 0                               | Black leve | l variable mo | ode |

|         |                          |    |    |      | 1                               | Black leve | l fixation mo | de  |

Panasonic AN2546FH-A

### ■ Technical Data (continued)

- 1. Serial interface description (continued)

- 2) Mode setting channel bits table (continued)

- (8) ch.22: Mode setup 2

| Sub-<br>address | D7      | D6   | D5     | D4    | D3    | D2  | D1   | D0    |

|-----------------|---------|------|--------|-------|-------|-----|------|-------|

| 16              | EXTTEST | DHTS | EXCHFI | POLSW | DMOSD | DSC | DCPS | DQPAL |

| Mode    |   | Function                         |

|---------|---|----------------------------------|

| EXTTEST | 0 | Normal mode                      |

|         | 1 | Test mode                        |

| DHTS    | 0 | 1H reverse stop                  |

|         | 1 | 1H reverse                       |

| EXCHFI  | 0 | Odd number field: Advance phase  |

|         | 1 | Even number field: Advance phase |

| POLSW   | 0 | Internal POL 1H reverse mode     |

|         | 1 | External POL 1H reverse mode     |

| DMOSD   | 0 | Analog OSD signal input          |

|         | 1 | Digital OSD signal input         |

| DSC     | 0 | Subcarrier output stop           |

|         | 1 | Subcarrier output                |

| DCPS    | 0 | Component input mode             |

|         | 1 | Composite input mode             |

| DQPAL   | 0 | STD PAL mode                     |

|         | 1 | Quasi PAL mode                   |

### 2. Recommended Operating Conditions

| Parameter                           | Symbol            | Condition              | Min | Тур | Max | Unit    |

|-------------------------------------|-------------------|------------------------|-----|-----|-----|---------|

| Composite video input signal        | Y <sub>IN</sub>   | Sync. chip - White     | 0.9 | 1.0 | 1.1 | V[p-p]  |

| Y-input signal voltage              | Y <sub>IN</sub>   | Pedestal - White       | 0.6 | 0.7 | 0.8 | V[p-p]  |

| C-input signal voltage              | C <sub>IN</sub>   | Burst signal amplitude | 200 | 300 | 400 | mV[p-p] |

| MOS input signal low-level voltage  | V <sub>MOSL</sub> |                        | 0   | _   | 0.9 | V       |

| MOS input signal high-level voltage | V <sub>MOSH</sub> |                        | 2.1 | _   | *1  | V       |

| Sync. signal input                  | H <sub>SYNC</sub> | Pedestal - Sync. chip  | 0.2 | 0.3 | 0.4 | V[p-p]  |

| Analog RGB signal input             | RGB <sub>IN</sub> | Pedestal - White       | 0.6 | 0.7 | 0.8 | V[p-p]  |

Note) \*1: Set it lower than  $V_{CC1}$  (Pin 6 voltage).

- Technical Data (continued)

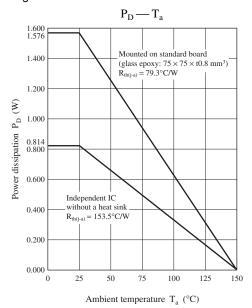

- 3. Power dissipation of package QFP064-P-1010

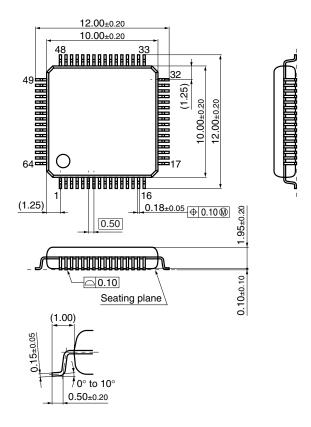

- New Package Dimensions (Unit: mm)

- QFP064-P-1010A (Lead-free package)

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuits examples of the products. It neither warrants non-infringement of intellectual property right or any other rights owned by our company or a third party, nor grants any license.

- (3) We are not liable for the infringement of rights owned by a third party arising out of the use of the product or technologies as described in this material.

- (4) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (5) The products and product specifications described in this material are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (6) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage, and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (7) When using products for which damp-proof packing is required, observe the conditions (including shelf life and amount of time let standing of unsealed items) agreed upon when specification sheets are individually exchanged.

- (8) This material may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.

2002 JUL

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.