No.4688

STK392-020

Convergence Correction Circuit

Three Channels in a Single Package

(Maximum Output Current: 6A)

### Overview

The STK392-020 is a hybrid IC for video projector convergence correction. Since this IC integrates three output amplifier circuits in a single package, the six convergence correction output circuits, i.e., the vertical and horizontal directions for each CRT of the RGB can be formed from only two ICs.

# **Applications**

Video projectors (both standard and high definition)

### **Features**

- Three output amplifier circuits integrated in a single 22-pin package

- High absolute maximum supply voltage (V<sub>CC</sub> max = ±44 V)

- Low thermal resistance ( $\theta$ j-c = 2.1 °C/W)

- High thermal stability ( $T_C \max = 125^{\circ}C$ )

- · Isolated early stage and output stage power supplies

- Output stage power supply switching supports high efficiency designs.

- The input system, power supply system and output system pins are isolated in the pin arrangement, thus reducing the influence of the pattern layout on the characteristics and easing design.

- Since constant current circuits are used in the pre-driver stage, operation is stable with respect to the power supply switching.

- The Sanyo convergence correction circuit product lineup (the STK392-000 series) handles a wide range of end-product classes. Therefore, the same PCB can be used for end products from popularly-priced units to top-of-the-line models.

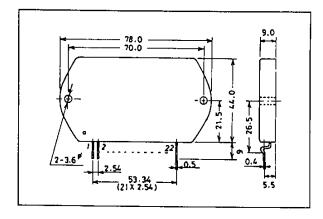

# **Package Dimensions**

unit: mm

### 4086A

# **Specifications**

Absolute Maximum Ratings at Ta = 25°C

| Parameter                       | Symbol              | Conditions                               | Ratings     | Unit |

|---------------------------------|---------------------|------------------------------------------|-------------|------|

| Maximum supply voltage          | V <sub>CC</sub> max |                                          | ±44         | V    |

| Maximum collector current       | Ic                  | Tr8, 10, 18, 20, 28, 30                  | +6.0        | A    |

| Thermal resistance              | θj-c                | Tr8, 10, 18, 20, 28, 30 (per transistor) | 2,1         | °C/W |

| Junction temperature            | Τj                  |                                          | 150         | °C   |

| Operating substrate temperature | Tc                  |                                          | 125         | •c   |

| Storage temperature             | Tstg                |                                          | -30 to +125 | → c  |

SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

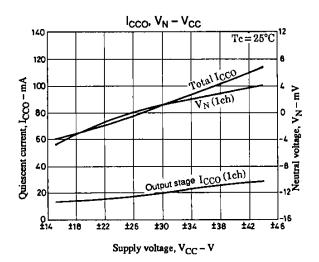

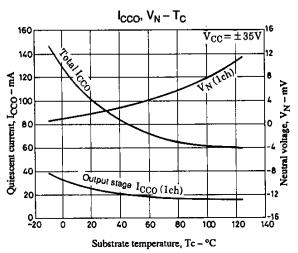

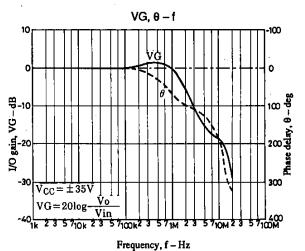

# Operating Characteristics at Ta = 25°C, Rg = 50 $\Omega$

| Parameter            | Symbol          | Conditions                                                                                  | Ratings |     |     | 4     |

|----------------------|-----------------|---------------------------------------------------------------------------------------------|---------|-----|-----|-------|

|                      |                 |                                                                                             | min     | typ | max | Unit  |

| Output noise voltage | V <sub>NO</sub> | V <sub>CC</sub> = ±35 V                                                                     |         | Ī   | 0.2 | mVrms |

| Quiescent current    | lcco            | V <sub>CC</sub> = ±35 V                                                                     | 30      | 90  | 150 | mA    |

| Neutral voltage      | V <sub>N</sub>  | V <sub>CC</sub> = ±35 V                                                                     | -50     | 0   | +50 | m∨    |

| Output delay time    | t <sub>D</sub>  | V <sub>CC</sub> = ±35 V, f = 15.75 kHz;<br>Triangle wave input, V <sub>OUT</sub> = 1.5 Vp-p |         |     | 1.0 | μs    |

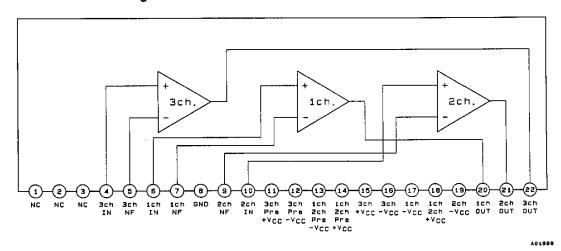

# **Equivalent Circuit Block Diagram**

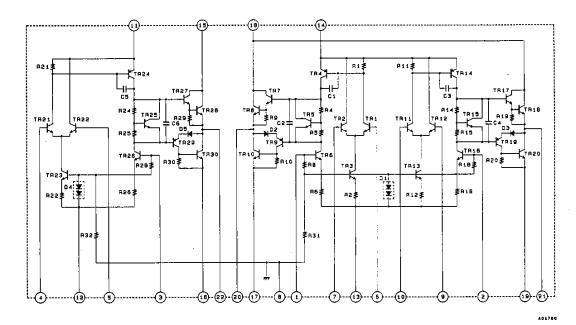

# **Internal Equivalent Circuit**

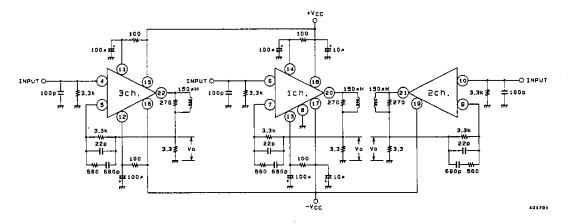

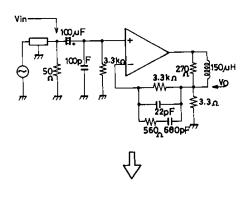

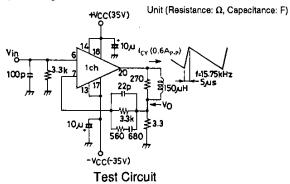

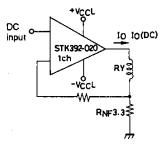

### **Test Circuit**

Unit (Resistance:  $\Omega$ , Capacitance: F)

Vo: Connect to VTVM when measuring  $V_{NO}$  Connect to a DC volt meter when measuring  $V_{N}$  Connect to the oscilloscope when measuring  $t_{D}$

# **Test Circuit**

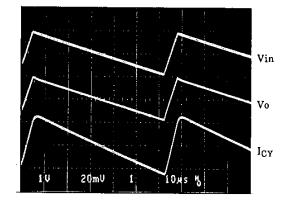

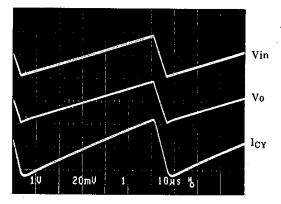

# **Operating Waveforms**

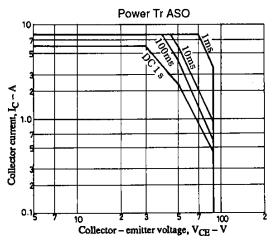

### Thermal Design

1. Ti max, Tc max, and θj-c

Tj max, Tc max, and 0j-c are stipulated in the maximum ratings as required parameters for thermal design.

• Tj max (junction temperature)

Tj max is a parameter that is due to the physical structure of the internal devices. Since devices will be degraded or destroyed if Tj exceeds this value, the design must not allow this value to be exceeded.

Tc max (operating substrate temperature)

Tc max is a parameter that arises from the internal devices, the materials used, and the circuit design. It is determined based on comprehensive considerations, including reliability. Devices are not guaranteed if they are operated with Tc exceeding this value.

θj-c (thermal resistance)

θj-c differs for each device in the design, and is stipulated in the maximum ratings since it is required to calculate Tj for the major devices in the design.

Note that Tj and Tc are independent parameters that depend on the operating conditions, and the thermal design must fulfill the maximum ratings of both these parameters.

2. Approaches to Thermal Design

Let Pd be the IC case internal operating power dissipation, and Pc be the power dissipation per power transistor. The required heat sink thermal resistance ( $\theta$ c-a) for this case internal power dissipation (Pd) can be derived as follows:

Condition 1: Taking Ta to be the end product guaranteed ambient temperature, the IC case temperature Tc must not exceed 125°C.

$$Pd \times \theta c - a + Ta < 125^{\circ}C (Tc max)....$$

Condition 2: The power transistor junction temperature must not exceed 150°C.

$$Pd \times \theta c - a + Pc \times \theta j - c + Ta < 150^{\circ}C (Tj max)....$$

Where  $\theta$ j-c is the thermal resistance per power transistor.

The thermal design must fulfill these above conditions.

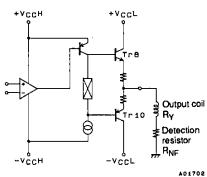

#### 3. Design Procedure

The figure at right shows a model of the STK392-020 channel 1 circuit. Taking the Pd's of each channel to be Pd1 (channel 1), Pd2 (channel 2) and Pd3 (channel 3), the total Pd max can be determined as:

Pd max = Pd1 max + Pd2 max + Pd3 max

That is, condition ① gives:

$$\theta c-a < \frac{Tc max - Ta max}{Pd max}$$

.....

which allows the required heat sink thermal resistance to be derived. (Here, Tc max is taken to be 125°C.)

Also, taking the power dissipation per power transistor for each channel to be Pc, the transistor junction temperature Tj will be:

$$T_i = Pd \max \times \theta c - a + Ta + Pc + \theta j - c \dots 4$$

and this can be used to confirm that Tj does not exceed Tj max (150°C).

At this point, if Tj exceeds  $150^{\circ}$ C in the design, Tc must be lowered by lowering the heat sink thermal resistance  $\theta$ c-a so that Tj does not exceed  $150^{\circ}$ C.

### STK392-020 Circuit Model (channel 1)

4. Thermal Design Example

Take the following to be the worst operating conditions for the STK392-020.

$$V_{CC}H = \pm 35 V$$

$$V_{CC}L = \pm 25 \text{ V}$$

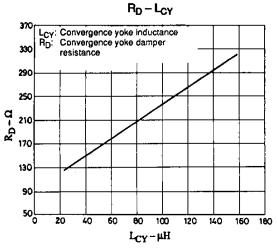

Output coil,  $L_Y = 150 \,\mu\text{H}$ ,  $R_Y = 0 \,\Omega$

Current detection resistor  $R_{NF} = 3.3 \Omega$

Ip-o max = 0.4 Ap-o (Ip-p = 0.8 A), Sawtooth waveform input

Io(DC) max = 0.4 A DC input

All three channels operating under the same conditions

Ta max =  $60^{\circ}$ C (unit internal temperature)

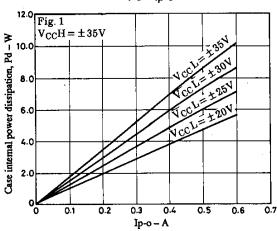

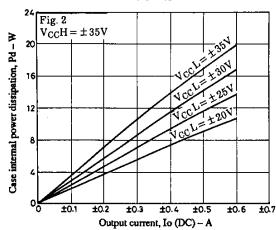

From figures 1 and 2, it can be seen that the Pd1 for channel 1 is:

(a) For a sawtooth wave input: Pd1 max = 4.8 W (AC)

(b) For a DC input:

Pd1 max = 9.5 W (DC)

This shows that Pd1 max AC < Pd1 max DC, i.e. that Pd1 is larger for a DC input.

Also, considering Pc for the output transistors gives:

(a) For a sawtooth wave (AC) input: Pc = 1/2 Pd1

(b) For a DC input:

Pc = Pd1 (Since the power concentrates in the transistor on one side.)

Therefore, the DC input Pc for the output transistors is larger.

Accordingly, the remainder of the thermal design is based on the DC input case.

Here we ignore the power dissipation in the early stages.

When: Pd1 max = Pd2 max = Pd3 max = 9.5 W, then the Pd max (total for three channels) will be:

Pd max = Pd1 max  $\times$  3 = 28.5 W

$$\theta c-a = \frac{Tc \max - Ta}{Pd \max} = \frac{125 - 60}{28.5} = 2.28^{\circ}C/W$$

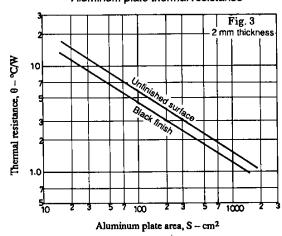

This means that if a 2 mm thick Al plate (with an unfinished surface) is used as the heat sink, then figure 3 shows that the following area S is required.

$$S = 625 \text{ cm}^2 (25 \times 25 \text{ cm})$$

Also, from formula (4), we see that the power transistor junction temperature Tj at this time will be:

$$Tj = Pd \max \times \theta c - a + Ta + Pc \max \times \theta j - c$$

= 28.5 \times 2.28 + 60 + 9.5 \times 2.1

= 145°C

This is a 5°C derating from the required 150°C Tj max.

(Addendum) To be precise, the power dissipated in the early stage circuits (transistor, resistors, etc.) should also be taken into consideration.

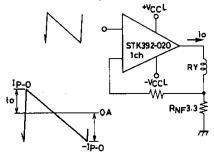

Figure 1: Sawtooth wave input (AC) Ip-o - Pd1

Figure 2: DC input Io(DC) - Pd1

Figure 3: Aluminum plate thermal resistance characteristics

### Sawtooth wave Input

$$Pd = \frac{V_{CC} I_{p-o}}{2} = \frac{R I_{p-o^2}}{3}$$

$$(R = R_{NF} + R_Y = R_{NF})$$

### Pd - Ip-o

# Aluminum plate thermal resistance

# **DC** input

$Pd = \{V_{CC} - (R_{NF} \times I_{DC})\} \times I_{DC}$

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 1996. Specifications and information herein are subject to change without notice.