Rev A5, Page 1/4

### ORDERING INFORMATION

| Туре  | Package   | Options | Order Designation | ξ |

|-------|-----------|---------|-------------------|---|

| iC-LV | BLCC LV4C |         | iC-LV BLCC LV4C   |   |

<sup>7.0</sup> mm x 7.0 mm **RoHS** compliant

| PIN CONFIGURATION | PIN F |       | IS                                                  |

|-------------------|-------|-------|-----------------------------------------------------|

| (top view)        | No.   | Name  | Function                                            |

|                   | 1     | LED   | LED Power Control Output (high-side current source) |

|                   | 2     | GND   | Ground                                              |

|                   | 3     | SOUT  | Serial Data Output (SSI) / Data Output D4           |

|                   | 4     | SERIN | Serial Data Input (SSI) / Data Output D3            |

|                   | 5     | SCLK  | Clock Input (SSI) / Data Output D2                  |

| 3                 | 6     | SYNM0 | Synchronisation Mode Input / Data Output D1         |

| 4 🗲 13            | 7     | SYNM1 | Synchronisation Mode Input / Data Output D0         |

| 5 🗲 📕 📕 🔁 12      | 8     | SEEN  | Serial Error Bit Enable Input (high active)         |

|                   | 9     | n.c.  | not connected                                       |

|                   | 10    | VCC   | +4+5.5 V Supply Voltage                             |

|                   | 11    | NINV  | Bit-wise Inversion Input (low active)               |

|                   | 12    | MODE  | Operating Mode Selection Input                      |

|                   | 13    | TEST  | Test Mode Enable Input (high active)                |

|                   | 14    | RSET  | LED Power Control Adjustment (wiring is optional)   |

|                   | 15    | NERR  | Error Output (low active)                           |

|                   | 16    | NDIR  | Reversal of Rotation Dir. Input (low active)        |

### ABSOLUTE MAXIMUM RATINGS

| ltem | Symbol | Parameter                           | Conditions                                                                                                                                                 | Fig. |      |      |            | Unit   |

|------|--------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|--------|

|      |        |                                     |                                                                                                                                                            |      | Min. | Тур. | Max.       |        |

| TG1  | Та     | Operating Ambient Temperature Range |                                                                                                                                                            |      | -40  |      | 125        | c      |

| TG2  | Ts     | Storage Temperature Range           |                                                                                                                                                            |      | -40  |      | 125        | c      |

| TG3  | Tpk    | Reflow Soldering Peak Temperature   | tpk < 20 s, convection reflow<br>tpk < 20 s, vapour phase<br>TOL (time on label) 8 h;<br>please refer to customer<br>information file No. 7 for<br>details |      |      |      | 260<br>230 | C<br>C |

Rev A5, Page 2/4

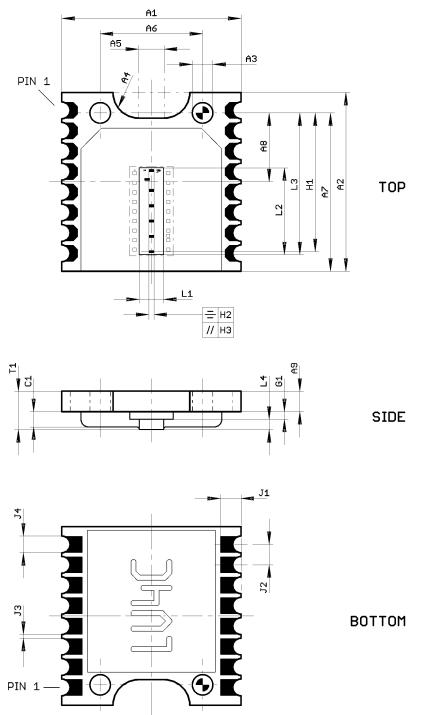

## PHYSICAL DIMENSIONS

DRB\_LV4C\_ROT180\_PACK\_1

Rev A5, Page 3/4

### DIMENSION TABLE

| ltem | Parameter                             | Comments                                             |      |      |      |           | Unit |  |

|------|---------------------------------------|------------------------------------------------------|------|------|------|-----------|------|--|

|      |                                       |                                                      | Min. | Тур. | Max. | Tolerance |      |  |

|      | Substrate                             |                                                      |      |      |      |           |      |  |

| A1   | Outline X                             |                                                      |      | 7.0  |      | ±0.2      | mm   |  |

| A2   | Outline Y                             |                                                      |      | 7.0  |      | ±0.1      | mm   |  |

| A3   | Alignment Hole Diameter               | alignment hole center is reference                   |      | 0.8  |      | +0.05     | mm   |  |

| A4   | Cut-Out Radius                        |                                                      |      | 1.0  |      |           | mm   |  |

| A5   | Cut-Out Centers                       |                                                      |      | 1.0  |      |           | mm   |  |

| A6   | Hole to Hole Pitch                    | tolerance applies also to Y-direction                |      | 4.0  |      | ±0.08     | mm   |  |

| A7   | Outline vs. Reference Y               |                                                      |      | 6.2  |      | ±0.15     | mm   |  |

| A8   | Reference vs. Center Y                |                                                      |      | 2.7  |      | ±0.15     | mm   |  |

| A9   | Substrate Thickness                   | bottom package to bottom die                         | 0.75 | 0.80 | 1.00 |           | mm   |  |

|      | Encapsulation                         |                                                      |      |      |      |           |      |  |

| C1   | Mold Thickness                        | note <sup>1</sup> )                                  | 0.50 |      | 0.70 |           | mm   |  |

|      | Chip Placement                        |                                                      |      |      |      |           |      |  |

| G1   | Chip Thickness                        |                                                      |      | 0.30 |      |           | mm   |  |

| H1   | Chip Position vs. Reference Y         | center of photodiode                                 |      | 5.44 |      | ±0.15     | mm   |  |

| H2   | Chip Symmetry                         |                                                      |      |      | 0.4  |           | mm   |  |

| H3   | Chip Parallelism                      |                                                      |      |      | 0.1  |           | mm   |  |

|      | Bottom Metal Pattern                  |                                                      |      |      |      |           |      |  |

| J1   | Lead Size                             |                                                      |      | 0.8  |      | ±0.15     | mm   |  |

| J2   | Lead Pitch<br>(or Lead-Lead Distance) | not accumulative                                     |      | 0.8  |      | ±0.08     | mm   |  |

| J3   | Lead-Lead Spacing                     |                                                      |      | 0.15 |      | ±0.05     | mm   |  |

| J4   | Lead Size                             |                                                      |      | 0.65 |      | ±0.05     | mm   |  |

|      | Glass Cover                           |                                                      |      |      |      |           |      |  |

| L1   | Glass Size X                          |                                                      |      | 0.95 |      | ±0.05     | mm   |  |

| L2   | Glass Size Y                          |                                                      |      | 3.40 |      | ±0.05     | mm   |  |

| L3   | Glass Position vs. Reference Y        |                                                      |      | 5.55 |      |           | mm   |  |

| L4   | Glass Thickness                       |                                                      |      | 0.40 |      |           | mm   |  |

|      | Thickness Specifications              |                                                      |      |      |      |           |      |  |

| T1   | Overall Thickness                     | note <sup>1</sup> ) bottom substrate to top of glass | 1.38 |      | 1.80 |           | mm   |  |

Notes: 1) nominal glass thickness of 0.4 mm

Rev A5, Page 4/4

### **REVISION HISTORY**

| Rev | Notes                                                                                                                                | Pages affected |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| A1  | Initial version                                                                                                                      |                |

| A2  | Table Pin Functions corrected                                                                                                        | 1              |

| A3  | Revision of pin layout (pad RC not connected)                                                                                        | 1              |

| A4  | Revision of Absolute Maximum Ratings (TG3) Reflow Soldering;<br>Physical Dimensions, Dimension Table Item H3 added;<br>Minor changes | 1, 2, 3        |

|     |                                                                                                                                      |                |

#### GENERAL HANDLING INSTRUCTIONS

After opening the dry pack, devices must be mounted within 8 hours (in factory conditions of maximum  $30^{\circ}$  / 60% RH) or must be stored at <10% RH. Devices require baking before mounting if the Humidity Indicator Card shows >10% when read at  $23^{\circ} \pm 5^{\circ}$  or if the conditi ons mentioned above are not met. Devices may be baked for 72 hours at 100°C using high-temperature device containers (trays).

#### Samples

Samples may not be subject for dry pack delivery, and, in that case, are not intended for reflow soldering.

This specification is for a newly developed product. iC-Haus therefore reserves the right to change or update, without notice, any information contained herein, design and specification; and to discontinue or limit production or distribution of any product versions. Please contact iC-Haus to ascertain the current data. Copying – even as an excerpt – is only permitted with iC-Haus approval in writing and precise reference to source.

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification on this site and does not assume liability for any errors or omissions in the materials. The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

As a general rule our developments, IPs, principle circuitry and range of Integrated Circuits are suitable and specifically designed for appropriate use in technical applications, such as in devices, systems and any kind of technical equipment, in so far as they do not infringe existing patent rights. In principle the range of use is limitless in a technical sense and refers to the products listed in the inventory of goods compiled for the 2007 export trade statistics issued by the Bureau of Statistics in Wiesbaden in December 2006, for example, or to any product in the product catalogue published for the 2007 exhibition in Hanover (Hannover-Messe).

We understand suitable application of our published designs to be state-of-the-art technology which can no longer be classed as inventive under the stipulations of patent law. Our explicit application notes are to be treated only as mere examples of the many possible and extremely advantageous uses our products can be put to.