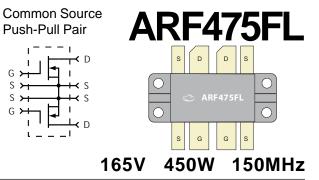

**RF POWER MOSFET** N-CHANNEL PUSH - PULL PAIR

The ARF475FL is a matched pair of RF power transistors in a common source configuration. It is designed for high voltage push-pull or parallel operation in narrow band ISM and MRI power amplifiers up to 150 MHz.

G

- Specified 150 Volt, 128 MHz Characteristics:

- **Output Power = 900 Watts Peak**

- Gain = 15dB (Class AB)

Efficiency = 50% min

- High Performance Push-Pull RF Package.

- High Voltage Breakdown and Large SOA for Superior Ruggedness.

- Low Thermal Resistance.

| MAXIMUN                          | MRATINGS All Ratings: T <sub>C</sub>                         | All Ratings: $T_{C} = 25^{\circ}C$ unless otherwise specified. |       |  |  |

|----------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|-------|--|--|

| Symbol                           | Parameter                                                    | ARF475FL                                                       | UNIT  |  |  |

| V <sub>DSS</sub>                 | Drain-Source Voltage                                         | 500                                                            | Volts |  |  |

| V <sub>DGO</sub>                 | Drain-Gate Voltage                                           | 500                                                            | VOIIS |  |  |

| I <sub>D</sub>                   | Continuous Drain Current @ $T_c = 25^{\circ}C$ (each device) | 10                                                             | Amps  |  |  |

| V <sub>GS</sub>                  | Gate-Source Voltage                                          | ±30                                                            | Volts |  |  |

| P <sub>D</sub>                   | Total Device Dissipation @ T <sub>C</sub> = 25°C             | 910                                                            | Watts |  |  |

| T <sub>J</sub> ,T <sub>STG</sub> | Operating and Storage Junction Temperature Range             | -55 to 175                                                     | °C    |  |  |

| TL                               | Lead Temperature: 0.063" from Case for 10 Sec.               | 300                                                            |       |  |  |

# STATIC ELECTRICAL CHARACTERISTICS (each device)

| Symbol                             | Characteristic / Test Conditions                                                     | MIN | TYP | MAX  | UNIT  |

|------------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|

| BV <sub>DSS</sub>                  | Drain-Source Breakdown Voltage ( $V_{GS} = 0V$ , $I_{D} = 250 \mu A$ )               | 500 |     |      | Volts |

| V <sub>DS(ON)</sub>                | On State Drain Voltage <sup>(1)</sup> ( $I_{D(ON)} = 5A, V_{GS} = 10V$ )             |     | 2.9 | 4    | VOILS |

|                                    | Zero Gate Voltage Drain Current ( $V_{DS} = V_{DSS}$ , $V_{GS} = 0V$ )               |     |     | 100  |       |

| DSS                                | Zero Gate Voltage Drain Current ( $V_{DS} = 50V, V_{GS} = 0, T_{C} = 125^{\circ}C$ ) |     |     | 500  | μA    |

| I <sub>GSS</sub>                   | Gate-Source Leakage Current ( $V_{GS} = \pm 30V$ , $V_{DS} = 0V$ )                   |     |     | ±100 | nA    |

| 9 <sub>fs</sub>                    | Forward Transconductance ( $V_{DS} = 15V, I_{D} = 5A$ )                              | 3   | 3.6 |      | mhos  |

| g <sub>fs1</sub> /g <sub>fs2</sub> | Forward Transconductance Match Ratio ( $V_{DS} = 15V, I_{D} = 5A$ )                  | 0.9 |     | 1.1  |       |

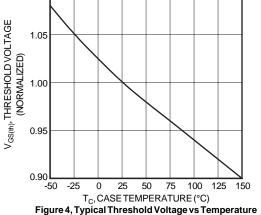

| V <sub>GS(TH)</sub>                | Gate Threshold Voltage ( $V_{DS} = V_{GS}$ , $I_D = 200$ mA)                         | 2   | 3.3 | 4    | Valta |

| $\Delta V_{GS(TH)}$                | Gate Threshold Voltage Match ( $V_{DS} = V_{GS}$ , $I_{D} = 200$ mA)                 |     |     | 0.2  | Volts |

# THERMAL CHARACTERISTICS

| Symbol                  | Characteristic                                                                  | MIN | ТҮР  | MAX   | UNIT  |

|-------------------------|---------------------------------------------------------------------------------|-----|------|-------|-------|

| $R_{_{	ext{	heta}JC}}$  | Junction to Case                                                                |     | 0.15 | 0.165 | °C AA |

| $R_{_{	ext{	heta}JHS}}$ | Case to Sink (Use High Efficiency Thermal Grease and Planar Heat Sink Surface.) |     | 0.30 | 0.33  | °C/W  |

🟹 🙏 CAUTION: These Devices are Sensitive to Electrostatic Discharge. Proper Handling Procedures Should Be Followed.

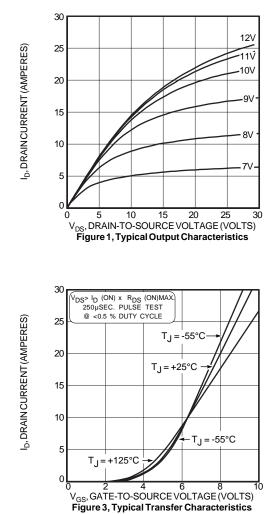

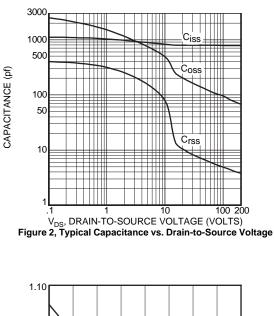

### DYNAMIC CHARACTERISTICS (per section)

| Symbol              | Characteristic               | Test Conditions                               | MIN | ТҮР | МАХ | UNIT |

|---------------------|------------------------------|-----------------------------------------------|-----|-----|-----|------|

| C <sub>iss</sub>    | Input Capacitance            | V <sub>GS</sub> = 0V                          |     | 780 | 830 |      |

| C <sub>oss</sub>    | Output Capacitance           | $V_{\rm DS} = 50V$                            |     | 125 | 130 | pF   |

| C <sub>rss</sub>    | Reverse Transfer Capacitance | f = 1MHz                                      |     | 7   | 9   |      |

| t <sub>d(on)</sub>  | Turn-on Delay Time           | V <sub>GS</sub> = 15V                         |     | 5.1 | 10  |      |

| t <sub>r</sub>      | Rise Time                    | V <sub>DD</sub> = 250V                        |     | 4.1 | 8   | ns   |

| t <sub>d(off)</sub> | Turn-off Delay Time          | I <sub>D</sub> = I <sub>D[Cont.]</sub> @ 25°C |     | 12  | 18  | 113  |

| t <sub>f</sub>      | Fall Time                    | R <sub>G</sub> = 1.6 Ω                        |     | 4.0 | 7   |      |

#### FUNCTIONAL CHARACTERISTICS (Push-Pull Configuration)

| Symbol          | Characteristic                     | Test Conditions                                  | MIN                            | ТҮР | МАХ | UNIT |

|-----------------|------------------------------------|--------------------------------------------------|--------------------------------|-----|-----|------|

| G <sub>PS</sub> | Common Source Amplifier Power Gain | f = 128 MHz<br>Idq = 15mA V <sub>DD</sub> = 150V | 14                             | 16  |     | dB   |

| η               | Drain Efficiency                   | $P_{out} = 900W$                                 | 50                             | 55  |     | %    |

| ψ               | Electrical Ruggedness VSWR 5:1     | PW = 3ms<br>10% duty cycle                       | No Degradation in Output Power |     |     |      |

(1) Pulse Test: Pulse width < 380  $\mu$ S, Duty Cycle < 2%.

$Microsemi\,Reserves\,the\,right\,to\,change, without\,notice, the\,specifications\,and\,information\,contained\,herein.$

Per transistor section unless otherwise specified.

Table 1 - Typical Series Equivalent Large Signal Input - Output Impedance

| Freq. (MHz) | $Z_{in}$ ( $\Omega$ ) gate to gate | $Z_{OL}(\Omega)$ drain - drain |

|-------------|------------------------------------|--------------------------------|

| 30          | 5.2 -j10                           | 41 -j20                        |

| 60          | 1.37 -j5.2                         | 26 -j25                        |

| 90          | .53 -j2.6                          | 16 -j23                        |

| 120         | .25 -j1.0                          | 10 -j20                        |

| 150         | .25 +j0.2                          | 6.7 -j17                       |

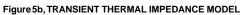

$Z_{in}$  - Gate -gate shunted with  $25 \Omega$   $~I_{DQ}$  = 15mA each side  $Z_{\text{OL}}$  - Conjugate of optimum load for 600 Watts peak output at  $V_{dd}$  = 150V 25% duty cycle and PW = 5ms

- TL3-6 Printed line L= 0.65" w=.23"

0.23" wide stripline on FR-4 board is ~  $30\Omega Z_{\Omega}$

Notes:

The value of L1 must be adjusted as the supply voltage is changed to maintain resonance in the output circuit. At 128MHz its value changes from approximately 40nH at 100V to 30nH at 150V.

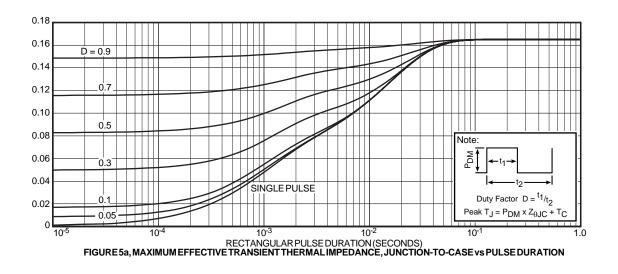

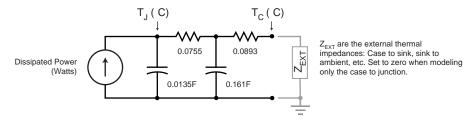

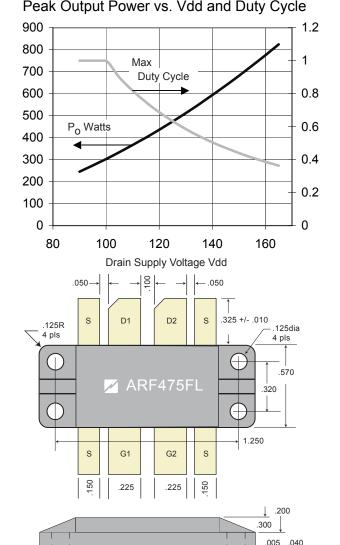

With the 50 $\Omega$  drain-to-drain load, the duty cycle above 100V must be reduced to insure power dissipation is within the limits of the device. Maximum pulse length should be 100mS or less. See transient thermal impedance, figure 5.

#### Thermal Considerations and Package Mounting:

The rated power dissipation is only available when the package mounting surface is at 25°C and the junction temperature is 175°C The thermal resistance between junctions and case mounting surface is 0.16°C/W. When installed, an additional thermal impedance of 0.15°C/W between the package base and the mounting surface is typical. Insure that the mounting surface is smooth and flat. Thermal joint compound must be used to reduce the effects of small surface irregularities. Use the minimum amount necessary to coat the surface. The heatsink should incorporate a copper heat spreader to obtain best results.

The package design clamps the ceramic base to the heatsink. A clamped joint maintains the required mounting pressure while allowing for thermal expansion of both the base and the heat sink. Four 4-40 (M3) screws provide the required mounting force. T = 6in-lb (0.68 N-m).

> HAZARDOUS MATERIAL WARNING The white ceramic portion of the device between leads and mounting surface is beryllium oxide, BeO. Beryllium oxide dust is toxic when inhaled. Care must be taken during handling and mounting to avoid damage to this area. These devices must never be thrown away with general industrial or domestic waste.

B 6-2007 050-4929

Microsemi's products are covered by one or more of U.S.patents 4,895,810 5,045,903 5,089,434 5,182,234 5,019,522 5,262,336 6,503,786 5,256,583 4,748,103 5,283,202 5,231,474 5,434,095 5,528,058 6,939,743 and foreign patents. US and Foreign patents pending. All Rights Reserved.

1.500

# Peak Output Power vs. Vdd and Duty Cycle