# **Universal Relay Driver**

#### **Features**

- ▶ 10 to 450V input voltage range

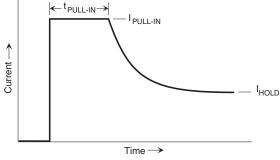

- ► Energy saving hold current mode

- ► Adjustable microcontroller supply

- Low supply current <1.0mA</li>

- Constant current coil

- ► Programmable pull-in current, pull-in time, and hold current

- Efficient PWM operation using the relay coils' inductance

### **Applications**

- Industrial controls

- Relay timers

- Solenoid drivers

- Home automation

### **General Description**

The Supertex HV9901 is a BiCMOS/DMOS universal relay driver that employs PWM switching techniques. It is designed for efficient and energy-saving operation of a low voltage relay with supply voltages ranging from 10 to 450V DC through utilization of the relay coils' inductance.

The circuit is capable of operating over a wide input voltage range without requiring a change of any external components. For example, this will enable users to use 5.0V coil relays for DC voltages 10 to 450V or AC voltages up to 240V.

The HV9901 has an internal high-voltage regulator to power internal PWM circuitry. Additionally, it includes an adjustable auxiliary regulator with a 1.0mA capability that can be used to supply low power micro controllers.

The pull-in current, pull-in time and hold current are all program-mable using only two resistors and a capacitor. The PWM switching frequency can be either:

- Synchronized to an external clock, or

- Synchronized to other HV9901s, where the synchronized frequency is the highest free-running frequency.

The enable (ENI) logic input is used to turn the relay on/off. Enable polarity may be selected via the POL input. Audible noise is prevented using fixed switching frequencies above 20kHz.

WARNING!!! Galvanic isolation is not provided. Dangerous voltages are present when connected to the AC line. It is the responsibility of the designer to ensure adequate safeguards are in place to protect the end user from electrical shock.

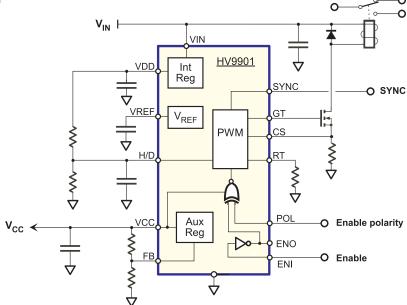

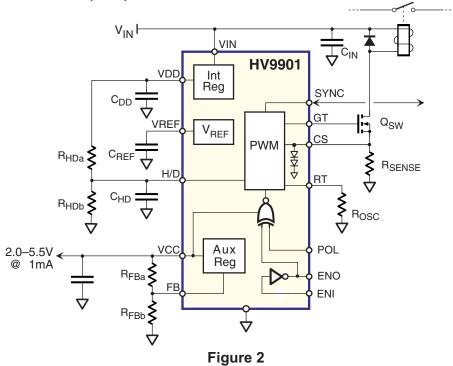

## **Typical Boost Application Circuit**

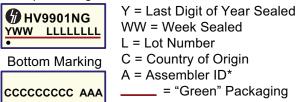

## **Ordering Information**

| Device | 16-Lead SOIC<br>9.90x3.90mm body,<br>1.75mm height (max), 1.27mm pitch |

|--------|------------------------------------------------------------------------|

| HV9901 | HV9901NG-G                                                             |

-G indicates package is RoHS compliant ('Green')

### **Absolute Maximum Ratings**

| Parameter                                        | Value                          |

|--------------------------------------------------|--------------------------------|

| Input voltage V <sub>IN</sub> <sup>1</sup>       | -0.5V to +470V                 |

| Input voltage to any other pin <sup>1</sup>      | -0.3V to V <sub>DD</sub> +0.3V |

| Operating temperature range                      | -40°C to +85°C                 |

| Continuous Power dissipation (T <sub>A</sub> = + | 25°C) <sup>2</sup> 750mW       |

#### Note:

- (1) All voltages are referenced to COM.

- (2) For operation above 25°C ambient derate linearly at 7.5 mW/°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

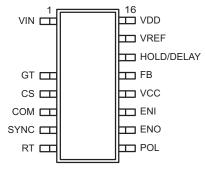

## **Pin Configuration**

16-Lead SOIC (NG) (top view)

#### **Product Marking**

Top Marking

16-Lead SOIC (NG)

\*May be part of top marking

## **Electrical Characteristics** ( $T_A = +25$ °C unless otherwise noted)

| Sym               | Parameter                                         | Min | Тур | Max | Units | Conditions                                                                                               |  |  |  |  |  |  |

|-------------------|---------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| High Volt         | High Voltage Regulator                            |     |     |     |       |                                                                                                          |  |  |  |  |  |  |

| V <sub>IN</sub>   | Input voltage                                     | 10  | -   | 450 | V     | I <sub>cc</sub> = 0 to 1.0mA load                                                                        |  |  |  |  |  |  |

| I <sub>IN</sub>   | Supply current                                    | -   | -   | 2.0 | mA    | No load at $V_{\rm pp}$ .<br>load at $I_{\rm cc}$ = 1.0mA<br>$C_{\rm gT}$ = 500pF, $f_{\rm osc}$ = 25KHz |  |  |  |  |  |  |

| V <sub>DD</sub>   | Internally regulated voltage                      | 8.5 | 9.0 | 9.5 | V     | No load at $V_{DD}$ .<br>$C_{GT} = 500pF$ ,<br>$f_{OSC} = 25KHz$                                         |  |  |  |  |  |  |

| UV <sub>on</sub>  | V <sub>DD</sub> under voltage lockout, on         | 7.8 | 8.2 | 8.5 | V     |                                                                                                          |  |  |  |  |  |  |

| UV <sub>HYS</sub> | V <sub>DD</sub> under voltage lockout, hysteresis | -   | 0.5 | -   | V     |                                                                                                          |  |  |  |  |  |  |

#### Adjustable Regulator

| $V_{cc}$        | Regulator output voltage range | 2.0 | -         | 5.5                   | V  | I <sub>cc</sub> = 1.0mA load |

|-----------------|--------------------------------|-----|-----------|-----------------------|----|------------------------------|

| $I_{cc}$        | Regulator output current       | 0   | -         | 1.0                   | mA | No load at V <sub>DD</sub> * |

| $V_{FB}$        | Feedback voltage               | 0   | $V_{REF}$ | V <sub>DD</sub> -1.0V | V  |                              |

| I <sub>FB</sub> | Input bias current             | -   | 25        | 100                   | nA | $V_{FB} = V_{REF}$           |

<sup>\*</sup> Maximum allowable load current limited by power dissipation and operating ambient temperature.

## **Electrical Characteristics** ( $T_A = +25$ °C unless otherwise noted)

| Sym                     | Parameter                                 | Min                   | Тур   | Max   | Units  | Conditions                                                      |

|-------------------------|-------------------------------------------|-----------------------|-------|-------|--------|-----------------------------------------------------------------|

| Reference               | •                                         |                       |       |       |        |                                                                 |

|                         | Bandgap reference voltage                 | 1.20                  | 1.25  | 1.30  | V      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$             |

| $V_{REF}$               | Load regulation                           | -                     | -     | 7.0   | mV     | 0mA < I <sub>REF</sub> < 0.3mA                                  |

|                         | Line regulation                           | -                     | 10    | 15    | mV     | 8.5V < V <sub>DD</sub> < 9.5V                                   |

| I <sub>REF(SHORT)</sub> | Short circuit current                     | -                     | -     | 1.0   | mA     |                                                                 |

| I <sub>REF(SINK)</sub>  | Reference voltage sink current            | -                     | -     | 20    | μA     |                                                                 |

| Oscillator              |                                           |                       |       |       |        |                                                                 |

| f                       | PW/M oscillator fraguency                 | 20                    | 25    | 35    | kHz    | $R_T = 1.0M\Omega$                                              |

| f <sub>osc</sub>        | PWM oscillator frequency                  | 80                    | 100   | 140   | kHz    | $R_T = 226K\Omega$                                              |

| -                       | Temperature coefficient                   | -                     | 170   | -     | ppm/°C | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$             |

| f <sub>SYNC</sub>       | Oscillator sync frequency                 | -                     | -     | 150   | kHz    |                                                                 |

| I <sub>SYNC</sub>       | Sync input/output sourcing current        | 20                    | -     | 55    | μA     |                                                                 |

| I <sub>SYNC</sub>       | Sync input/output sinking current         | 1.0                   | -     | -     | mA     | V <sub>SYNC</sub> = 0.1V                                        |

| V <sub>SYNC</sub>       | Sync input logic low voltage              | -                     | -     | 1.0   | V      |                                                                 |

| PWM                     |                                           |                       |       |       |        |                                                                 |

| D.                      | Maximum dutu avala                        | 96.5                  | -     | 99.5  | %      | $R_T = 1.0M\Omega$                                              |

| $D_{MAX}$               | Maximum duty cycle                        | 86.5                  | -     | 97.5  | %      | R <sub>T</sub> = 226KΩ                                          |

| t <sub>BLNK</sub>       | Blanking time                             | 150                   | 215   | 280   | ns     |                                                                 |

| MOSFET                  | Driver Output                             |                       |       |       |        |                                                                 |

| $V_{\rm GTH}$           | Gate drive output high                    | V <sub>DD</sub> - 0.3 | -     | -     | V      | I <sub>OUT</sub> = 10mA                                         |

| $V_{\rm GTL}$           | Gate drive output low                     | -                     | -     | 0.30  | V      | I <sub>OUT</sub> = -10mA                                        |

| t <sub>R</sub>          | Rise time                                 | -                     | 30    | 50    | ns     | 0 - 500-5                                                       |

| t <sub>F</sub>          | Fall time                                 | -                     | 30    | 50    | ns     | C <sub>GT</sub> = 500pF                                         |

| Current S               | ensing                                    |                       |       |       |        |                                                                 |

| V <sub>CS(HL)</sub>     | Current sense voltage, high limit         | 0.775                 | 0.833 | 0.891 | V      |                                                                 |

| t <sub>DELAY(HL)</sub>  | Current limit delay to GT, high limit     | -                     | 200   | 250   | ns     | 50mV overdrive                                                  |

| I <sub>cs</sub>         | Input bias current                        | -                     | 25    | 1000  | nA     | POL = Low, ENI = Low                                            |

| V <sub>os</sub>         | Low limit comparator input offset voltage | -                     | -     | ±60   | mV     |                                                                 |

| t <sub>DELAY(LL)</sub>  | Current limit delay to GT, low limit      | -                     | 200   | 250   | ns     | 50mV overdrive                                                  |

| V <sub>HOLD/DEL</sub>   | Hold/delay output voltage                 | V <sub>DD</sub> - 0.4 | -     | -     | V      | I <sub>HOLD/DEL</sub> (sourcing) -100µA<br>POL = Low, ENI = Low |

| I <sub>HOLD/DEL</sub>   | Hold/delay input bias current             | -                     | 25    | 500   | nA     | POL = Low, ENI = Low                                            |

### Electrical Characteristics (T<sub>a</sub> = +25°C unless otherwise noted)

| Sym              | Parameter                    | Min                | Тур  | Max                | Units | Conditions                    |

|------------------|------------------------------|--------------------|------|--------------------|-------|-------------------------------|

| t <sub>ENI</sub> | Shutdown delay               | -                  | 50   | 100                | ns    |                               |

| V                | Enable input voltage - High  | 0.7V <sub>cc</sub> | -    | V <sub>cc</sub>    | V     |                               |

| V <sub>ENI</sub> | Enable input voltage - Low   | 0                  | -    | 0.3V <sub>cc</sub> | V     |                               |

|                  | Enable input current - High  | -                  | 1.0  | 5.0                | μA    |                               |

| I <sub>ENI</sub> | Enable input current - Low   | -5.0               | -1.0 | -                  | μA    |                               |

| \/               | Polarity voltage - High      | 0.7V <sub>cc</sub> | _    | V <sub>cc</sub>    | V     | 2.0V < V <sub>cc</sub> < 5.5V |

| $V_{POL}$        | Polarity voltage - Low       | 0                  | -    | 0.3V <sub>cc</sub> | V     |                               |

| 1                | Polarity current - High      | -                  | 1.0  | 5.0                | μA    |                               |

| POL              | Polarity current - Low       | -5.0               | -1.0 | -                  | μA    |                               |

| \/               | Enable output voltage - High | 0.9V <sub>cc</sub> | -    | V <sub>cc</sub>    | V     |                               |

| V <sub>ENO</sub> | Enable output voltage - Low  | 0                  | _    | 0.1V <sub>cc</sub> | V     |                               |

**Enable Logic Truth Table**

| POL  | ENI  | ENO  | Gate Drive Output                                                          |

|------|------|------|----------------------------------------------------------------------------|

| Low  | Low  | High | V <sub>GT</sub> = Oscillating output, duty cycle depends on inductive load |

| Low  | High | Low  | V <sub>GT</sub> = Low, SYNC = High, oscillator shut down.                  |

| High | High | Low  | V <sub>GT</sub> = Oscillating output, duty cycle depends on inductive load |

| High | Low  | High | V <sub>GT</sub> = Low, SYNC = High, oscillator shut down.                  |

# **Application Information**

$$\begin{split} I_{PULL-IN} &= \frac{V_{CS\,(HL)}}{R_{SENSE}} & V_{CS\,(HI)} = 833 \text{mV nom} \\ V_{CS\,(LL)} &= \frac{V_{DD}}{1 + \frac{R_{HDa}}{R_{HDb}}} & V_{DD} = 9.0 \text{V nom} \\ I_{HOLD} &= \frac{V_{CS\,(LL)}}{R_{SENSE}} \\ t_{PULL-IN} &= -\Big(R_{HDa} \, \Big\| R_{HDb} \, \Big) C_{HD} \, In \Bigg( 1 - \frac{V_{CS\,(HL)} - V_{DD}}{V_{CS\,(LL)} - V_{DD}} \Bigg) \\ f_{PWM} &\approx 3.23 \text{kHz} + \frac{21.8 \text{GHz} \cdot \Omega}{R_{OSC}} \quad \text{(valid for } f_{pwm} > 23 \text{kHz}) \\ V_{CC} &= 1.25 \text{V} \Bigg( 1 + \frac{R_{FBa}}{R_{FBb}} \Bigg) \end{split}$$

Figure 1

## Application Information (cont.)

**Pin Description**

|      | escripti |                                                                                                                                       |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Pin# | Name     | Description                                                                                                                           |

| 1    | VIN      | Input supply.                                                                                                                         |

| 2    | -        | Pin not present                                                                                                                       |

| 3    | -        | Pin not present                                                                                                                       |

| 4    | GT       | Gate driver output for driving the external switching MOSFET.                                                                         |

| 5    | CS       | Current sense input.                                                                                                                  |

| 6    | COM      | Common. Connect to circuit ground.                                                                                                    |

| 7    | SYNC     | Open-drain input/output for synchronizing the internal PWM oscillator to other HV9901s or to an external clock.                       |

| 8    | RT       | A resistor from this pin to ground sets the PWM switching frequency.                                                                  |

| 9    | POL      | Input that determines the polarity of the ENI input. See the truth table.                                                             |

| 10   | ENO      | Enable out. It is the logical inversion of the ENI signal.                                                                            |

| 11   | ENI      | Enabled input. Whether ENI is active low or active high is determined by the POL input.                                               |

| 12   | VCC      | Output of the internal auxiliary regulator. Output voltage is determined by the resistive divider connected to the FB pin.            |

| 13   | FB       | Feedback input for the auxiliary regulator.                                                                                           |

| 14   | H/D      | HOLD/DELAY input. An RC network connected to this pin controls the pull-in time and the holding current. See the equations on page 4. |

| 15   | VREF     | Internal reference voltage. Bypass locally with a 10nF capacitor.                                                                     |

| 16   | VDD      | Output of the internal regulator. Bypass locally with a 10nF capacitor.                                                               |

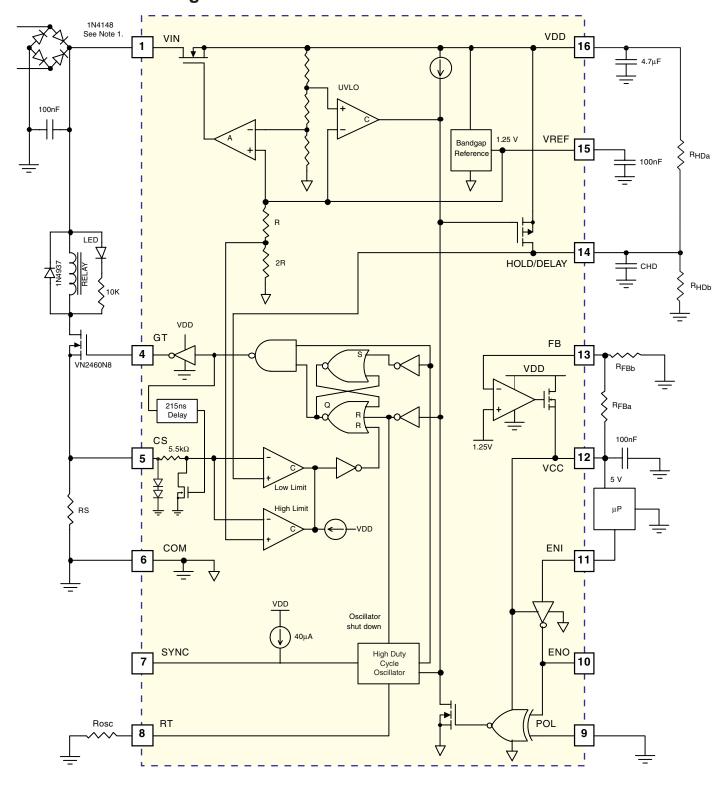

## **Functional Block Diagram**

#### Notes:

- 1. This diode and bridge rectifier required only for AC operation.

- 2. For non-isolated AC operation the entire circuit must be floating.

- 3. All comparators have open drain outputs.

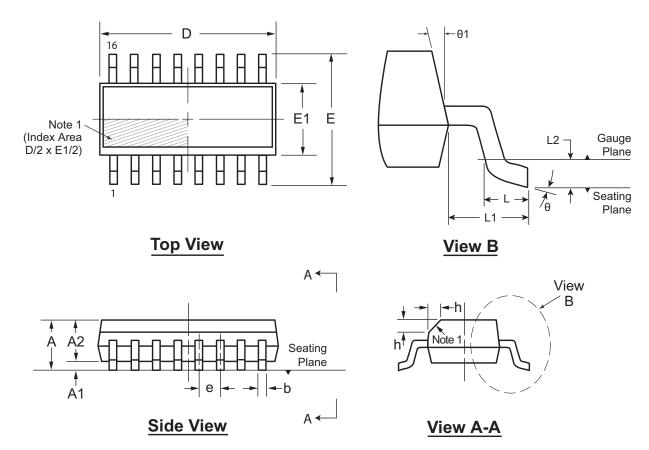

# 16-Lead SOIC (Narrow Body) Package Outline (NG)

9.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

Note 1:

This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier may be either a mold, or an embedded metal or marked feature.

| Symb           | ol  | A     | A1   | A2    | b    | D     | E    | E1   | е           | h    | L    | L1          | L2          | θ          | θ1  |

|----------------|-----|-------|------|-------|------|-------|------|------|-------------|------|------|-------------|-------------|------------|-----|

| <u> </u>       | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 9.80  | 5.80 | 3.80 | 4.07        | 0.25 | 0.40 | 4.04        | 0.05        | <b>0</b> ° | 5°  |

| Dimension (mm) | NOM | -     | -    | -     | -    | 9.90  | 6.00 | 3.90 | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -   |

| (mm)           | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 10.00 | 6.20 | 4.00 | ВОО         | 0.50 | 1.27 | 11          | ВОО         | 8°         | 15° |

JEDEC Registration MS-012, Variation AC, Issue E, Sept. 2005.

Drawings are not to scale.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". **Supertex** does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2008 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

**Supertex** inc. 1235 Bordeaux Drive, Sunnyvale, CA 94089

TEL: (408) 222-8888 / FAX: (408) 222-4895 www.supertex.com

<sup>\*</sup> This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.