### S2S65P10

## Multi Video Input Interlace / Progressive Conversion IC

#### DESCRIPTION

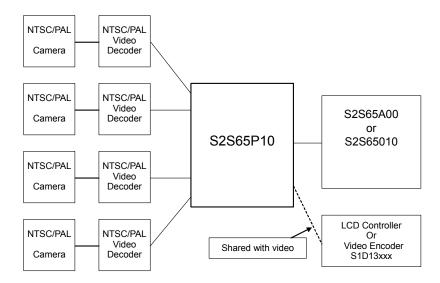

S2S65P10 is an IC which converts the interlace signals into the progressive signals. Combining S2S65P10 with the image controller IC (S2S65A00) or the network camera controller IC (S1S65010) makes it possible to convert the digital signals sent from the NTSC/PAL video decoder into the JPEG format. S2S65P10 has a large-capacity SRAM built in, so it requires no external RAM. S2S65P10 has four channels of video input, and provides versatile screen outputs, including fixed, auto-scan, and 4-input-merge screen outputs. It has also the moving-object detection function built in. It interrupts the host CPU upon detecting a moving object, so it saves power consumption of the system.

#### **■ FEATURES**

Video input

4 ch. for input, out of which 1 ch. is shared with video output.

8-bit input mode

Complies with ITU-R BT.601 (4:2:2) / ITU-R BT.656

Compatible with NTSC/PAL

Compatible with interlace input/progressive input

Video output

2 ch. for input, out of which 1 ch. is shared with video input.

8-bit output mode

Complies with ITU-R BT.601 (4:2:2) / ITU-R BT.656

Compatible with progressive output

30fps@VGA

4 - 1 Intelligent Image Switch function

Compatible with 4-inputs-merged screen (QVGA x 4 = VGA)

Host interface

I<sup>2</sup>C interface

Interrupt by detecting moving object

Image Processing

Interlace/Progressive Conversion

Conversion of aspect ratio

Area sensor (for moving object detection)

- Camera control output/GPIO

- No external RAM required

- Guaranteed operating temperature: -40 +100 °C

- Source Voltages: 1.8 V (core), 2.4 3.6 V (I/O)

- Package: QFP15-100pin (14 x 14 x 1.4 mm, 0.5 mm pin pitch)

#### **■ BLOCK DIAGRAM**

# ■ COMBINING AS A CHIPSET WITH IMAGE CONTROLLER IC (\$2\$65A00) THAT SUPPORT DUAL CAMERA, AND WITH NETWORK CAMERA CONTROLLER IC (\$1C65010)

S2S65P10, combining as a chipset with the image controller IC (S2S65A00) that supports dual camera, can connect with eight camera sets (each consisting of camera module + NTSC/PAL decoder) at the maximum. S2S65P10 can also connect with four camera sets (module + NTSC/PAL decoder) at the maximum by combining as a chipset with the network camera controller IC (S1S65010).

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

©Seiko Epson Corporation 2008, All rights reserved.

#### **SEIKO EPSON CORPORATION**

SEMICONDUCTOR OPERATIONS DIVISION

IC Sales Department

IC International Sales Group

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5117

■ EPSON Electronic devices Website

http://www.epson.jp/device/semicon\_e/

Document code: 411411900 First issue February 2008 in Japan