### S1D13503 Graphics LCD Controller

# S1D13503 TECHNICAL MANUAL

Issue Date: 01/01/30

**Document Number: X18A-Q-001-07**

Copyright © 1997, 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

THIS PAGE LEFT BLANK

S1D13503 Issue Date: 01/01/30

### CUSTOMER SUPPORT INFORMATION

### **Comprehensive Support Tools**

Seiko Epson Corp. provides to the system designer and computer OEM manufacturer a complete set of resources and tools for the development of graphics systems.

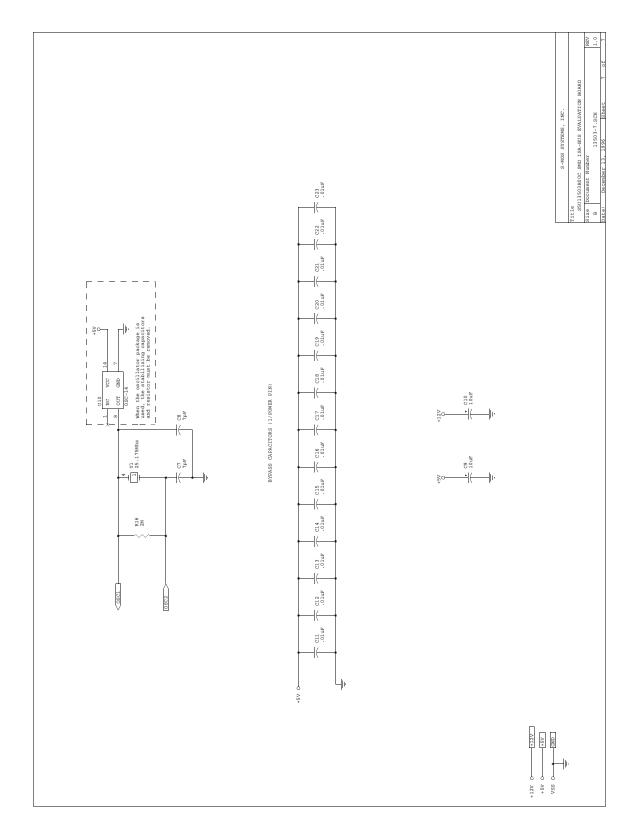

### **Evaluation / Demonstration Board**

- Assembled and fully tested graphics evaluation board with installation guide and schematics

- To borrow an evaluation board, please contact your local Seiko Epson Corp. sales representative

### **VGA Chip Documentation**

• Technical manual includes Data Sheet, Application Notes, and Programmer's Reference

#### Software

- · Video BIOS

- OEM Utilities

- User Utilities

- Evaluation Software

- To obtain these programs, contact Application Engineering Support

### **Application Engineering Support**

Engineering and Sales Support is provided by:

#### Japan

Seiko Epson Corporation Electronic Devices Marketing Division 421-8, Hino, Hino-shi Tokyo 191-8501, Japan Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp

#### **Hong Kong**

Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346

#### **North America**

Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com

### **Europe**

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110

#### Taiwan, R.O.C.

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan, R.O.C. Tel: 02-2717-7360 Fax: 02-2712-9164

### Singapore

Epson Singapore Pte., Ltd. No. 1 Temasek Avenue #36-00 Millenia Tower Singapore, 039192 Tel: 337-7911 Fax: 334-2716

Issue Date: 01/01/30 S1D13503

THIS PAGE LEFT BLANK

S1D13503 Issue Date: 01/01/30

### TABLE OF CONTENTS

### INTRODUCTION

S1D13503 Graphics LCD Controller Data Sheet

#### **SPECIFICATION**

S1D13503 Hardware Functional Specification

### PROGRAMMER'S REFERENCE

S1D13503 Programming Notes and Examples

### **UTILITIES**

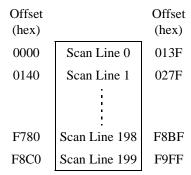

13503SHOW.EXE Display Utility

13503VIRT.EXE Display Utility

13503BIOS.COM Display Utility

13503MODE.EXE Display Utility

13503PD.EXE Power Down Utility

13503READ.EXE Diagnostic Utility

### **EVALUATION**

S5U13503B00C Rev 1 Evaluation Board User Manual

### **APPLICATION NOTES**

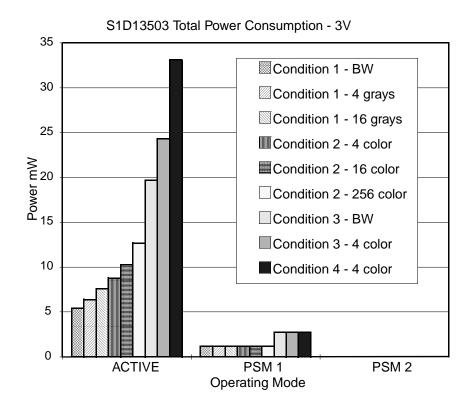

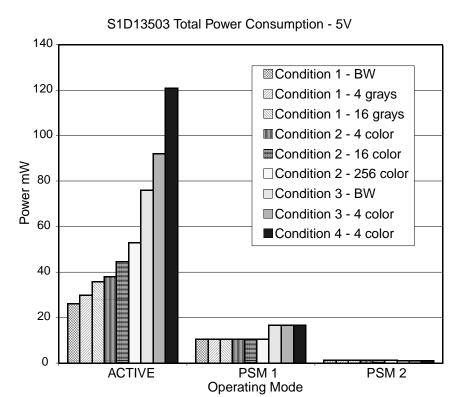

**Power Consumption**

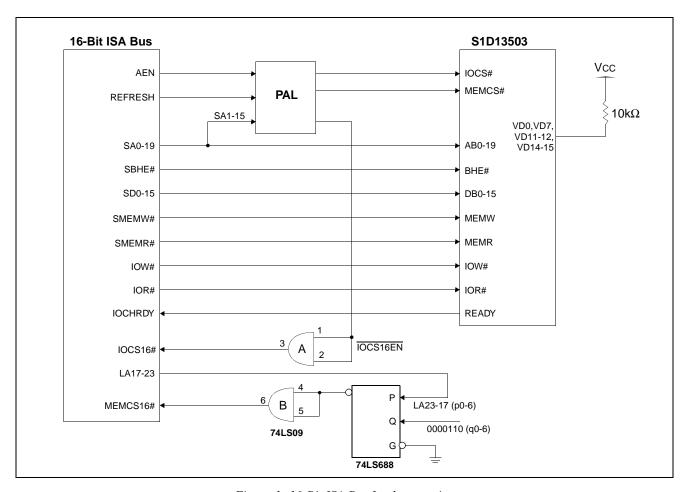

ISA Bus Interface Considerations

MC68340 Interface Considerations

LCD Panel Options/Memory Requirements

S1D13503/S1D13502 Feature Comparison

Issue Date: 01/01/30 S1D13503

THIS PAGE LEFT BLANK

S1D13503 Issue Date: 01/01/30

# GRAPHICS S1D13503

January 2001

### S1D13503 GRAPHICS LCD CONTROLLER

### DESCRIPTION

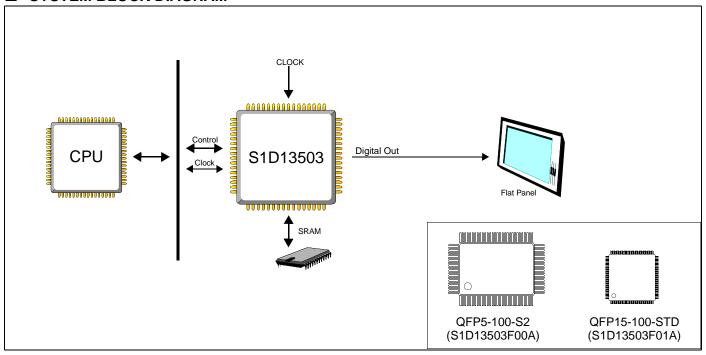

The S1D13503 is a dot matrix graphic LCD controller supporting resolutions up to 1024x1024. It is capable of displaying a maximum of 256 simultaneous colors out of a possible 4096 or 16 gray shades. Design flexibility allows the S1D13503 to interface to either an MC68000 family microprocessor or an 8/16-bit MPU/bus with minimum external logic. The Static RAM (SRAM) interface used for the display buffer is optimized for speed and performance, supporting up to 128K bytes.

Two power save modes, combined with operating voltages of 2.7 volts through 5.5 volts, allow for a wide range of applications while providing minimum power consumption.

#### **■** FEATURES

### **CPU Interface**

- Pin compatible with the S1D13502.

- 16-bit 16 MHz MC68xxx MPU interface.

- 8/16-bit MPU interface controlled by a READY (or WAIT#) signal.

- Option to use built-in index register or direct-mapping to access one of sixteen internal registers.

### **Memory Interface**

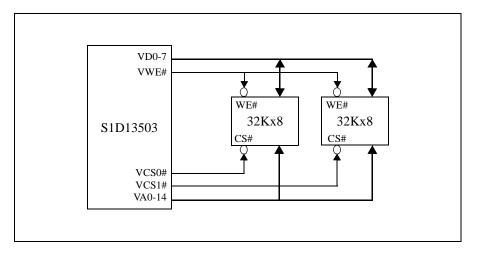

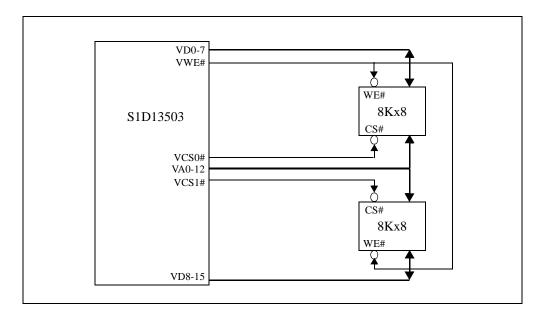

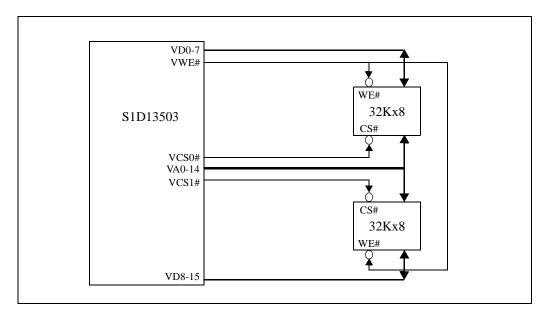

8/16-bit SRAM interface configurations:

128K bytes using one 64Kx16 SRAMs.

128K bytes using two 64Kx8 SRAMs.

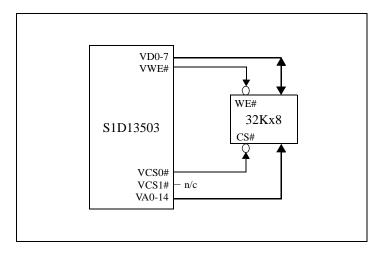

64K bytes using two 32Kx8 SRAMs.

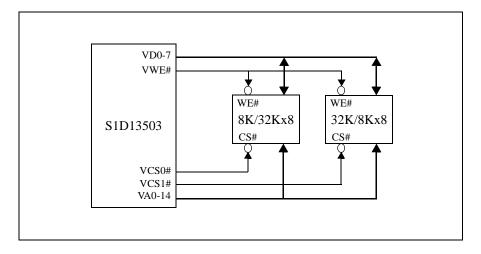

40K bytes using one 8Kx8 and one 32Kx8

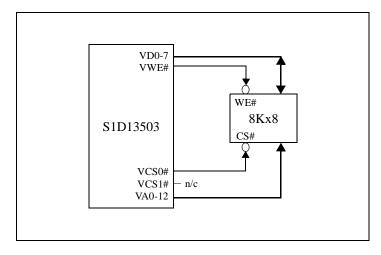

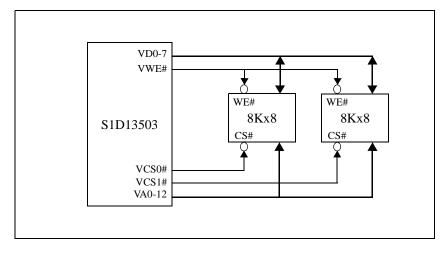

32K bytes using one 32Kx8 SRAM. 16K bytes using two 8Kx8 SRAMs. 8K bytes using one 8Kx8 SRAM.

### **Display Modes**

- Black-and-white display.

- 2/4 bits-per-pixel, 4/16-level gray-scale display.

- 2/4/8 bits-per-pixel, 4/16/256-level color display.

### **Display Support**

- Single-panel, single-drive passive display. Dual-panel, dual-drive passive display.

- Maximum number of vertical lines:

1,024 lines (single-panel, single-drive display).

2,048 lines (dual-panel, dual-drive display).

- Split screen display support allowing two different images to be simultaneously displayed.

- Virtual display support (displays images larger than the panel size through the use of panning).

### **Clock Source**

2-terminal crystal or external oscillator.

### **Power Down Modes**

- Low power consumption.

- Two software power-save modes.

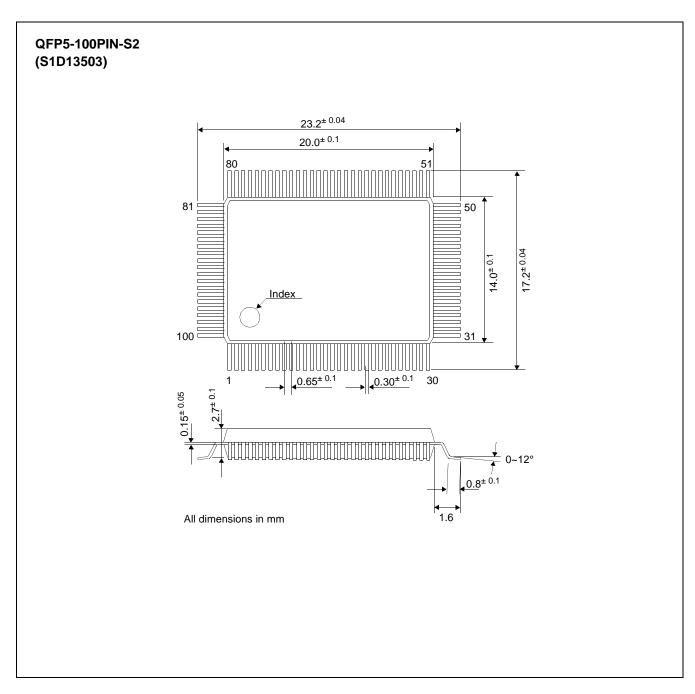

### **Package**

- QFP5-100-S2 package (F00A).

- QFP15-100-STD package (F01A).

# **EPSON**<sup>®</sup>

### S1D13503

### ■ SYSTEM BLOCK DIAGRAM

# CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS:

- S1D13503 Technical Manual

- S5U13503 Evaluation Boards

- CPU Independent Software Utilities

#### Japan

Seiko Epson Corporation Electronic Devices Marketing Division 421-8, Hino, Hino-shi Tokyo 191-8501, Japan

Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp

### **Hong Kong**

Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346

### North America

Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com

#### Europe

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110

### Taiwan

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan Tel: 02-2717-7360 Fax: 02-2712-9164

### Singapore

No. 1 Temasek Avenue #36-00 Millenia Tower Singapore, 039192

Epson Singapore Pte., Ltd.

Tel: 337-7911 Fax: 334-2716

Copyright ©1997, 2001 Epson Research and Development, Inc. All rights reserved.

VDC Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. Microsoft and Windows are registered trademarks of Microsoft Corporation.

X18A-C-002-03

### S1D13503 Dot Matrix Graphics Color LCD Controller

# **Hardware Functional Specification**

**Document Number: X18A-A-001-08**

$\label{lem:copyright @ 1997, 2001} \textbf{Epson Research and Development, Inc. All Rights Reserved.}$

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

THIS PAGE LEFT BLANK

### **Table of Contents**

| 1 | INTRODUCTION                                            | . 9  |

|---|---------------------------------------------------------|------|

|   | 1.1 Scope                                               | 9    |

|   | 1.2 Overview Description                                | 9    |

| 2 | FEATURES                                                | 10   |

|   | 2.1 Technology                                          | . 10 |

|   | 2.2 System                                              | . 10 |

|   | 2.3 Display Modes                                       | . 10 |

|   | 2.4 Display Support                                     | . 11 |

|   | 2.5 Power Management                                    | . 11 |

| 3 | TYPICAL SYSTEM BLOCK DIAGRAMS                           | 12   |

|   | 3.1 16-Bit MC68000 MPU                                  | . 12 |

|   | 3.2 MPU with READY (or WAIT#) signal                    | . 13 |

|   | 3.3 ISA Bus                                             | . 14 |

|   | 3.4 Internal Block Diagram                              | . 15 |

|   | 3.5 Functional Block Descriptions                       | . 15 |

|   | 3.5.1 Bus Signal Translation                            |      |

|   | 3.5.2 Control Registers                                 |      |

|   | 3.5.3 Sequence Controller                               |      |

|   | 3.5.4 LCD Panel Interface                               |      |

|   | 3.5.5 Look-Up Table                                     |      |

|   | 3.5.6 Port Decoder                                      |      |

|   | 3.5.7 Memory Decoder                                    |      |

|   | 3.5.8 Data Bus Conversion                               |      |

|   | 3.5.9 Address Generator                                 |      |

|   | 3.5.10 MPU / CRT Selector                               |      |

|   | 3.5.12 Clock Inputs / Timing                            |      |

|   | 3.5.13 SRAM Interface                                   |      |

|   |                                                         |      |

| 4 | PINOUT DIAGRAM                                          | 17   |

| 5 | PIN DESCRIPTION                                         |      |

|   | 5.1 Description                                         |      |

|   | 5.2 Summary of Configuration Options                    | . 26 |

| 6 | D.C. CHARACTERISTICS                                    | 27   |

| 7 | A.C. CHARACTERISTICS                                    | 29   |

|   | 7.1 Bus Interface Timing                                | . 29 |

|   | 7.1.1 MC68000 Interface Timing                          |      |

|   | 7.1.2 Non-MC68000, MPU/Bus With READY (or WAIT#) Signal |      |

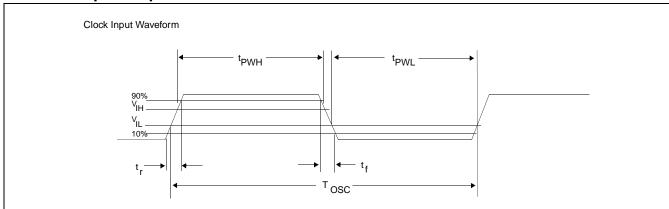

|   | 7.2 Clock Input Requirements                            | . 37 |

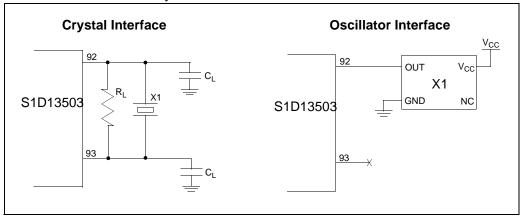

|   | 7.2.1 Recommended Clock Input                           | . 38 |

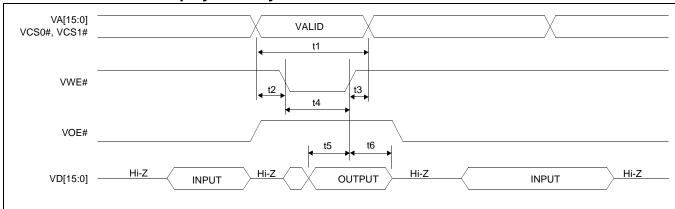

|    | 7.3 E | Display Memory Interface Timing                                                        |

|----|-------|----------------------------------------------------------------------------------------|

|    | 7.3.  | 1 Write Data to Display Memory                                                         |

|    | 7.3.  | 2 Read Data From Display Memory                                                        |

|    | 7.4 L | CD Interface                                                                           |

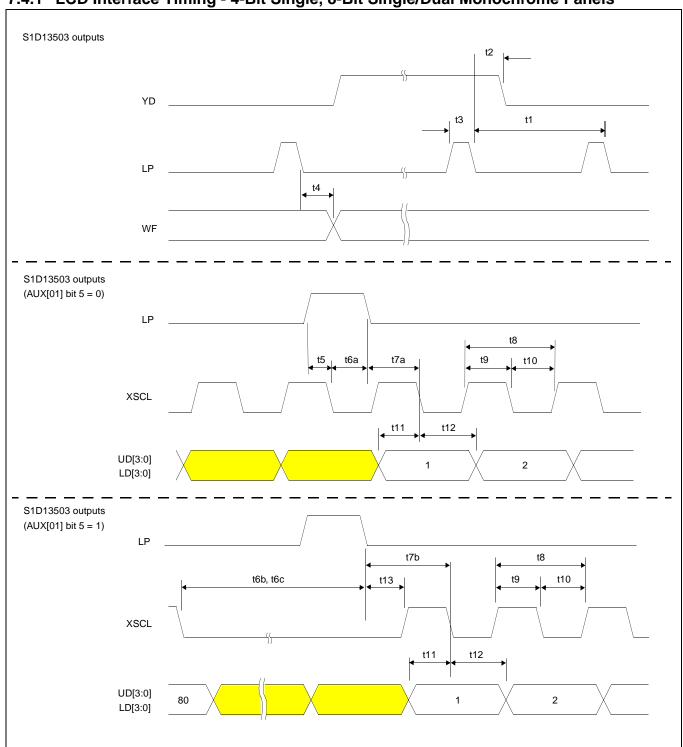

|    | 7.4.  | 1 LCD Interface Timing - 4-Bit Single, 8-Bit Single/Dual Monochrome Panels 41          |

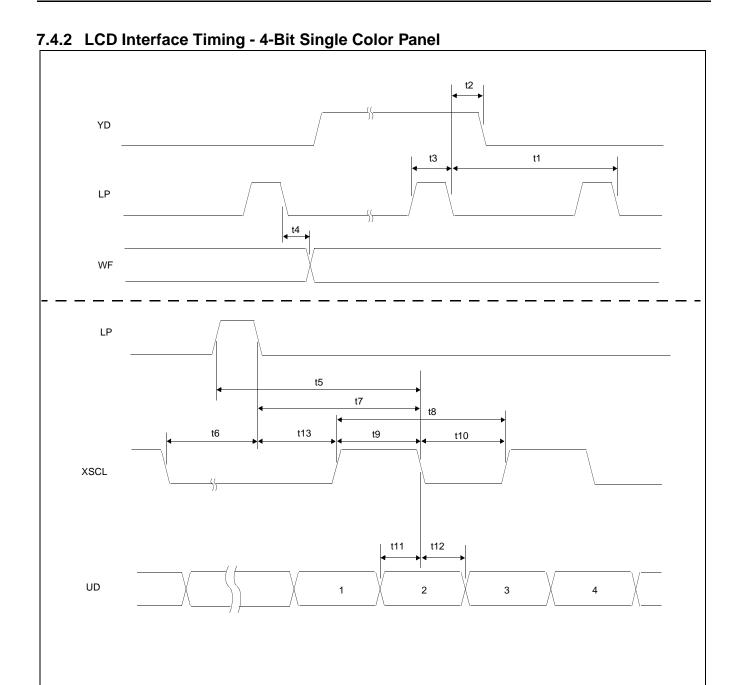

|    | 7.4.  | 2 LCD Interface Timing - 4-Bit Single Color Panel                                      |

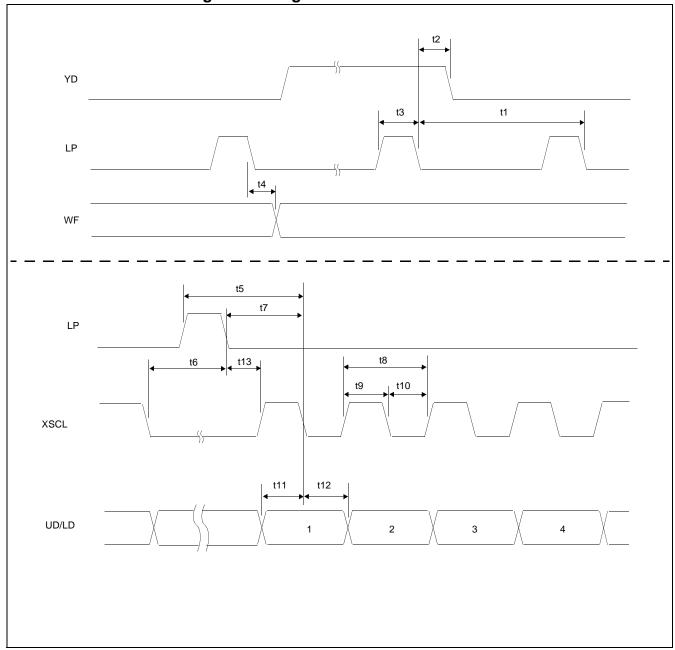

|    | 7.4.  | 3 LCD Interface Timing - 8-Bit Single Color Panels Format 2/8-Bit Dual Color Panels 46 |

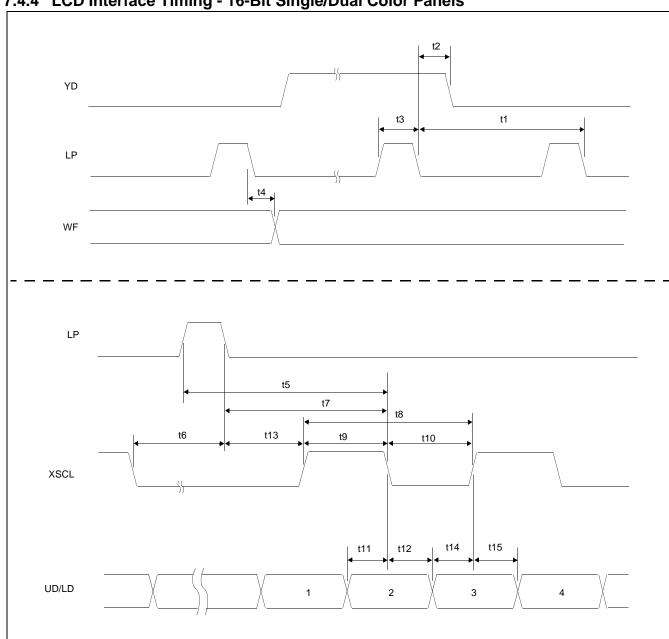

|    | 7.4.  | 4 LCD Interface Timing - 16-Bit Single/Dual Color Panels                               |

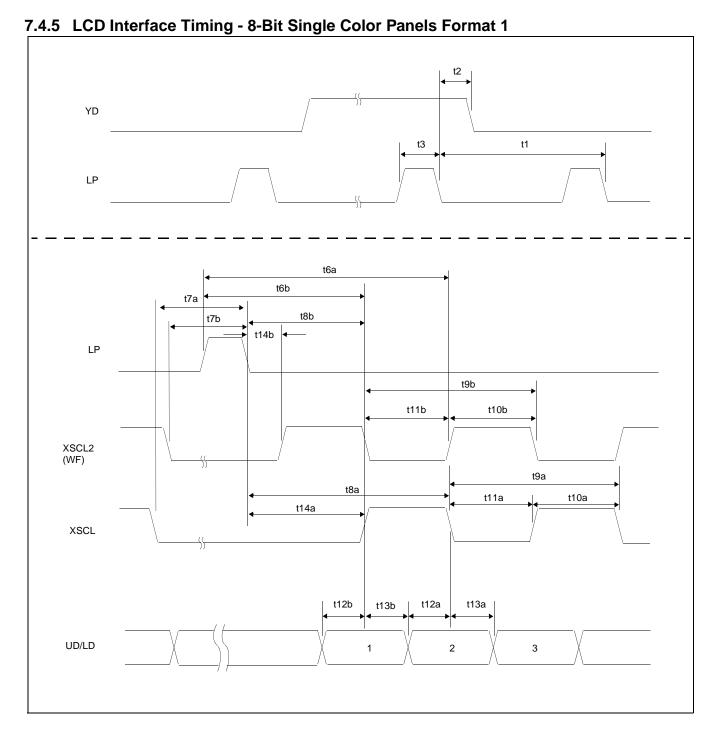

|    |       | 5 LCD Interface Timing - 8-Bit Single Color Panels Format 1                            |

|    | 7.4.  | 6 LCD Interface Options                                                                |

| 8  | HARD  | WARE REGISTER INTERFACE                                                                |

|    | 8.1 R | Legister Descriptions                                                                  |

|    | 8.2 L | ook-Up Table Architecture                                                              |

|    | 8.2.  | 1 Gray Shade Display Modes                                                             |

|    | 8.2.  | 2 Color Display Modes                                                                  |

|    | 8.3 P | ower Save Modes                                                                        |

|    | 8.3.  | 1 Power Save Mode 1                                                                    |

|    | 8.3.  | 2 Power Save Mode 2                                                                    |

|    |       | 3 Power Save Mode Function Summary                                                     |

|    | 8.3.  | 4 Pin States in Power Save Modes                                                       |

| 9  | DISPL | AY MEMORY INTERFACE                                                                    |

|    | 9.1 S | RAM Configurations Supported                                                           |

|    | 9.1.  | 1 8-Bit Mode                                                                           |

|    | 9.1.  | 2 16-bit Mode                                                                          |

|    | 9.2 S | RAM Access Time                                                                        |

|    | 9.2.  | 1 8-bit Display Memory Interface:                                                      |

|    | 9.2.  | 2 16-bit Display Memory Interface:                                                     |

|    | 9.3 F | rame Rate Calculation                                                                  |

|    | 9.3.  | 1 For single panel                                                                     |

|    | 9.3.  | 2 For dual panel                                                                       |

|    | 9.4 N | Memory Size Calculation                                                                |

|    | 9.5 N | Memory Size Requirement                                                                |

| 10 | MECH  | ANICAL DATA                                                                            |

### **List of Tables**

| Table 4-1:  | PAD Coordinates                                                                   | . 20 |

|-------------|-----------------------------------------------------------------------------------|------|

| Table 5-1:  | Bus Interface                                                                     | . 22 |

| Table 5-2:  | Display Memory Interface                                                          | .24  |

| Table 5-3:  | LCD Interface                                                                     | . 25 |

| Table 5-4:  | Clock Inputs                                                                      | . 25 |

| Table 5-5:  | Power Supply                                                                      | .25  |

| Table 5-6:  | Summary of Power On / Reset Options                                               | .26  |

| Table 5-7:  | I/O and Memory Addressing Example                                                 | .26  |

| Table 6-1:  | Absolute Maximum Ratings                                                          | .27  |

| Table 6-2:  | Recommended Operating Conditions                                                  | .27  |

| Table 6-3:  | Input Specifications                                                              | .27  |

| Table 6-4:  | Output Specifications                                                             | .28  |

| Table 7-1:  | IOW# Timing (MC68000)                                                             | .29  |

| Table 7-2:  | IOR# Timing (MC68000)                                                             | .30  |

| Table 7-3:  | MEMW# Timing (MC68000)                                                            | .31  |

| Table 7-4:  | MEMR# Timing (MC68000)                                                            | .32  |

| Table 7-5:  | IOW# Timing (Non-MC68000)                                                         | .33  |

| Table 7-6:  | IOR# Timing (Non-MC68000)                                                         | .34  |

| Table 7-7:  | MEMW# Timing (Non-MC68000)                                                        | .35  |

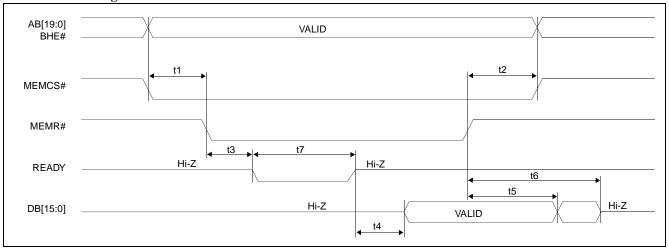

| Table 7-8:  | MEMR# Timing (Non-MC68000)                                                        | .36  |

| Table 7-9:  | Clock Input Requirements                                                          | .37  |

| Table 7-10: | Write Data to Display Memory                                                      | .39  |

| Table 7-11: | Read Data From Display Memory                                                     | .40  |

| Table 7-12: | LCD Interface Timing - 4-Bit Single and 8-Bit Single/Dual Monochrome Panel        | .42  |

| Table 7-13: | LCD Interface Timing - 4-Bit Single Color Panel                                   | .45  |

| Table 7-14: | LCD Interface Timing - 8-Bit Single Color Panels Format 2/8-Bit Dual Color Panels | . 47 |

| Table 7-15: | LCD Interface Timing - 16-Bit Single/Dual Color Panels                            | .49  |

| Table 7-16: | LCD Interface Timing - 8-Bit Single Color Panels Format 1                         | .51  |

| Table 8-1:  | Gray Shade/Color Mode Selection                                                   | .62  |

| Table 8-2:  | LCD Data Width                                                                    | . 63 |

| Table 8-3:  | Maximum Value of Line Byte Count Register - 8-Bit Display Memory Interface        | . 64 |

| Table 8-4:  | Maximum Value of Line Byte Count Register - 16-Bit Display Memory Interface       | . 64 |

| Table 8-5:  | Power Save Mode Selection                                                         | .64  |

| Table 8-6:  | ID Bit Usage                                                                      | .70  |

| Table 8-7:  | Look-Up Table Access                                                              | .70  |

| Table 8-8:  | Look-Up Table Configurations                                                      | .72  |

| Table 8-9:  | Power Save Mode Selection                                                         | .77  |

| Table 8-10: | Power Save Mode Function Summary                                                  | .78  |

| Table 8-11: | Pin States in Power Save Modes                                                    | .78  |

| Table 9-1:  | 8-Bit Display Memory Interface SRAM Access Time                                   | .83  |

| Table 9-2:  | 16-Bit Display Memory Interface SRAM Access Time                                  |      |

| Table 9-3:  | Memory Size Requirement: Number of Horizontal Pixels = 640                        |      |

| Table 9-4:  | Memory Size Requirement: Number of Horizontal Pixels = 480                        |      |

| Table 9-5:  | Memory Size Requirement: Number of Horizontal Pixels = 320                        |      |

|             |                                                                                   |      |

THIS PAGE LEFT BLANK

### **List of Figures**

| Figure 1:  | 16-Bit 68000 Series                                                               |

|------------|-----------------------------------------------------------------------------------|

| Figure 2:  | 8-Bit Mode, Example: Z80                                                          |

| Figure 3:  | 16-Bit Mode, Example: i8086 (maximum mode)                                        |

| Figure 4:  | 8-Bit Mode (ISA)                                                                  |

| Figure 5:  | 16-Bit Mode (ISA)                                                                 |

| Figure 6:  | Internal Block Diagram                                                            |

| Figure 7:  | S1D13503 Pinout Diagram                                                           |

| Figure 8:  | S1D13503 Pinout Diagram                                                           |

| Figure 9:  | S1D13503 Pad Diagram                                                              |

| Figure 10: | IOW# Timing (MC68000)                                                             |

| Figure 11: | IOR# Timing (MC68000)                                                             |

| Figure 12: | MEMW# Timing (MC68000)                                                            |

| Figure 13: | MEMR# Timing (MC68000)                                                            |

| Figure 14: | IOW# Timing (Non-MC68000)                                                         |

| Figure 15: | IOR# Timing (Non-MC68000)                                                         |

| Figure 16: | MEMW# Timing (Non-MC68000)                                                        |

| Figure 17: | MEMR# Timing (Non-MC68000)                                                        |

| Figure 18: | Clock Input Requirements                                                          |

| Figure 19: | Recommended Clock Interface                                                       |

| Figure 20: | Write Data to Display Memory                                                      |

| Figure 21: | Read Data From Display Memory                                                     |

| Figure 22: | LCD Interface Timing - Monochrome Panel                                           |

| Figure 23: | LCD Interface Timing - 4-Bit Single Color Panel                                   |

| Figure 24: | LCD Interface Timing - 8-Bit Single Color Panels Format 2/8-Bit Dual Color Panels |

| Figure 25: | LCD Interface Timing - 16-Bit Single/Dual Color Panels                            |

| Figure 26: | LCD Interface Timing - 8-Bit Single Color Panels Format 1                         |

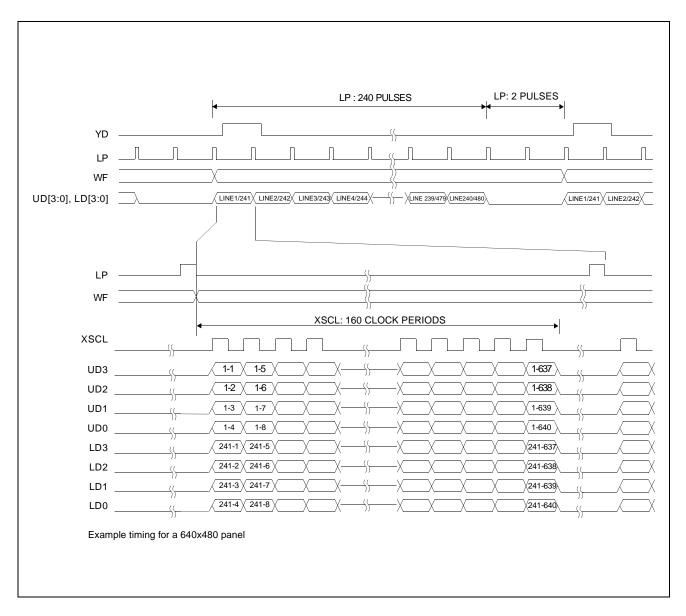

| Figure 27: | 4-Bit Single Monochrome Panel Timing                                              |

| Figure 28: | 8-Bit Single Monochrome Panel Timing                                              |

| Figure 29: | 8-Bit Dual Monochrome Panel Timing                                                |

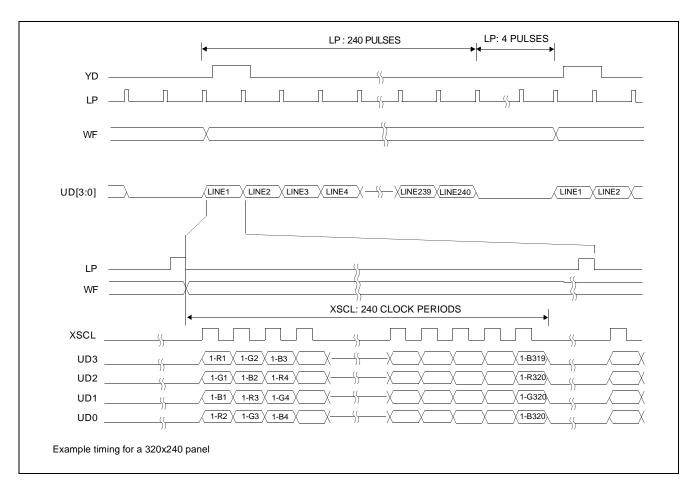

| Figure 30: | 4-Bit Single Color Panel Timing                                                   |

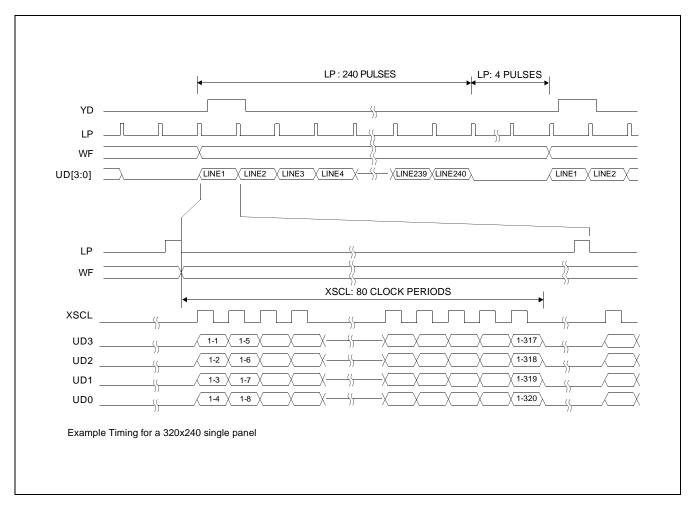

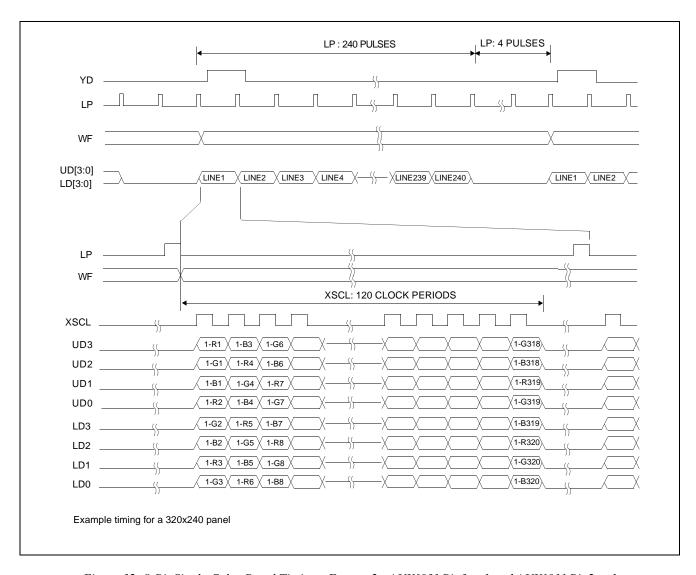

| Figure 31: | 8-Bit Single Color Panel Timing - Format 1                                        |

| Figure 32: | 8-Bit Single Color Panel Timing - Format 2                                        |

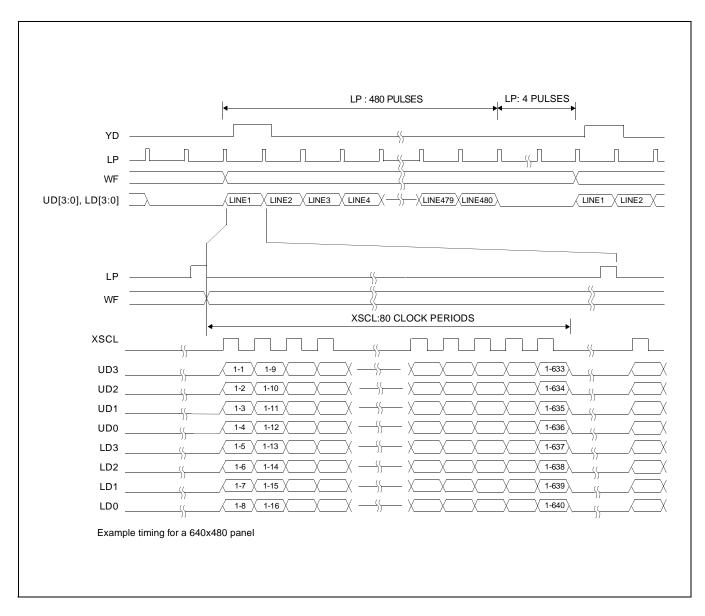

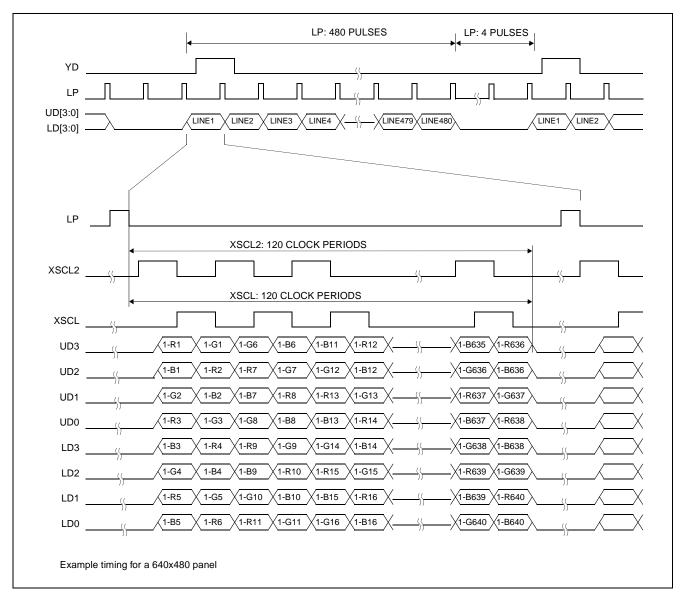

| Figure 33: | 8-Bit Dual Color Panel Timing                                                     |

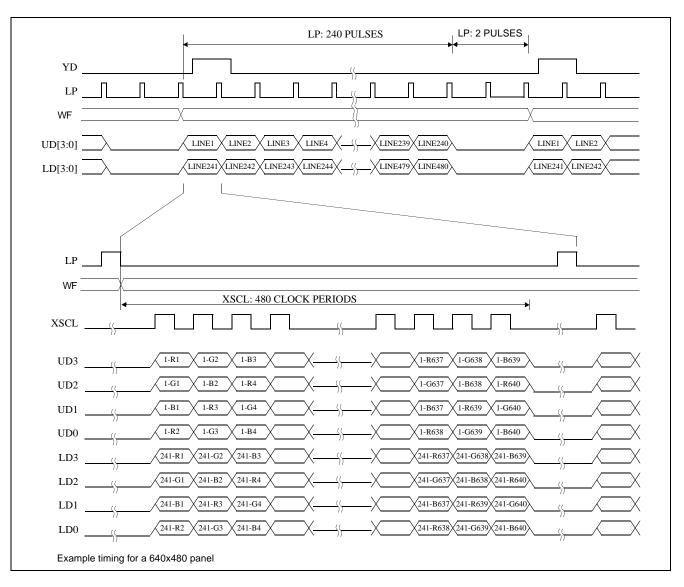

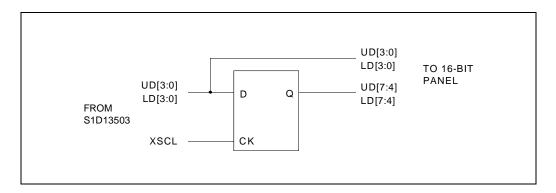

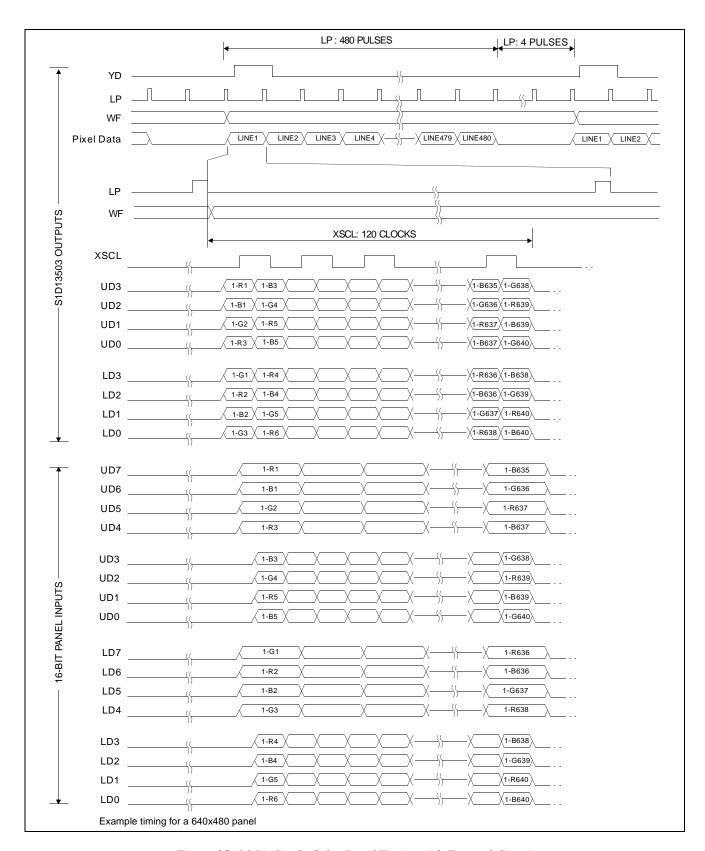

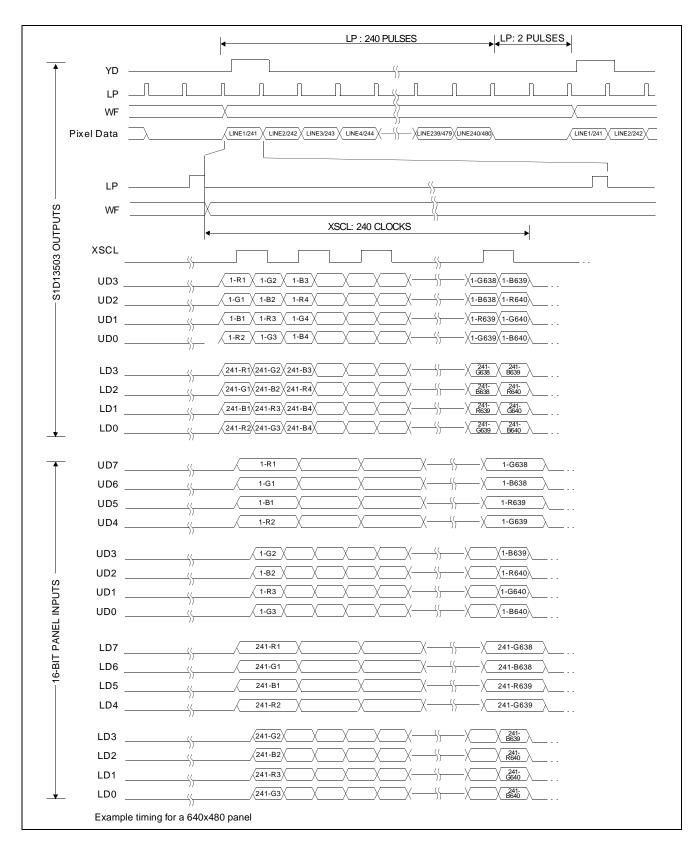

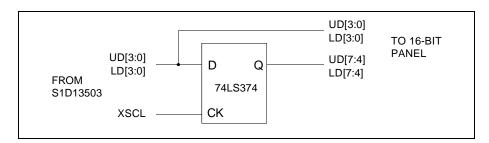

| Figure 34: | External Circuit Required for 16-Bit Panel                                        |

| Figure 35: | 16-Bit Single Color Panel Timing with External Circuit                            |

| Figure 36: | 16-Bit Dual Color Panel Timing with External Circuit                              |

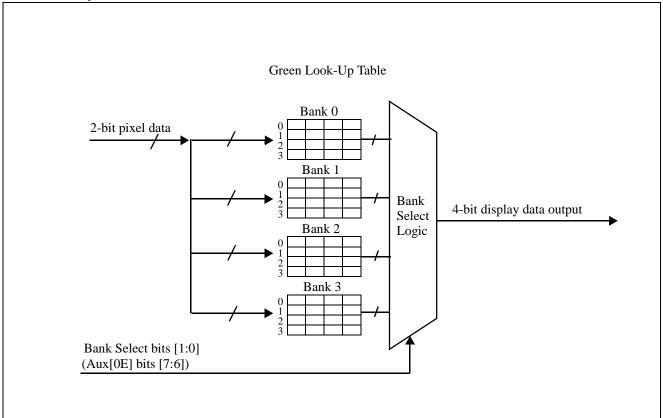

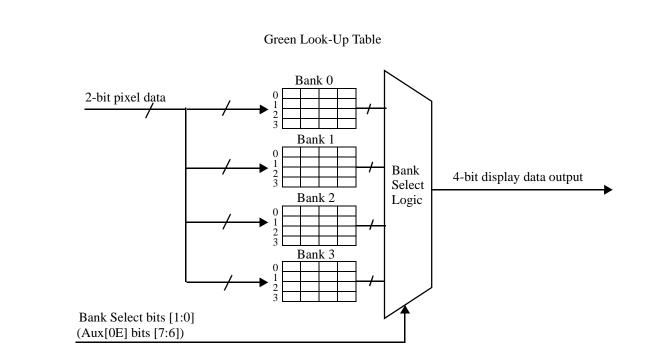

| Figure 37: | 4-Level Gray-Shade Mode Look-Up Table Architecture  |

|------------|-----------------------------------------------------|

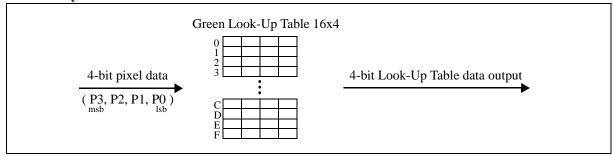

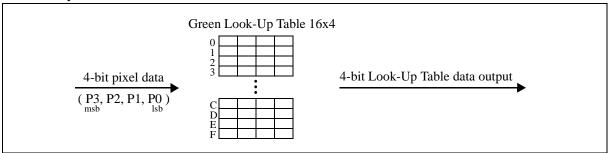

| Figure 38: | 16-Level Gray-Shade Mode Look-Up Table Architecture |

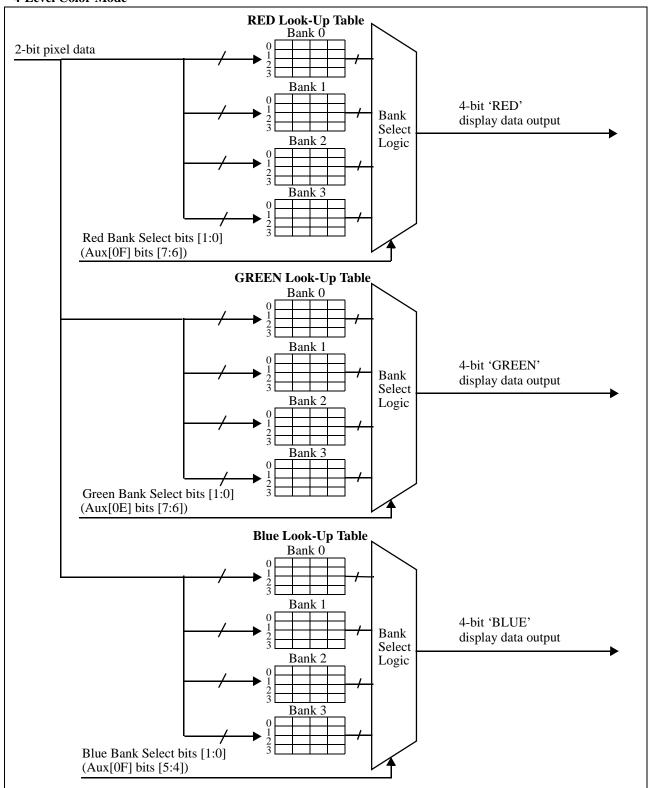

| Figure 39: | 4-Level Color Mode Look-Up Table Architecture       |

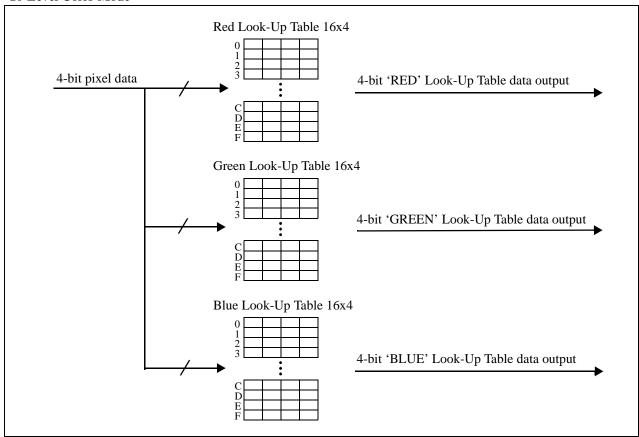

| Figure 40: | 16-Level Color Mode Look-Up Table Architecture      |

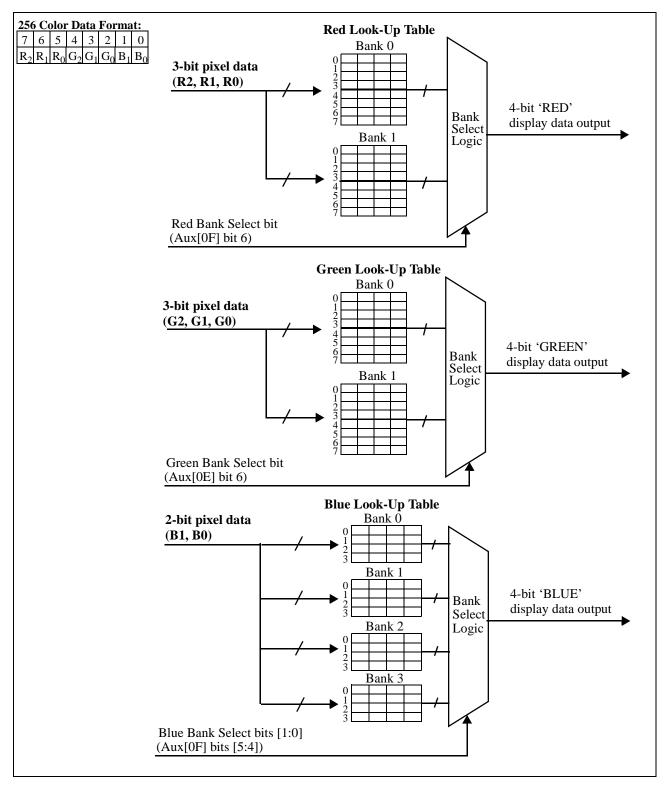

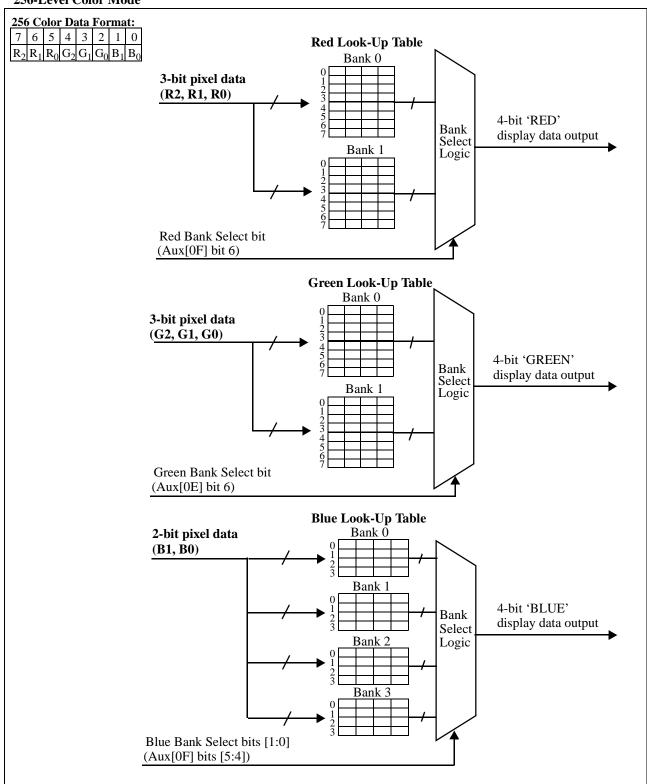

| Figure 41: | 256-Level Color Mode Look-Up Table Architecture     |

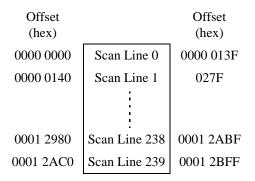

| Figure 42: | 8-Bit Mode - 8K bytes SRAM                          |

| Figure 43: | 8-Bit Mode - 16K bytes SRAM                         |

| Figure 44: | 8-Bit Mode - 32K bytes SRAM                         |

| Figure 45: | 8-Bit Mode - 40K bytes SRAM                         |

| Figure 46: | 8-Bit Mode - 64K bytes SRAM                         |

| Figure 47: | 16-Bit Mode - 16K bytes SRAM                        |

| Figure 48: | 16-Bit Mode - 64K bytes SRAM                        |

| Figure 49: | 16-Bit Mode - 128K bytes SRAM                       |

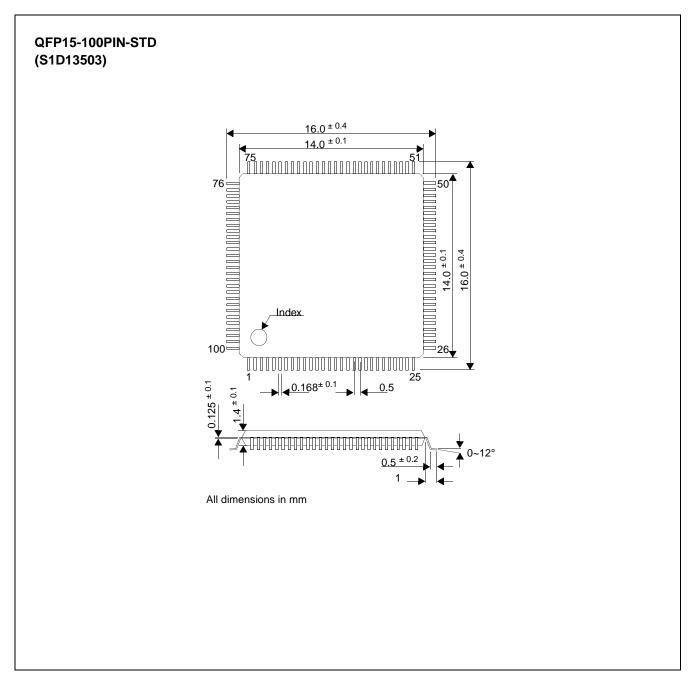

| Figure 50: | Mechanical Drawing QFP5-100-S2 (S1D13503)           |

| Figure 51: | Mechanical Drawing QFP15-100-STD (S1D13503)         |

### 1 INTRODUCTION

### 1.1 Scope

This is the Functional Specification for the S1D13503 Dot Matrix Graphic Color LCD Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences, Video Subsystem Designers and Software Developers.

### 1.2 Overview Description

This device is designed for products where low cost, low power consumption, and low component count are the major design considerations. This chip operates from 2.7 Volts to 5.5 Volts and up to 25MHz to suit different power consumption, speed and cost requirements. The S1D13503 offers a flexible microprocessor interface, and is pin compatible with the S1D13502 within the same package types (e.g. the 13503D0A is pin compatible with the 13502; the 13503 is pin compatible with the 13502).

The S1D13503 is capable of displaying a maximum of 16 levels of gray shade or 256 simultaneous colors. In gray shade modes, a 16x4 Look-Up Table is provided to allow remapping of the 16 possible gray shades displayed on the LCD panel. In color modes, three 16x4 Look-Up Tables are provided to allow remapping of the 4096 possible colors displayed on the LCD panel. The S1D13503S1D13503 can interface to an MC68000 family microprocessor or an 8/16-bit MPU/Bus with minimum external "glue" logic. This device can directly control up to 128K bytes of static RAM with a 16-bit data path, or up to 64K bytes with an 8-bit data path.

Hardware Functional Specification Issue Date: 01/01/29

### 2 FEATURES

### 2.1 Technology

- low power CMOS

- 2.7 to 5.5 volt operation

- 100 pin QFP5-S2 surface mount package

- 100 pin QFP15-STD surface mount package

### 2.2 System

- maximum 25 MHz input clock (or pixel clock)

- 2-terminal crystal input for internal oscillator or direct connection to external clock source

- maximum 16 MHz, 16-bit MC68000 MPU interface

- 8-bit or 16-bit MPU/Bus interface with memory accesses controlled by a READY (or WAIT#) signal

- option to use built-in index register or direct-mapping to access one of sixteen internal registers

- 8-bit or 16-bit SRAM data bus interface configurations

- display memory configurations :

- 128k bytes using one 64Kx16 SRAM

- 128k bytes using two 64Kx8 SRAMs

- 64k bytes using two 32Kx8 SRAMs

- 40k bytes using one 8Kx8 and one 32Kx8 SRAM

- 32k bytes using one 32Kx8 SRAM

- 16k bytes using two 8Kx8 SRAMs

- 8k bytes using one 8Kx8 SRAM

### 2.3 Display Modes

- 1 bit-per-pixel, black-and-white display mode

- 2/4 bits-per-pixel, 4/16 level gray shade display modes

- 2/4/8 bits-per-pixel, 4/16/256 level color display modes

- one 16x4 Look-Up Table provided for gray shade display modes

- three 16x4 Look-Up Tables provided for color display modes

- maximum 16 shades of gray

- maximum 256 simultaneous colors from a possible 4096 colors

- split screen display mode (see AUX[0A])

- virtual display mode (see AUX[0D])

#### Note

256 color display mode support requires a 16-bit display memory interface

### 2.4 Display Support

- example resolutions:

- 1024 x 768 black-and-white

- 640 x 480 with 4 colors/grays

- 640 x 400 with 16 colors/grays

- 320 x 240 with 256 colors

- passive monochrome LCD panels:

- 4-bit single (4-bit data transfer)

- 8-bit single (8-bit data transfer)

- 8-bit dual (4-bit data transfer for each half panel)

- passive color LCD panels:

- 4-bit single (4-bit data transfer)

- 8-bit single (8-bit data transfer)

- 8-bit dual (4-bit data transfer for each half panel)

- 16-bit single (8-bit data transfer with external circuit)

- 16-bit dual (8-bit data transfer with external circuit)

See Section 9.5 on page 85 for complete details

### 2.5 Power Management

- two software power-save modes

- · low power consumption

- panel power control switch (see AUX[01] bit 4)

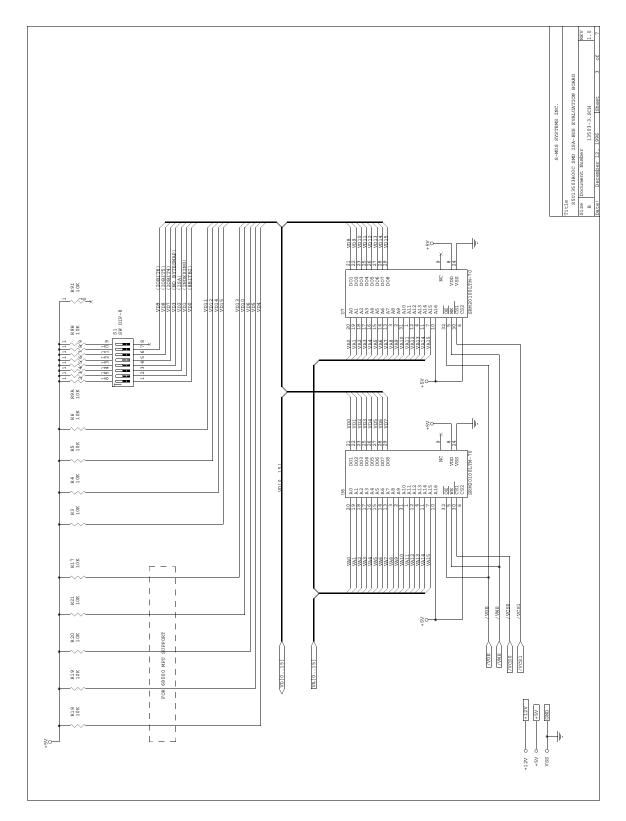

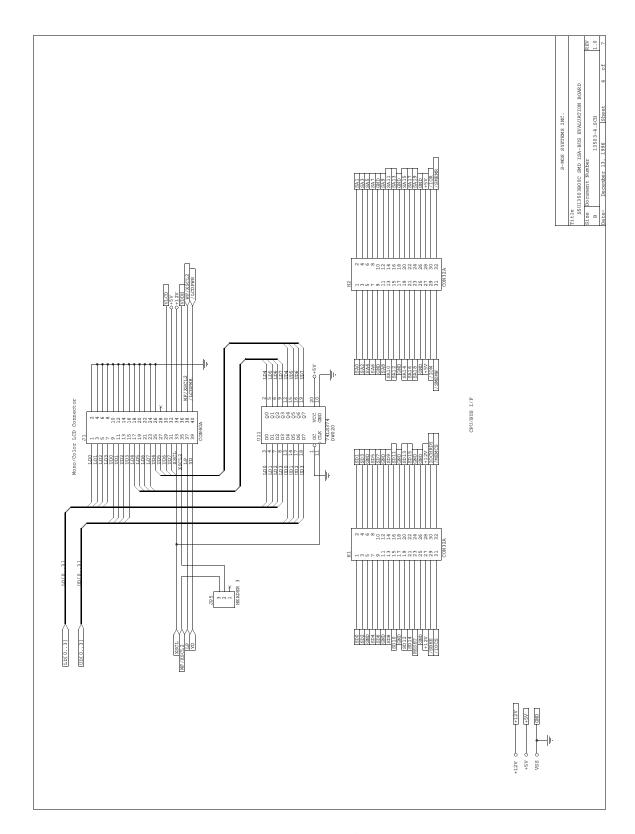

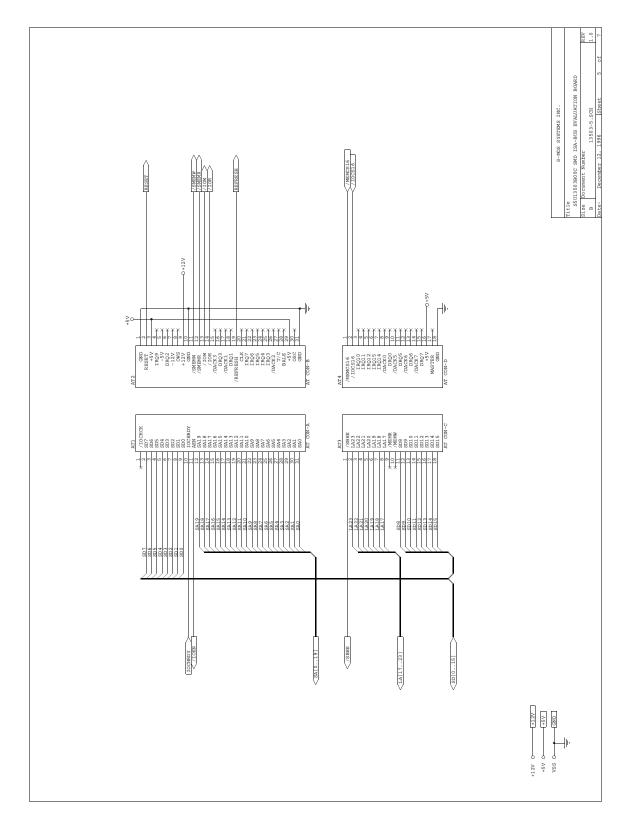

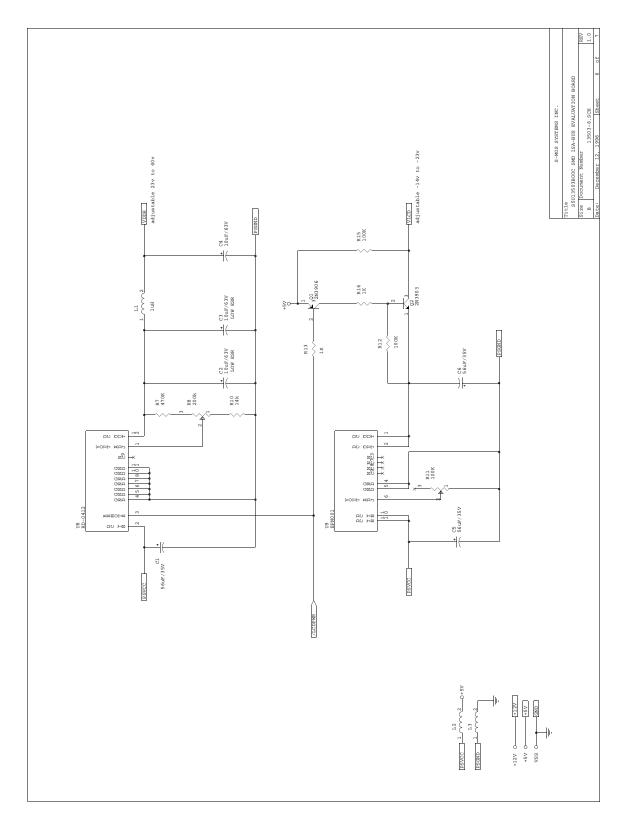

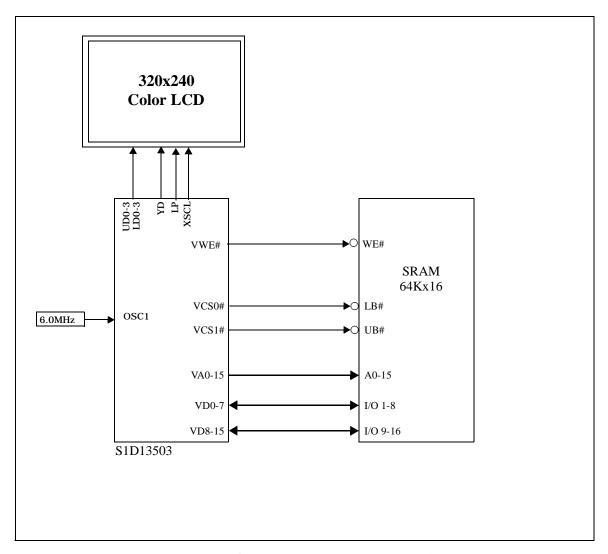

### 3 TYPICAL SYSTEM BLOCK DIAGRAMS

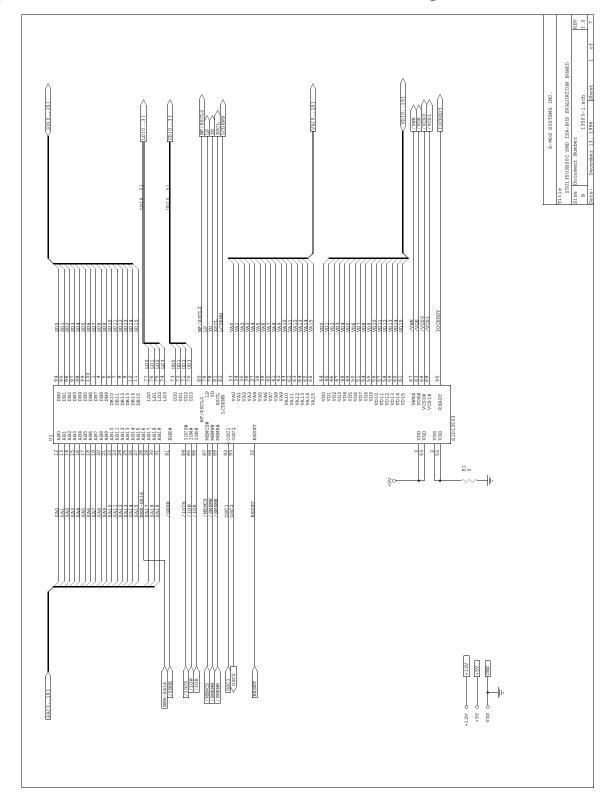

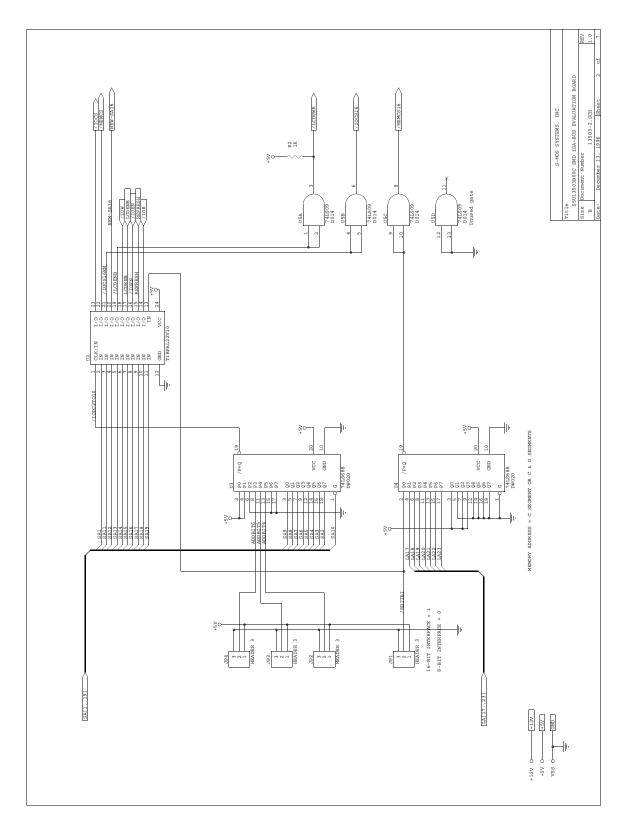

The following figures show typical system implementations of the S1D13503. All of the following block diagrams are shown without SRAM or LCD display. Refer to the interface specific Application Notes for complete details.

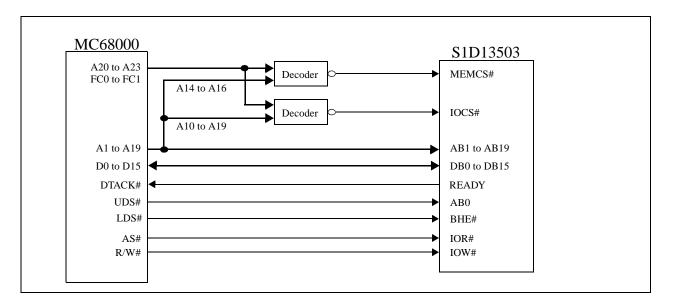

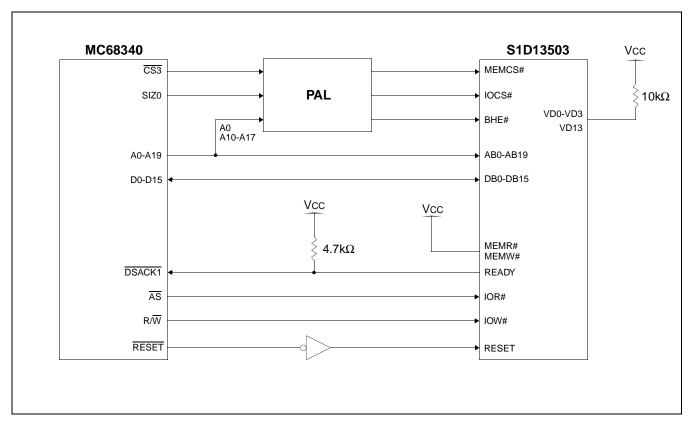

### 3.1 16-Bit MC68000 MPU

Figure 1: 16-Bit 68000 Series (example implementation only - actual may vary)

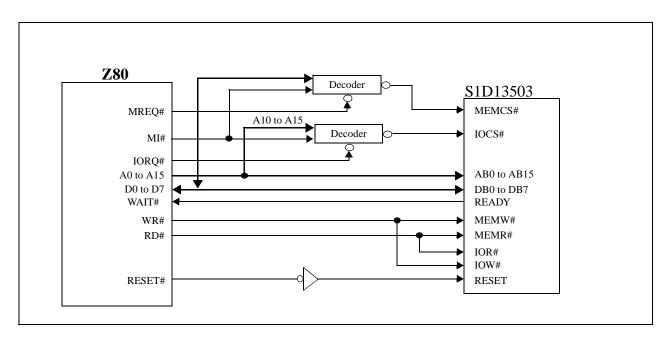

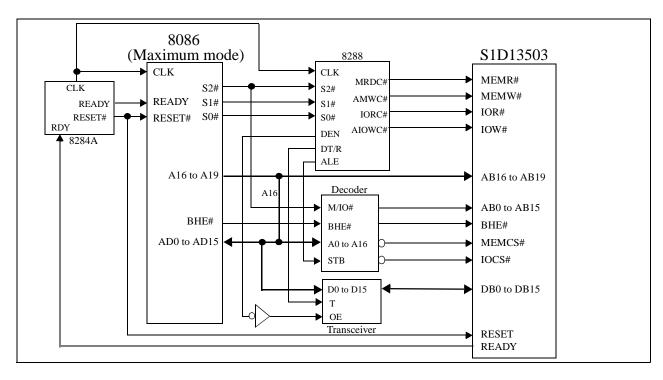

### 3.2 MPU with READY (or WAIT#) signal

Figure 2: 8-Bit Mode, Example: Z80 (example implementation only - actual may vary)

Figure 3: 16-Bit Mode, Example: i8086 (maximum mode) (example implementation only - actual may vary)

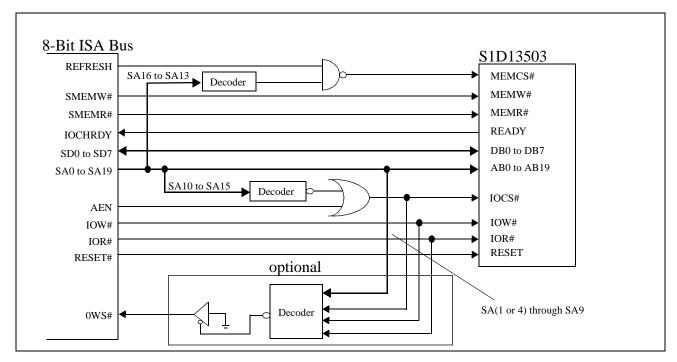

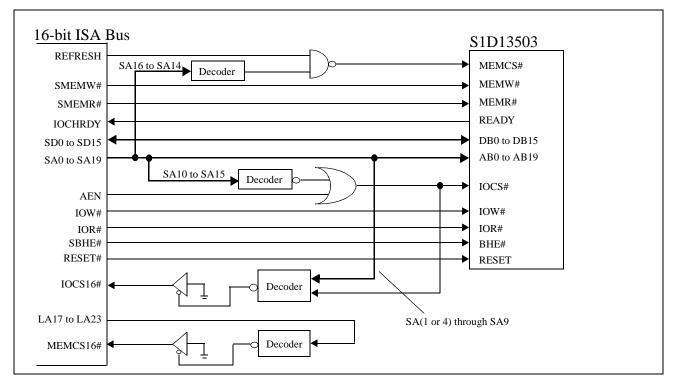

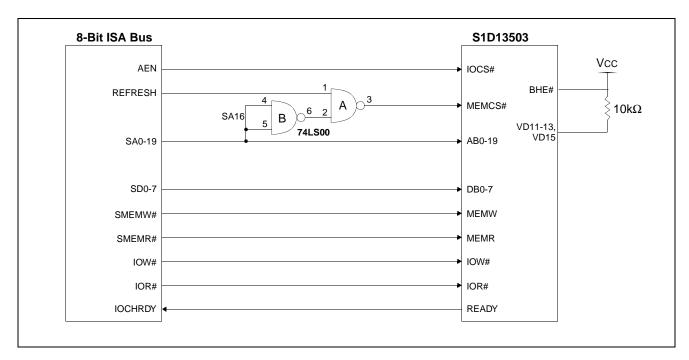

### 3.3 ISA Bus

Figure 4: 8-Bit Mode (ISA) (example implementation only - actual may vary)

Figure 5: 16-Bit Mode (ISA) (example implementation only - actual may vary)

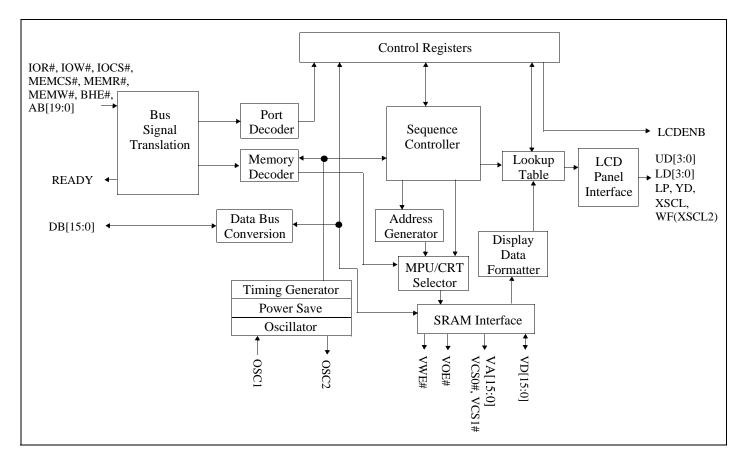

### 3.4 Internal Block Diagram

Figure 6: Internal Block Diagram

### 3.5 Functional Block Descriptions

### 3.5.1 Bus Signal Translation

According to configuration setting VD2, Bus Signal Translation translates MC68000 type MPU signals, or READY type MPU signals to internal bus interface signals.

### 3.5.2 Control Registers

The Control Register contains 16 internal control and configuration registers. These registers can be accessed by either direct-mapping or by using the built-in internal index register.

### 3.5.3 Sequence Controller

The Sequence Controller generates horizontal and vertical display timings according to the configuration registers settings.

### 3.5.4 LCD Panel Interface

The LCD Panel Interface performs frame rate modulation and output data pattern formatting for both passive monochrome and passive color LCD panels.

### 3.5.5 Look-Up Table

The Look-Up Table contains three 16x4-bit wide palettes. In gray shade modes, the "green" palette can be configured for the re-mapping of 16 possible shades of gray. In color modes, all three palettes can be configured for the re-mapping of 4096 possible colors.

### 3.5.6 Port Decoder

According to configuration settings VD1, VD12 - VD4, IOCS# and address lines AB9-1, the Port Decoder validates a given I/O cycle.

### 3.5.7 Memory Decoder

According to configuration settings VD15 - VD13, MEMCS# and address lines AB19-17, the Memory Decoder validates a given memory cycle.

### 3.5.8 Data Bus Conversion

According to configuration setting VD0, Data Bus Conversion maps the external data bus, either 8-bit or 16-bit, into the internal odd and even data bus.

### 3.5.9 Address Generator

The Address Generator generates display refresh addresses to be used to access display memory.

### 3.5.10 MPU / CRT Selector

The MPU / CRT Selector grants access to the display memory from either the MPU or the display refresh circuitry.

### 3.5.11 Display Data Formatter

The Display Data Formatter reads in the display data from the display memory and outputs the correct format for all supported gray shade and color selections.

### 3.5.12 Clock Inputs / Timing

Clock Inputs / Timing generates the internal master clock according to gray-level / color selected and display memory interface. The master clock (MCLK) can be:

- MCLK = input clock

- MCLK = 1/2 input clock

- MCLK = 1/4 input clock.

Pixel clock = input clock =  $f_{OSC}$

### 3.5.13 SRAM Interface

The SRAM Interface generates the necessary signals to interface to the Display Memory (SRAM).

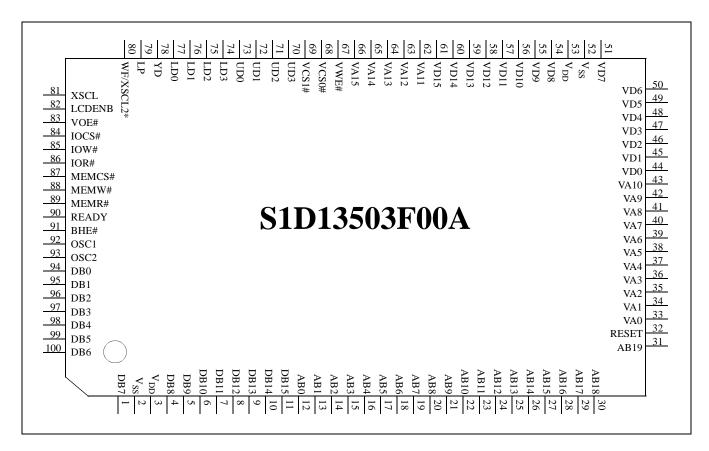

### **4 PINOUT DIAGRAM**

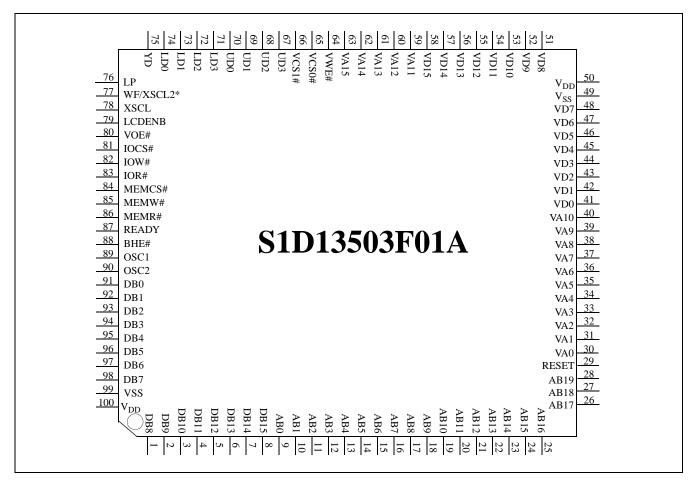

Figure 7: S1D13503F00A Pinout Diagram

Package type: 100 pin surface mount QFP5-S2.

#### Note

- \* Pin 80 = WF in all display modes except format 1 for 8-bit single color panel.

- \* Pin 80 = XSCL2 in format 1 for 8-bit single color panel.

Figure 8: S1D13503F01A Pinout Diagram

Package type: 100 pin surface mount QFP15-STD.

### Note

- \* Pin 77 = WF in all display modes except format 1 for 8-bit single color panel.

- \* Pin 77 = XSCL2 in format 1 for 8-bit single color panel.

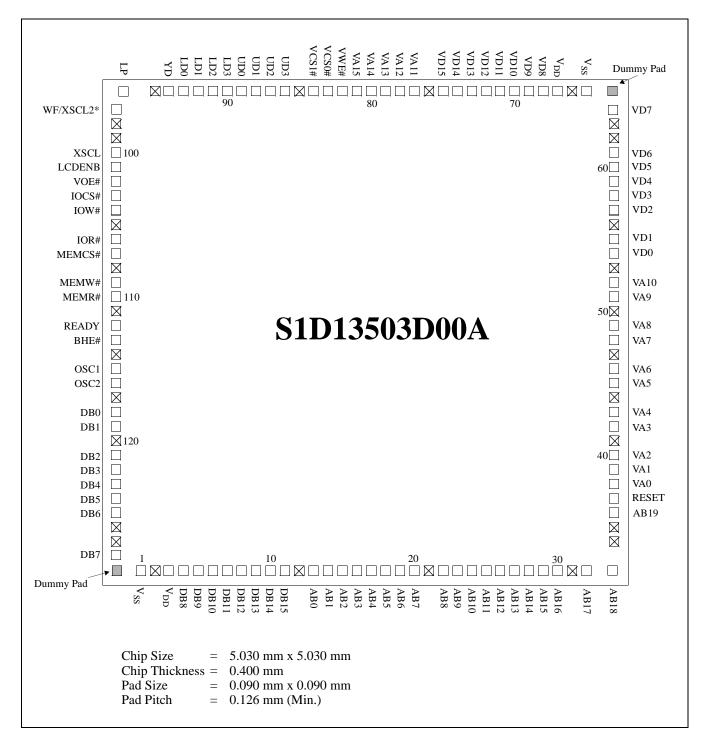

Figure 9: S1D13503D00A Pad Diagram

### Note

\* Pad 97 = WF in all display modes except format 1 for 8-bit single color panel.

\* Pad 97 = XSCL2 in format 1 for 8-bit single color panel.

Table 4-1: PAD Coordinates

| Pad  | Pin  | Pad Center |        |  |  |

|------|------|------------|--------|--|--|

| No.  | Name | Coord      | dinate |  |  |

| 140. | Name | X          | Y      |  |  |

| 1    | VSS  | -2.165     | -2.390 |  |  |

| 2    |      | -2.000     | -2.390 |  |  |

| 3    | VDD  | -1.840     | -2.390 |  |  |

| 4    | DB8  | -1.685     | -2.390 |  |  |

| 5    | DB9  | -1.535     | -2.390 |  |  |

| 6    | DB10 | -1.388     | -2.390 |  |  |

| 7    | DB11 | -1.246     | -2.390 |  |  |

| 8    | DB12 | -1.106     | -2.390 |  |  |

| 9    | DB13 | -0.969     | -2.390 |  |  |

| 10   | DB14 | -0.835     | -2.390 |  |  |

| 11   | DB15 | -0.703     | -2.390 |  |  |

| 12   |      | -0.573     | -2.390 |  |  |

| 13   | AB0  | -0.444     | -2.390 |  |  |

| 14   | AB1  | -0.317     | -2.390 |  |  |

| 15   | AB2  | -0.190     | -2.390 |  |  |

| 16   | AB3  | -0.063     | -2.390 |  |  |

| 17   | AB4  | 0.063      | -2.390 |  |  |

| 18   | AB5  | 0.190      | -2.390 |  |  |

| 19   | AB6  | 0.317      | -2.390 |  |  |

| 20   | AB7  | 0.444      | -2.390 |  |  |

| 21   |      | 0.573      | -2.390 |  |  |

| 22   | AB8  | 0.703      | -2.390 |  |  |

| 23   | AB9  | 0.835      | -2.390 |  |  |

| 24   | AB10 | 0.969      | -2.390 |  |  |

| 25   | AB11 | 1.106      | -2.390 |  |  |

| 26   | AB12 | 1.246      | -2.390 |  |  |

| 27   | AB13 | 1.388      | -2.390 |  |  |

| 28   | AB14 | 1.535      | -2.390 |  |  |

| 29   | AB15 | 1.685      | -2.390 |  |  |

| 30   | AB16 | 1.840      | -2.390 |  |  |

| 31   |      | 2.000      | -2.390 |  |  |

| 32   | AB17 | 2.165      | -2.390 |  |  |

| 33   | AB18 | 2.390      | -2.340 |  |  |

| 34   |      | 2.390      | -2.000 |  |  |

| 35   |      | 2.390      | -1.840 |  |  |

| 36   | AB19 | 2.390      | -1.685 |  |  |

| Pad | Pin   |       | Center<br>dinate |

|-----|-------|-------|------------------|

| No. | Name  | Х     | Υ                |

| 37  | RESET | 2.390 | -1.535           |

| 38  | VA0   | 2.390 | -1.388           |

| 39  | VA1   | 2.390 | -1.246           |

| 40  | VA2   | 2.390 | -1.106           |

| 41  |       | 2.390 | -0.969           |

| 42  | VA3   | 2.390 | -0.835           |

| 43  | VA4   | 2.390 | -0.703           |

| 44  |       | 2.390 | -0.573           |

| 45  | VA5   | 2.390 | -0.444           |

| 46  | VA6   | 2.390 | -0.317           |

| 47  |       | 2.390 | -0.190           |

| 48  | VA7   | 2.390 | -0.063           |

| 49  | VA8   | 2.390 | 0.063            |

| 50  |       | 2.390 | 0.190            |

| 51  | VA9   | 2.390 | 0.317            |

| 52  | VA10  | 2.390 | 0.444            |

| 53  |       | 2.390 | 0.573            |

| 54  | VD0   | 2.390 | 0.703            |

| 55  | VD1   | 2.390 | 0.835            |

| 56  |       | 2.390 | 0.969            |

| 57  | VD2   | 2.390 | 1.106            |

| 58  | VD3   | 2.390 | 1.246            |

| 59  | VD4   | 2.390 | 1.388            |

| 60  | VD5   | 2.390 | 1.535            |

| 61  | VD6   | 2.390 | 1.685            |

| 62  |       | 2.390 | 1.840            |

| 63  |       | 2.390 | 2.000            |

| 64  | VD7   | 2.390 | 2.165            |

| 65  | VSS   | 2.165 | 2.390            |

| 66  |       | 2.000 | 2.390            |

| 67  | VDD   | 1.840 | 2.390            |

| 68  | VD8   | 1.685 | 2.390            |

| 69  | VD9   | 1.535 | 2.390            |

| 70  | VD10  | 1.388 | 2.390            |

| 71  | VD11  | 1.246 | 2.390            |

| 72  | VD12  | 1.106 | 2.390            |

Table 4-1: PAD Coordinates

| Pad | Pin      | Pad Center<br>Coordinate |       |  |  |

|-----|----------|--------------------------|-------|--|--|

| No. | Name     |                          |       |  |  |

|     |          | Х                        | Υ     |  |  |

| 73  | VD13     | 0.969                    | 2.390 |  |  |

| 74  | VD14     | 0.835                    | 2.390 |  |  |

| 75  | VD15     | 0.703                    | 2.390 |  |  |

| 76  |          | 0.573                    | 2.390 |  |  |

| 77  | VA11     | 0.444                    | 2.390 |  |  |

| 78  | VA12     | 0.317                    | 2.390 |  |  |

| 79  | VA13     | 0.190                    | 2.390 |  |  |

| 80  | VA14     | 0.063                    | 2.390 |  |  |

| 81  | VA15     | -0.063                   | 2.390 |  |  |

| 82  | VWE#     | -0.190                   | 2.390 |  |  |

| 83  | VCS0#    | -0.317                   | 2.390 |  |  |

| 84  | VCS1#    | -0.444                   | 2.390 |  |  |

| 85  |          | -0.573                   | 2.390 |  |  |

| 86  | UD3      | -0.703                   | 2.390 |  |  |

| 87  | UD2      | -0.835                   | 2.390 |  |  |

| 88  | UD1      | -0.969                   | 2.390 |  |  |

| 89  | UD0      | -1.106                   | 2.390 |  |  |

| 90  | LD3      | -1.246                   | 2.390 |  |  |

| 91  | LD2      | -1.388                   | 2.390 |  |  |

| 92  | LD1      | -1.535                   | 2.390 |  |  |

| 93  | LD0      | -1.685                   | 2.390 |  |  |

| 94  | YD       | -1.840                   | 2.390 |  |  |

| 95  |          | -2.000                   | 2.390 |  |  |

| 96  | LP       | -2.340                   | 2.390 |  |  |

| 97  | WF/XSCL2 | -2.390                   | 2.165 |  |  |

| 98  |          | -2.390                   | 2.000 |  |  |

| 99  |          | -2.390                   | 1.840 |  |  |

| 100 | XSCL     | -2.390                   | 1.685 |  |  |

| 101 | LCDENB   | -2.390                   | 1.535 |  |  |

| Pad<br>No. | Pin       |        | enter<br>dinate |

|------------|-----------|--------|-----------------|

| NO.        | Name      | Х      | Υ               |

| 102        | VOE#      | -2.390 | 1.388           |

| 103        | IOCS#     | -2.390 | 1.246           |

| 104        | IOW#      | -2.390 | 1.106           |

| 105        |           | -2.390 | 0.969           |

| 106        | IOR#      | -2.390 | 0.835           |

| 107        | MEMCS#    | -2.390 | 0.703           |

| 108        |           | -2.390 | 0.573           |

| 109        | MEMW#     | -2.390 | 0.444           |

| 110        | MEMR#     | -2.390 | 0.317           |

| 111        |           | -2.390 | 0.190           |

| 112        | READY     | -2.390 | 0.063           |

| 113        | BHE#      | -2.390 | -0.063          |

| 114        |           | -2.390 | -0.190          |

| 115        | OSC1      | -2.390 | -0.317          |

| 116        | OSC2      | -2.390 | -0.444          |

| 117        |           | -2.390 | -0.573          |

| 118        | DB0       | -2.390 | -0.703          |

| 119        | DB1       | -2.390 | -0.835          |

| 120        |           | -2.390 | -0.969          |

| 121        | DB2       | -2.390 | -1.106          |

| 122        | DB3       | -2.390 | -1.246          |

| 123        | DB4       | -2.390 | -1.388          |

| 124        | DB5       | -2.390 | -1.535          |

| 125        | DB6       | -2.390 | -1.685          |

| 126        |           | -2.390 | -1.840          |

| 127        |           | -2.390 | -2.000          |

| 128        | DB7       | -2.390 | -2.165          |

| 129        | Dummy Pad | 2.390  | 2.390           |

| 130        | Dummy Pad | -2.390 | -2.390          |

### 5 PIN DESCRIPTION

### 5.1 Description

Key:

I = Input O = Output

I/O = Bidirectional (Input/Output)

P = Power pin

COx = CMOS level output driver, x denotes driver type (see Table 6-4, "Output Specifications," on page 28)

COxS = CMOS level output driver with slew rate control for noise reduction, x denotes driver type (see Table 6-4,

"Output Specifications," on page 28)

TSx = Tri-state CMOS level output driver, x denotes driver type (see Table 6-4, "Output Specifications," on

page 28)

TSxD2 = Tri-state CMOS level output driver with pull down resistor (typical values of  $100K\Omega/200K\Omega$  at 5V/3.0V

respectively), x denotes driver type (see Table 6-4, "Output Specifications," on page 28)

TTL = TTL level input ( $V_{DD} = 5.0V$ , see Table 6-3, "Input Specifications," on page 27)

TTLS = TTL level input with hysteresis

Table 5-1: Bus Interface

| Pin Name     | Type | F00A<br>Pin #            | F01A<br>Pin #     | D00A<br>Pad #                                | Driver | Description                                                                                                                                                                                                                                        |

|--------------|------|--------------------------|-------------------|----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0-<br>DB15 | I/O  | 94 -<br>100, 1,<br>4 -11 | 91 - 98,<br>1 - 8 | 118-<br>119,<br>121-<br>125,<br>128,<br>4-11 | TS2    | These pins are connected to the system data bus. In 8-bit bus mode, DB8-DB15 must be tied to $V_{DD}$ .                                                                                                                                            |

| AB0          | I    | 12                       | 9                 | 13                                           | TTLS   | In MC68000 MPU interface, this pin is connected to the Upper Data Strobe (UDS#) pin of MC68000. In other MPU/Bus interfaces, this pin is connected to the system address bus.                                                                      |

| AB1-<br>AB19 | I    | 13 - 31                  | 10 - 28           | 14-20,<br>22-30,<br>32-33,<br>36             | TTL    | These pins are connected to the system address bus.                                                                                                                                                                                                |

| BHE#         | I    | 91                       | 88                | 113                                          | TTLS   | In MC68000 MPU interface, this pin is connected to the Lower Data Strobe (LDS#) pin of MC68000. In other MPU/Bus interfaces, this pin is the Byte High Enable input for use with 16-bit system. In 8-bit bus mode tie the BHE# input to $V_{DD}$ . |

| IOCS#        | I    | 84                       | 81                | 103                                          | TTLS   | Active low input to select one of sixteen internal registers.                                                                                                                                                                                      |

Table 5-1: Bus Interface

| Pin Name | Туре | F00A<br>Pin# | F01A<br>Pin # | D00A<br>Pad #                                                                                              | Driver | Description                                                                                                                                                                                                                                                                                                                          |

|----------|------|--------------|---------------|------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOW#     | I    | 85           | 82            | 104                                                                                                        | TTLS   | In MC68000 MPU interface, this pin is connected to the R/W# pin of MC68000. This input pin defines whether the data transfer is a read (active high) or write (active low) cycle. In other MPU/Bus interfaces, this is the active low input to write data into an internal register.                                                 |

| IOR#     | I    | 86           | 83            | pin of MC68000. This input pin indicates a valid add available on the address bus. In other MPU/Bus interf |        | In MC68000 MPU interface, this pin is connected to the AS# pin of MC68000. This input pin indicates a valid address is available on the address bus. In other MPU/Bus interfaces, this is the active low input to read data from an internal register.                                                                               |

| MEMCS#   | I    | 87           | 84            | 107                                                                                                        | TTLS   | Active low input to indicate a memory cycle.                                                                                                                                                                                                                                                                                         |

| MEMW#    | I    | 88           | 85            | 109                                                                                                        | TTLS   | Active low input to indicate a memory write cycle. This pin should be tied to $V_{\rm DD}$ in an MC68000 MPU interface.                                                                                                                                                                                                              |

| MEMR#    | I    | 89           | 86            | 110                                                                                                        | TTLS   | Active low input to indicate a memory read cycle. This pin should be tied to $V_{\rm DD}$ in an MC68000 MPU interface.                                                                                                                                                                                                               |

| READY    | О    | 90           | 87            | 112                                                                                                        | TS3    | For MC68000 MPU interface, this pin is connected to the DTACK# pin of MC68000 and is driven low when the data transfer is complete. In other MPU/Bus interfaces, this output is driven low to force the system to insert wait states when needed.  READY is placed in a high impedance (Hi-Z) state after the transfer is completed. |

| RESET    | Ι    | 32           | 29            | 37                                                                                                         | TTLS   | Active high input to force all signals to their inactive states.                                                                                                                                                                                                                                                                     |

Table 5-2: Display Memory Interface

| Pin          | TD.  | F00A F01A D00A D    | Description        |                                                         |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |

|--------------|------|---------------------|--------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | Type | Pin#                | Pin#               | Pad #                                                   | Driver                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                           |

| VD0-         | I/O  |                     | 41 - 48,           | 54-55,<br>57-61,<br>64,<br>68-75                        | 18102                                                                                                                       | These pins are connected to the display memory data bus. For 16-bit interface, VD0-VD7 are connected to the display memory data bus of even byte addresses and VD8-VD15 are connected to the display memory data bus of odd byte addresses. The output drivers of these pins are placed in a high impedance state when RESET is high. |

| VD15         |      |                     | 51 - 58            |                                                         |                                                                                                                             | On the falling edge of RESET, the values of VD0-VD15 are latched into the chip to configure various hardware options (see Section Table 5-6: on page 26).                                                                                                                                                                             |

|              |      |                     |                    |                                                         |                                                                                                                             | VD0-VD15 each have an internal pull-down resistor (see Section Table 6-3: on page 27).                                                                                                                                                                                                                                                |

| VA0-<br>VA15 | 0    | 33 - 43,<br>62 - 66 | 30 - 40<br>59 - 63 | 38-40,<br>42-43,<br>45-46,<br>48-49,<br>51-52,<br>77-81 | CO1                                                                                                                         | These pins are connected to the display memory address bus.                                                                                                                                                                                                                                                                           |

| VCS1#        | О    | 69                  | 66                 | 84                                                      | CO1 Active low chip-select output to the second or odd byte address SRAM. See Display Memory Interface section for details. |                                                                                                                                                                                                                                                                                                                                       |

| VCS0#        | О    | 68                  | 65                 | 83                                                      | CO1                                                                                                                         | Active low chip-select output to the first or even byte address SRAM. See Display Memory Interface section for details.                                                                                                                                                                                                               |

| VWE#         | О    | 67                  | 64                 | 82                                                      | CO1                                                                                                                         | Active low output used for writing data to the display memory. This pin is connected to the WE# input of the SRAMs.                                                                                                                                                                                                                   |

| VOE#         | О    | 83                  | 80                 | 102                                                     | CO1                                                                                                                         | Active low output to enable reading of data from the display memory. This pin is connected to the OE# input of the SRAMs.                                                                                                                                                                                                             |

Table 5-3: LCD Interface

| Pin Name     | FPDI-1 <sup>TM</sup><br>Pin Name <sup>a</sup> | Туре |                    | F01A<br>Pin #      | D00A<br>Pad #      | Driver | Description                                                                                                                                                                                                        |

|--------------|-----------------------------------------------|------|--------------------|--------------------|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | UD3-UD0<br>UD3-LD0                            | О    | 70 - 73<br>74 - 77 | 67 - 70<br>71 - 74 | 86 - 89<br>90 - 93 | CO3S   | Panel display data bus. The data format depends on the specific panel connected. For 4-bit single panels, LD3-LD0 are driven low (0 state).                                                                        |

| XSCL         | FPSHIFT                                       | О    | 81                 | 78                 | 100                | CO3    | Display data shift clock. Data is shifted into the LCD X-drivers on the falling edge of this signal.                                                                                                               |

| LP           | FPLINE                                        | О    | 79                 | 76                 | 96                 | CO3    | Display data latch clock. The falling edge of this signal is used to latch a row of display data in the LCD X-drivers and to turn on the Y driver (row driver).                                                    |

| WF/<br>XSCL2 | MOD<br>FPSHIFT2                               | О    | 80                 | 77                 | 97                 | CO3    | For format 1 of 8-bit single color panels this is the second shift clock.  For all other modes, this is the LCD backplane BIAS signal. This output toggles once every frame, or as programmed in AUX[05] bits 7-2. |

| YD           | FPFRAME                                       | О    | 78                 | 75                 | 94                 | CO3    | Vertical scanning start pulse. A logic '1' on this signal, sampled by the LCD module on the falling edge of LP, is used by the panel Y driver (row driver) to indicate the start of the vertical frame.            |

| LCDENB       |                                               | О    | 82                 | 79                 | 101                | CO2    | LCD enable signal output. It can be used externally to turn off the panel supply voltage and backlight.                                                                                                            |

$<sup>^{\</sup>rm a}~$  VESA Flat Panel Display Interface Standard (FPDI-1  $^{\rm TM}$ )

Table 5-4: Clock Inputs

| Pin<br>Name | Type | F00A<br>Pin# | F01A<br>Pin # | D00A<br>Pad # | Driver | Description                                                                                                                                                                                                 |

|-------------|------|--------------|---------------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1        | I    | 92           | 89            | 115           | *      | This pin, along with OSC2, is the 2-terminal crystal interface when using a 2-terminal crystal as the clock input. If an external oscillator is used as a clock source, then this pin is the clock input.   |

| OSC2        | О    | 93           | 90            | 116           | *      | This pin, along with OSC1, is the 2-terminal crystal interface when using a 2-terminal crystal as the clock input. If an external oscillator is used as a clock source this pin should be left unconnected. |

Table 5-5: Power Supply

| Pin Name | Туре | F00A Pin# | F01A Pin# | D00A Pad# | Driver | Description    |

|----------|------|-----------|-----------|-----------|--------|----------------|

| $V_{DD}$ | P    | 3, 53     | 50, 100   | 3, 67     | P      | Voltage supply |

| $V_{SS}$ | P    | 2, 52     | 49, 99    | 1, 65     | P      | Voltage ground |

### 5.2 Summary of Configuration Options

The S1D13503 requires some configuration information on power-up. This information is provided through the SRAM data lines VD[0...15]. The state of these pins are read on the falling edge of RESET and used to configure the following options:

Pin Name value on this pin at falling edge of RESET is used to configure: (1/0)VD0 8-bit host bus interface 16-bit host bus interface VD1 Use direct-mapping for I/O accesses Use internal index register for I/O accesses MPU / Bus interface with memory accesses VD2 MC68000 MPU interface controlled by a READY (WAIT#) signal Swap of high and low data bytes in 16-bit bus No byte swap of high and low data bytes in VD3 interface 16-bit bus interface Select I/O mapping address bits [9:1]. These nine bits are latched on power-up and are compared to the MPU address bits [9-1]. A valid I/O cycle combined with a valid address will enable the internal I/O decoder. Therefore, VD12-VD4 both types of I/O mapping are limited to even address boundaries to determine either the absolute or indexed I/O address of the first register. Note that a "valid I/O cycle" includes IOCS# being toggled low. Select memory mapping address bits [3:1] These three bits are latched on power-up and are compared to the MPU address bits [19-17]. A valid memory cycle combined with a valid address will enable the internal memory decoder. As only the three most significant bits of the address are compared, the maximum amount of VD15-VD13 memory supported is 128K bytes. Note that a "valid memory cycle" includes MEMCS# being toggled low. When using 128K byte memory it must be mapped at an even address such that all 128K bytes is available without a change in state on A17, as this would invalidate the internal compare logic.

Table 5-6: Summary of Power On / Reset Options

#### Note

The S1D13503 has internal pulldown resistors on these pins and therefore will be pulled down and read on a logic "0" after RESET. If pullup resistors are required refer to Table 6-3, "Input Specifications," on page 27 for pulldown resistor values.

**Example:** If an ISA bus (no byte swap) with memory segment "A" and I/O location 300h are used, the corresponding settings of VD15-VD0 would be:

|           | 8-Bit ISA Bus 16-Bit |                |                   | ISA Bus        |

|-----------|----------------------|----------------|-------------------|----------------|

| Pin Name  | Index<br>Register    | Direct Mapping | Index<br>Register | Direct Mapping |

| VD0       | 0                    | 0              | 1                 | 1              |

| VD1       | 0                    | 1              | 0                 | 1              |

| VD2       | 0                    | 0              | 0                 | 0              |

| VD3       | 0                    | 0              | 0                 | 0              |

| VD12-VD4  | 11 0000 000          | 11 0000 xxx    | 11 0000 000       | 11 0000 xxx    |

| VD15-VD13 | 101                  | 101            | 101               | 101            |

Table 5-7: I/O and Memory Addressing Example

Where x = don't care; 1 = connected to pull-up resistor; 0 = no pull-up resistor

### 6 D.C. CHARACTERISTICS

Table 6-1: Absolute Maximum Ratings

| Symbol           | Parameter               | Rating                         | Units |

|------------------|-------------------------|--------------------------------|-------|

| V <sub>DD</sub>  | Supply Voltage          | -0.3 to + 6.0                  | V     |

| V <sub>IN</sub>  | Input Voltage           | $-0.3 \text{ to V}_{DD} + 0.5$ | V     |

| V <sub>OUT</sub> | Output Voltage          | $-0.3 \text{ to V}_{DD} + 0.5$ | V     |

| T <sub>STG</sub> | Storage Temperature     | -65 to 150                     | ° C   |

| T <sub>SOL</sub> | Solder Temperature/Time | 260 for 10 sec. max at lead    | ° C   |

Table 6-2: Recommended Operating Conditions

| Symbol           | Parameter                        | Condition                              | Min             | Тур          | Max      | Units |

|------------------|----------------------------------|----------------------------------------|-----------------|--------------|----------|-------|

| $V_{DD}$         | Supply Voltage                   | $V_{SS} = 0 V$                         | 2.7             | 3.0/3.3/5.0  | 5.5      | V     |

| V <sub>IN</sub>  | Input Voltage                    |                                        | V <sub>SS</sub> |              | $V_{DD}$ | V     |

| I <sub>OPR</sub> | Operating Current                | f <sub>OSC</sub> = 6 MHz<br>256 colors |                 | 4.5/5.0/11   |          | mA    |

| T <sub>OPR</sub> | Operating Temperature            |                                        | -40             | 25           | 85       | ° C   |

| P <sub>TYP</sub> | Typical Active Power Consumption | f <sub>OSC</sub> = 6 MHz<br>256 colors |                 | 13.5/16.5/55 |          | mW    |

Table 6-3: Input Specifications

| Symbol            | Parameter                | Condition            | Min | Тур | Max | Units |

|-------------------|--------------------------|----------------------|-----|-----|-----|-------|

|                   |                          | $V_{\rm DD} = 4.5 V$ |     |     | 0.8 |       |

| $V_{\mathrm{IL}}$ | Low Level Input Voltage  | $V_{DD} = 3.0V$      |     |     | 0.4 | V     |

|                   |                          | $V_{DD} = 2.7V$      |     |     | 0.3 |       |

|                   |                          | $V_{\rm DD} = 5.5 V$ | 2.0 |     |     |       |

| $V_{IH}$          | High Level Input Voltage | $V_{DD} = 3.6V$      | 1.3 |     |     | V     |

|                   |                          | $V_{DD} = 3.3V$      | 1.2 |     |     |       |

|                   |                          | $V_{\rm DD} = 5.0$   |     |     | 2.4 |       |

| $V_{T+}$          | Positive-going Threshold | $V_{\rm DD} = 3.3$   |     |     | 1.4 | V     |

|                   |                          | $V_{DD} = 3.0$       |     |     | 1.3 |       |

|                   |                          | $V_{\rm DD} = 5.0$   | 0.6 |     |     |       |

| $V_{T-}$          | Negative-going Threshold | $V_{\rm DD} = 3.3$   | 0.5 |     |     | V     |

|                   |                          | $V_{DD} = 3.0$       | 0.4 |     |     |       |

|                   |                          | $V_{\rm DD} = 5.0$   | 0.1 |     |     |       |

| $V_{H}$           | Hysteresis Voltage       | $V_{\rm DD} = 3.3$   | 0.1 |     |     | V     |

|                   |                          | $V_{DD} = 3.0$       | 0.1 |     |     |       |

| I <sub>IZ</sub>   | Input Leakage Current    |                      | -1  |     | 1   | μΑ    |

Table 6-3: Input Specifications (Continued)

| Symbol          | Parameter              | Condition        | Min | Тур | Max | Units |

|-----------------|------------------------|------------------|-----|-----|-----|-------|

| C <sub>IN</sub> | Input Pin Capacitance  | f=1 MHz,         |     |     | 12  | pF    |

| CIN             | input i in Capacitanee | $V_{DD} = 0V$    |     |     | 12  | PΓ    |

| R <sub>PD</sub> | Pull Down Resistance   | $V_{DD} = 5.0V$  | 50  | 100 | 200 | kΩ    |

| КРД             | Full Down Resistance   | $V_I = V_{DD}$   | 30  | 100 | 200 | K22   |

| D               | Dell Deser Desistence  | $V_{DD} = 3.3V$  | 90  | 180 | 360 | kΩ    |

| $R_{PD}$        | Pull Down Resistance   | $V_I = V_{DD}$   | 90  | 160 | 300 | K22   |

| D               | Dell Deser Besisters   | $V_{DD} = 3.0V$  | 100 | 200 | 400 | kΩ    |

| $R_{PD}$        | Pull Down Resistance   | $V_{I} = V_{DD}$ | 100 | 200 | 400 | K22   |

Table 6-4: Output Specifications

| Symbol                 | Parameter                                                           | Condition                                                                   | Min                  | Тур | Max | Units |

|------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|-----|-----|-------|

|                        | Low Level Output Voltage                                            | $V_{DD} = Min$                                                              |                      |     |     |       |

| $V_{OL}(5.0V)$         | Type 1 - TS1D2, CO1<br>Type 2 - TS2, CO2<br>Type 3 - TS3, CO3, CO3S | $I_{OL} = 4 \text{ mA}$ $I_{OL} = 8 \text{ mA}$ $I_{OL} = 12 \text{ mA}$    |                      |     | 0.4 | V     |

|                        | Low Level Output Voltage                                            | $V_{DD} = Min$                                                              |                      |     |     |       |

| V <sub>OL</sub> (3.3V) | Type 1 - TS1D2, CO1<br>Type 2 - TS2, CO2<br>Type 3 - TS3, CO3, CO3S | $I_{OL} = 2 \text{ mA}$ $I_{OL} = 4 \text{ mA}$ $I_{OL} = 6 \text{ mA}$     |                      |     | 0.3 | V     |

|                        | Low Level Output Voltage                                            | V <sub>DD</sub> = Min                                                       |                      |     |     |       |

| V <sub>OL</sub> (3.0V) | Type 1 - TS1D2, CO1<br>Type 2 - TS2, CO2<br>Type 3 - TS3, CO3, CO3S | $I_{OL} = 1.8 \text{ mA}$ $I_{OL} = 3.5 \text{ mA}$ $I_{OL} = 5 \text{ mA}$ |                      |     | 0.3 | V     |

|                        | High Level Output Voltage                                           | $V_{DD} = Min$                                                              |                      |     |     |       |

| V <sub>OH</sub> (5.0V) | Type 1 - TS1D2, CO1<br>Type 2 - TS2, CO2<br>Type 3 - TS3, CO3, CO3S | $I_{OH}$ = -4 mA<br>$I_{OH}$ = -8mA<br>$I_{OH}$ = -12 mA                    | V <sub>DD</sub> -0.4 |     |     | V     |

|                        | Low Level Output Voltage                                            | $V_{DD} = Min$                                                              |                      |     |     |       |

| V <sub>OH</sub> (3.3V) | Type 1 - TS1D2, CO1<br>Type 2 - TS2, CO2<br>Type 3 - TS3, CO3, CO3S | $I_{OL} = -2 \text{ mA}$ $I_{OL} = -4 \text{ mA}$ $I_{OL} = -6 \text{ mA}$  | V <sub>DD</sub> -0.3 |     |     | V     |

|                        | High Level Output Voltage                                           | V <sub>DD</sub> = Min                                                       |                      |     |     |       |

| V <sub>OH</sub> (3.0V) | Type 1 - TS1D2, CO1<br>Type 2 - TS2, CO2<br>Type 3 - TS3, CO3, CO3S | $I_{OH}$ = -1.8 mA<br>$I_{OH}$ = -3.5 mA<br>$I_{OH}$ = -5 mA                | V <sub>DD</sub> -0.3 |     |     | V     |

| $I_{OZ}$               | Output Leakage Current                                              |                                                                             | -1                   |     | 1   | μΑ    |

| C <sub>OUT</sub>       | Output Pin Capacitance                                              | f =1 MHz,<br>V <sub>DD</sub> = 0V                                           |                      |     | 12  | pF    |

| $C_{BID}$              | Bidirectional Pin Capacitance                                       | f =1 MHz,<br>V <sub>DD</sub> = 0V                                           |                      |     | 12  | pF    |

## 7 A.C. CHARACTERISTICS

Conditions :  $V_{DD}$  = 3.0V  $\pm$  10%,  $V_{DD}$  = 3.3V  $\pm$  10%, or  $V_{DD}$  = 5.0V  $\pm$  10%  $T_A$  = -40 °C to 85 °C

$T_{rise}$  and  $T_{fall}$  for all inputs must be  $\leq 5$  nsec (10% ~ 90%)

C<sub>L</sub> = 80pF (Bus/MPU Interface)

C<sub>L</sub> = 100pF (LCD Panel Interface)

C<sub>L</sub> = 20pF (Display Memory Interface)

# 7.1 Bus Interface Timing

# 7.1.1 MC68000 Interface Timing

#### Note

All input timing parameters are based on a maximum 16MHz MPU clock.

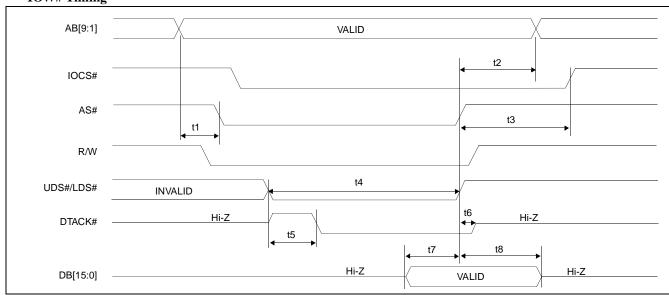

#### **IOW# Timing**

Figure 10: IOW# Timing (MC68000)

Table 7-1: IOW# Timing (MC68000)

|        |                                               | 3V/. | 3.3V | 5   | V   |       |

|--------|-----------------------------------------------|------|------|-----|-----|-------|

| Symbol | Parameter                                     | Min  | Max  | Min | Max | Units |

| t1     | AB[9:1] valid before AS# falling edge         | 10   |      | 0   |     | ns    |

| t2     | AB[9:1] hold from AS# rising edge             | 20   |      | 10  |     | ns    |

| t3     | IOCS# hold from AS# rising edge               | 0    |      | 0   |     | ns    |

| t4     | UDS#/LDS# valid before AS# rising edge        | 30   |      | 20  |     | ns    |

| t5     | UDS#/LDS# falling edge to DTACK# falling edge |      | 40   |     | 25  | ns    |

| t6     | AS# rising edge to DTACK# hi-z delay          |      | 40   |     | 25  | ns    |

| t7     | DB[15:0] setup to AS# rising edge             | 20   |      | 10  |     | ns    |

| t8     | DB[15:0] hold from AS# rising edge            | 20   |      | 10  |     | ns    |

Figure 11: IOR# Timing (MC68000)

Table 7-2: IOR# Timing (MC68000)

|        |                                                 | 3V/. | 3.3 V | 5   | V   |       |

|--------|-------------------------------------------------|------|-------|-----|-----|-------|

| Symbol | Parameter                                       | Min  | Max   | Min | Max | Units |

| t1     | AB[9:1] and IOCS# valid before AS# falling edge | 10   |       | 0   |     | ns    |

| t2     | AB[9:1] and IOCS# hold from AS# rising edge     | 20   |       | 10  |     | ns    |

| t3     | AS# falling edge to DTACK# falling edge         |      | 40    |     | 25  | ns    |

| t4     | AS# rising edge to DTACK# hi-z delay            |      | 40    |     | 25  | ns    |

| t5     | AS# falling edge to DB[15:0] valid              |      | 60    |     | 40  | ns    |

| t6     | DB[15:0] hold from AS# rising edge              |      | 20    |     | 15  | ns    |

| t7     | AS# rising edge to DB[15:0] hi-z delay          |      | 35    |     | 25  | ns    |

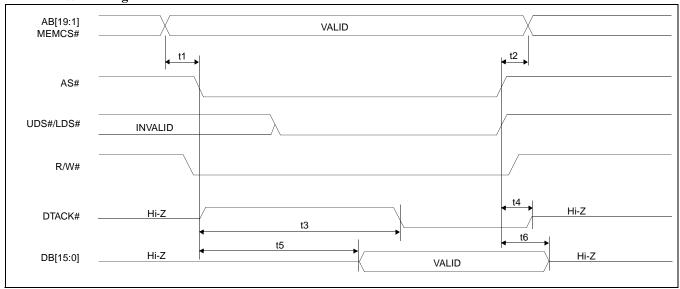

## **MEMW# Timing**

Figure 12: MEMW# Timing (MC68000)

Table 7-3: MEMW# Timing (MC68000)

|        |                                                   | 3V/ | 3.3V                  | 5V  |                       |       |

|--------|---------------------------------------------------|-----|-----------------------|-----|-----------------------|-------|

| Symbol | Parameter                                         | Min | Max                   | Min | Max                   | Units |

| t1     | AB[19:1] and MEMCS# valid before AS# falling edge | 0   |                       | 0   |                       | ns    |

| t2     | AB[19:1] and MEMCS# hold from AS# rising edge     | 0   |                       | 0   |                       | ns    |

| t3     | AS# falling edge to DTACK# falling edge           |     | 3.5 *<br>MCLK<br>+ 20 |     | 3.5 *<br>MCLK<br>+ 10 | ns    |

| t4     | AS# rising edge to DTACK hi-z delay               |     | 40                    |     | 25                    | ns    |

| t5     | AS# falling edge to DB[15:0] valid                |     | MCLK<br>-40           |     | MCLK<br>-20           | ns    |

| t6     | DB[15:0] hold from AS# rising edge                | 0   |                       | 0   |                       | ns    |

Where MCLK period =  $1/f_{OSC}$ , or  $2/f_{OSC}$ , or  $4/f_{OSC}$  depending on which display mode the chip is in. (see section 9.2 and 9.3)

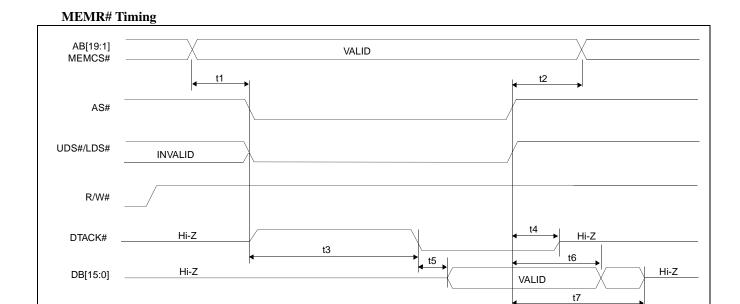

Figure 13: MEMR# Timing (MC68000)

Table 7-4: MEMR# Timing (MC68000)

|        | 3V/3.3V                                           |     | 5                     | $\mathbf{V}$ |                       |       |

|--------|---------------------------------------------------|-----|-----------------------|--------------|-----------------------|-------|

| Symbol | Parameter                                         | Min | Max                   | Min          | Max                   | Units |

| t1     | AB[19:1] and MEMCS# valid before AS# falling edge | 0   |                       | 0            |                       | ns    |

| t2     | AB[19:1] and MEMCS# hold from AS# rising edge     | 0   |                       | 0            |                       | ns    |

| t3     | AS# falling edge to DTACK# falling edge           |     | 3.5 *<br>MCLK<br>+ 20 |              | 3.5 *<br>MCLK<br>+ 10 | ns    |

| t4     | AS# rising edge to DTACK# hi-z delay              |     | 40                    |              | 15                    | ns    |

| t5     | DTACK# falling edge to DB[15:0] valid             |     | 20                    |              | 15                    | ns    |

| t6     | DB[15:0] hold from AS# rising edge                |     | 25                    |              | 15                    | ns    |

| t7     | AS# rising edge to DB[15:0] hi-z delay            |     | 40                    |              | 30                    | ns    |

Where MCLK period =  $1/f_{OSC}$ , or  $2/f_{OSC}$ , or  $4/f_{OSC}$  depending on which display mode the chip is in. (see section 9.2 and 9.3)

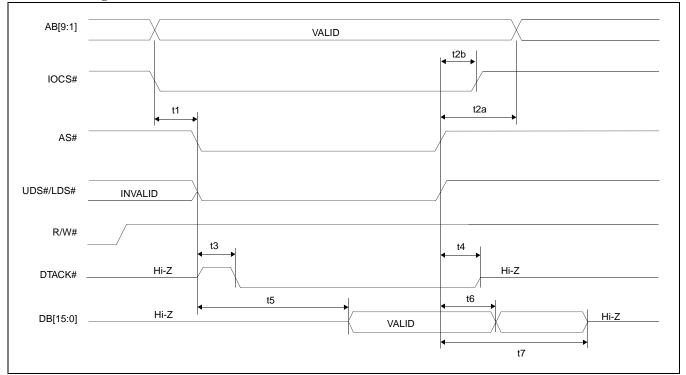

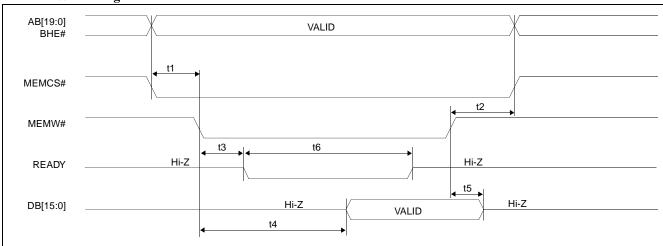

# 7.1.2 Non-MC68000, MPU/Bus With READY (or WAIT#) Signal

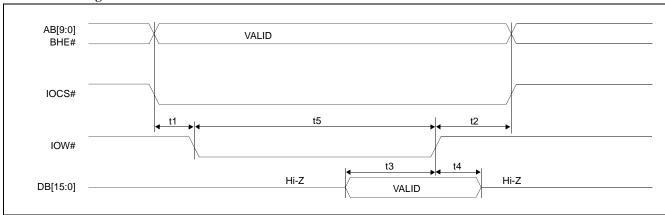

# **IOW# Timing**

Figure 14: IOW# Timing (Non-MC68000)

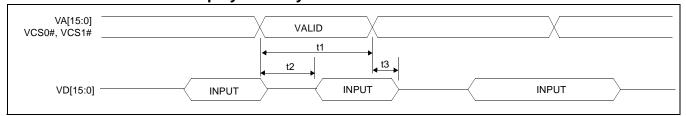

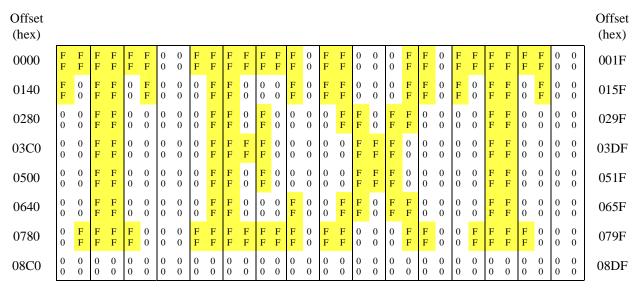

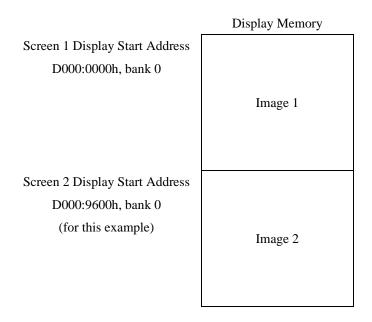

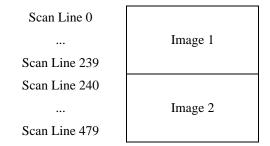

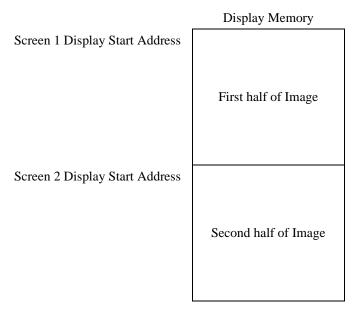

Table 7-5: IOW# Timing (Non-MC68000)