# CelXpres<sup>™</sup> T8207 ATM Interconnect

### 1 Product Overview

### 1.1 Features

- > OC-3 transport capability

- UTOPIA level 1 and 2 (8-bit) cell-level handshake interface (ATM or PHY layers)

- 32 multi-PHY (MPHY) operation

- Shared UTOPIA mode

- Egress SDRAM buffer support to expand UTOPIA output priority queues for 32K to 512K cells:

- 64 queues configurable up to four queues per PHY with programmable sizes

- Programmable number of UTOPIA output queues with four levels of priority

- Support of ATM traffic management via partial packet discard (PPD), forward explicit congestion notification (FECN), and the cell loss priority (CLP) bit

- Programmable slew rate GTL+ I/O:

- 1.7 Gbits/s cell bus operation

- Programmable as bus arbiter

- Flexible per port cell counters

- Cell header translation and insertion with virtual path identifier (VPI) and virtual channel identifier (VCI) via external SRAM (up to 64K entries)

- Support of network node interface (NNI) and user network interface (UNI) header types with optional generic flow control (GFC) insertion

- Programmable operations and maintenance and resource management (OAM/RM) cell routing

- Support of multicast and broadcast cells per PHY

- Programmable priority for control/data cells transmission onto cell bus

- Eight GPIO pins

- JTAG support

- Optional monitoring of misrouted cells

- Microprocessor interface, supporting both Motorola<sup>®</sup> and Intel<sup>®</sup> modes (multiplexed and nonmultiplexed)

- Control cell transmission and reception through microprocessor port

- Single 3.3 V power supply

- 3.3 V TTL I/O (5 V tolerant)

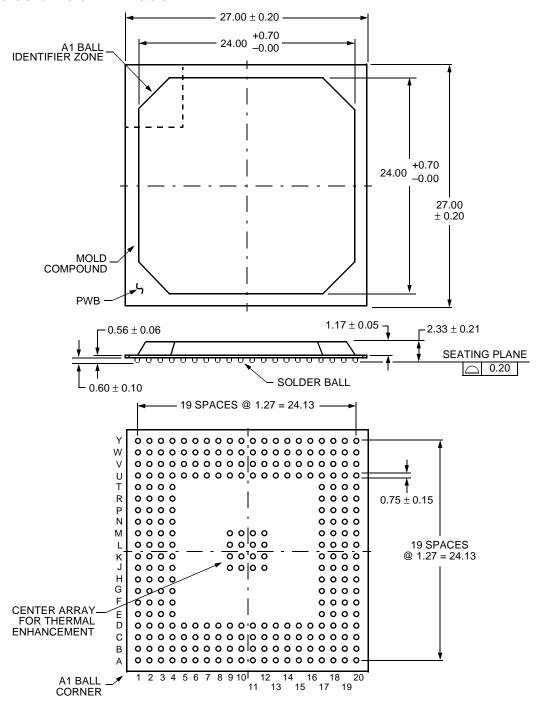

- 272-pin PBGA package

- Industrial temperature range (-40 °C to +85 °C)

- Hot insertion capability

- Compatible with *Transwitch CellBus*®

### 1.2 Applications

- Asymmetric digital subscriber line (ADSL) digital subscriber line access multiplexer (DSLAMs)

- Access gateways

- Access multiplexers/concentrators

- Multiservice access equipment platforms

# **Table of Contents**

| Co | Contents                                                      | Page |

|----|---------------------------------------------------------------|------|

| 1  | Product Overview                                              | 1    |

|    | 1.1 Features                                                  | 1    |

|    | 1.2 Applications                                              |      |

|    | 1.3 Description                                               | 8    |

|    | 1.4 Conventions                                               | 11   |

|    | 1.5 Glossary                                                  | 12   |

| 2  | Pin Description                                               | 13   |

| 3  | Powerup/Reset Sequence                                        | 20   |

| 4  | Hot Insertion                                                 | 21   |

| 5  | PLL Configuration                                             | 22   |

| 6  |                                                               |      |

|    | 6.1 Microprocessor Interface Configuration                    | 23   |

|    | 6.2 Microprocessor Interrupts                                 |      |

|    | 6.3 Accessing the CelXpres T8207 via Microprocessor Interface |      |

|    | 6.3.1 Accessing the Extended Memory Registers                 |      |

|    | 6.3.1.1 Extended Memory Writes                                |      |

|    | 6.3.1.2 Extended Memory Reads                                 |      |

|    | 6.3.2 CelXpres T8207 Access Performance                       |      |

| 7  | · · · · · · · · · · · · · · · · · · ·                         |      |

| 8  |                                                               |      |

|    | 8.1 Look-Up Table RAM                                         |      |

|    | 8.2 Organization                                              |      |

|    | 8.3 Look-Up Procedure                                         |      |

|    | 8.4 Extended Records                                          |      |

|    | 8.5 Diagnostics                                               |      |

| _  | 8.6 Setup                                                     |      |

| 9  |                                                               |      |

|    | 9.1 Incoming UTOPIA Cell Interface                            |      |

|    | 9.1.1 Incoming PHY Mode (Cells Received by T8207)             |      |

|    | 9.1.2 Incoming ATM Mode (Cells Received by T8207)             |      |

|    | 9.2 Outgoing UTOPIA Cell Interface                            |      |

|    | 9.2.1 Outgoing PHY Mode (Cells Sent by T8207)                 |      |

|    | 9.2.2 Outgoing ATM Mode (Cells Sent by T8207)                 |      |

|    | 9.3 Counters                                                  |      |

|    | •                                                             |      |

|    | 9.5 Shared UTOPIA Mode                                        |      |

|    | 9.7 UTOPIA Pill Widdes                                        |      |

| 10 | 0 Cell Bus Interface                                          |      |

| 10 | 10.1 General Architecture                                     |      |

|    | 10.2 Cell Bus Frames                                          |      |

|    | 10.3 Cell Bus Routing Headers                                 |      |

|    | 10.3.1 Control Cells                                          |      |

|    | 10.3.2 Data Cells                                             |      |

|    | 10.3.3 Loopback Cells                                         |      |

|    | 10.3.4 Multicast Routing                                      |      |

|    | 10.3.5 Broadcast Routing                                      |      |

|    | 10.4 Cell Bus Arbitration                                     |      |

|    | 10.5 Cell Bus Monitoring                                      |      |

|    | 10.6 GTL+ Logic                                               |      |

|    | 10.7 Cell Bus Write and Read Clocks                           |      |

|    |                                                               |      |

| Co | ntents                      |                                                               | Page |  |  |  |

|----|-----------------------------|---------------------------------------------------------------|------|--|--|--|

| 11 | SDRAM Inter                 | face                                                          | 64   |  |  |  |

|    |                             | y Configuration                                               |      |  |  |  |

|    |                             | p Sequence                                                    |      |  |  |  |

|    |                             | /<br>// Interface Timing                                      |      |  |  |  |

|    |                             | g                                                             |      |  |  |  |

|    |                             | M Refresh                                                     |      |  |  |  |

|    |                             | /I Throughput                                                 |      |  |  |  |

| 12 |                             | jement                                                        |      |  |  |  |

|    |                             | ss Priority (CLP)                                             |      |  |  |  |

|    |                             | d Explicit Congestion Notification (FECN)                     |      |  |  |  |

|    |                             | Packet Discard (PPD)                                          |      |  |  |  |

| 13 |                             | ccess Port                                                    |      |  |  |  |

|    |                             | ion Register                                                  |      |  |  |  |

|    |                             | ary-Scan Register                                             |      |  |  |  |

| 14 |                             |                                                               |      |  |  |  |

|    |                             | r Types                                                       |      |  |  |  |

|    |                             | Memory Access Registers                                       |      |  |  |  |

|    |                             | Little-Endian Format (big_end = 0) for Extended Memory Access |      |  |  |  |

|    |                             | Registers 30h—37h                                             | 86   |  |  |  |

|    | 14.2.2                      | Big-Endian Format (big_end = 1) for Extended Memory Access    |      |  |  |  |

|    |                             | Registers 30h—37h                                             | 88   |  |  |  |

|    | 14.2.3                      | General-Purpose I/O Control Registers                         |      |  |  |  |

|    |                             | Control Cells                                                 |      |  |  |  |

|    |                             | Multicast Memories                                            |      |  |  |  |

|    |                             | ed Memory Registers                                           |      |  |  |  |

|    |                             | Main Registers                                                |      |  |  |  |

|    |                             | UTOPIA Registers                                              |      |  |  |  |

|    |                             | 14.3.2.1 TX UTOPIA Configuration                              |      |  |  |  |

|    |                             | 14.3.2.2 TX UTOPIA Monitoring                                 |      |  |  |  |

|    |                             | 14.3.2.3 RX UTOPIA Monitoring                                 |      |  |  |  |

|    | 14.3.3                      | SDRAM Registers                                               |      |  |  |  |

|    |                             | 14.3.3.1 SDRAM Control Memory                                 |      |  |  |  |

|    | 14.3.4                      | Various Internal Memories                                     |      |  |  |  |

|    |                             | 14.3.4.1 Control Cell Memories                                |      |  |  |  |

|    |                             | 14.3.4.2 Multicast Number Memories                            |      |  |  |  |

|    |                             | 14.3.4.3 PPD State Memory                                     |      |  |  |  |

|    | 14.3.5                      | · · · · · · · · · · · · · · · · · · ·                         |      |  |  |  |

|    |                             | 14.3.5.1 Look-Up Translation Memory                           |      |  |  |  |

|    |                             | 14.3.5.2 SDRAM Buffer Memory                                  |      |  |  |  |

| 15 | Absolute Max                | imum Ratings                                                  |      |  |  |  |

|    |                             | ed Operating Conditions                                       |      |  |  |  |

|    |                             | cautions                                                      |      |  |  |  |

|    |                             | quirements and Characteristics                                |      |  |  |  |

|    |                             | Information                                                   |      |  |  |  |

|    |                             | trical Characteristics                                        |      |  |  |  |

| 19 |                             | rements                                                       |      |  |  |  |

| -  |                             | ocessor Interface Timing                                      |      |  |  |  |

|    |                             | A Timing                                                      |      |  |  |  |

|    |                             | al LUT Memory Timing                                          |      |  |  |  |

|    |                             | s Timing                                                      |      |  |  |  |

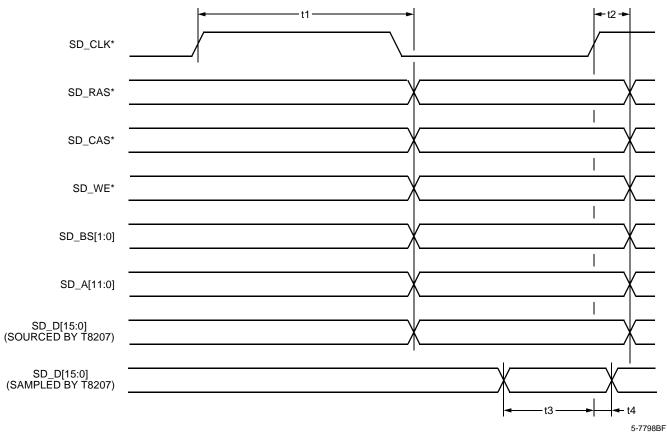

|    | 19.5 SDRAM Interface Timing |                                                               |      |  |  |  |

| 20 |                             | am                                                            |      |  |  |  |

|    |                             | rmation                                                       |      |  |  |  |

| Figure                                                                            | Page |

|-----------------------------------------------------------------------------------|------|

| Figure 1. Functional Block Diagram                                                | 9    |

| Figure 2. Dual Bus Implementation                                                 | 10   |

| Figure 3. 272-Pin PBGA—Top View                                                   | 19   |

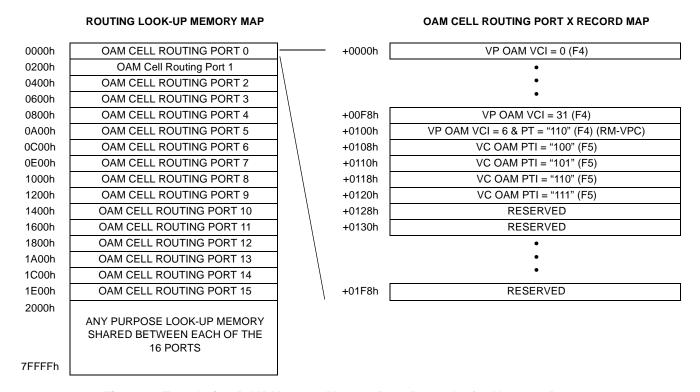

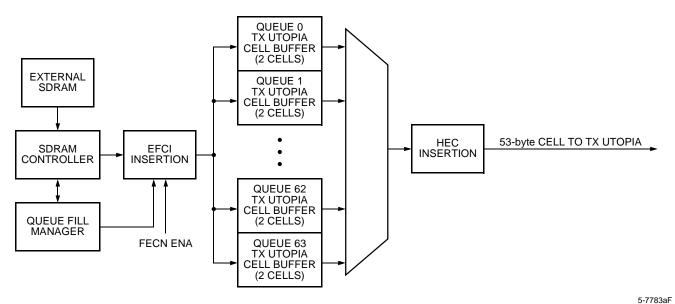

| Figure 4. Translation RAM Memory Map—8-Byte Records, for Up to 16 Ports           | 29   |

| Figure 5. Translation RAM Memory Map—8-Byte Records, for Greater than 16 Ports    | 30   |

| Figure 6. Translation Record Types—8-Byte Records                                 | 31   |

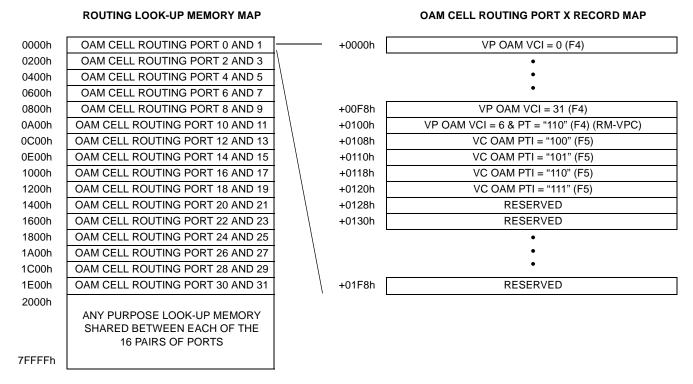

| Figure 7. Translation RAM Flow Diagram                                            |      |

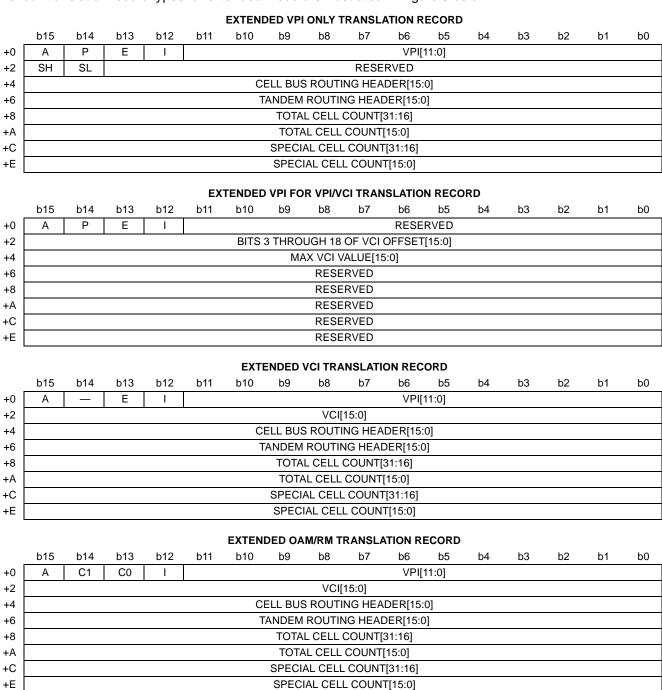

| Figure 8. Translation Record Types—Extended Mode                                  |      |

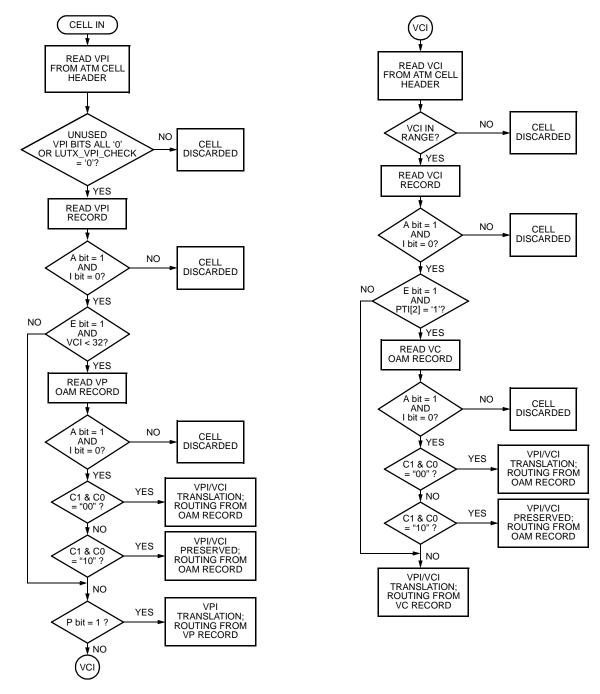

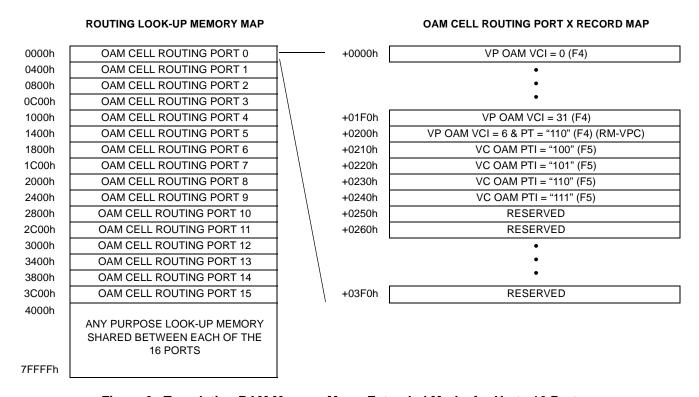

| Figure 9. Translation RAM Memory Map—Extended Mode, for Up to 16 Ports            | 38   |

| Figure 10. Translation RAM Memory Map—Extended Mode, for Greater than 16 Ports    | 39   |

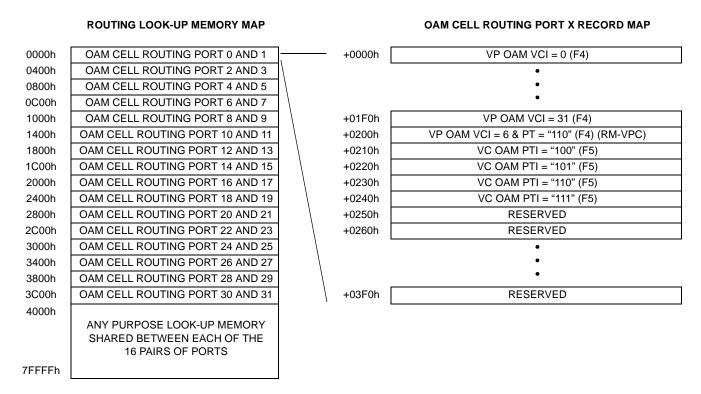

| Figure 11. Queue Priority Multiplexing                                            | 46   |

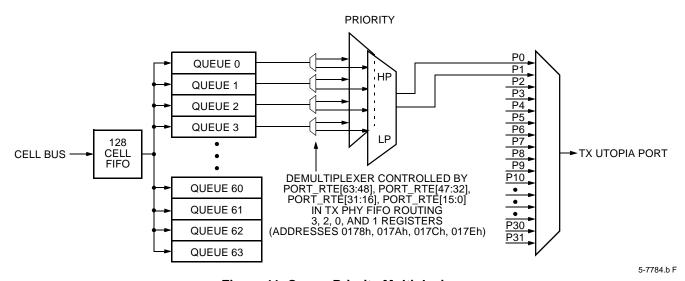

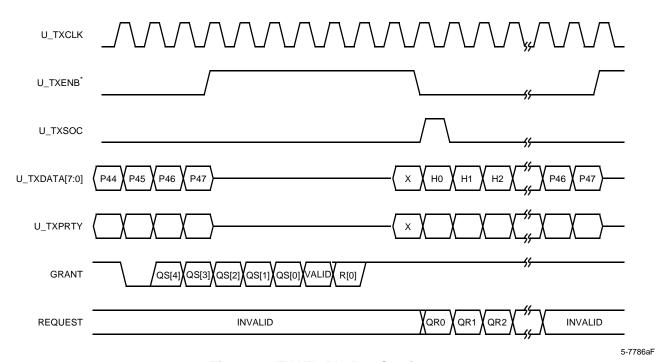

| Figure 12. TX UTOPIA Cell Handling                                                |      |

| Figure 13. TX UTOPIA Bus Sharing                                                  |      |

| Figure 14. Cell Bus Frame Format (Bit Positions for 16 User Mode)                 | 56   |

| Figure 15. Cell Bus Frame Format (Bit Positions for 32 User Mode)                 |      |

| Figure 16. Cell Bus Routing Headers                                               |      |

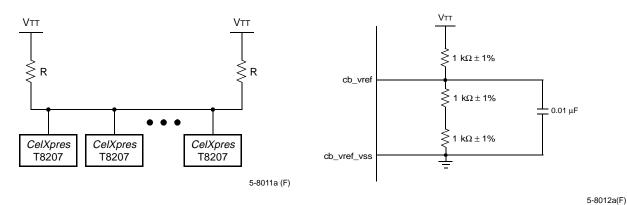

| Figure 17. GTL+ External Circuitry                                                |      |

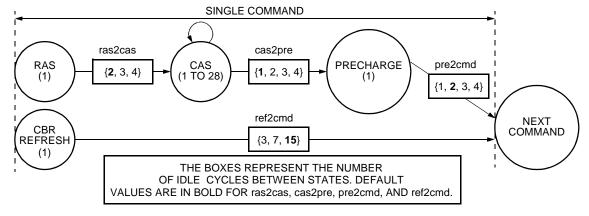

| Figure 18. SDRAM Timing Parameters                                                | 65   |

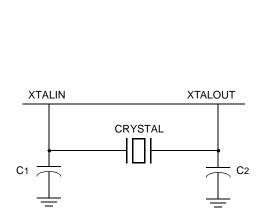

| Figure 19. Crystal                                                                |      |

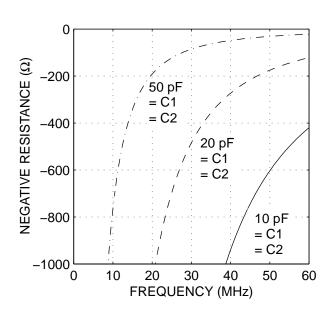

| Figure 20. Negative Resistance Plot                                               |      |

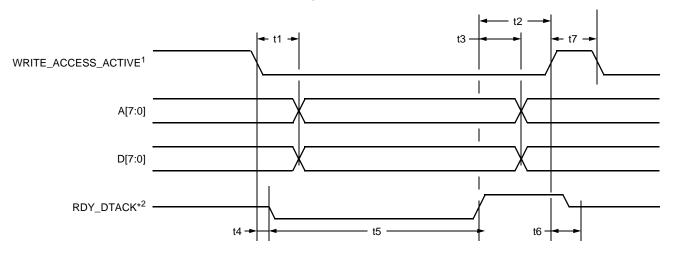

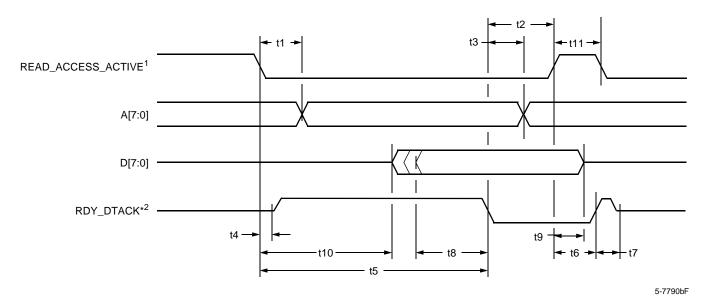

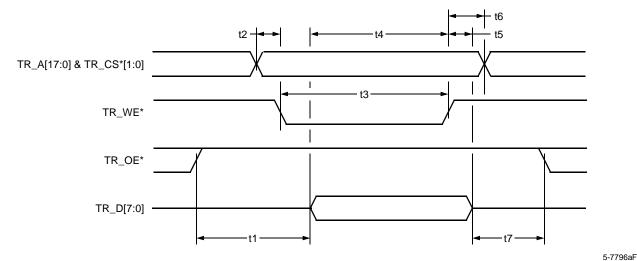

| Figure 21. Nonmultiplexed Intel Mode Write Access Timing                          |      |

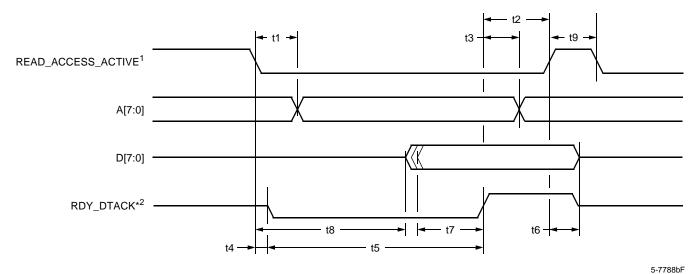

| Figure 22. Nonmultiplexed Intel Mode Read Access Timing                           |      |

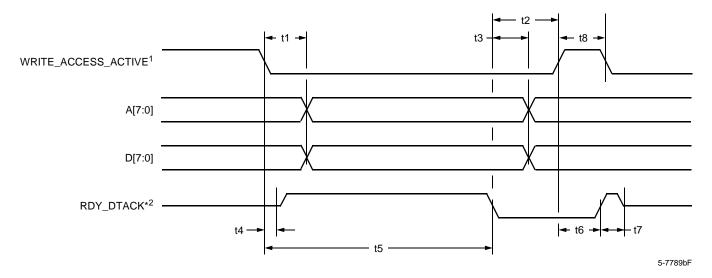

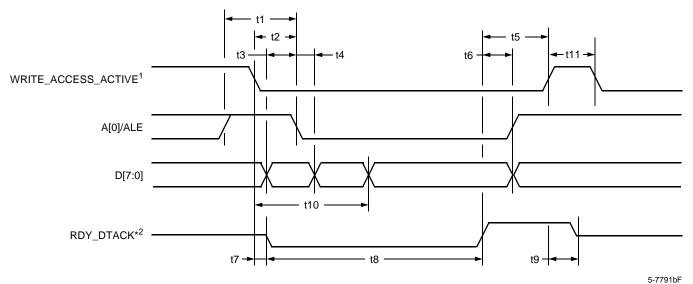

| Figure 23. Motorola Mode Write Access Timing                                      |      |

| Figure 24. Motorola Mode Read Access Timing                                       | 148  |

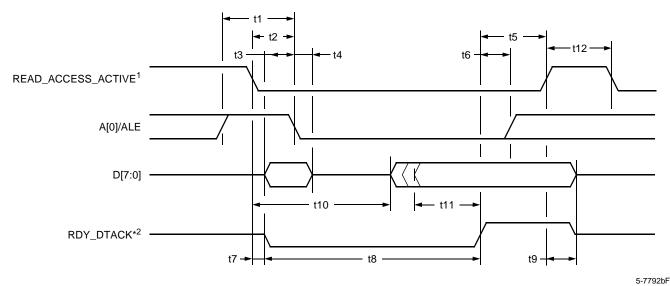

| Figure 25. Multiplexed Intel Mode Write Access Timing                             |      |

| Figure 26. Multiplexed Intel Mode Read Access Timing                              |      |

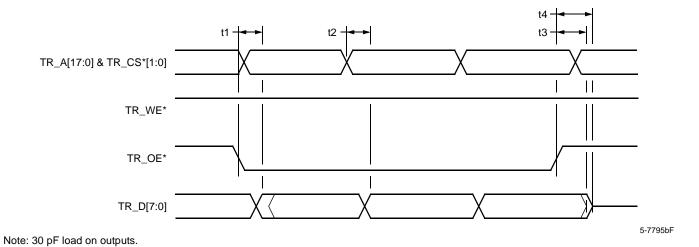

| Figure 27. External LUT Memory Read Timing (cyc_per_acc = 2 and cyc_per_acc = 3)  |      |

| Figure 28. External LUT Memory Write Timing (cyc_per_acc = 2 and cyc_per_acc = 3) |      |

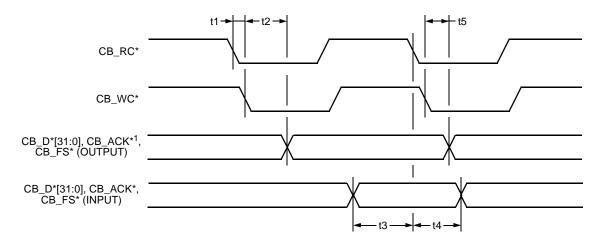

| Figure 29. Cell Bus Timing                                                        |      |

| Figure 30. SDRAM Interface Timing                                                 | 156  |

| Table                                                                                             | Page |

|---------------------------------------------------------------------------------------------------|------|

| Table 1. UTOPIA Pins                                                                              | 13   |

| Table 2. Cell Bus Pins                                                                            | 14   |

| Table 3. SDRAM Interface Pins                                                                     | 15   |

| Table 4. Microprocessor Interface Pins                                                            | 16   |

| Table 5. Translation SRAM Interface                                                               | 17   |

| Table 6. JTAG Pins                                                                                | 17   |

| Table 7. General-Purpose Pins                                                                     | 18   |

| Table 8. Power Pins                                                                               | 18   |

| Table 9. Loop Filter Register Settings                                                            | 22   |

| Table 10. Access Times                                                                            |      |

| Table 11. Active and Ignore Truth Table                                                           |      |

| Table 12. VPI Value Truth Table                                                                   |      |

| Table 13. OAM Routing Control Truth Table                                                         | 32   |

| Table 14. F5 Translation Record Addresses Table—8-Byte Records                                    | 33   |

| Table 15. F5 Translation Record Addresses Table—Extended Mode                                     |      |

| Table 16. Port Numbering for MPHY Configurations                                                  | 51   |

| Table 17. Supported Memory Configurations                                                         | 64   |

| Table 18. Queue Organization and Port Group Address/Priority Bits for 16 Ports with T8207_sel = 1 | 67   |

| Table 19. Queue Organization and Port Group Address/Priority Bits for 32 Ports                    | 69   |

| Table 20. Queue Organization and Port Group Address/Priority Bits for 16 Ports with T8207_sel = 0 | 71   |

| Table 21. Instruction Register                                                                    | 75   |

| Table 22. Boundary-Scan Register Descriptions                                                     | 76   |

| Table 23. Register Map                                                                            | 79   |

| Table 24. Identification 0 (IDNT0) (00h)                                                          | 82   |

| Table 25. Identification 1 (IDNT1) (01h)                                                          | 82   |

| Table 26. Identification 2 (IDNT2) (02h)                                                          |      |

| Table 27. Direct Configuration/Control Register (DCCR) (28h)                                      | 83   |

| Table 28. Interrupt Service Request (ISREQ) (29h)                                                 |      |

| Table 29. mclk PLL Configuration 0 (MPLLCF0) (2Ah)                                                |      |

| Table 30. mclk PLL Configuration 1 (MPLLCF1) (2Bh)                                                |      |

| Table 31. GTL+ Slew Rate Configuration (GTLSRCF) (2Eh)                                            |      |

| Table 32. GTL+ Control (GTLCNTRL) (2Fh)                                                           |      |

| Table 33. Extended Memory Address 1 (Little Endian) (EMA1_LE) (30h)                               |      |

| Table 34. Extended Memory Address 2 (Little Endian) (EMA2_LE) (31h)                               |      |

| Table 35. Extended Memory Address 3 (Little Endian) (EMA3_LE) (32h)                               |      |

| Table 36. Extended Memory Address 4 (Little Endian) (EMA4_LE) (33h)                               |      |

| Table 37. Extended Memory Access (Little Endian) (EMA_LE) (34h)                                   |      |

| Table 38. Extended Memory Data Low (Little Endian) (EMDL_LE) (36h)                                |      |

| Table 39. Extended Memory Data High (Little Endian) (EMDH_LE) (37h)                               |      |

| Table 40. Extended Memory Address 4 (Big Endian) (EMA4_BE) (30h)                                  |      |

| Table 41. Extended Memory Address 3 (Big Endian) (EMA3_BE) (31h)                                  |      |

| Table 42. Extended Memory Address 2 (Big Endian) (EMA2_BE) (32h)                                  |      |

| Table 43. Extended Memory Address 1 (Big Endian) (EMA1_BE) (33h)                                  |      |

| Table 44. Extended Memory Access (Big Endian) (EMA_BE) (34h)                                      |      |

| Table 45. Extended Memory Data High (Big Endian) (EMDH_BE) (36h)                                  |      |

| Table 46. Extended Memory Data Low (Big Endian) (EMDL_BE) (37h)                                   |      |

| Table 47. GPIO Output Enable (GPIO_OE) (39h)                                                      |      |

| Table 48. GPIO Output Value (GPIO_OV) (3Bh)                                                       | 90   |

| Table                                                                                | Page |

|--------------------------------------------------------------------------------------|------|

| Table 49. GPIO Input Value (GPIO_IV) (3Dh)                                           | 90   |

| Table 50. Control Cell Receive Direct Memory (CCRXDM) (60h to 93h)                   |      |

| Table 51. Control Cell Transmit Direct Memory (CCTXDM) (A0h to D7h)                  |      |

| Table 52. PHY Port 0 and Control Cells Multicast Direct Memory (PP0MDM) (E0h to FFh) |      |

| Table 53. Main Configuration 1 (MCF1) (0100h)                                        |      |

| Table 54. Main Interrupt Status 1 (MIS1) (0102h)                                     |      |

| Table 55. Main Interrupt Enable 1 (MIE1) (0104h)                                     |      |

| Table 56. TX UTOPIA Clock Configuration (TXUCCF) (010Ch)                             |      |

| Table 57. RX UTOPIA Clock Configuration (RXUCCF) (010Eh)                             | 97   |

| Table 58. Main Configuration/Control (MCFCT) (0110h)                                 |      |

| Table 59. Main Configuration 2 (MCF2) (0112h)                                        |      |

| Table 60. UTOPIA Configuration (UCF) (0114h)                                         | 100  |

| Table 61. Main Configuration 3 (MCF3) (0116h)                                        |      |

| Table 62. Loopback (LB) (0118h)                                                      |      |

| Table 63. UTOPIA Configuration 3 (UCF3) (011Ah)                                      |      |

| Table 64. UTOPIA Configuration 2 (UCF2) (011Ch)                                      | 101  |

| Table 65. Extended LUT Configuration (ELUTCF) (011Eh)                                | 101  |

| Table 66. Extended LUT Control (ELUTCN) (0120h)                                      | 102  |

| Table 67. Cell Bus Configuration/Status (CBCFS) (0130h)                              | 103  |

| Table 68. Main Interrupt Status 2 (MIS2) (0132h)                                     |      |

| Table 69. Main Interrupt Enable 2 (MIE2) (0134h)                                     | 104  |

| Table 70. Misrouted LUT 1 (MLUT1) (0142h)                                            | 105  |

| Table 71. Misrouted LUT 2 (MLUT2) (0144h)                                            |      |

| Table 72. Misrouted Cell Header High (MCHH) (0146h)                                  | 105  |

| Table 73. Misrouted Cell Header Low (MCHL) (0148h)                                   | 105  |

| Table 74. HEC Interrupt Status 1 (HIS1) (0302h)                                      | 106  |

| Table 75. HEC Interrupt Enable 1 (HIE1) (0304h)                                      | 106  |

| Table 76. HEC Interrupt Status (HIS) (0306h)                                         | 106  |

| Table 77. HEC Interrupt Enable (HIE) (0308h)                                         | 106  |

| Table 78. LUT Interrupt Service Request (LUTISR) (030Eh)                             |      |

| Table 79. LUT X Configuration/Status (LUTXCFS) (0320h to 033Eh)                      | 107  |

| Table 80. Master Queue 3 (MQ3) (0158h)                                               |      |

| Table 81. Master Queue 2 (MQ2) (015Ah)                                               | 108  |

| Table 82. Master Queue 0 (MQ0) (015Ch)                                               |      |

| Table 83. Master Queue 1 (MQ1) (015Eh)                                               |      |

| Table 84. Slave Queue 0 (SQ0) (016Ch)                                                | 110  |

| Table 85. Slave Queue 1 (SQ1) (016Eh)                                                |      |

| Table 86. TX PHY FIFO Routing 3 (TXPFR3) (0178h)                                     |      |

| Table 87. TX PHY FIFO Routing 2 (TXPFR2) (017Ah)                                     |      |

| Table 88. TX PHY FIFO Routing 0 (TXPFR0) (017Ch)                                     |      |

| Table 89. TX PHY FIFO Routing 1 (TXPFR1) (017Eh)                                     |      |

| Table 90. Routing Information 1 (RI1) (0200h)                                        |      |

| Table 91. Routing Information 2 (RI2) (0202h)                                        |      |

| Table 92. Routing Information 3 (RI3) (0204h)                                        |      |

| Table 93. PPD Information 1 (PPDI1) (0206h)                                          |      |

| Table 94. PPD Information 2 (PPDI2) (0208h)                                          |      |

| Table 95. PPD Information 3 (PPDI3) (020Ah)                                          |      |

| Table 96. PPD Information 4 (PPDI4) (020Ch)                                          |      |

| Table 97. PPD Information 5 (PPDI5) (020Eh)                                          |      |

| Table 98. PPD Information 6 (PPDI6) (0210h)                                          |      |

| Table 99. PPD Information 7 (PPDI7) (0212h)                                          | 124  |

| Table                                                                                       | Page |

|---------------------------------------------------------------------------------------------|------|

| Table 100. PPD Memory Write (PPDMW) (0418h)                                                 | 124  |

| Table 101. PHY Port X Transmit Count Structure (PPXTXCNT) (0600h to 067Ch)                  |      |

| Table 102. PHY Port X Receive Count Structure (PPXRXCNT) (0700h to 07F8h)                   |      |

| Table 103. LUT X Configuration 1 Structure (LUTXCF1) (0704h to 077Ch)                       |      |

| Table 104. SDRAM Control (SCT) (0400h)                                                      |      |

| Table 105. SDRAM Interrupt Status (SIS) (0402h)                                             |      |

| Table 106. SDRAM Interrupt Enable (SIE) (0404h)                                             |      |

| Table 107. SDRAM Configuration (SCF) (0408h)                                                |      |

| Table 108. Refresh (RFRSH) (0410h)                                                          |      |

| Table 109. Refresh Lateness (RFRSHL) (0412h)                                                | 130  |

| Table 110. Idle State 1 (IS1) (0420h)                                                       | 130  |

| Table 111. Idle State 2 (IS2) (0422h)                                                       | 130  |

| Table 112. Manual Access State 1 (MAS1) (0424h)                                             | 131  |

| Table 113. Manual Access State 2 (MAS2) (0426h)                                             | 131  |

| Table 114. SDRAM Interrupt Service Request 4 (SISR4) (0438h)                                | 132  |

| Table 115. SDRAM Interrupt Service Request 3 (SISR3) (043Ah)                                | 132  |

| Table 116. SDRAM Interrupt Service Request 1 (SISR1) (043Ch)                                | 132  |

| Table 117. SDRAM Interrupt Service Request 2 (SISR2) (043Eh)                                | 132  |

| Table 118. Queue X (QX) (0440h to 04BEh)                                                    |      |

| Table 119. Queue X Definition Structure (QXDEF) (2000h to 27E0h)                            | 135  |

| Table 120. Control Cell Receive Extended Memory (CCRXEM) (0800h to 0832h)                   | 137  |

| Table 121. Control Cell Transmit Extended Memory (CCTXEM) (0900h to 0936h)                  | 137  |

| Table 122. PHY Port 0 and Control Cells Multicast Extended Memory (PP0MEM) (0C00h to 0C1Eh) |      |

| Table 123. PHY Port X Multicast Memory (PPXMM) (0C20h to 0DE0h)                             | 139  |

| Table 124. PPD Memory (PPDM) (1000h to 13FEh)                                               | 140  |

| Table 125. Translation RAM Memory (TRAM) (100000h to 17FFFEh)                               |      |

| Table 126. SDRAM (SDRAM) (2000000h to 3FFFFFEh)                                             | 141  |

| Table 127. Maximum Rating Parameters and Values                                             | 142  |

| Table 128. Recommended Operating Conditions                                                 | 142  |

| Table 129. HBM ESD Threshold                                                                | 142  |

| Table 130. Crystal Specifications                                                           | 143  |

| Table 131. External Clock Requirements                                                      | 143  |

| Table 132. dc Electrical Characteristics                                                    | 144  |

| Table 133. Input Clocks                                                                     | 145  |

| Table 134. Output Clocks                                                                    |      |

| Table 135. Nonmultiplexed Intel Mode Write Access Timing                                    | 147  |

| Table 136. Nonmultiplexed Intel Mode Read Access Timing                                     | 147  |

| Table 137. Motorola Mode Write Access Timing                                                | 149  |

| Table 138. Motorola Mode Read Access Timing                                                 | 149  |

| Table 139. Multiplexed Intel Mode Write Access Timing                                       | 151  |

| Table 140. Multiplexed Intel Mode Read Access Timing                                        | 151  |

| Table 141. TX UTOPIA Timing (70 pF Load on Outputs)                                         |      |

| Table 142. RX UTOPIA Timing (70 pF Load on Outputs)                                         |      |

| Table 143. External LUT Memory Read Timing (cyc_per_acc = 2)                                |      |

| Table 144. External LUT Memory Read Timing (cyc_per_acc = 3)                                | 154  |

| Table 145. External LUT Memory Write Timing (cyc_per_acc = 2)                               | 154  |

| Table 146. External LUT Memory Write Timing (cyc_per_acc = 3)                               | 154  |

| Table 147. Cell Bus Timing                                                                  |      |

| Table 148. SDRAM Interface Timing                                                           | 156  |

### 1.3 Description

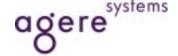

The *CelXpres* T8207 device integrates all of the required functionality to transport ATM cells across a backplane architecture with high-speed cell traffic exceeding 1.5 Gbits/s to a maximum of 32 destinations. The management of multiple service categories and monitoring of performance on ATM and PHY interfaces is incorporated in the device's functionality. Traffic delivery to multi-PHYs (MPHYs) is managed through the UTOPIA interface.

The T8207 device meets the ATM Forum's universal test and operations PHY interface for ATM (UTOPIA) Level 1, Version 2.01 and Level 2, Version 1.0 specifications for cell-level handshake and MPHY data path operation with rates up to 353 Mbits/s. The T8207 supports the required MPHY operation as described in Sections 4.1 and 4.2 of the ATM Forum's Level 2 specification. The T8207 supports MPHY operation with one transmit cell available (TxCLAV) signal and one receive cell available (RxCLAV) signal for up to 16 PHY ports for an 8-bit UTOPIA 2 interface configuration. With two transmit cells available/enable (TxCLAV/enb\*) pairs of signals and receive cells available/enable (RxCLAV/enb\*) pairs of signals, 32 MPHYs can be supported. In addition to the required UTOPIA signals, the optional transmit parity (TxPRTY) and receive parity (RxPRTY) signals are provided.

The T8207 may be configured as an ATM or PHY level device providing cell routing between UTOPIA and a 32-bit wide cell bus. In addition to the 32 data signals, the bus has the following signals:

- Read clock

- Write clock

- Frame sync

- Acknowledge

ATM cells arriving from the UTOPIA interface may get VPI and VCI translation and routing information from a lookup table in external SRAM. An external synchronous dynamic random access memory (SDRAM) is used to extend the buffering for ATM cells destined for the UTOPIA interface. This external SDRAM may be partitioned into four or less independently sized queues per PHY for a configuration of 16 MPHYs and two queues per PHY or a programmable number of queues per PHY for a configuration of 32 MPHYs. The number of cells per queue per PHY is programmable. The four queues may be used to implement quality of service (QoS) using different priorities for each queue.

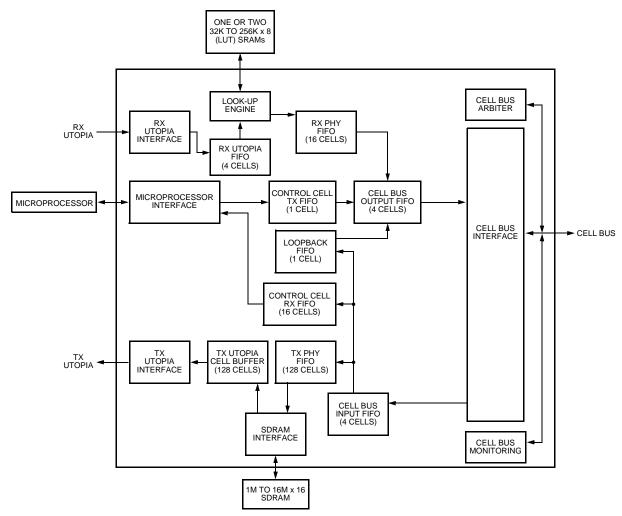

The CelXpres T8207 provides a shared UTOPIA mode, which allows two devices on different cell buses to share the same UTOPIA bus in ATM mode. Using a glueless interface, the two T8207 devices resolve queue priorities and arbitrate the use of the UTOPIA bus. This shared mode can be used to provide redundancy or increase UTOPIA traffic capacity by supporting traffic from multiple cell buses.

The *CelXpres* T8207 supports the transport of control and loopback cells with an external microprocessor. Control or loopback cells may be sent or received through the microprocessor interface. The 8-bit microprocessor interface may be configured to be *Motorola* or *Intel* compatible and is used to configure and monitor the device.

Figure 1. Functional Block Diagram

5-7542E (F)

Figure 2 illustrates the use of the *CelXpres* T8207 in a system with dual backplane cell buses using shared UTOPIA mode. In this configuration, both T8207 devices on each card receive cells from the UTOPIA bus, and each device uses its translation table to determine if the cell should be transmitted on its backplane cell bus. In the egress direction, each T8207 device receives cells from its cell bus to transmit on the UTOPIA bus. MPHY arbitration and queue priorities are resolved using a two-wire interface between the two devices. Although a single ATM virtual connection is not typically established on both backplane cell buses simultaneously, no restrictions exist for a single PHY utilizing both backplane cell buses for different virtual connections supporting higher throughput from two bus interfaces. Redundant bus configurations can be supported in the event of a bus failure with T8207 devices by configuring one device to assume bus responsibility from the other.

Figure 2. Dual Bus Implementation

0041

### 1.4 Conventions

- All numbers in this document are decimals unless otherwise specified.

- Hexadecimal numbers can be identified by the 'h' suffix, e.g., A5h.

- Binary numbers are either in double quotes for multiple bits or in single quotes for individual bits, e.g., "1001" and '0.'

- A byte is 8 bits, a word is 16 bits, and a double word (dword) is 32 bits.

- A binary value of '1' is high, and a binary value of '0' is low.

- To clear is to change one or multiple bit values to '0.'

- To set is to change one or multiple bit values to '1.'

- All memory addresses are specified in hexadecimal.

- Addresses are converted from bytes to words or double words using the little-endian format, unless otherwise specified.

- A signal name with a trailing asterisk is active-low, e.g., sd\_we\*.

- Bits y to x will be designated bits (y:x).

## 1.5 Glossary

#### **Bus Cell:**

Major content of the cell bus frame consisting of 56 bytes, 4 bytes for routing options and 52 bytes for the ATM cell content, which excludes the HEC. The bus cell is preceded by the 4 bytes of request and followed by the 4 bytes of grant and parity information.

#### **CLP**

Cell loss priority. The CLP is a 1-bit field in the cell header that becomes set when the cell violates the negotiated quality of service parameters.

#### EFCI:

Explicit forward congestion indication. The EFCI is a 1-bit field in the PTI field of the cell header that becomes set when the cell encounters congestion.

#### FECN:

Forward explicit congestion notification. FECN is a method used by the network to signal to the destination when congestion is encountered. The EFCI bit is used to indicate the congestion.

#### GFC:

Generic flow control. The GFC is a 4-bit field in the cell header that may be used by a UNI to support traffic and congestion control. Typically, this field is programmed to "0000" indicating that generic flow control is not supported. GFC may be used in priority protocols.

### **Grant Section:**

Last 4 bytes of the cell bus frame. The grant section occurs during the last clock cycle of the cell bus frame. During this cycle, the cell bus arbiter indicates which T8207 may transmit during the next bus cell unit of the cell bus frame. A parity vector is also transmitted during the grant section.

#### HEC:

Header error control. The HEC is a 1-byte field in the cell header used for bit error detection and correction in the header.

#### NNI:

Network node interface. The NNI is the interface between nodes in the public network.

#### OAM Cell:

Operations and maintenance cell. An OAM cell carries local management information.

#### PPD.

Partial packet discard. PPD is a technique to relieve congestion. When one cell in a packet is lost, all remaining cells in the packet, except the last, are discarded.

### PTI:

Payload type identifier. The PTI is a 3-bit field in the cell header containing information about the type of data (user, OAM, or traffic management) and about encountered congestion.

#### QoS:

Quality of service. Quality of service parameters define the performance requirements and characteristics for traffic on an assigned channel. Some parameters include cell loss ratio, cell transfer delay, cell delay variation, peak cell rate, and sustained cell rate.

#### RМ

Resource management. RM is the local management of network resources.

#### **RxCLAV:**

Receive cell available signal as described in the ATM Forum's universal test and operations PHY interface for ATM (UTOPIA) Level 1, Version 2.01 and Level 2, Version 1.0 specifications.

#### **RXENB**

Receive enable signal as described in the ATM Forum's universal test and operations PHY interface for ATM (UTOPIA) Level 1, Version 2.01 and Level 2, Version 1.0 specifications.

#### **TxCLAV**

Transmit cell available signal as described in the ATM Forum's universal test and operations PHY interface for ATM (UTOPIA) Level 1, Version 2.01 and Level 2, Version 1.0 specifications.

### TxENB:

Transmit enable signal as described in the ATM Forum's universal test and operations PHY interface for ATM (UTOPIA) Level 1, Version 2.01 and Level 2, Version 1.0 specifications.

#### UNI:

User network interface. The UNI is the interface between a private network node and a public network node.

### VCI:

Virtual channel identifier. The VCI is a 2-byte field in the cell header that identifies the virtual channel used by the cell.

### VPI:

Virtual path identifier. The VPI is an 8-bit field in the UNI cell header or a 12-bit field in the NNI cell header that identifies the virtual path of the cell.

# 2 Pin Description

This section defines the *CelXpres* T8207 pins. All TTL compatible inputs or I/O are 5 V tolerant. No GTL+ inputs or I/O are 5 V tolerant.

**Table 1. UTOPIA Pins**

| Symbol        | Ball                                         | Reset | Туре       | Name/Description                                                                                                                                                                                                  |

|---------------|----------------------------------------------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Зушьог        |                                              | Value | туре       | Name/Description                                                                                                                                                                                                  |

| u_rxaddr[4:0] | R2, P3, R1, P2,<br>P1                        | Z     | I/O        | <b>RX UTOPIA Address Lines.</b> 10 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                                                    |

| u_rxdata[7:0] | V2, U3, T4, V1,<br>U2, T3, U1, T2            | _     | Ι          | RX UTOPIA Data Lines. TTL compatible input, 5 V tolerant.                                                                                                                                                         |

| u_rxclk       | T1                                           | Z     | I/O        | RX UTOPIA Clock. 10 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                                                                   |

| u_rxsoc       | P4                                           | _     | I          | <b>RX UTOPIA Start of Cell (Active-High).</b> TTL compatible input, 5 V tolerant.                                                                                                                                 |

| u_rxclav[0]   | L4                                           | Z     | I/O        | RX UTOPIA PHY 0 Cell Available (Active-High). Main RX cell available in single PHY mode. 10 mA drive, TTL compatible I/O, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                  |

| u_rxclav[3:1] | M3, M2, M1                                   | _     | I          | RX UTOPIA Cell Available Lines (Active-High). TTL compatible input, 5 V tolerant. These pins have an internal 50 k $\Omega$ pull-up resistor.                                                                     |

| u_rxenb*[0]   | M4                                           | Z     | I/O        | <b>RX UTOPIA PHY 0 Enable (Active-Low).</b> Main RX enable in single PHY mode. 10 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                     |

| u_rxenb*[3:1] | N3, N2, N1                                   | Z     | I/O        | <b>RX UTOPIA PHY Enable Lines (Active-Low).</b> 10 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                                    |

| u_rxprty      | R3                                           | _     | I          | <b>RX UTOPIA Odd Parity.</b> TTL compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                                                                                         |

| u_txaddr[4:0] | P17, R19, R20,<br>P18, P19                   | Z     | I/O        | <b>TX UTOPIA Address Lines.</b> 10 mA drive, TTL compatible I/O. 5 V tolerant.                                                                                                                                    |

| u_txdata[7:0] | W20, V19, U19,<br>U18, T17, V20,<br>U20, T18 | Z     | 0          | TX UTOPIA Data Lines. 10 mA drive, TTL compatible output.                                                                                                                                                         |

| u_txclk       | R18                                          | Z     | I/O        | TX UTOPIA Clock. 10 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                                                                   |

| u_txsoc       | T20                                          | Z     | 0          | TX UTOPIA Start of Cell (Active-High). 10 mA drive, TTL compatible output.                                                                                                                                        |

| u_txclav[0]   | M20                                          | Z     | I/O        | TX UTOPIA PHY 0 Cell Available (Active-High). Main TX cell available in single PHY mode. 10 mA drive, TTL compatible I/O. 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                  |

| u_txclav[3:1] | M17, M18, M19                                |       | _          | TX UTOPIA Cell Available Lines (Active-High). TTL compatible input, 5 V tolerant. These pins have an internal 50 k $\Omega$ pull-up resistor.                                                                     |

| u_txenb*[0]   | N20                                          | Z     | <u>/</u> O | TX UTOPIA PHY 0 Enable (Active-Low). Main TX enable in single PHY mode. 10 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                            |

| u_txenb*[3:1] | P20, N18, N19                                | Z     | 0          | <b>TX UTOPIA Enable Lines (Active-Low).</b> 10 mA drive, TTL compatible output.                                                                                                                                   |

| u_txprty      | T19                                          | Z     | 0          | TX UTOPIA Odd Parity. 10 mA drive, TTL compatible output.                                                                                                                                                         |

| u_shr_o       | V16                                          | 1     | 0          | Shared UTOPIA Output. Used as grant if device is shared UTOPIA master or as request if device is shared UTOPIA slave. 4 mA drive, TTL compatible output. This pin has an internal 50 k $\Omega$ pull-up resistor. |

| u_shr_i       | W17                                          |       | Ι          | Shared UTOPIA Input. Used as request if device is shared UTOPIA master or as grant if chip is shared UTOPIA slave. TTL compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.   |

Table 2. Cell Bus Pins

| Symbol      | Ball                                                                                                                                                                      | Reset<br>Value | Туре | Name/Description                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ua*[4:0]    | B18, B17, C17,<br>D16, A18                                                                                                                                                |                | I    | <b>Unit Address Lines (Active-Low).</b> Address assigned to device for cell bus identification. TTL compatible input, 5 V tolerant.                                                                                                        |

| cb_d*[31:0] | B5, C6, D7, A5,<br>B6, C7, A6, B7,<br>A7, C8, B8, A8,<br>D9, C9, B9, A9,<br>A11, C11, B11,<br>A12, B12, C12,<br>D12, A13, B13,<br>C13, A14, B14,<br>C14, A15, B15,<br>D14 | Z              | 1/0  | Cell Bus Data Lines (Active-Low). GTL+ I/O.                                                                                                                                                                                                |

| cb_wc*      | A10                                                                                                                                                                       |                | _    | Cell Bus Write Clock (Active-Low). Uses falling edge to output data on cell bus. Write and read clocks have the same frequency but different phase. GTL+ input.                                                                            |

| cb_rc*      | B10                                                                                                                                                                       |                | Ι    | Cell Bus Read Clock (Active-Low). Uses falling edge to latch data from cell bus. Write and read clocks have the same frequency but different phase. GTL+ input.                                                                            |

| cb_fs*      | C15                                                                                                                                                                       | Z              | I/O  | Cell Bus Frame Sync (Active-Low). GTL+ I/O.                                                                                                                                                                                                |

| cb_ack*     | B16                                                                                                                                                                       | Z              | I/O  | Cell Bus Acknowledge Signal (Active-Low). Driven low on cycle 0 of the following frame when a valid cell is received from the cell bus. This signal is not driven for broadcast or multicast cells. GTL+ I/O.                              |

| arb_en*     | A17                                                                                                                                                                       |                | Ι    | Cell Bus Arbiter Enable (Active-Low). Cell bus arbiter enable. Only one device on the cell bus may be configured as arbiter. TTL-compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                  |

| cb_disable* | C16                                                                                                                                                                       |                | -    | Cell Bus Disable (Active-Low). CMOS input that 3-states all GTL+ outputs when low, but GTL+ buffer inputs are active. This pin has an internal 50 k $\Omega$ pull-up resistor.                                                             |

| cb_iref     | A4                                                                                                                                                                        |                | Ι    | Cell Bus Current Reference. Precision current reference for GTL+ buffers. A 1 k $\Omega$ , 1% resistor must be connected between this pin and GND.                                                                                         |

| cb_vref     | D10                                                                                                                                                                       |                | I    | <b>Cell Bus Voltage Reference.</b> GTL+ buffer threshold voltage reference (1.0 V typical). This voltage reference is 2/3 V $\tau\tau$ , created using a voltage divider of three 1 kΩ, 1% resistors between V $\tau\tau$ and cb_vref_vss. |

| cb_vref_vss | C10                                                                                                                                                                       | _              | _    | Cell Bus Voltage Reference Ground.                                                                                                                                                                                                         |

**Table 3. SDRAM Interface Pins**

| Symbol     | Ball                                                                                         | Reset<br>Value | Туре | Name/Description                                                                                                                                                                                                 |

|------------|----------------------------------------------------------------------------------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sd_a[11:0] | L19, L18, L20,<br>K20, K19, K18,<br>K17, J20, J19,<br>J18, J17, H20                          | Х              | 0    | <b>SDRAM Address Lines.</b> 7 mA drive, TTL compatible output. These buffers are 50 $\Omega$ impedance matching buffers. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance.             |

| sd_d[15:0] | F19, E20, G17,<br>F18, E19, D20,<br>E18, D19, C20<br>E17, D18, C19,<br>B20, C18, B19,<br>A20 | Z              | I/O  | SDRAM Data Lines. 7 mA drive, TTL compatible I/O. These buffers are 50 $\Omega$ impedance matching buffers. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance.                          |

| sd_bs[1:0] | H18, G20                                                                                     | Х              | 0    | SDRAM Bank Selects. 7 mA drive, TTL compatible output. These buffers are 50 $\Omega$ impedance matching buffers. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance.                     |

| sd_ras*    | G19                                                                                          | 1              | 0    | SDRAM Row Address Select (Active-Low). 7 mA drive, TTL compatible output. This buffer is a 50 $\Omega$ impedance matching buffer. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance.    |

| sd_cas*    | F20                                                                                          | 1              | 0    | SDRAM Column Address Select (Active-Low). 7 mA drive, TTL compatible output. This buffer is a 50 $\Omega$ impedance matching buffer. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance. |

| sd_we*     | G18                                                                                          | 1              | 0    | SDRAM Write Enable (Active-Low). 7 mA drive, TTL compatible output. This buffer is a 50 $\Omega$ impedance matching buffer. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance.          |

| sd_clk     | H19                                                                                          | Z              | I/O  | <b>SDRAM Clock.</b> 7 mA drive, TTL compatible output. This buffer is a 50 $\Omega$ impedance matching buffer. Long printed-wiring board traces should have 50 $\Omega$ nominal impedance.                       |

| sd_iref    | A19                                                                                          | _              | I    | SDRAM Current Reference. Precision current reference for SDRAM buffers. A 1 k $\Omega$ , 1% resistor must be connected between this pin and GND.                                                                 |

**Table 4. Microprocessor Interface Pins**

| Symbol     | Ball                                    | Reset<br>Value | Туре | Name/Description                                                                                                                                                                                               |

|------------|-----------------------------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a[7:1]     | W6, Y6, V7, W7,<br>Y7, V8, W8           | _              | I    | Microprocessor Port Address Lines. Most significant 7 bits of the address bus. TTL compatible input, 5 V tolerant.                                                                                             |

| a[0]/ale   | Y8                                      |                | I    | Microprocessor Port Address 0/Address Latch Enable. Least significant bit of the address bus in nonmultiplexed mode or address latch enable in multiplexed mode.                                               |

| d[7:0]     | U9, V9 W9, Y9,<br>W10, V10, Y10,<br>Y11 | Z              | I/O  | <b>Microprocessor Port Data Lines.</b> 6 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                                           |

| sel*       | W12                                     | _              | I    | <b>Microprocessor Chip Select (Active-Low).</b> TTL compatible input, 5 V tolerant.                                                                                                                            |

| wr*_ds*    | V12                                     |                | I    | Microprocessor Write/Data Strobe. Active-low write enable in <i>Intel</i> mode. Active-low data strobe in <i>Motorola</i> mode. TTL compatible input, 5 V tolerant.                                            |

| rd*_rw*    | U12                                     |                | I    | Microprocessor Read/Write. Active-low read enable in<br>Intel mode, or read/write* enable in Motorola mode, where read is active-high and write is active-low. TTL compatible input, 5 V tolerant.             |

| int_irq*   | Y12                                     | 0/1            | 0    | CPU Interrupt. Active-high in <i>Intel</i> mode and active-low in <i>Motorola</i> mode. 4 mA drive, TTL compatible output.                                                                                     |

| rdy_dtack* | U11                                     | Z              | 0    | Ready/Data Transfer Acknowledge. Active-high ready signal in <i>Intel</i> mode and active-low data transfer acknowledge in <i>Motorola</i> mode. Indicates access complete. 6 mA drive, TTL compatible output. |

| mot_sel    | Y13                                     |                |      | Intel/Motorola Selection. '0' = Intel, '1' = Motorola. TTL compatible input, 5 V tolerant.                                                                                                                     |

| mux        | W13                                     | _              | I    | <b>Microprocessor Multiplex Select.</b> Active-high for multiplex mode. TTL compatible input, 5 V tolerant.                                                                                                    |

**Table 5. Translation SRAM Interface**

| Symbol      | Ball                                                                               | Reset<br>Value | Туре | Name/Description                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tr_a[17:0]  | L3, L2, L1, K1,<br>K3, K2, J1, J2,<br>J3, J4, H1, H2,<br>H3, G1, G2, G3,<br>F1, F2 | Х              | 0    | <b>Translation RAM Address Lines.</b> 4 mA drive, TTL compatible output.                                                                                                                  |

| tr_d[7:0]   | E3, D1, C1, E4,<br>D3, D2, C2, B1                                                  | Z              | I/O  | <b>Translation RAM Data Lines.</b> 4 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                          |

| tr_cs*[1:0] | E1, E2                                                                             | 1              | 0    | Translation RAM Chip Selects (Active-Low). Chip selects to select one of two external SRAMs. For connection to one external device, tr_cs*[0] is used. 4 mA drive, TTL compatible output. |

| tr_oe*      | F3                                                                                 | 1              | 0    | External RAM Output Enable (Active-Low). 4 mA drive, TTL compatible output.                                                                                                               |

| tr_we*      | G4                                                                                 | 1              | 0    | External RAM Write Enable (Active-Low). 4 mA drive, TTL compatible output.                                                                                                                |

### **Table 6. JTAG Pins**

| Symbol     | Ball | Reset<br>Value | Туре | Name/Description                                                                                                                                                                    |

|------------|------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| jtag_tdi   | Y16  | _              | İ    | Test Data Input (JTAG). TTL compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                                                                |

| jtag_tdo   | W16  | Х              | 0    | <b>Test Data Output (JTAG).</b> 4 mA drive, TTL compatible output.                                                                                                                  |

| jtag_trst* | W15  |                | I    | Test Reset (JTAG) (Active-Low). Should be pulled low when part is in normal operation. TTL compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor. |

| jtag_tclk  | V15  | _              | I    | Test Clock (JTAG). TTL compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                                                                     |

| jtag_tms   | U14  | _              | I    | <b>Test Mode Select (JTAG).</b> TTL compatible input, 5 V tolerant. This pin has an internal 50 k $\Omega$ pull-up resistor.                                                        |

**Table 7. General-Purpose Pins**

| Symbol    | Ball                                                                                                                                              | Reset<br>Value | Туре | Name/Description                                                                                                                                                                                                                                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gpio[7:0] | U5, Y3, Y4, V5,<br>W5, Y5, V6, U7                                                                                                                 | _              | I/O  | <b>General-Purpose I/O.</b> 4 mA drive, TTL compatible I/O, 5 V tolerant.                                                                                                                                                                          |

| reset*    | V14                                                                                                                                               |                | Ι    | <b>Reset (Active-Low).</b> Schmitt trigger, TTL compatible input, 5 V tolerant.                                                                                                                                                                    |

| xtalin    | V13                                                                                                                                               |                | ı    | <b>Crystal Input (pclk).</b> This input may be driven by either a crystal or an external clock. If a crystal is used, connect it between this pin and xtalout and connect the appropriately valued capacitor from this pin to Vss.                 |

|           |                                                                                                                                                   |                |      | If an external clock is used, this is a 5 V tolerant CMOS input with 50 MHz max input frequency.                                                                                                                                                   |

| xtalout   | Y14                                                                                                                                               | _              | 0    | <b>Crystal Output Feedback.</b> If a crystal is used, connect it between this pin and xtalin and connect the appropriately valued capacitor from this pin to Vss. If an external clock is used to drive xtalin, this pin must be left unconnected. |

| cko       | W11                                                                                                                                               |                | 0    | <b>Buffered Clock Output.</b> If enabled, pclk is output on this pin. 8 mA drive, TTL compatible output. This pin is high impedance if not enabled.                                                                                                |

| cko_e     | V11                                                                                                                                               |                | I    | <b>CKO Enable.</b> Enable for buffered clock output. If cko is not used, tie this enable pin low. Active-high, TTL compatible input, 5 V tolerant.                                                                                                 |

| NC        | A2, A3, A16, B2,<br>B3, B4, C3, C4,<br>C5, D5, U16, V3,<br>V4, V17, V18,<br>W1, W2, W3,<br>W4, W18, W19,<br>Y1, Y2, Y15,<br>Y17, Y18, Y19,<br>Y20 | _              | _    | No Connection. Reserved.                                                                                                                                                                                                                           |

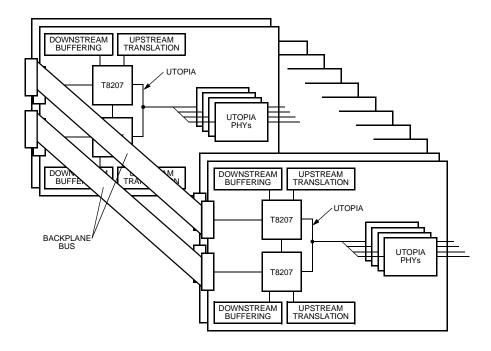

**Table 8. Power Pins**

| Symbol | Ball                                                                                                                                 | Name/Description                                                                                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Vdd    | D6, D11, D15, F4, F17, K4, L17, R4, R17, U6, U10, U15                                                                                | <b>Power.</b> 3.3 V. These pins should be properly                                                                 |

|        |                                                                                                                                      | decoupled using 0.01 μF or 0.1 μF capacitors.                                                                      |

| Vss    | A1, D4, D8, D13, D17, H4, H17, J9, J10, J11, J12, K9, K10, K11, K12, L9, L10, L11, L12, M9, M10, M11, M12, N4, N17, U4, U8, U13, U17 | Ground.                                                                                                            |

| Vdda   | W14                                                                                                                                  | Clock Oscillator Power. 3.3 V. This pin should be properly decoupled using 0.01 $\mu F$ or 0.1 $\mu F$ capacitors. |

Figure 3. 272-Pin PBGA—Top View

5-8013(f)

## 3 Powerup/Reset Sequence

One of the following two methods may be used to reset the T8207:

- 1. Assert the reset\* pin low for at least 5 pclk periods or 100 ns, whichever is longer, and then return it high for a hardware reset. For a powerup reset, the reset\* pin should be held low for at least 5 pclk periods or 100 ns, whichever is longer, after the power supply ramps to its operating voltage and the crystal oscillator is stable.

- 2. Write both the srst\* and srst\_reg\* bits in the direct configuration/control register (address 28h) to '0,' and leave them at that value for at least 1 µs to perform a software reset.

The device is now in the reset state, and the following start-up procedure must be executed to ensure proper operation:

- 1. After pclk (xtalin) is provided to the T8207, and the device is in the reset state:

- A. Write the mclk PLL configuration 0 and 1 registers at addresses 2Ah and 2Bh.

- B. Continue after the PLL has stabilized in 100 µs.

- 2. Set the srst\_reg\* bit (to take the main registers out of reset), and program the cyc\_per\_acc and big\_end bits in the direct configuration/control register (address 28h).

- 3. Wait 1 µs for the circuit to stabilize.

## Extended memory accesses may now be performed only to the main register group.

- 4. Write the desired values to the main configuration 1 register (address 0100h), the TX UTOPIA clock configuration register (address 010Ch), and the RX UTOPIA clock configuration register (address 010Eh) in the extended memory registers. These bits should not be modified at a later time without returning to the reset state.

- 5. Program the main configuration 2 register (address 0112h) and the UTOPIA configuration register (address 0114h). These registers should not be modified at a later time without returning to the reset state.

- 6. Program the cb\_arb\_sel and cb\_usr\_mode bits in the cell bus configuration/status register (address 0130h).

- 7. Wait one clock period of the slowest clock (cell bus, UTOPIA, or pclk) for the circuit to stabilize.

- 8. Set the srst\* bit in the direct configuration/control register (address 28h).

- Wait three clock periods of the slowest clock (cell bus, UTOPIA, or pclk) for the circuit to stabilize.

### The T8207 device is now out of reset state.

- 10. Initialize the SDRAM per the SDRAM specifications.

- 11. Enable the SDRAM by setting the sdram\_en bit in the SDRAM control register (address 0400h).

- 12. Initialize the LUT to benign values (recommended).

- 13. Initialize the multicast memory to all '0' (recommended).

- 14. Program the three routing information registers (addresses 0200h through 0204h) and the seven PPD information registers (addresses 0206h through 0212h).

### 4 Hot Insertion

When a connector with proper pin sequencing is used, the Agere Systems Inc. GTL+ buffers withstand hot insertion into a backplane without corrupting the cell bus or damaging the device. The ground pins on the connector should extend beyond all other pins so that the ground connections are made first. In addition, the power pins on the connector should extend beyond the signal pins so that the power connections are made before the signal but after the ground connections.

During hot insertion, the cell bus is not corrupted because the GTL+ outputs go to a high-impedance state during the powerup reset. Therefore, proper timing should be met in the external powerup reset circuit.

## 5 PLL Configuration

The frequency of the device's main clock (mclk) is derived from the clock at the xtalin input (pclk) and is given by the following equation when the PLL is engaged:

$$f_{\text{mclk}} = f_{\text{pclk}} \ x \frac{(M+2)}{(2 \times (MOD8(N+1)+1))}$$

### Note: When the PLL is engaged, mclk is the output of the PLL.

M and N are the pll\_m[4:0] and pll\_n[2:0] counter values in the mclk PLL configuration 1 register (address 2Bh) and must be set so that the voltage-controlled oscillator (VCO) operates in the appropriate range. The maximum value for fmclk is 100 MHz. The valid range for M is between 2 and 22 inclusive, and the valid range for N is between 0 and 7 inclusive. When multiple sets of values can achieve the desired result, choose the lowest value of M and the corresponding value for N.

### Note: The output of the PLL must always be at least 50 MHz.

The loop filter must be set properly for correct operation of the PLL. The proper setting of the loop filter bits, If[3:0], in the mclk PLL configuration 0 register (address 2Ah) is determined by the chosen value for M. The following table lists the If[3:0] settings for given values of M. Typical PLL lock-in time is 50  $\mu$ s.

**Table 9. Loop Filter Register Settings**

| M     | Mclk PLL Configuration 0 (2Ah) If[3:0] |

|-------|----------------------------------------|

| 22    | "0111"                                 |

| 16—21 | "0110"                                 |

| 10—15 | "0101"                                 |

| 6—9   | "0100"                                 |

| 4—5   | "0011"                                 |

| 2—3   | "0010"                                 |

#### **PLL Configuration Example:**

Given a pclk frequency of 50 MHz and a desired mclk frequency of 100 MHz, the proper values of M, N, and If[3:0] are the following:

M = 2

N = 7

If[3:0] = "0010"

The bypass PLL (bypb) and PLL enable (pllen) bits are used to select the source of mclk for the T8207. To select the output of the PLL as the clock, both bits must be programmed to '1,' and to select pclk as the clock, both bits must be programmed to '0.'

## 6 Microprocessor Interface

## 6.1 Microprocessor Interface Configuration

The microprocessor interface may be configured for either *Intel* or *Motorola* mode via the mot\_sel input. Tie mot\_sel high to select *Motorola* mode and low to select *Intel* mode. In addition, the address and data buses may be configured for multiplexed or nonmultiplexed mode using the mux input. To select multiplexed mode, tie mux high, and to select nonmultiplexed mode, tie mux low. In multiplexed mode, d[7:0] are used for both the address and the data bus, and the a[0] input becomes an address latch enable (ale) signal. In nonmultiplexed mode, separate address, a[7:0], and data, d[7:0], buses are used. In both modes, the active-low sel\* input selects the device for microprocessor read or write accesses. The data leads are 3-stated when the sel\*, wr\*\_ds\*, or rd\*\_wr\* signal is high.

In *Motorola* mode, rd\*\_rw\* is a read/write enable signal, which indicates the current access is a read when it is high and a write when low. The wr\*\_ds\* signal is data strobe in *Motorola* mode. The rdy\_dtack\* output is an active-low data transfer acknowledge signal. The T8207 takes this signal low when the microprocessor access is complete. The rdy\_dtack\* output returns high when the microprocessor acknowledges the access by taking the sel\* or wr\*\_ds\* signal high. The rdy\_dtack\* output then goes high-impedance.