# **PM5380**

# S/UNI®-8x155

# **SATURN® User Network Interface** (8x155) Telecom Standard Product

# **Data Sheet**

Released

Issue No. 2: June 2002

## **Legal Information**

## Copyright

Copyright 2002 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2010299(R2)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

SATURN and S/UNI are registered trademarks of PMC-Sierra, Inc. PMC-Sierra and POS-PHY Level 3<sup>TM</sup> are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

#### **Patents**

#### **Granted**

The technology discussed in this document is protected by one or more of the following patent grants:

U.S. Patent No. 5,835,602, 6,052,073, 6,150,965, 6,188,692 and 6,246,738. Canadian Patent No. 2,254,225, 2,194,919 and 2,149,076. United Kingdom Patent No. 2,290,438. Other relevant patent grants may also exist.

## **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

Document Information: <a href="mailto:document@pmc-sierra.com">document@pmc-sierra.com</a>

Corporate Information: <a href="mailto:info@pmc-sierra.com">info@pmc-sierra.com</a>

Technical Support: <a href="mailto:apps@pmc-sierra.com">apps@pmc-sierra.com</a>

Web Site: <a href="mailto:http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

## **Revision History**

| Issue No. | Issue Date | Details of Change                                                 |

|-----------|------------|-------------------------------------------------------------------|

| 1         | April 2002 | Document Issued                                                   |

| 2         | June 2002  | Added new ordering information table.                             |

|           |            | Updated Clock Source Configuration Register (0x1000) Description. |

## **Table of Contents**

| Le  | gal Info | rmation                                                                | 2  |

|-----|----------|------------------------------------------------------------------------|----|

|     | Соруг    | ight                                                                   | 2  |

|     | Discla   | imer                                                                   | 2  |

|     | Trade    | marks                                                                  | 2  |

|     | Paten    | ts 2                                                                   |    |

| Со  | ntactin  | ts 2 g PMC-SierraHistory                                               | 3  |

| Re  | vision I | -<br>History                                                           | 4  |

| Tal | ole of C | Contents                                                               | 5  |

| Lis | t of Re  | gisters                                                                | 9  |

| Lis | t of Fig | ures                                                                   | 20 |

| Lis | t of Tab | oles                                                                   | 22 |

| 1   | Defini   | tions                                                                  | 24 |

| 2   | Featu    | res                                                                    | 27 |

|     | 2.1      | General                                                                | 27 |

|     | 2.2      | The SONET Receiver                                                     | 27 |

|     | 2.3      | The Receive ATM Processor                                              | 28 |

|     | 2.4      | The Receive POS Processor                                              | 28 |

|     | 2.5      | The SONET Transmitter                                                  | 29 |

|     | 2.6      | The Transmit ATM Processor                                             | 29 |

|     | 2.7      | The Transmit POS Processor                                             | 29 |

|     | 2.8      | The APS/Crossbar Support                                               | 30 |

|     | 2.9      | Device Interworking                                                    | 30 |

| 3   | Applic   | cations                                                                | 31 |

| 4   | Refer    | ences                                                                  | 32 |

| 5   | Applic   | cation Examples                                                        | 33 |

| 6   | Block    | Diagram                                                                | 36 |

| 7   | Descr    | iption                                                                 | 37 |

| 8   | Pin D    | iagram                                                                 | 39 |

| 9   | Pin D    | escription                                                             | 43 |

|     | 9.1      | Serial Line Side Interface Signals                                     | 43 |

|     | 9.2      | Serial APS Interface Signals                                           | 44 |

|     | 9.3      | Clocks and Alarms Signals                                              | 45 |

|     | 9.4      | Section and Line Status DCC Signals                                    | 46 |

|     | 9.5      | Transmit ATM (UTOPIA) and Packet over SONET/SDH (POS) System Interface | 47 |

|    | 9.6      | Receive ATM (UTOPIA) and Packet over SONET/SDH (POS) System Interface   | 52   |

|----|----------|-------------------------------------------------------------------------|------|

|    | 9.7      | Microprocessor Interface Signals                                        | 56   |

|    | 9.8      | JTAG Test Access Port (TAP) Signals                                     | 57   |

|    | 9.9      | Analog Signals                                                          | 58   |

|    | 9.10     | Power and Ground                                                        |      |

|    | 9.11     | No Connects                                                             | 63   |

| 10 | Function | onal Description                                                        | 66   |

|    | 10.1     | Receive Line Interface (CRSI)                                           | 66   |

|    | 10.2     | Receive Section Overhead Processor (RSOP)                               | 67   |

|    | 10.3     | Receive Line Overhead Processor (RLOP)                                  | 69   |

|    | 10.4     | The Receive APS, Synchronization Extractor and Bit Error Monitor (RASE) | 71   |

|    | 10.5     | Receive Path Overhead Processor (RPOP)                                  | 71   |

|    | 10.6     | Receive ATM Cell Processor (RXCP)                                       | 75   |

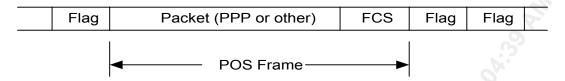

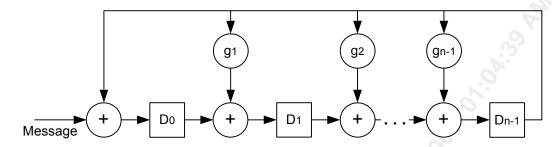

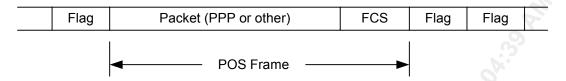

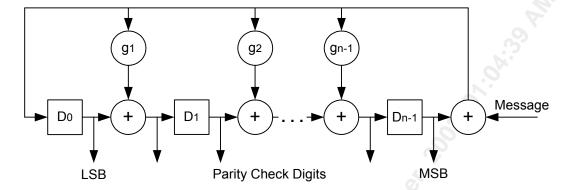

|    | 10.7     | Receive POS Frame Processor (RXFP)                                      | 77   |

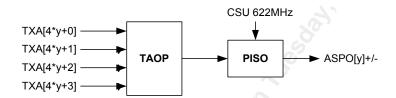

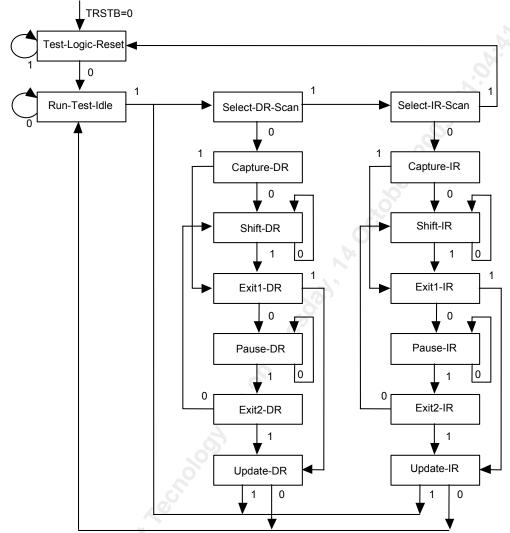

|    | 10.8     | Transmit Line Interface (CSPI)                                          | 79   |

|    | 10.9     | Transmit Section Overhead Processor (TSOP)                              | 80   |

|    | 10.10    | Transmit Line Overhead Processor (TLOP)                                 | 81   |

|    | 10.11    | Transmit Path Overhead Processor (TPOP)                                 | 82   |

|    | 10.12    | Transmit ATM Cell Processor (TXCP)                                      | 83   |

|    | 10.13    | Transmit POS Frame Processor (TXFP)                                     | 83   |

|    | 10.14    | SONET/SDH Path Trace Buffer (SPTB)                                      | 86   |

|    | 10.15    | SONET/SDH Section Trace Buffer (SSTB)                                   | 88   |

|    | 10.16    | WAN Synchronization Controller (WANS)                                   | 89   |

|    | 10.17    | ATM UTOPIA and Packet over SONET/SDH POS-PHY System Interfaces          | 91   |

|    | 10.18    | Transmit APS Interface                                                  | 93   |

|    | 10.19    | Transmit APS Overhead Processor                                         | 93   |

|    | 10.20    | SONET/SDH Path Aligner                                                  | 94   |

|    | 10.21    | Receive APS Interface                                                   | 94   |

|    | 10.22    | Receive APS Overhead Processor                                          | 95   |

|    | 10.23    | Channel Cross Connect                                                   | 97   |

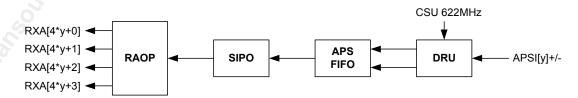

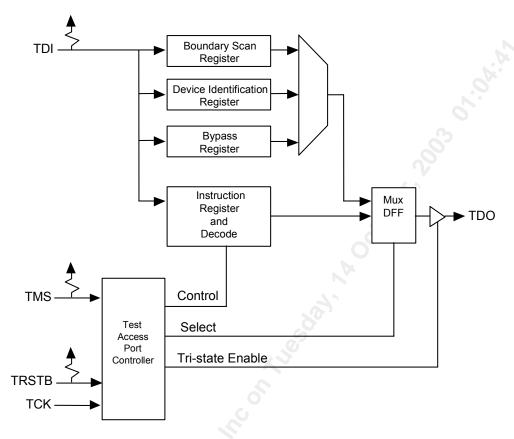

|    | 10.24    | JTAG Test Access Port                                                   | 97   |

|    | 10.25    | Microprocessor Interface                                                | 97   |

| 11 | Norma    | Il Mode Register Descriptions                                           | 98   |

|    | 11.1     | Register Memory Map                                                     | 98   |

|    | 11.2     | Registers                                                               | .111 |

| 12 | Test F   | eatures Description                                                     | 368  |

|    | 12.1     | Master Test and Test Configuration Registers                  | 368 |

|----|----------|---------------------------------------------------------------|-----|

|    | 12.2     | JTAG Test Port                                                | 371 |

| 13 | Opera    | tion                                                          | 380 |

|    | 13.1     | SONET/SDH Frame Mappings and Overhead Byte Usage              | 380 |

|    | 13.2     | UTOPIA Level 3 ATM Cell Data Structure                        | 384 |

|    | 13.3     | POS-PHY Level 3 Data Structures                               | 385 |

|    | 13.4     | Setting ATM Mode of Operation                                 | 387 |

|    | 13.5     | Setting Packet-Over-SONET/SDH Mode of Operation               | 388 |

|    | 13.6     | Setting SONET or SDH Mode of Operation                        | 388 |

|    | 13.7     | Bit Error Rate Monitor                                        | 389 |

|    | 13.8     | Auto Alarm Control Configuration                              |     |

|    | 13.9     | Clocking Options                                              | 391 |

|    | 13.10    | WAN Synchronization (WANS Block)                              | 392 |

|    | 13.11    |                                                               |     |

|    |          | APS Support                                                   |     |

|    | 13.13    | JTAG Support                                                  | 399 |

|    | 13.14    | Board Design Recommendations                                  | 403 |

|    | 13.15    | Power Supplies                                                | 404 |

|    | 13.16    | High Speed PECL Interfaces                                    | 406 |

|    | 13.17    | Clock Synthesis and Recovery                                  | 409 |

|    | 13.18    | System Interface DLL Operation                                | 410 |

| 14 | Function | onal Timing                                                   | 411 |

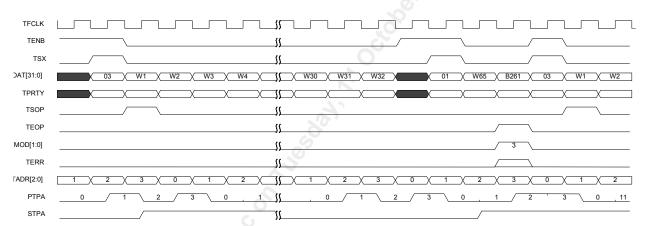

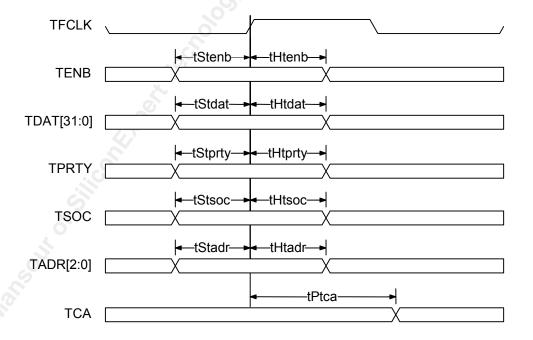

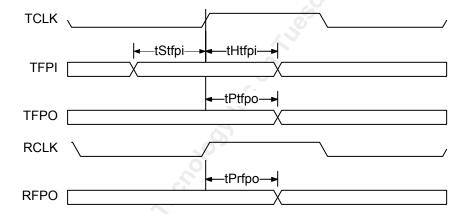

|    | 14.1     | Transmit ATM UTOPIA Level 3 System Interface                  | 411 |

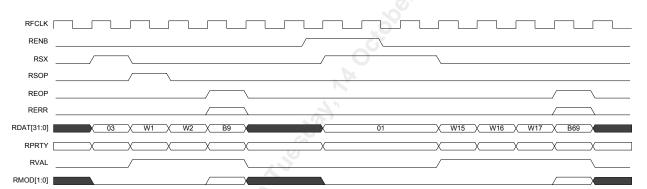

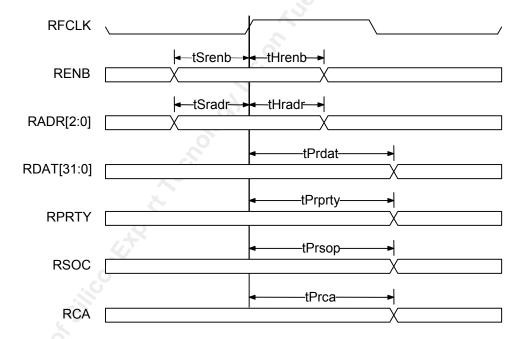

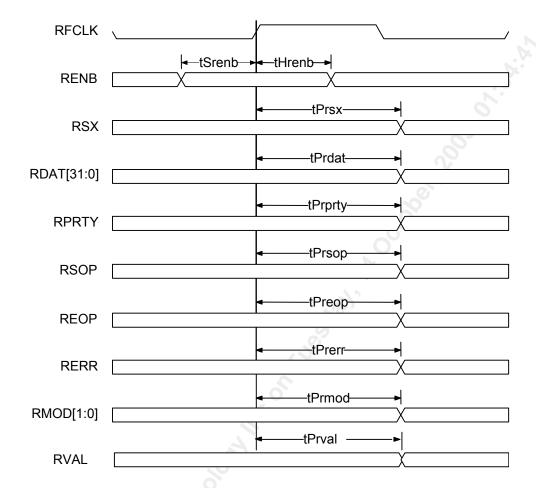

|    | 14.2     | Receive ATM UTOPIA Level 3 System Interface                   | 412 |

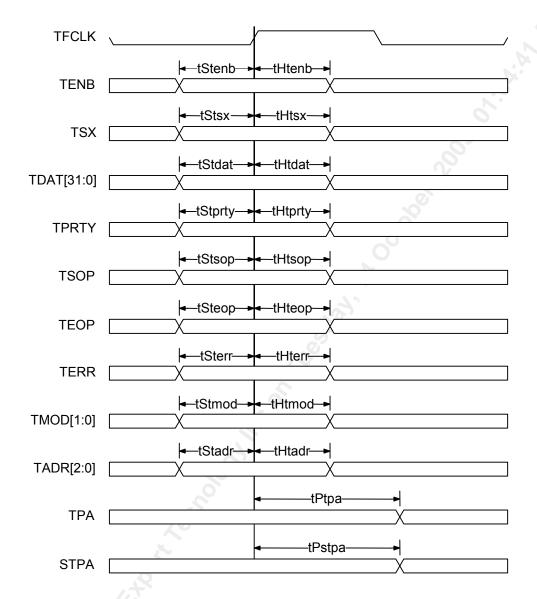

|    | 14.3     | Transmit Packet over SONET/SDH (POS) Level 3 System Interface | 412 |

|    | 14.4     | Receive Packet over SONET/SDH (POS) Level 3 System Interface  | 413 |

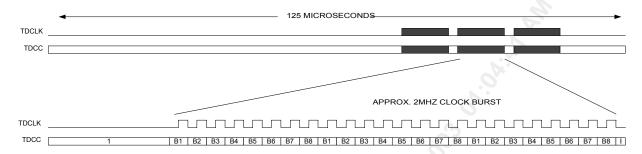

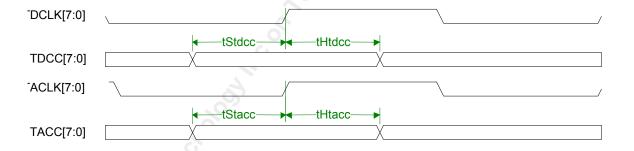

|    | 14.5     | Transmit Data Communication Channels                          | 414 |

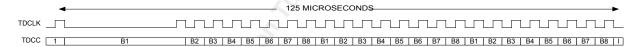

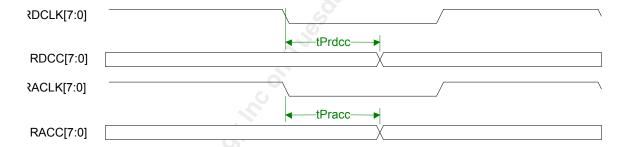

|    | 14.6     | Receive Data Communication Channels                           | 415 |

| 15 | Absolu   | ute Maximum Ratings                                           | 417 |

| 16 | D.C. C   | characterstics                                                | 418 |

| 17 | Power    | Information                                                   | 420 |

| 18 | Microp   | processor Interface Timing Characteristics                    | 421 |

| 19 | A.C. T   | iming Characteristics                                         | 424 |

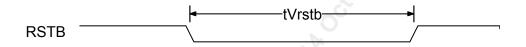

|    | 19.1     | System Reset Timing                                           | 424 |

|    | 19.2     | OC-3 Interface Timing Characteristics                         | 424 |

|    | 19.3     | UTOPIA Level 3 System Interface Timing                        | 425 |

|    | 19.4  | POS Level 3 System Interface Timing    | 427 |

|----|-------|----------------------------------------|-----|

|    |       | Transmit DCC Interface Timing          |     |

|    | 19.6  | Receive DCC Interface Timing           | 432 |

|    |       | Clock and Frame Pulse Interface Timing |     |

|    | 19.8  | APS Interface Timing Characteristics   | 434 |

|    | 19.9  | JTAG Test Port Timing                  | 436 |

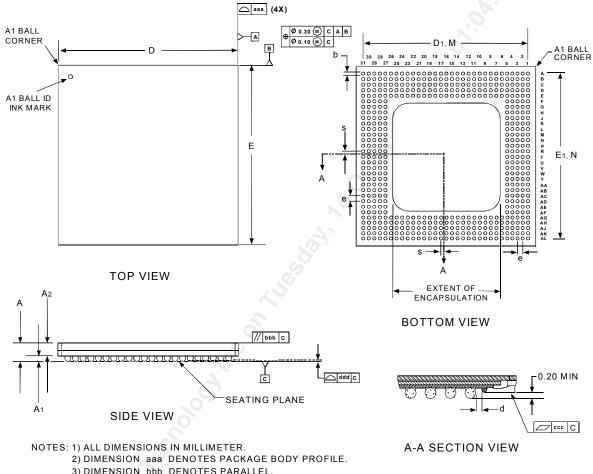

| 20 |       | ing And Thermal Information            |     |

| 21 | Mecha | anical Information                     | 439 |

| No | tes   | 440                                    |     |

# **List of Registers**

| Register 0x000: S/UNI-8x155 Master Reset and Identity                                                         | 111 |

|---------------------------------------------------------------------------------------------------------------|-----|

| Register 0x001: S/UNI-8x155 Master Configuration                                                              | 112 |

| Register 0x003: S/UNI-8x155 Clock Monitors                                                                    | 113 |

| Register 0x100: S/UNI-8x155 Master Interrupt Status #1                                                        | 115 |

| Register 0x101: S/UNI-8x155 Master Interrupt Status #2                                                        | 117 |

| Register 0x004, 0x104, 0x204, 0x304, 0x404, 0x504, 0x604, 0x704: Channel Master Configuration #1              | 118 |

| Register 0x005, 0x105, 0x205, 0x305, 0x405, 0x505, 0x605, 0x705: Channel Master Configuration #2              | 120 |

| Register 0x006, 0x106, 0x206, 0x306, 0x406, 0x506, 0x606, 0x706: Channel Reset/Master Interrupt Status #1     | 122 |

| Register 0x007, 0x107, 0x207, 0x307, 0x407, 0x507, 0x607, 0x707: Channel Master Interrupt Status #2           | 124 |

| Register 0x008, 0x108, 0x208, 0x308, 0x408, 0x508, 0x608, 0x708: Channel Auto Line RDI Control                | 126 |

| Register 0x009, 0x109, 0x209, 0x309, 0x409, 0x509, 0x609, 0x709: Channel Auto Path RDI Control                | 128 |

| Register 0x00A, 0x10A, 0x20A, 0x30A, 0x40A, 0x50A, 0x60A, 0x70A: Channel Auto Enhanced Path RDI Control       | 130 |

| Register 0x00B, 0x10B, 0x20B, 0x30B, 0x40B, 0x50B, 0x60B, 0x70B: Channel Receive RDI and Enhanced RDI Control | 133 |

| Register 0x00C, 0x10C, 0x20C, 0x30C, 0x40C, 0x50C, 0x60C, 0x70C: Channel Received Line AIS Control            | 135 |

| Register 0x00D, 0x10D, 0x20D, 0x30D, 0x40D, 0x50D, 0x60D, 0x70D: Channel Receive Path AIS Control             | 137 |

| Register 0x00E, 0x10E, 0x20E, 0x30E, 0x40E, 0x50E, 0x60E, 0x70E: Channel Receive Alarm Control #1             | 139 |

| Register 0x00F, 0x10F, 0x20F, 0x30F, 0x40F, 0x50F, 0x60F, 0x70F: Channel Receive Alarm Control #2             | 139 |

| Register 0x010, 0x110, 0x210, 0x310, 0x410, 0x510, 0x610, 0x710: RSOP Control/Interrupt Enable                | 141 |

| Register 0x011, 0x111, 0x211, 0x311, 0x411, 0x511, 0x611, 0x711: RSOP Status/Interrupt Status                 | 143 |

| Register 0x012, 0x112, 0x212, 0x312, 0x412, 0x512, 0x612, 0x712: RSOP Section BIP-8 LSB                       | 145 |

| Register 0x013, 0x113, 0x213, 0x313, 0x413, 0x513, 0x613, 0x713: RSOP Section BIP-8 MSB                       | 145 |

| Register 0x014, 0x114, 0x214, 0x314, 0x414, 0x514, 0x614, 0x714: TSOP Control                                 |     |

| Register 0x015, 0x115, 0x215, 0x315, 0x415, 0x515, 0x615, 0x715: TSOP  Diagnostic                        | . 147 |

|----------------------------------------------------------------------------------------------------------|-------|

| Register 0x018, 0x118, 0x218, 0x318, 0x418, 0x518, 0x618, 0x718: RLOP  Control/Status                    | . 148 |

| Register 0x019, 0x119, 0x219, 0x319, 0x419, 0x519, 0x619, 0x719: RLOP Interrupt Enable/Interrupt Status  | . 150 |

| Register 0x01A, 0x11A, 0x21A, 0x31A, 0x41A, 0x51A, 0x61A, 0x71A: RLOP<br>Line BIP-24 LSB                 | . 152 |

| Register 0x01B, 0x11B, 0x21B, 0x31B, 0x41B, 0x51B, 0x61B, 0x71B: RLOP<br>Line BIP-24                     | . 152 |

| Register 0x01C, 0x11C, 0x21C, 0x31C , 0x41C , 0x51C , 0x61C , 0x71C: RLOP Line BIP-24 MSB                | . 153 |

| Register 0x01D, 0x11D, 0x21D, 0x31D, 0x41D, 0x51D, 0x61D, 0x71D: RLOP<br>Line FEBE LSB                   | . 154 |

| Register 0x01E, 0x11E, 0x21E, 0x31E, 0x41E, 0x51E, 0x61E, 0x71E: RLOP Line FEBE                          | . 154 |

| Register 0x01F, 0x11F, 0x21F, 0x31F, 0x41F, 0x51F, 0x61F, 0x71F: RLOP<br>Line FEBE MSB                   | . 155 |

| Register 0x020, 0x120, 0x220, 0x320, 0x420, 0x520, 0x620, 0x720: TLOP Control                            | . 156 |

| Register 0x021, 0x121, 0x221, 0x321, 0x421, 0x521, 0x621, 0x721: TLOP  Diagnostic                        | . 157 |

| Register 0x022, 0x122, 0x222, 0x322, 0x422, 0x522, 0x622, 0x722: TLOP Transmit K1                        | . 158 |

| Register 0x023, 0x123, 0x223, 0x323, 0x423, 0x523, 0x623, 0x723: TLOP Transmit K2                        | . 159 |

| Register 0x024, 0x124, 0x224, 0x324, 0x424, 0x524, 0x624, 0x724: S/UNI-8x155 Transmit Sync. Message (S1) | . 160 |

| Register 0x025, 0x125, 0x225, 0x325, 0x425, 0x525, 0x625, 0x725: S/UNI-8x155 Transmit J0/Z0              | . 161 |

| Register 0x028, 0x128, 0x228, 0x328, 0x428, 0x528, 0x628, 0x728: SSTB Control                            | . 162 |

| Register 0x029, 0x129, 0x229, 0x329, 0x429, 0x529, 0x629, 0x729: SSTB Section Trace Identifier Status    | . 164 |

| Register 0x02A, 0x12A, 0x22A, 0x32A, 0x42A, 0x52A, 0x62A, 0x72A: SSTB Indirect Address Register          | . 166 |

| Register 0x02B, 0x12B, 0x22B, 0x32B, 0x42B, 0x52B, 0x62B, 0x72B: SSTB Indirect Data Register             | . 167 |

| Register 0x02E, 0x12E, 0x22E, 0x32E, 0x42E, 0x52E, 0x62E, 0x72E: SSTB Indirect Access Trigger Register   | . 168 |

| Register 0x030, 0x130, 0x230, 0x330, 0x430, 0x530, 0x630, 0x730 (EXTD=0):  RPOP Status/Control           | . 169 |

| Register 0x030, 0x130, 0x230, 0x330, 0x430, 0x530, 0x630, 0x730 (EXTD=1):  RPOP Status/Control   | . 171 |

|--------------------------------------------------------------------------------------------------|-------|

| Register 0x031, 0x131, 0x231, 0x331, 0x431, 0x531, 0x631, 0x731 (EXTD=0):  RPOP Interrupt Status | . 172 |

| Register 0x031, 0x131, 0x231, 0x331, 0x431, 0x531, 0x631, 0x731 (EXTD=1):  RPOP Interrupt Status | . 174 |

| Register 0x032, 0x132, 0x232, 0x332, 0x432, 0x532, 0x632, 0x732: RPOP  Pointer Interrupt Status  | . 175 |

| Register 0x033, 0x133, 0x233, 0x333, 0x433, 0x533, 0x633, 0x733 (EXTD=0):  RPOP Interrupt Enable | . 177 |

| Register 0x033, 0x133, 0x233, 0x333, 0x433, 0x533, 0x633, 0x733 (EXTD=1):  RPOP Interrupt Enable | . 179 |

| Register 0x034, 0x134, 0x234, 0x334, 0x434, 0x534, 0x634, 0x734: RPOP Pointer Interrupt Enable   | . 180 |

| Register 0x035, 0x135, 0x235, 0x335, 0x435, 0x535, 0x635, 0x735: RPOP Pointer LSB                | . 182 |

| Register 0x036, 0x136, 0x236, 0x336, 0x436, 0x536, 0x636, 0x736: RPOP Pointer MSB                | . 182 |

| Register 0x037, 0x137, 0x237, 0x337, 0x437, 0x537, 0x637, 0x737: RPOP Path Signal Label          | . 184 |

| Register 0x038, 0x138, 0x238, 0x338, 0x438, 0x538, 0x638, 0x738: RPOP Path BIP-8 LSB             | . 185 |

| Register 0x039, 0x139, 0x239, 0x339, 0x439, 0x539, 0x639, 0x739: RPOP Path BIP-8 MSB             | . 185 |

| Register 0x03A, 0x13A, 0x23A, 0x33A, 0x43A, 0x53A, 0x63A, 0x73A: RPOP Path FEBE LSB              | . 186 |

| Register 0x03B, 0x13B, 0x23B, 0x33B, 0x43B, 0x53B, 0x63B, 0x73B: RPOP Path FEBE MSB              | . 186 |

| Register 0x03C, 0x13C, 0x23C, 0x33C, 0x43C, 0x53C, 0x63C, 0x73C: RPOP RDI                        | . 187 |

| Register 0x03D, 0x13D, 0x23D, 0x33D, 0x43D, 0x53D, 0x63D, 0x73D: RPOP Ring Control               | . 188 |

| Register 0x040, 0x140, 0x240, 0x340, 0x440, 0x540, 0x640, 0x740: TPOP Control/Diagnostic         | . 190 |

| Register 0x041, 0x141, 0x241, 0x341, 0x441, 0x541, 0x641, 0x741: TPOP Pointer Control            | . 192 |

| Register 0x043, 0x143, 0x243, 0x343, 0x443, 0x543, 0x643, 0x743: TPOP Current Pointer LSB        | . 194 |

| Register 0x044, 0x144, 0x244, 0x344, 0x444, 0x544, 0x644, 0x744: TPOP  Current Pointer MSB       | . 194 |

| Register 0x045, 0x145, 0x245, 0x345, 0x445, 0x545, 0x645, 0x745: TPOP Arbitrary Pointer LSB      | . 195 |

| Register 0x046, 0x146, 0x246, 0x346, 0x446, 0x546, 0x646, 0x746: TPOP  Arbitrary Pointer MSB                | . 196 |

|-------------------------------------------------------------------------------------------------------------|-------|

| Register 0x047, 0x147, 0x247, 0x347, 0x447, 0x547, 0x647, 0x747: TPOP Path Trace                            | . 197 |

| Register 0x048, 0x148, 0x248, 0x348, 0x448, 0x548, 0x648, 0x748: TPOP Path Signal Label                     | . 198 |

| Register 0x049, 0x149, 0x249, 0x349, 0x449, 0x549, 0x649, 0x749: TPOP Path Status                           | . 199 |

| Register 0x04E, 0x14E, 0x24E, 0x34E, 0x44E, 0x54E, 0x64E, 0x74E: TPOP  Concatenation LSB                    | . 201 |

| Register 0x04F, 0x14F, 0x24F, 0x34F, 0x44F, 0x54F, 0x64F, 0x74F: TPOP  Concatenation MSB                    | . 201 |

| Register 0x050, 0x150, 0x250, 0x350, 0x450, 0x550, 0x650, 0x750: SPTB Control                               | . 202 |

| Register 0x051, 0x151, 0x251, 0x351, 0x451, 0x551, 0x651, 0x751: SPTB Path Trace Identifier Status          | . 204 |

| Register 0x052, 0x152, 0x252, 0x352, 0x452, 0x552, 0x652, 0x752: SPTB Indirect Address Register             | . 206 |

| Register 0x053, 0x153, 0x253, 0x353, 0x453, 0x553, 0x653, 0x753: SPTB Indirect Data Register                | . 207 |

| Register 0x054, 0x154, 0x254, 0x354, 0x454, 0x554, 0x654, 0x754: SPTB<br>Expected Path Signal Label         | . 208 |

| Register 0x055, 0x155, 0x255, 0x355, 0x455, 0x555, 0x655, 0x755: SPTB Path Signal Label Status              | . 210 |

| Register 0x056, 0x156, 0x256, 0x356, 0x456, 0x556, 0x656, 0x756: SPTB Indirect Access Trigger Register      | . 212 |

| Register 0x058, 0x158, 0x258, 0x358, 0x458, 0x558, 0x658, 0x758: DCRU  Configuration                        | . 213 |

| Register 0x05A, 0x15A, 0x25A, 0x35A, 0x45A, 0x55A, 0x65A, 0x75A: DCRU<br>RESET                              | . 214 |

| Register 0x05C, 0x15C, 0x25C, 0x35C, 0x45C, 0x55C, 0x65C, 0x75C: CRSI Configuration                         | . 215 |

| Register 0x05D, 0x15D, 0x25D, 0x35D, 0x45D, 0x55D, 0x65D, 0x75D: CRSI Status                                | . 217 |

| Register 0x060, 0x160, 0x260, 0x360, 0x460, 0x560, 0x660, 0x760: RXCP Configuration 1                       | . 219 |

| Register 0x061, 0x161, 0x261, 0x361, 0x461, 0x561, 0x661, 0x761: RXCP Configuration 2                       | . 220 |

| Register 0x062, 0x162, 0x262, 0x362, 0x462, 0x562, 0x662, 0x762: RXCP FIFO/UTOPIA Control and Configuration | . 221 |

| Register 0x063, 0x163, 0x263, 0x363, 0x463, 0x563, 0x663, 0x763: RXCP Interrupt Enable and Counter Status   | . 222 |

| Register 0x064, 0x164, 0x264, 0x364, 0x464, 0x564, 0x664, 0x764: RXCP  Status/Interrupt Status  | 224 |

|-------------------------------------------------------------------------------------------------|-----|

| Register 0x065, 0x165, 0x265, 0x365, 0x465, 0x565, 0x665, 0x765: RXCP LCD Count Threshold MSB   | 226 |

| Register 0x066, 0x166, 0x266, 0x366, 0x466, 0x566, 0x666, 0x766: RXCP LCD Count Threshold LSB   | 226 |

| Register 0x067, 0x167, 0x267, 0x367, 0x467, 0x567, 0x667, 0x767: RXCP Idle Cell Header Pattern  | 227 |

| Register 0x068, 0x168, 0x268, 0x368, 0x468, 0x568, 0x668, 0x768: RXCP Idle Cell Header Mask     | 228 |

| Register 0x06A, 0x16A, 0x26A, 0x36A, 0x46A, 0x56A, 0x66A, 0x76A: RXCP<br>HCS Error Count        | 229 |

| Register 0x06B, 0x16B, 0x26B, 0x36B, 0x46B, 0x56B, 0x66B, 0x76B: RXCP Receive Cell Counter LSB  | 230 |

| Register 0x06C, 0x16C, 0x26C, 0x36C, 0x46C, 0x56C, 0x66C, 0x76C: RXCP Receive Cell Counter      | 230 |

| Register 0x06D, 0x16D, 0x26D, 0x36D, 0x46D, 0x56D, 0x66D, 0x76D: RXCP Receive Cell Counter MSB  | 231 |

| Register 0x06E, 0x16E, 0x26E, 0x36E, 0x46E, 0x56E, 0x66E, 0x76E: RXCP Idle Cell Counter LSB     | 232 |

| Register 0x06F, 0x16F, 0x26F, 0x36F, 0x46F, 0x56F, 0x66F, 0x76F: RXCP Idle Cell Counter         | 232 |

| Register 0x070, 0x170, 0x270, 0x370, 0x470, 0x570, 0x670, 0x770: RXCP Idle Cell Counter MSB     | 233 |

| Register 0x080, 0x180, 0x280, 0x380, 0x480, 0x580, 0x680, 0x780: TXCP  Configuration 1          | 234 |

| Register 0x081, 0x181, 0x281, 0x381, 0x481, 0x581, 0x681, 0x781: TXCP  Configuration 2          | 236 |

| Register 0x082, 0x182, 0x282, 0x382, 0x482, 0x582, 0x682, 0x782: TXCP Cell Count Status         | 237 |

| Register 0x083, 0x183, 0x283, 0x383, 0x483, 0x583, 0x683, 0x783: TXCP Interrupt Enable/Status   | 238 |

| Register 0x084, 0x184, 0x284, 0x384, 0x484, 0x584, 0x684, 0x784: TXCP Idle Cell Header Control  | 239 |

| Register 0x085, 0x185, 0x285, 0x385, 0x485, 0x585, 0x685, 0x785: TXCP Idle Cell Payload Control | 240 |

| Register 0x086, 0x186, 0x286, 0x386, 0x486, 0x586, 0x686, 0x786: TXCP Transmit Cell Count LSB   | 241 |

| Register 0x087, 0x187, 0x287, 0x387, 0x487, 0x587, 0x687, 0x787: TXCP  Transmit Cell Count      | 241 |

| Register 0x088, 0x188, 0x288, 0x388, 0x488, 0x588, 0x688, 0x788: TXCP Transmit Cell Count MSB   | 242 |

| Register 0x094, 0x194, 0x294, 0x394, 0x494, 0x594, 0x694, 0x794: Receive Cell/Packet Counter LSB      | 243 |

|-------------------------------------------------------------------------------------------------------|-----|

| Register 0x095, 0x195, 0x295, 0x395, 0x495, 0x595, 0x695, 0x795: Receive Cell/Packet Counter          | 243 |

| Register 0x096, 0x196, 0x296, 0x396, 0x496, 0x596, 0x696, 0x796: Receive Cell/Packet Counter MSB      | 244 |

| Register 0x098, 0x198, 0x298, 0x398, 0x498, 0x598, 0x698, 0x798: JAT  Configuration #1                | 245 |

| Register 0x099, 0x199, 0x299, 0x399, 0x499, 0x599, 0x699, 0x799: JAT Configuration #2                 | 246 |

| Register 0x09A, 0x19A, 0x29A, 0x39A, 0x49A, 0x59A, 0x69A, 0x79A: JAT Reset                            | 247 |

| Register 0x0A0, 0x1A0, 0x2A0, 0x3A0, 0x4A0, 0x5A0, 0x6A0, 0x7A0: RXFP Configuration                   | 248 |

| Register 0x0A1, 0x1A1, 0x2A1, 0x3A1, 0x4A1, 0x5A1, 0x6A1, 0x7A1: RXFP Configuration/Interrupt Enable  | 250 |

| Register 0x0A2, 0x1A2, 0x2A2, 0x3A2, 0x4A2, 0x5A2, 0x6A2, 0x7A2: RXFP Interrupt Status                | 251 |

| Register 0x0A3, 0x1A3, 0x2A3, 0x3A3, 0x4A3, 0x5A3, 0x6A3, 0x7A3: RXFP Minimum Packet Length           | 252 |

| Register 0x0A4, 0x1A4, 0x2A4, 0x3A4, 0x4A4, 0x5A4, 0x6A4, 0x7A4: RXFP  Maximum Packet Length LSB      | 253 |

| Register 0x0A5, 0x1A5, 0x2A5, 0x3A5, 0x4A5, 0x5A5, 0x6A5, 0x7A5: RXFP  Maximum Packet Length MSB      | 253 |

| Register 0x0A6 , 0x1A6, 0x2A6, 0x3A6, 0x4A6, 0x5A6, 0x6A6, 0x7A6: RXFP Receive Initiation Level       | 254 |

| Register 0x0A8, 0x1A8, 0x2A8, 0x3A8, 0x4A8, 0x5A8, 0x6A8, 0x7A8: RXFP Receive Byte Count LSB          | 255 |

| Register 0x0A9, 0x1A9, 0x2A9, 0x3A9, 0x4A9, 0x5A9, 0x6A9, 0x7A9: RXFP Receive Byte Count              | 255 |

| Register 0x0AA, 0x1AA, 0x2AA, 0x3AA, 0x4AA, 0x5AA, 0x6AA, 0x7AA: RXFP Receive Byte Count              | 256 |

| Register 0x0AB, 0x1AB, 0x2AB, 0x3AB, 0x4AB, 0x5AB, 0x6AB, 0x7AB: RXFP Receive Byte Count MSB          | 256 |

| Register 0x0AC, 0x1AC, 0x2AC, 0x3AC, 0x4AC, 0x5AC, 0x6AC, 0x7AC: RXFP Receive Frame Count LSB         | 257 |

| Register 0x0AD, 0x1AD, 0x2AD, 0x3AD, 0x4AD, 0x5AD, 0x6AD, 0x7AD: RXFP Receive Frame Count             | 257 |

| Register 0x0AE, 0x1AE, 0x2AE, 0x3AE, 0x4AE, 0x5AE, 0x6AE, 0x7AE: RXFP Receive Frame Count MSB         | 258 |

| Register 0x0AF, 0x1AF, 0x2AF, 0x3AF, 0x4AF, 0x5AF, 0x6AF, 0x7AF: RXFP Receive Aborted Frame Count LSB |     |

| Register 0x0B0, 0x1B0, 0x2B0, 0x3B0, 0x4B0, 0x5B0, 0x6B0, 0x7B0: RXFP  Receive Aborted Frame Count MSB                | 259 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Register 0x0B1, 0x1B1, 0x2B1, 0x3B1, 0x4B1, 0x5B1, 0x6B1, 0x7B1: RXFP Receive FCS Error Frame Count LSB               | 260 |

| Register 0x0B2, 0x1B2, 0x2B2, 0x3B2, 0x4B2, 0x5B2, 0x6B2, 0x7B2: RXFP Receive FCS Error Frame Count MSB               | 260 |

| Register 0x0B3, 0x1B3, 0x2B3, 0x3B3, 0x4B3, 0x5B3, 0x6B3, 0x7B3: RXFP Receive Minimum Length Error Frame Count LSB    | 261 |

| Register 0x0B4, 0x1B4, 0x2B4, 0x3B4, 0x4B4, 0x5B4, 0x6B4, 0x7B4: RXFP Receive Minimum Length Error Frame Counter MSB  | 261 |

| Register 0x0B5, 0x1B5, 0x2B5, 0x3B5, 0x4B5, 0x5B5, 0x6B5, 0x7B5: RXFP Receive Maximum Length Error Frame Counter LSB  | 262 |

| Register 0x0B6, 0x1B6, 0x2B6, 0x3B6, 0x4B6, 0x5B6, 0x6B6, 0x7B6: RXFP Receive Maximum Length Error Frame Counter MSB  | 262 |

| Register 0x0C0, 0x1C0, 0x2C0, 0x3C0, 0x4C0, 0x5C0, 0x6C0, 0x7C0: TXFP Interrupt Enable/Status                         | 263 |

| Register 0x0C1, 0x1C1, 0x2C1, 0x3C1, 0x4C1, 0x5C1, 0x6C1, 0x7C1: TXFP Configuration                                   | 264 |

| Register 0x0C2, 0x1C2, 0x2C2, 0x3C2, 0x4C2, 0x5C2, 0x6C2, 0x7C2: TXFP Control                                         | 266 |

| Register 0x0C5, 0x1C5, 0x2C5, 0x3C5, 0x4C5, 0x5C5, 0x6C5, 0x7C5: TXFP Transmit Byte Count LSB                         | 268 |

| Register 0x0C6, 0x1C6, 0x2C6, 0x3C6, 0x4C6, 0x5C6, 0x6C6, 0x7C6: TXFP  Transmit Byte Count                            | 268 |

| Register 0x0C7, 0x1C7, 0x2C7, 0x3C7, 0x4C7, 0x5C7, 0x6C7, 0x7C7: TXFP Transmit Byte Count                             | 269 |

| Register 0x0C8, 0x1C8, 0x2C8, 0x3C8, 0x4C8, 0x5C8, 0x6C8, 0x7C8: TXFP Transmit Byte Count MSB                         | 269 |

| Register 0x0C9, 0x1C9, 0x2C9, 0x3C9, 0x4C9, 0x5C9, 0x6C9, 0x7C9: TXFP Transmit Frame Count LSB                        | 270 |

| Register 0x0CA, 0x1CA, 0x2CA, 0x3CA, 0x4CA, 0x5CA, 0x6CA, 0x7CA: TXFP Transmit Frame Count                            | 270 |

| Register 0x0CB, 0x1CB, 0x2CB, 0x3CB, 0x4CB, 0x5CB, 0x6CB, 0x7CB: TXFP Transmit Frame Count MSB                        | 271 |

| Register 0x0CC, 0x1CC, 0x2CC, 0x3CC, 0x4CC, 0x5CC, 0x6CC, 0x7CC:  TXFP Transmit User Aborted Frame Count LSB          | 272 |

| Register 0x0CD, 0x1CD, 0x2CD, 0x3CD, 0x4CD, 0x5CD, 0x6CD, 0x7CD: TXFP Transmit User Aborted Frame Count MSB           | 272 |

| Register 0x0CE, 0x1CE, 0x2CE, 0x3CE, 0x4CE, 0x5CE, 0x6CE, 0x7CE: TXFP Transmit Underrun/Error Aborted Frame Count LSB | 273 |

| Register 0x0CF, 0x1CF, 0x2CF, 0x3CF, 0x4CF, 0x5CF, 0x6CF, 0x7CF: TXFP Transmit Underrun/Error Aborted Frame Count MSB | 273 |

|                                                                                                                       |     |

| Register 0x0D0, 0x1D0, 0x2D0, 0x3D0, 0x4D0, 0x5D0, 0x6D0, 0x7D0: WANS  Configuration              | 274 |

|---------------------------------------------------------------------------------------------------|-----|

| Register 0x0D1, 0x1D1, 0x2D1, 0x3D1, 0x4D1, 0x5D1, 0x6D1, 0x7D1: WANS Interrupt and Status        | 275 |

| Register 0x0D2, 0x1D2, 0x2D2, 0x3D2, 0x4D2, 0x5D2, 0x6D2, 0x7D2: WANS Phase Word LSB              | 276 |

| Register 0x0D3, 0x1D3, 0x2D3, 0x3D3, 0x4D3, 0x5D3, 0x6D3, 0x7D3: WANS Phase Word                  | 276 |

| Register 0x0D4, 0x1D4, 0x2D4, 0x3D4, 0x4D4, 0x5D4, 0x6D4, 0x7D4: WANS Phase Word                  | 277 |

| Register 0x0D5, 0x1D5, 0x2D5, 0x3D5, 0x4D5, 0x5D5, 0x6D5, 0x7D5: WANS Phase Word MSB              | 277 |

| Register 0x0D9, 0x1D9, 0x2D9, 0x3D9, 0x4D9, 0x5D9, 0x6D9, 0x7D9: WANS<br>Reference Period LSB     | 278 |

| Register 0x0DA, 0x1DA, 0x2DA, 0x3DA, 0x4DA, 0x5DA, 0x6DA, 0x7DA: WANS Reference Period MSB        | 278 |

| Register 0x0DB, 0x1DB, 0x2DB, 0x3DB, 0x4DB, 0x5DB, 0x6DB, 0x7DB: WANS Phase Counter Period LSB    | 279 |

| Register 0x0DC, 0x1DC, 0x2DC, 0x3DC, 0x4DC, 0x5DC, 0x6DC, 0x7DC: WANS Phase Counter Period MSB    | 279 |

| Register 0x0DD, 0x1DD, 0x2DD, 0x3DD, 0x4DD, 0x5DD, 0x6DD, 0x7DD: WANS Phase Average Period        | 280 |

| Register 0x0E0, 0x1E0, 0x2E0, 0x3E0, 0x4E0, 0x5E0, 0x6E0, 0x7E0: RASE Interrupt Enable            | 281 |

| Register 0x0E1, 0x1E1, 0x2E1, 0x3E1, 0x4E1, 0x5E1, 0x6E1, 0x7E1: RASE Interrupt Status            | 282 |

| Register 0x0E2, 0x1E2, 0x2E2, 0x3E2, 0x4E2, 0x5E2, 0x6E2, 0x7E2: RASE Configuration/Control       | 284 |

| Register 0x0E3, 0x1E3, 0x2E3, 0x3E3, 0x4E3, 0x5E3, 0x6E3, 0x7E3: RASE SF Accumulation Period LSB  | 286 |

| Register 0x0E4, 0x1E4, 0x2E4, 0x3E4, 0x4E4, 0x5E4, 0x6E4, 0x7E4: RASE SF Accumulation Period      | 286 |

| Register 0x0E5, 0x1E5, 0x2E5, 0x3E5, 0x4E5, 0x5E5, 0x6E5, 0x7E5: RASE SF Accumulation Period MSB  | 287 |

| Register 0x0E6, 0x1E6, 0x2E6, 0x3E6, 0x4E6, 0x5E6, 0x6E6, 0x7E6: RASE SF Saturation Threshold LSB | 288 |

| Register 0x0E7, 0x1E7, 0x2E7, 0x3E7, 0x4E7, 0x5E7, 0x6E7, 0x7E7: RASE SF Saturation Threshold MSB | 288 |

| Register 0x0E8, 0x1E8, 0x2E8, 0x3E8, 0x4E8, 0x5E8, 0x6E8, 0x7E8: RASE SF Declaring Threshold LSB  | 289 |

| Register 0x0E9, 0x1E9, 0x2E9, 0x3E9, 0x4E9, 0x5E9, 0x6E9, 0x7E9: RASE SF Declaring Threshold MSB  | 289 |

| Register 0x0EA, 0x1EA, 0x2EA, 0x3EA, 0x4EA, 0x5EA, 0x6EA, 0x7EA: RASE SF Clearing Threshold LSB          | 290 |

|----------------------------------------------------------------------------------------------------------|-----|

| Register 0x0EB, 0x1EB, 0x2EB, 0x3EB, 0x4EB, 0x5EB, 0x6EB, 0x7EB: RASE SF Clearing Threshold MSB          | 290 |

| Register 0x0EC, 0x1EC, 0x2EC, 0x3EC, 0x4EC, 0x5EC, 0x6EC, 0x7EC: RASE SD Accumulation Period LSB         | 291 |

| Register 0x0ED, 0x1ED, 0x2ED, 0x3ED, 0x4ED, 0x5ED, 0x6ED, 0x7ED: RASE SD Accumulation Period             | 291 |

| Register 0x0EE, 0x1EE, 0x2EE, 0x3EE, 0x4EE, 0x5EE, 0x6EE, 0x7EE: RASE SD Accumulation Period MSB         | 292 |

| Register 0x0EF, 0x1EF, 0x2EF, 0x3EF, 0x4EF, 0x5EF, 0x6EF, 0x7EF: RASE SD Saturation Threshold LSB        | 293 |

| Register 0x0F0, 0x1F0, 0x2F0, 0x3F0, 0x4F0, 0x5F0, 0x6F0, 0x7F0: RASE SD Saturation Threshold MSB        | 293 |

| Register 0x0F1, 0x1F1, 0x2F1, 0x3F1, 0x4F1, 0x5F1, 0x6F1, 0x7F1: RASE SD Declaring Threshold LSB         | 294 |

| Register 0x0F2, 0x1F2, 0x2F2, 0x3F2, 0x4F2, 0x5F2, 0x6F2, 0x7F2: RASE SD Declaring Threshold MSB         | 294 |

| Register 0x0F3, 0x1F3, 0x2F3, 0x3F3, 0x4F3, 0x5F3, 0x6F3, 0x7F3: RASE SD Clearing Threshold LSB          | 295 |

| Register 0x0F4, 0x1F4, 0x2F4, 0x3F4, 0x4F4, 0x5F4, 0x6F4, 0x7F4: RASE SD Clearing Threshold MSB          | 295 |

| Register 0x0F5, 0x1F5, 0x2F5, 0x3F5, 0x4F5, 0x5F5, 0x6F5, 0x7F5: RASE  Receive K1                        | 296 |

| Register 0x0F6, 0x1F6, 0x2F6, 0x3F6, 0x4F6, 0x5F6, 0x6F6, 0x7F6: RASE<br>Receive K2                      | 297 |

| Register 0x0F7, 0x1F7, 0x2F7, 0x3F7, 0x4F7, 0x5F7, 0x6F7, 0x7F7: RASE<br>Receive Z1/S1                   | 298 |

| Register 0x0FC, 0x1FC, 0x2FC, 0x3FC, 0x4FC, 0x5FC, 0x6FC, 0x7FC: Channel Concatenation Status and Enable | 299 |

| Register 0x0FD, 0x1FD, 0x2FD, 0x3FD, 0x4FD, 0x5FD, 0x6FD, 0x7FD: Channel Concatenation Interrupt Status  | 300 |

| Register 0x0FE, 0x1FE, 0x2FE, 0x3FE, 0x4FE, 0x5FE, 0x6FE, 0x7FE: Channel Serial Interface Configuration  | 301 |

| Register 0x0FF, 0x1FF, 0x2FF, 0x3FF, 0x4FF, 0x5FF, 0x6FF, 0x7FF: Channel Clock Monitors                  | 302 |

| Register 0x1000: S/UNI-8x155 Clock Source Configuration                                                  | 303 |

| Register 0x1001: S/UNI-8x155 DCC Interface Configuration                                                 | 304 |

| Register 0x1004: APS Configuration and Status                                                            | 305 |

| Register 0x1005: APS FIFO Configuration and Status                                                       | 307 |

| Register 0x1006: APS Interrupt Status #1                                                                 | 308 |

| Register 0v1008: APS Reset Control                                                                       | 300 |

| Register 0x1011: TUL3 Interrupt Status/Enable 1         312           Register 0x1012: TUL3 Interrupt Status/Enable 2         315           Register 0x1013: TUL3 ATM Level 3 FIFO Configuration         316           Register 0x1014: TUL3 ATM Level 3 Signal Label         317           Register 0x1015: TUL3 POS Level 3 FIFO High Water Mark         318           Register 0x1016: TUL3 POS Level 3 FIFO High Water Mark         319           Register 0x1017: TUL3 POS Level 3 Signal Label         320           Register 0x1019: TUL3 Channel #0, #4 Mode Configuration         321           Register 0x1011: TUL3 Channel #1, #5 Mode Configuration         322           Register 0x1016: TUL3 Channel #3, #7 Mode Configuration         323           Register 0x1010: TUL3 Channel #3, #7 Mode Configuration         324           Register 0x1020: RUL3 Interface Configuration         325           Register 0x1020: RUL3 Interface Configuration         325           Register 0x1020: RUL3 ATM Level 3 Signal Label         327           Register 0x1021: RUL3 Interface Configuration         328           Register 0x1022: RUL3 ATM Level 3 Signal Label         333           Register 0x1022: RUL3 ATM Level 3 Signal Label         333           Register 0x1022: RUL3 POS Level 3 Transfer Size         332           Register 0x1022: RUL3 POS Level 3 Transfer Size         332                                   | Register 0x1010: TUL3 Interface Configuration                   | 310            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|

| Register 0x1013: TUL3 ATM Level 3 FIFO Configuration         316           Register 0x1014: TUL3 ATM Level 3 Signal Label         317           Register 0x1015: TUL3 POS Level 3 FIFO Low Water Mark         318           Register 0x1016: TUL3 POS Level 3 FIFO High Water Mark         319           Register 0x1017: TUL3 POS Level 3 Signal Label         320           Register 0x1019: TUL3 Channel #0, #4 Mode Configuration         321           Register 0x1019: TUL3 Channel #1, #5 Mode Configuration         322           Register 0x101B: TUL3 Channel #3, #7 Mode Configuration         323           Register 0x101C: TUL3 Channel #3, #7 Mode Configuration         324           Register 0x1020: RUL3 Interrupt Status/Enable         327           Register 0x1021: RUL3 Interrupt Status/Enable         327           Register 0x1022: RUL3 ATM Level 3 FIFO Configuration         328           Register 0x1022: RUL3 ATM Level 3 Signal Label         329           Register 0x1022: RUL3 ATM Level 3 Signal Label         329           Register 0x1024: RUL3 POS Level 3 Signal Label         331           Register 0x1025: RUL3 POS Level 3 Signal Label         331           Register 0x1026: RUL3 POS Level 3 Transfer Size         332           Register 0x1028: RUL3 Level 2 Channel #1, #5 Mode Configuration         333           Register 0x1029: RUL3 Level 2 Channel #3, #7 Mode Configuration          | Register 0x1011: TUL3 Interrupt Status/Enable 1                 | 312            |

| Register 0x1014: TUL3 ATM Level 3 Signal Label         317           Register 0x1015: TUL3 POS Level 3 FIFO Low Water Mark         318           Register 0x1016: TUL3 POS Level 3 FIFO High Water Mark         319           Register 0x1017: TUL3 POS Level 3 Signal Label         320           Register 0x1019: TUL3 Channel #0, #4 Mode Configuration         321           Register 0x101A: TUL3 Channel #1, #5 Mode Configuration         323           Register 0x101C: TUL3 Channel #3, #7 Mode Configuration         323           Register 0x1020: RUL3 Interface Configuration         324           Register 0x1021: RUL3 Interface Configuration         325           Register 0x1022: RUL3 ATM Level 3 FIFO Configuration         328           Register 0x1022: RUL3 ATM Level 3 FIFO Configuration         328           Register 0x1022: RUL3 ATM Level 3 Signal Label         329           Register 0x1024: RUL3 POS Level 3 Configuration         330           Register 0x1025: RUL3 POS Level 3 Signal Label         331           Register 0x1026: RUL3 POS Level 3 Transfer Size         332           Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration         333           Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration         334           Register 0x1029: RUL3 Level 2 Channel #3, #7 Mode Configuration         336           Register 0x1030: DUL TUL3 Configuration        | Register 0x1012: TUL3 Interrupt Status/Enable 2                 | 315            |

| Register 0x1015: TUL3 POS Level 3 FIFO Low Water Mark         318           Register 0x1016: TUL3 POS Level 3 FIFO High Water Mark         319           Register 0x1017: TUL3 POS Level 3 Signal Label         320           Register 0x1019: TUL3 Channel #0, #4 Mode Configuration         321           Register 0x101A: TUL3 Channel #1, #5 Mode Configuration         322           Register 0x101B: TUL3 Channel #2, #6 Mode Configuration         323           Register 0x101C: TUL3 Channel #3, #7 Mode Configuration         324           Register 0x1020: RUL3 Interface Configuration         325           Register 0x1021: RUL3 Interrupt Status/Enable         327           Register 0x1022: RUL3 ATM Level 3 FIFO Configuration         328           Register 0x1022: RUL3 ATM Level 3 Signal Label         329           Register 0x1022: RUL3 ATM Level 3 Signal Label         329           Register 0x1022: RUL3 POS Level 3 Configuration         330           Register 0x1022: RUL3 POS Level 3 Signal Label         331           Register 0x1025: RUL3 POS Level 3 Signal Label         331           Register 0x1026: RUL3 POS Level 3 Transfer Size         332           Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration         333           Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration         334           Register 0x1029: RUL3 Level 2 Channel #3, #7 Mode Configurat | Register 0x1013: TUL3 ATM Level 3 FIFO Configuration            | 316            |

| Register 0x1016: TUL3 POS Level 3 FIFO High Water Mark.       319         Register 0x1017: TUL3 POS Level 3 Signal Label       320         Register 0x1019: TUL3 Channel #0, #4 Mode Configuration       321         Register 0x101A: TUL3 Channel #1, #5 Mode Configuration       322         Register 0x101D: TUL3 Channel #2, #6 Mode Configuration       323         Register 0x1020: RUL3 Interface Configuration       324         Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x1020: RUL3 Level 2 Channel #2, #6 Mode Configuration       336         Register 0x1020: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1030: DLL RUL3 Configuration       336         Register 0x1030: DLL RUL3                                             | Register 0x1014: TUL3 ATM Level 3 Signal Label                  | 317            |

| Register 0x1017: TUL3 POS Level 3 Signal Label       320         Register 0x1019: TUL3 Channel #0, #4 Mode Configuration       321         Register 0x101A: TUL3 Channel #1, #5 Mode Configuration       322         Register 0x101B: TUL3 Channel #2, #6 Mode Configuration       323         Register 0x101C: TUL3 Channel #3, #7 Mode Configuration       324         Register 0x1020: RUL3 Interrupt Status/Enable       325         Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x1029: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1028: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1031: DLL RUL3 Control Status       338         Register 0x1036: DLL RUL3                                            | Register 0x1015: TUL3 POS Level 3 FIFO Low Water Mark           | 318            |

| Register 0x1019: TUL3 Channel #0, #4 Mode Configuration       321         Register 0x101A: TUL3 Channel #1, #5 Mode Configuration       322         Register 0x101B: TUL3 Channel #2, #6 Mode Configuration       323         Register 0x101C: TUL3 Channel #3, #7 Mode Configuration       324         Register 0x1020: RUL3 Interrace Configuration       325         Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Configuration       330         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x1029: RUL3 Level 2 Channel #2, #6 Mode Configuration       336         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x102B: RUL3 Level 3 Configuration       337         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1031: DLL TUL3 Control Status       338         Reg                                            |                                                                 |                |

| Register 0x101A: TUL3 Channel #1, #5 Mode Configuration       322         Register 0x101B: TUL3 Channel #2, #6 Mode Configuration       323         Register 0x101C: TUL3 Channel #3, #7 Mode Configuration       324         Register 0x1020: RUL3 Interrace Configuration       325         Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x1029: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x1028: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1028: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1029: DLL TUL3 Configuration       337         Register 0x1030: DLL TUL3 Configuration       336         Register 0x1030: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Control Status       340         Register 0x1038, 0x1030                                            |                                                                 |                |

| Register 0x101B: TUL3 Channel #2, #6 Mode Configuration       323         Register 0x101C: TUL3 Channel #3, #7 Mode Configuration       324         Register 0x1020: RUL3 Interface Configuration       325         Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x1029: RUL3 Level 2 Channel #2, #6 Mode Configuration       336         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x103D: DLL TUL3 Configuration       337         Register 0x1030: DLL TUL3 Reset       338         Register 0x1031: DLL RUL3 Configuration       340         Register 0x1032: DLL RUL3 Control Status       342         Register 0x1034: DLL RUL3 Control Status       342         Register 0x1036: DLL RUL3 Control Status       342         Register 0x1039, 0x103D: TAOP Link #0 and #1 Control       34                                                     | Register 0x1019: TUL3 Channel #0, #4 Mode Configuration         | 321            |

| Register 0x101C:       TUL3 Channel #3, #7 Mode Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Register 0x101A: TUL3 Channel #1, #5 Mode Configuration         | 322            |

| Register 0x1020: RUL3 Interface Configuration       325         Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #3, #7 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1031: DLL TUL3 Configuration       337         Register 0x1032: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Control Status       340         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1039, 0x103D: TAOP Link #0 and #1 Control       343         Register 0x1040, 0x104C: RAOP Link #0 and #1 Diagnostic       344         Register 0x1040, 0x104C: RAOP Link #0 and                                            | Register 0x101B: TUL3 Channel #2, #6 Mode Configuration         | 323            |

| Register 0x1021: RUL3 Interrupt Status/Enable       327         Register 0x1022: RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023: RUL3 ATM Level 3 Signal Label       329         Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1030: DLL TUL3 Configuration       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Control Status       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104B, 0x104F: RAO                                            | Register 0x101C: TUL3 Channel #3, #7 Mode Configuration         | 324            |

| Register 0x1022:       RUL3 ATM Level 3 FIFO Configuration       328         Register 0x1023:       RUL3 ATM Level 3 Signal Label       329         Register 0x1024:       RUL3 POS Level 3 Configuration       330         Register 0x1025:       RUL3 POS Level 3 Signal Label       331         Register 0x1026:       RUL3 POS Level 3 Transfer Size       332         Register 0x1028:       RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029:       RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A:       RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B:       RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030:       DLL TUL3 Configuration       337         Register 0x1030:       DLL TUL3 Configuration       338         Register 0x1032:       DLL TUL3 Control Status       339         Register 0x1034:       DLL RUL3 Configuration       340         Register 0x1036:       DLL RUL3 Reset       341         Register 0x1037:       DLL RUL3 Control Status       342         Register 0x1039,       0x103D:       TAOP Link #0 and #1 Control       343         Register 0x1048,       0x104C:       RAOP Link #0 and #1 Status/Interrupt Enable       345                                                                                                                                | Register 0x1020: RUL3 Interface Configuration                   | 325            |

| Register 0x1023:       RUL3 ATM Level 3 Signal Label       329         Register 0x1024:       RUL3 POS Level 3 Configuration       330         Register 0x1025:       RUL3 POS Level 3 Signal Label       331         Register 0x1026:       RUL3 POS Level 3 Transfer Size       332         Register 0x1028:       RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029:       RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A:       RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B:       RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030:       DLL TUL3 Configuration       337         Register 0x1030:       DLL TUL3 Reset       338         Register 0x1032:       DLL TUL3 Control Status       339         Register 0x1033:       DLL RUL3 Configuration       340         Register 0x1036:       DLL RUL3 Reset       341         Register 0x1036:       DLL RUL3 Control Status       342         Register 0x1037:       DLL RUL3 Control Status       342         Register 0x1039,       0x1030:       TAOP Link #0 and #1 Control       343         Register 0x1048,       0x104C:       RAOP Link #0 and #1 Section BIP-8 LSB       349                                                                                                                                                          | Register 0x1021: RUL3 Interrupt Status/Enable                   | 327            |

| Register 0x1024: RUL3 POS Level 3 Configuration       330         Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1031: DLL TUL3 Configuration       338         Register 0x1032: DLL TUL3 Control Status       339         Register 0x1033: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Configuration       340         Register 0x1037: DLL RUL3 Control Status       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1039, 0x103D: TAOP Link #0 and #1 Control       343         Register 0x1048, 0x104C: RAOP Link #0 and #1 Diagnostic       344         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Enable       345         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                           | Register 0x1022: RUL3 ATM Level 3 FIFO Configuration            | 328            |

| Register 0x1025: RUL3 POS Level 3 Signal Label       331         Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1032: DLL TUL3 Reset       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Status/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                        | Register 0x1023: RUL3 ATM Level 3 Signal Label                  | 329            |

| Register 0x1026: RUL3 POS Level 3 Transfer Size       332         Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1031: DLL TUL3 Configuration       338         Register 0x1032: DLL TUL3 Control Status       339         Register 0x1033: DLL TUL3 Configuration       340         Register 0x1036: DLL RUL3 Configuration       340         Register 0x1037: DLL RUL3 Reset       341         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Diagnostic       344         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Enable       345         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                        | Register 0x1024: RUL3 POS Level 3 Configuration                 | 330            |

| Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration       333         Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1032: DLL TUL3 Reset       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                   | Register 0x1025: RUL3 POS Level 3 Signal Label                  | 331            |

| Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configuration       334         Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1032: DLL TUL3 Reset       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349          Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                   | Register 0x1026: RUL3 POS Level 3 Transfer Size                 | 332            |

| Register 0x102A:       RUL3 Level 2 Channel #2, #6 Mode Configuration       335         Register 0x102B:       RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030:       DLL TUL3 Configuration       337         Register 0x1032:       DLL TUL3 Reset       338         Register 0x1033:       DLL TUL3 Control Status       339         Register 0x1034:       DLL RUL3 Configuration       340         Register 0x1036:       DLL RUL3 Reset       341         Register 0x1037:       DLL RUL3 Control Status       342         Register 0x1038,       0x103C:       TAOP Link #0 and #1 Control       343         Register 0x1039,       0x103D:       TAOP Link #0 and #1 Diagnostic       344         Register 0x1048,       0x104C:       RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049,       0x104D:       RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B,       0x104F:       RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                  | Register 0x1028: RUL3 Level 2 Channel #0, #4 Mode Configuration | ration 333     |

| Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configuration       336         Register 0x1030: DLL TUL3 Configuration       337         Register 0x1032: DLL TUL3 Reset       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1048, 0x104C: RAOP Link #0 and #1 Diagnostic       344         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Enable       345         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Register 0x1029: RUL3 Level 2 Channel #1, #5 Mode Configur      | ration 334     |

| Register 0x1030: DLL TUL3 Configuration       337         Register 0x1032: DLL TUL3 Reset       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Register 0x102A: RUL3 Level 2 Channel #2, #6 Mode Configu       | ration 335     |

| Register 0x1032: DLL TUL3 Reset       338         Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Register 0x102B: RUL3 Level 2 Channel #3, #7 Mode Configu       | ration336      |

| Register 0x1033: DLL TUL3 Control Status       339         Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Register 0x1030: DLL TUL3 Configuration                         | 337            |

| Register 0x1034: DLL RUL3 Configuration       340         Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Register 0x1032: DLL TUL3 Reset                                 | 338            |

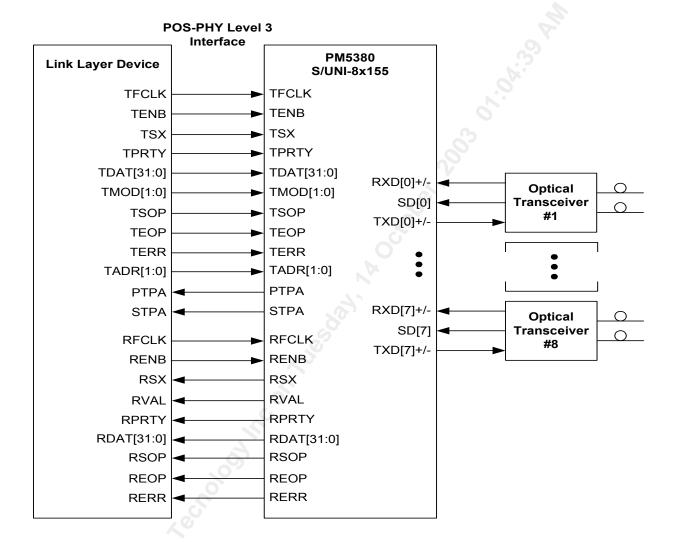

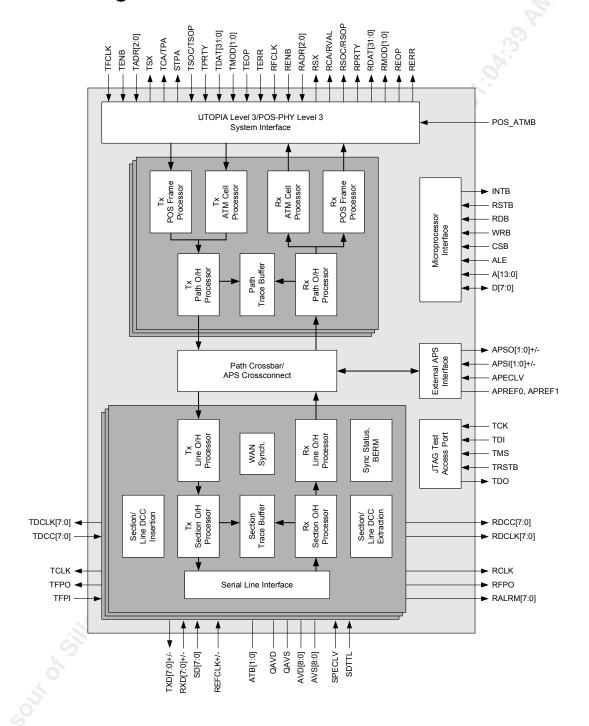

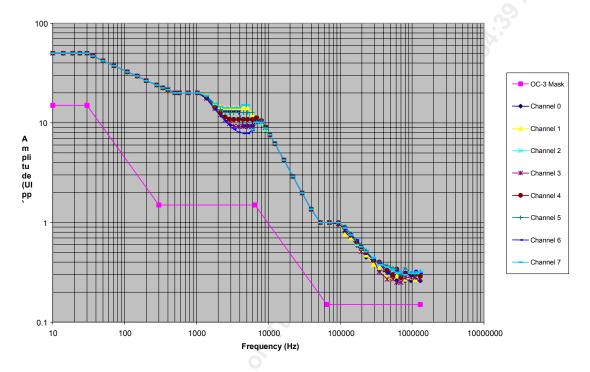

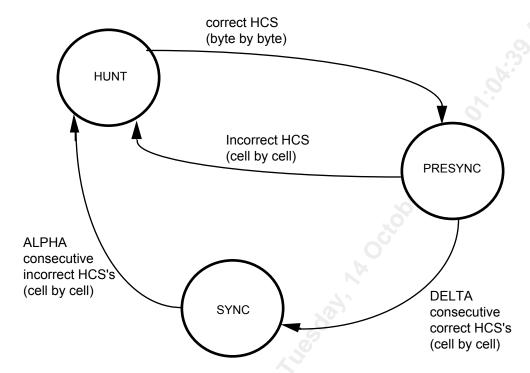

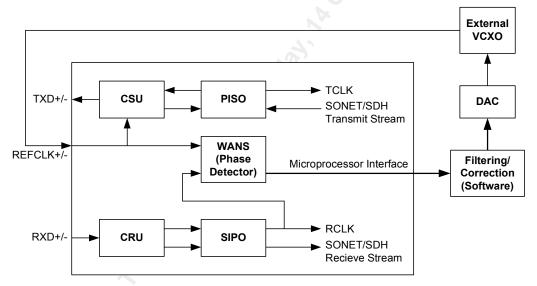

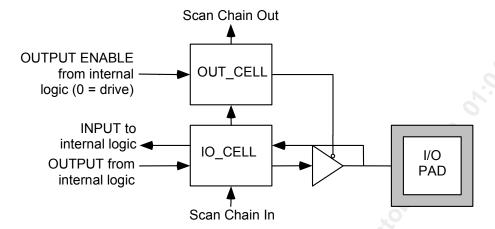

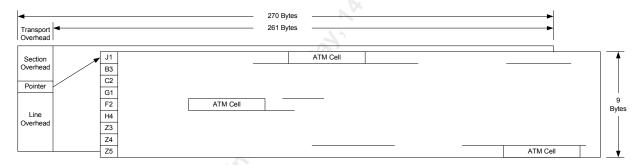

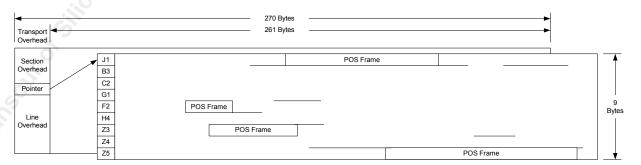

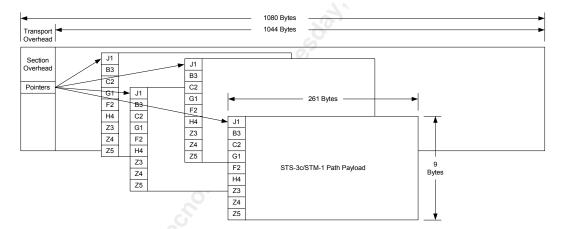

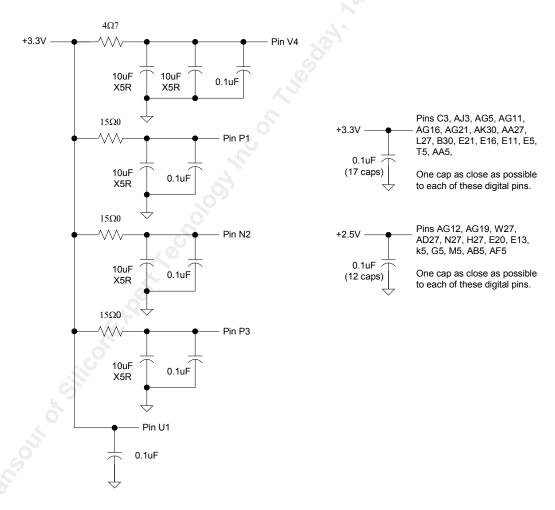

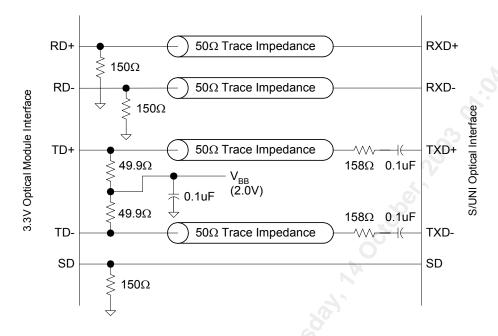

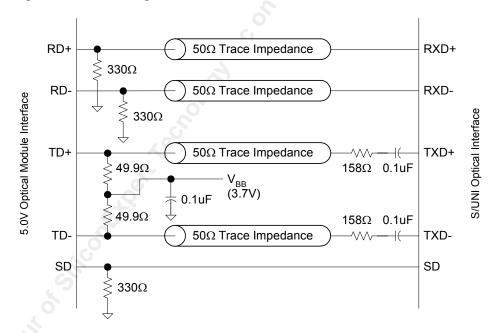

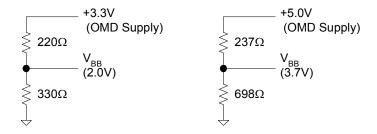

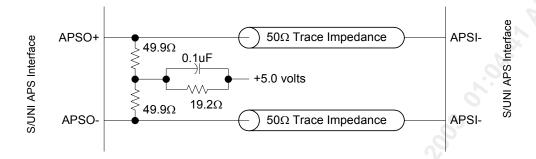

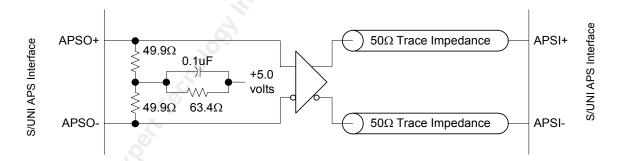

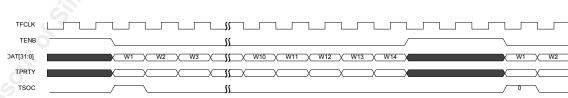

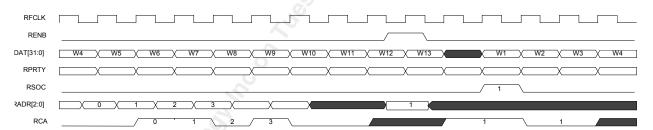

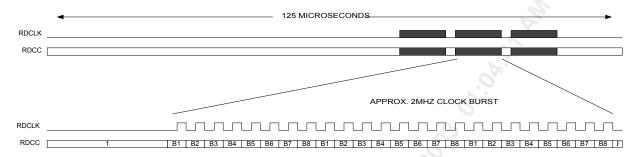

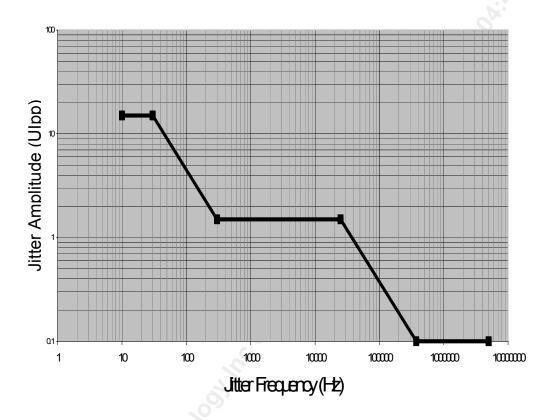

| Register 0x1036: DLL RUL3 Reset       341         Register 0x1037: DLL RUL3 Control Status       342         Register 0x1038, 0x103C: TAOP Link #0 and #1 Control       343         Register 0x1039, 0x103D: TAOP Link #0 and #1 Diagnostic       344         Register 0x1048, 0x104C: RAOP Link #0 and #1 Control/Interrupt Enable       345         Register 0x1049, 0x104D: RAOP Link #0 and #1 Status/Interrupt Status       347         Register 0x104A, 0x104E: RAOP Link #0 and #1 Section BIP-8 LSB       349         Register 0x104B, 0x104F: RAOP Link #0 and #1 Section BIP-8 MSB       349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Register 0x1033: DLL TUL3 Control Status                        | 339            |