# CM-120 USB 7-in-1 Combo Card Reader Controller Datasheet

Version 1.3

| VP         | Project Leader | Product   | Engineer             | Test        |

|------------|----------------|-----------|----------------------|-------------|

| Eric Cheng | Yuen-Hsu Lu    | Jason Liu | Bryan Lu<br>David Ho | Yi-Sung Lin |

#### C-MEDIA ELECTRONICS INC.

TEL: 886-2-8773-1100 FAX: 886-2-8773-2211

6F, 100, Sec. 4, Civil Boulevard, Taipei, Taiwan 106, R.O.C.

For detailed product information, please contact sales@cmedia.com.tw

# **NOTICES**

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHAT SO EVER, INCLUDING ANY WARRANTY OF MERCHANT ABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, DOCUMENT OR SAMPLE.

ALL RIGHTS RESERVED. NO PART OF THIS DOCUMENT MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS, ELECTRONIC OR MECHANICAL, INCLUDING INFORMATION STORAGE AND RETRIEVAL SYSTEMS, WITHOUT PERMISSION IN WRITING FROM THE C-MEDIA ELECTRONICS, INC.

Third-party brands and names are the property of their respective owners.

Copyright 2002-2003 © C-Media Electronics Inc.

\*C-Media reserves the right to modify the specifications without further notice.

#### 1.DESCRIPTION AND OVERVIEW

#### Overview

CM120 is a USB 1.1 full speed 7-in-1 controller for Combo Card Reader, applicable for major MB / NB chipsets of Intel, VIA, Ali, and SIS. CM120 is suitable for PC2001-compliant desktops, notebook computers, and any other platforms with USB host controller port.

#### Plug and Play

CM120 provides friendly plug and play function, and by using the select pin the power can be switched between usb bus power (500mA) or self power (100mA). It only takes one 12MHz crystal input to provide provides internal 48MHz PLL frequency for USB system operation. It is a popular purpose USB interface reader/writer controllers which integrates PLL, embedded data buffer and high performance engine. It comprises SPI (HID) mode to external MCU and 16 bits GPIO for user-friendliness.

#### 7-in-1 Card Interface

CM120 comprises six mainstream card interfaces: Compact Flash Card (CF) / Microdrive, Smart Media Card (SM) / eXtreme Digital Card (xD) , Multi Media Card (MMC) / Secure Digital Card (SD) and Memory Stick Card (MS).

#### Cost-effectiveness

As to the cost concern, CM120 integrates the processor and embedded data buffer. In that regard, it does not need any external memory module or others bom materials.

#### **Features**

- USB 1.1 Full Speed

- Compliant with USB Storage device class specifications

- Compliant with USB HID device specification v1.0

- Fixed USB full speed mode 12Mbits/s

- Uses 3 sets Endpoint control, two bulk pipes, and one control pipe

- USB bus power and self power capability. Low power consumption

- Internal PLL, need only 12MHz crystal to provide 48MHz frequency

- Fully Support Compact Flash (CF) card / Microdrive card interface

- Fully Support Smart Media (SM) / eXtreme Digital (xD) card interface

- Fully Support Multi Media card (MMC) / Secure Digital card (SD) interface

- Fully Support Memory Stick card (MS) interface

- Capable of preventing inappropriate card plug-out via the utilization of time out mechanism

- Support SPI mode interface

- Support 5 kinds of LED display for USB/CF/SD/SM/MS to indicate operation status

- Support 16 bits general purpose input and output

- Available 100 QFP package.

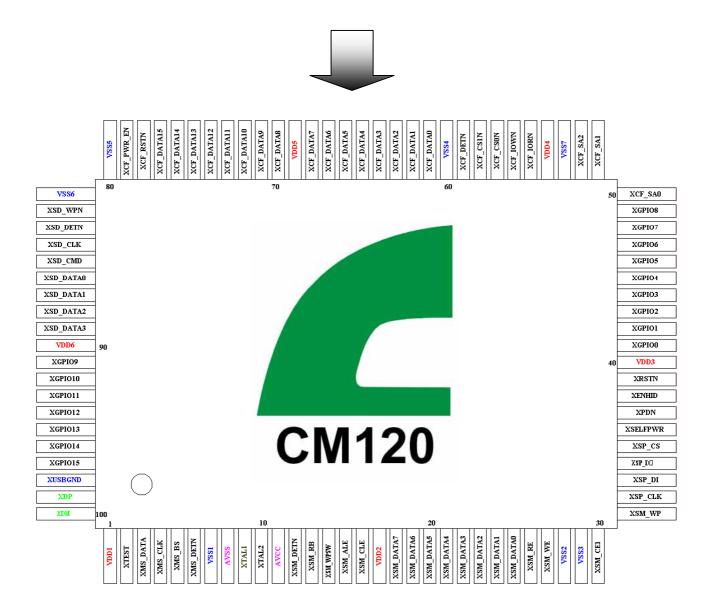

# **PIN DESCRIPTIONS**

#### **CM 120**

| Pin No.                    | Pin Name                          | Pin Type                                | Description                                                                                                                          |

|----------------------------|-----------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1                          | VDD1                              | Р                                       | Digital POWER 3.3V                                                                                                                   |

| 2                          | XTEST                             | I_S/P_L                                 | Testmode enable                                                                                                                      |

| 3                          | XMS_DATA                          | B/P_H                                   | Memory Stick data bus                                                                                                                |

| 4                          | XMS_CLK                           | 0                                       | Memory Stick clock output                                                                                                            |

| 5                          | XMS_BS                            | 0                                       | Memory Stick bus state output                                                                                                        |

| 6                          | XMS_DETN                          | I_S/P_H                                 | Memory Stick card detect low active                                                                                                  |

| 7                          | VSS1                              | Р                                       | Digital GND                                                                                                                          |

| 8                          | AVSS                              | P                                       | PLL Analog GND                                                                                                                       |

| 9                          | XTAL1                             | I/A                                     | 12MHz Crystal Input                                                                                                                  |

| 10                         | XTAL2                             | O/A                                     | 12MHz Crystal Output                                                                                                                 |

| 11                         | AVDD                              | P                                       | PLL Analog power 3.3V                                                                                                                |

| 12                         | XSMXD_DETN                        | I_S/P_H                                 | SmartMedia / xD card detect low active                                                                                               |

| 13                         | XSMXD_RBN                         | I/P_H                                   | SmartMedia / xD ready busy low active                                                                                                |

| 14                         | XSM_WPSWN                         | I_S/P_H                                 | SmartMedia write protect low active                                                                                                  |

| 15                         | XSMXD_ALE                         | 0                                       | SmartMedia / xD address latch enable                                                                                                 |

| 16                         | XSMXD_CLE                         | 0                                       | SmartMedia / xD command latch enable                                                                                                 |

| 17                         | VDD2                              | Р                                       | Digital POWER 3.3V                                                                                                                   |

| 18-25                      | XSMXD_DATA [7:0]                  | B/P_L                                   | SmartMedia / xD data bus [7:0]                                                                                                       |

| 26                         | XSMXD_REN                         | 0                                       | SmartMedia / xD read command                                                                                                         |

| 27                         | XSMXD_WEN                         | 0                                       | SmartMedia / xD write command                                                                                                        |

| 28                         | VSS2                              | Р                                       | Digital GND                                                                                                                          |

| 29                         | VSS3                              | P                                       | Digital GND                                                                                                                          |

| 30                         | XSMXD_CEN                         | 0                                       | SmartMedia / xD chip enable                                                                                                          |

| 31                         | XSMXD_WPN                         | 0                                       | SmartMedia / xD write protect output                                                                                                 |

| 32                         | XSP_CLK                           | I_S                                     | SPI mode clock output                                                                                                                |

| 33                         | XSP_DI                            | I                                       | SPI mode data input                                                                                                                  |

| 34                         | VOD DO                            |                                         | ODI and to to to t                                                                                                                   |

| 0.                         | XSP_DO                            | 0                                       | SPI mode data output                                                                                                                 |

| 35                         | XSP_CS                            | I                                       | SPI mode data output SPI mode chip select output                                                                                     |

|                            |                                   | I                                       |                                                                                                                                      |

| 35                         | XSP_CS                            | I                                       | SPI mode chip select output                                                                                                          |

| 35<br>36                   | XSP_CS<br>XSELFPWR                | I<br>I_S/P_L                            | SPI mode chip select output USB self power enable                                                                                    |

| 35<br>36<br>37             | XSP_CS XSELFPWR XPDN              | I<br>I_S/P_L<br>O                       | SPI mode chip select output USB self power enable Power Save for external Device low active                                          |

| 35<br>36<br>37<br>38       | XSP_CS XSELFPWR XPDN XENHID       | I<br>I_S/P_L<br>O<br>I_S/P_L            | SPI mode chip select output USB self power enable Power Save for external Device low active HID enable                               |

| 35<br>36<br>37<br>38<br>39 | XSP_CS XSELFPWR XPDN XENHID XRSTN | I<br>I_S/P_L<br>O<br>I_S/P_L<br>I_S/P_H | SPI mode chip select output USB self power enable Power Save for external Device low active HID enable System reset input low active |

| Pin No. | Pin Name               | Pin Type | Description                             |

|---------|------------------------|----------|-----------------------------------------|

| 50-52   | XCF_SA[0:2]            | 0        | CF/Microdrive address bus [0:2]         |

| 53      | VSS7                   | Р        | Digital GND                             |

| 54      | VDD4                   | Р        | Digital POWER 3.3V                      |

| 55      | XCF_IORN               | 0        | CF/Microdrive I/O read low active       |

| 56      | XCF_IOWN               | 0        | CF/Microdrive I/O write low active      |

| 57-58   | XCF_CS[0:1]N           | 0        | CF/Microdrive chip select bus [0:1]     |

| 59      | XCF_DETN               | I/P_H    | CF/Microdrive card detect low active    |

| 60      | VSS4                   | Р        | Digital GND                             |

| 61-68   | XCF_DATA[0:7]          | B/P_L    | CF/Microdrive data bus [0:7]            |

| 69      | VDD5                   | Р        | Digital POWER 3.3V                      |

| 70-77   | XCF_DATA[8:15]         | B/P_L    | CF/Microdrive data bus [8:15]           |

| 78      | XCF_ORSTN              | 0        | CF/Microdrive resest output low active  |

| 79      | XCF_PWR_EN             | 0        | CF/Microdrive power output enable       |

| 80      | VSS5                   | Р        | Digital GND                             |

| 81      | VSS6                   | Р        | Digital GND                             |

| 82      | XSD_WPN                | I_S/P_H  | SD/MMC write protect high active        |

| 83      | XSD_DETN               | I_S/P_H  | SD/MMC card detect low active           |

| 84      | XSD_CLK                | 0        | SD/MMC clock output                     |

| 85      | XSD_CMD                | B/P_H    | SD/MMC command/response                 |

| 86-89   | XSD_DATA[0:3]          | B/P_H    | SD/MMC data bus[0:3]                    |

| 90      | VDD6                   | Р        | Digital POWER 3.3V                      |

| 91      | XSMXD_PWR_EN /XGPIO[9] | B/P_L    | SmartMedia / xD power enable low active |

| 92      | XSD_PWR_EN / XGPIO[10] | B/P_L    | Secure Digital power enable low active  |

| 93      | XCF_LED / XGPIO[11]    | B/P_L    | CF/Microdrive access LED display        |

| 94      | XSD_LED / XGPIO[12]    | B/P_L    | SD/MMC access LED display               |

| 95      | XSMXD_LED / XGPIO[13]  | B/P_L    | SmartMedia / xD access LED display      |

| 96      | XMS_LED / XGPIO[14]    | B/P_L    | MemoryStick access LED display          |

| 97      | XUSB_LED / XGPIO[15]   | B/P_L    | USB access LED display                  |

| 98      | XUSBGND                | Р        | USB Analog GND                          |

| 99      | XDP                    | A/B      | USB data plus                           |

| 100     | XDM                    | A/B      | USB data minus                          |

Note 1. I: Input pin; O: Output pin; B: Bi-direction pin

2. I\_S : Schmitt trigger input

3. P\_L : Internal pull low4. P\_H : Internal pull high

5. A: Analog PAD

Figure 1. Pin Assignments (Top View)

CM120 7-in-1 USB combo card reader is designed according to the Universal Serial BUS(USB) Mass Storage Class specifications, capable of managing the file access and file format, dead lock avoidance, card detection, write protection, ECC corecation and detection, custiomized icon name and LED display in PC environment. It includes:

- File Management: file read/write, file delete, file copy, file execution and format.

- **Dead Locking Avoidance :** prevent users from inappropriate card plug-out card or other some unreasonable access via the utilization of time out mechanism.

- Card Detection : CF/Microvdrive, SD/MMC, SM/xD, MS card detection.

- ECC Corecation & Detectoion: SmartMedia (SM) / eXtreme Digital (xD) and Memory Stick (MS) support one bit ECC correcation and two bits ECC detection.

- Custiomized Icon Name: Provide customized name and iocn for each disk in file manager.

- LED Display: Provide 5 kinds LED dipslay with 1) USB access, 2) CF/Microdrive access, 3) SD/MMC access, 4) SM/xD access and 5) MS access. Sink current is 8mA.

- SPI Mode: Support SPI mode to process external MCU to access HID function.

- 16 bits GPIO: Support 16 bits general purpose input nand output for user-friendliness.

| SOURCE                                             | PIN NAME                                                     | PIN Position             |

|----------------------------------------------------|--------------------------------------------------------------|--------------------------|

| CF/Microdrive                                      | XCF_SA[0:2], XCF_IORN, XCF_IOWN, XCF_CS[0:1]N, XCF_DETN,     | 50~52,55,56,57~58,59,61  |

| CF/MICIOUTIVE                                      | XCF_DATA[0:15], XCF_RSTN, XCF_PWR_EN                         | ~68,70~77,78,79          |

| CD/MMC                                             | XSD_WPN, XSD_DETN, XSD_CLK, XSD_CMD, XSD_DATA[0:3],          | 02 02 04 05 00 00        |

| SD/MMC                                             | XSD_PWR_EN                                                   | 82,83,84,85,86~89        |

|                                                    | $XSMXD\_DETN, XSMXD\_RB, XSM\_WPSW, XSMXD\_ALE, XSMXD\_CLE,$ | 40.40.44.4540.40.05.00   |

| SM/xD                                              | XSMXD_DATA[7:0], XSMXD_RE, XSMXD_WE, XSMXD_CE1,              | 12,13,14,1516,18~25,26,  |

|                                                    | XSMXD_WP, XSMXD_PWR_EN                                       | 27,30,31,91              |

| MS XMS_DATA, XMS_CLK, XMS_BS, XMS_DETN, XMS_PWR_EN |                                                              | 3,4,5,6,49               |

| SPI                                                | XSP_CLK, XSP_DI, XSP_DO, XSP_CS                              | 32,33,34,35              |

| LED                                                | XUSB_LED, XMS_LED, XSM_LED, XSD_LED, XCF_LED                 | 97,96,95,94,93           |

| CDIO                                               | XUSB_LED, XMS_LED, XSMXD_LED, XSD_LED, XCF_LED,              | 07 04 40 44              |

| GPIO                                               | XSD_PWR_EN, XSMXD_PWR_EN, XMS_PWR_EN, XGPIO[7:0]             | 97~91,49~41              |

| Misc                                               | XTEST, XSELFPWR, XPDN, XENHID, XRSTN, XDP, XDM               | 2,36,37,38,39,99,100     |

| POWER                                              | VDD1,AVCC,VDD2,VDD3,VDD4,VDD5,VDD6                           | 1,11,17,40,54,69,90      |

| GND                                                | VSS1, AVSS, VSS2, AVSS3, AVSS7, AVSS4, AVSS5, AVSS6, XUSBGND | 7,8,28,29,53,60,80,81,98 |

<sup>\*</sup>Note: DI – digital input pin , DO – digital output pin, DIO – digital bi-directional pin, P – power pin, PD – pull down with 100K Ohm resistor, AI – analog input, AO – analog output

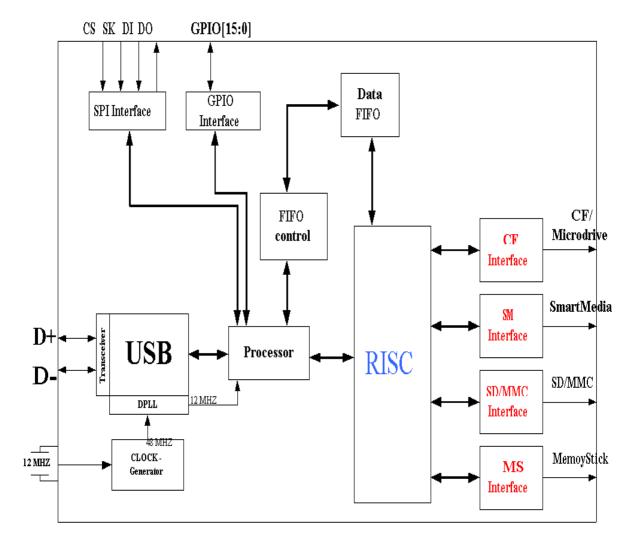

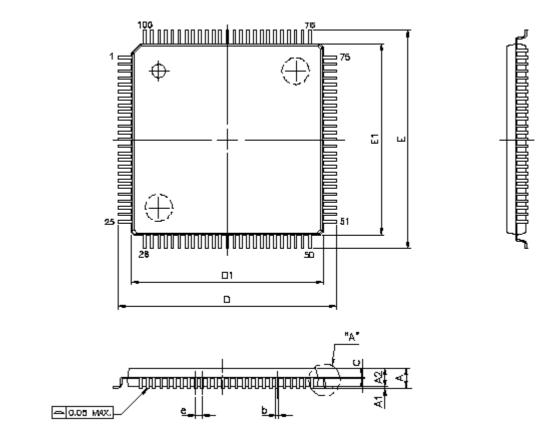

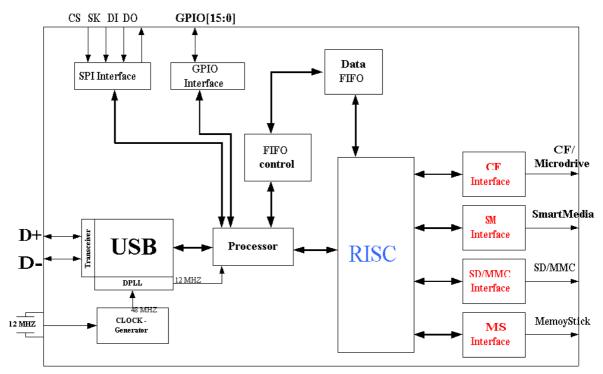

# **Block diagram of CM120**

Figure 2: Block Diagram Of CM120

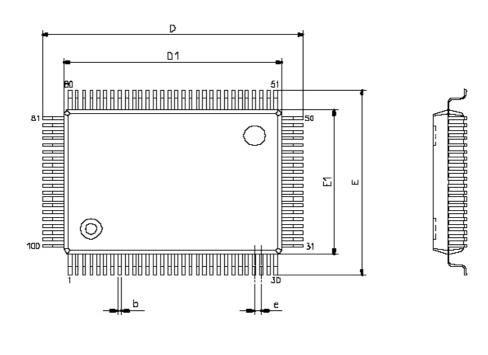

#### 2. ORDERING INFORMATION

| Model Number | Package     | Operating Ambient Temperature | Supply Range            |

|--------------|-------------|-------------------------------|-------------------------|

| CM120        | 100-Pin QFP | 0° C to +70° C                | DVdd =3.3V, AVdd = 3.3V |

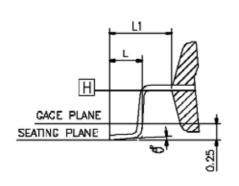

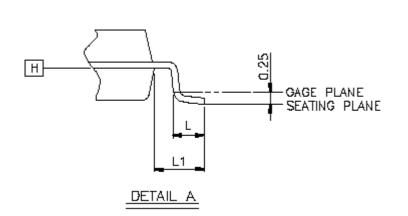

Outline of Dimensions Dimensions shown in inches and (mm)

#### ♦100 Pin QFP

| SYMBOLS | MIN.    | NOM           | MAX.  |

|---------|---------|---------------|-------|

| A       | I       | -             | 3.30  |

| A1      | 0.25    | _             | 1     |

| A2      | 2.6B    | 2. <b>8</b> D | 2.92  |

| ь       | 0.20    | 0.30          | 0.40  |

| D       | 24.49   | 24.80         | 25.10 |

| D1      | 19.90   | 20.00         | 20.10 |

| Ð       | 0.50    | 0.65<br>18.80 | D.8   |

| E       | E 1B.48 |               | 19.10 |

| E1      | 13.90   | 14.00         | 14.10 |

| L       | L 1.00  |               | 1.40  |

| L1      | L1 2.21 |               | 2.59  |

| e O     |         | _             | 12    |

UNIT: mm

Figure 3: Mechanical Dimension of CM120

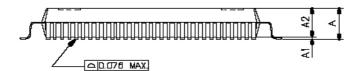

#### ♦100 Pin LQFP

VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| MIN.      | NOM.                                       | MAX. |  |

|-----------|--------------------------------------------|------|--|

|           |                                            | 1.60 |  |

| 0.05      |                                            | 0.15 |  |

| 1.35      | 1.40                                       | 1.45 |  |

| 0.17      | 0.20                                       | 0.27 |  |

| 0.09      | 0.127                                      | 0.20 |  |

| 1         | 6.00 BS                                    | С    |  |

| 1         | 4.00 BS                                    | С    |  |

| 16.00 BSC |                                            |      |  |

| 14.00 BSC |                                            |      |  |

|           | 0.50 BS                                    | С    |  |

| 0.45      | 0.60                                       | 0.75 |  |

|           | 1.OD REF                                   | =    |  |

|           | <br>0.05<br>1.35<br>0.17<br>0.09<br>1<br>1 |      |  |

Figure 3.1: Mechanical Dimension of CM120L

# **TABLE OF CONTENTS**

| 1. | DE  | SCRIPTION AND OVERVIEW           | 2  |

|----|-----|----------------------------------|----|

| 2. | OR  | DERING INFORMATION               | 8  |

| 3. | PIN | V/SIGNAL DESCRIPTIONS            | 13 |

| 3  | 3.1 | USB & Misc I/O SIGNALS           | 13 |

| 3  | 3.2 | CF&Microdrive I/O SIGNALS        | 13 |

| 3  | 3.3 | SD&MMC I/O SIGNALS               | 14 |

| 3  | 3.4 | SM I/O SIGNALS                   | 14 |

| 3  | 3.5 | MS I/O SIGNALS                   | 14 |

| 3  | 3.6 | POWER AND GROUND SIGNALS         | 15 |

| 4. | SY  | STEM INTERFACE                   | 16 |

| 4  | 1.1 | SYSTEM                           | 16 |

| 4  | 1.2 | CLOCKING                         | 16 |

| 4  | 1.3 | RESETTING                        | 16 |

| 4  | 1.4 | CF/Microdrive INTERFACE PROTOCOL | 17 |

| 4  | 1.5 | SD/MMC INTERFACE PROTOCOL        | 18 |

| 4  | 1.6 | SM INTERFACE PROTOCOL            | 20 |

| 4  | 1.7 | MS INTERFACE PROTOCOL            | 24 |

| 4  | 1.8 | USB LOW POWER MODE               | 26 |

| 5. | AC  | TIMING CHARACTERISTICS           | 28 |

| 5  | 5.1 | POWER ON RESET                   | 28 |

| 5  | 5.2 | SYSTEM RESET                     | 28 |

| 5  | 5.3 | CLOCKS                           | 28 |

| 5  | 5.4 | COMPACT FLASH TIMING             | 29 |

| 5  | 5.5 | SECURE DIGITAL TIMING            | 31 |

| 5  | 5.6 | SMARTMEDIA TIMING                | 30 |

| 5  | 5.7 | XD TIMING                        | 34 |

| 5  | 5.8 | MEMORYSTICK TIMING               | 35 |

| 6  | DE  | EEDENCES                         | 27 |

# **LIST OF FIGURES**

| Figure 1: Pin Assignments (Top View)                                                        | 5  |

|---------------------------------------------------------------------------------------------|----|

| Figure 2: Block Diagram Of CM120                                                            | 7  |

| Figure 3: Mechanical Dimension of CM120                                                     | 8  |

| Figure 3: Mechanical Dimension of CM120                                                     | 9  |

| Figure 4 : CM120 block diagram                                                              | 16 |

| Figure 5 : CpmpactFlash Storage Card Block Diagram                                          | 17 |

| Figure 6: "no response" and "no data" operations                                            | 18 |

| Figure 7: Command token format                                                              | 19 |

| Figure 8: Response token format                                                             | 19 |

| Figure 9: Timing of multiple block read command and stop command, read status command       | 19 |

| Figure 10: Timing of multiple block write command and stop command received after last data | a  |

| block programming, and the latter is the read status command                                | 20 |

| Figure 11 : SmartMedia Card                                                                 | 20 |

| Figure 11.1: xD Card                                                                        | 21 |

| Figure 12: SM Card Sequential Read Timing                                                   | 22 |

| Figure 13: SM Card Auto Page Program Timing                                                 | 22 |

| Figure 14: SM Card Auto Block Erase Timing                                                  | 23 |

| Figure 15 : SM Card ID Read Timing                                                          | 23 |

| Figure 16: SM Card Reset Timing                                                             | 24 |

| Figure 17: Sequential Read                                                                  | 24 |

| Figure 18: MS Serial Interface Block Diagram                                                | 26 |

| Figure 19: MS Read Protocol                                                                 | 26 |

| Figure 20: MS Write Protocol                                                                | 27 |

| Figure 21: Suspend and Resume wakeup state                                                  | 27 |

| Figure 22: Power-On Reset Timing Diagram                                                    | 28 |

| Figure 23: System Reset                                                                     | 28 |

| Figure 24: CLK Timing Diagram                                                               | 28 |

| Figure 25: True IDE Mode I/O Read Timing Diagram                                            | 29 |

| Figure 26: True IDE Mode I/O Write Timing Diagram                                           | 30 |

| Figure 27: SD/MMC bus signal levels                                                         | 31 |

| Figure 28: Timing diagram data input/output referenced to clock                             | 31 |

# **LIST OF TABLES**

| Table 1: USB & Misc Signal List                   | 12 |

|---------------------------------------------------|----|

| Table 2 : CF/Microdrive Signal List               | 12 |

| Table 3 : SD/MMC Signal List                      | 13 |

| Table 4:SM Signal List                            | 13 |

| Table 5:MS Signal List                            | 13 |

| Table 6: Power and Ground Signal of CM120         | 14 |

| Table 7: CF True IDE Mode I/O Decoding            | 17 |

| Table 8 : Clocks                                  | 28 |

| Table 9: True IDE Mode I/O Input (Read) Timing    | 28 |

| Table 10: True IDE Mode I/O Output (Write) Timing | 29 |

| Table 11:SD/MMC bus I/O Signal Voltages           | 30 |

| Table 12:SD/MMC Bus Timing, Parameter Value       | 31 |

| Table 13: AC Characteristics                      | 31 |

| Table 14: Parameter                               | 33 |

| Table 15: ATE Test Mode Timing                    | 35 |

#### 3. PIN / SIGNAL DESCRIPTIONS

#### 3.1 USB & Misc I/O SIGNALS

These signals connect CM120 to USB host controller counterpart, external crystal, multi-power selection, general purpose control and external MCU component.

Table 1: USB & Misc Signal List

| Signal Name | Type | Description                      |

|-------------|------|----------------------------------|

| XDP         | I/O  | USB data plus signal             |

| XDN         | I/O  | USB data minus signal            |

| XTEST       | I    | Testmode enable                  |

| XTAL1       | I    | 12 MHz crystal input             |

| XTAL2       | 0    | 12 MHz crystal output            |

| XSELFPWR    | I    | USB self power enable            |

| XPDN        | 0    | USB power down enable            |

| XENHID      | I    | HID function enable              |

| XRSTN       | I    | System reset input               |

| XSP_CLK     | I    | SPI mode clock input             |

| XSP_DI      | I    | SPI mode data input              |

| XSP_DO      | 0    | SPI mode data output             |

| XSP_CS      | I    | SPI mode chipselect input        |

| XGPIO[7:0]  | I/O  | General purpose input and output |

#### 3.2 CF & Microdrive I/O SIGNALS

These signals connect CM120 to analog sources and sinks, including microphones and speakers.

Table 2: CF/Microdrive Signal List

| Signal Name    | Type | Description                          |

|----------------|------|--------------------------------------|

| XCF_SA[2:0]    | 0    | CF/Microdrive addressbus[2:0] output |

| XCF_IORN       | 0    | CF/Microdrive read command output    |

| XCF_IOWN       | 0    | CF/Microdrive write command output   |

| XCF_CS[1:0]N   | 0    | CF/Microdrive chip select bus output |

| XCF_DETN       | I    | CF/Microdrive card detect input      |

| XCF_DATA[15:0] | I/O  | CF/Microdrive data bus               |

| XCF_RSTN       | 0    | CF/Microdrive reset output           |

| XCF_PWR_EN     | 0    | CF/Microdrive power enable output    |

| XCF_LED        | 0    | CF/Microdrive LED output             |

#### 3.3 SD/MMC I/O SIGNALS

Table 3: SD/MMC Signal List

| Signal Name   | Туре | Description                |  |  |

|---------------|------|----------------------------|--|--|

| XSD_WPN       | I    | SD/MMC write protect input |  |  |

| XSD_DETN      | I    | SD/MMC card detect input   |  |  |

| XSD_CLK       | 0    | SD/MMC clock output        |  |  |

| XSD_CMD       | I/O  | SD/MMC command response    |  |  |

| XSD_DATA[3:0] | I/O  | SD/MMC data bus            |  |  |

| XSD_PWR_EN    | 0    | SD/MMC power enable output |  |  |

| XSD_LED       | 0    | SD/MMC LED output          |  |  |

#### 3.4 SM / xD I/O SIGNALS

Table 4: SM Signal List

| Signal Name     | Туре | Description                  |  |  |

|-----------------|------|------------------------------|--|--|

| XSMXD_DETEN     | I    | SM / xD card detect input    |  |  |

| XSMXD_RB        | I    | SM / xD read/busy input      |  |  |

| XSM_WPSW        | ı    | SM write protect input       |  |  |

| XSMXD_ALE       | 0    | SM / xD address latch output |  |  |

| XSMXD_CLE       | 0    | SM / xD command latch output |  |  |

| XSMXD_DATA[7:0] | I/O  | SM / xD data bus             |  |  |

| XSMXD_RE        | 0    | SM / xD read command output  |  |  |

| XSMXD_WE        | 0    | SM / xD write command output |  |  |

| XSMXD_CE1       | 0    | SM / xD chip enable output   |  |  |

| XSMXD_WP        | 0    | SM / xD write protect output |  |  |

| XSMXD_PWR_EN    | 0    | SM / xD power enable output  |  |  |

| XSMXD_LED       | 0    | SM / xD LED output           |  |  |

#### 3.5 MS I/O SIGNALS

Table 5 : MS Signal List

| Signal Name | Type | Description            |  |  |

|-------------|------|------------------------|--|--|

| XMS_DATA    | I/O  | MS data bus            |  |  |

| XMS_CLK     | 0    | MS clock output        |  |  |

| XMS_BS      | 0    | MS bus state output    |  |  |

| XMS_DETN    | I    | MS card detect input   |  |  |

| XMS_PWR_EN  | 0    | MS power enable output |  |  |

| XMS_LED     | 0    | MS LED output          |  |  |

#### 3.6 POWER AND GROUND SIGNALS

Table 6: Power and Ground Signal of CM120

| Signal Name | Туре | Description              |  |  |

|-------------|------|--------------------------|--|--|

| VDD1        | Р    | Digital power Vdd = 3.3V |  |  |

| VDD2        | Р    | Digital power Vdd = 3.3V |  |  |

| VDD3        | Р    | Digital power Vdd = 3.3V |  |  |

| VDD4        | Р    | Digital power Vdd = 3.3V |  |  |

| VDD5        | Р    | Digital power Vdd = 3.3V |  |  |

| VDD6        | Р    | Digital power Vdd = 3.3V |  |  |

| VSS1        | Р    | Digital ground           |  |  |

| VSS2        | Р    | Digital ground           |  |  |

| VSS3        | Р    | Digital ground           |  |  |

| VSS4        | Р    | Digital ground           |  |  |

| VSS5        | Р    | Digital ground           |  |  |

| VSS6        | Р    | Digital ground           |  |  |

| VSS7        | Р    | Digital ground           |  |  |

| XUSBGND     | Р    | Analog ground            |  |  |

| AVCC        | Р    | Analog power Vdd = 3.3V  |  |  |

| AVSS        | Р    | Analog ground            |  |  |

#### 4. SYSTEM INTERFACE

#### 4.1 System

All USB device command/status information intertransmit data over USB bus with four signals (D+, D-, VBUS, GND) cable. The system interface of the signals connecting the CM120 is shown in Figure 1. It includes clock generator, reset, processor, risc, fifo control, data memory, CF/Microdrive interface, SmartMedia interface, SD/MMC interface, Memory Stick interface, SPI and GPIO.

Figure 4. CM120 block diagram

#### 4.2 CLOCK Generator

CM120 generates its clock internally from an externally connected 12MHz crystal clock source through the XTAL1 pin. Internal PLL function provides 48MHz for USB operation.

The beginning of all USB packets or frames transmitted over USB bus needs one 4X12 MHz to decode the correct phase information. Subsequently, it is sampled on the receiver side of CM120 on each immediately followed rising edge of PLL 48MHz clock.

#### 4.3 RESETTING

There are 3 types of reset detailed under "Timing Characteristics":

- 1. A Power-on reset where all CM120 logic (registers included) is initialized to its default state

- 2. A System reset where the contents of the CM120 register set are left unaltered

- 3. A Register reset which only initializes the CM120 registers to their default states

#### 4.4 CF/Microdrive INTERFACE PROTOCOL

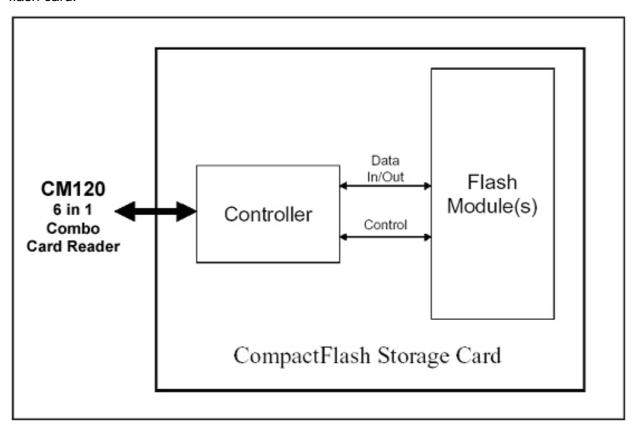

The CompactFlash interface contains a 50-pin connector to CompactFlash Storage Card or Microdrive. The CF interface of the chip can be connected to either type I CF or type II Microdrive flash card.

Figure 5:CpmpactFlash Storage Card Block Diagram

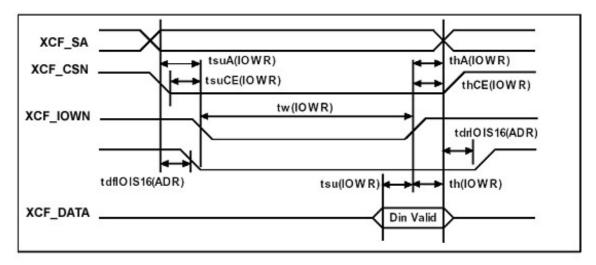

The Figure 25 and Figure 26 are the I/O read/write waveform for our CF bus protocol in True IDE Mode. The I/O read/write timing can be referenced on CF+ & CF SPECIFICATION REV. 1.4. The I/O decoding method is listed in table 7. It is obvious that the figure 8 is the read status cycle, and the figure 9 is the write data cycle.

|         |          |         |         |         | <u>*</u>         |                  |

|---------|----------|---------|---------|---------|------------------|------------------|

| XCF-S1N | XCF-CS0N | XCF_SA2 | XCF_SA1 | XCF_SAD | XCF_IORN=0       | CXF_IOWN=0       |

| 1       | 0        | 0       | 0       | 0       | RD DATA          | WR DATA          |

| 1       | 0        | 0       | 0       | 1       | ERROR REGISTER   | FEATURES         |

| 1       | 0        | 0       | 1       | 0       | SECTOR COUNT     | SECTOR COUNT     |

| 1       | 0        | 0       | 1       | 1       | SECTOR NO.       | SECTOR NO.       |

| 1       | 0        | 1       | 0       | 0       | CYLINDER LOW     | CYLINDER LOW     |

| 1       | 0        | 1       | 0       | 1       | CYLINDER HIGH    | CYLINDER HIGH    |

| 1       | 0        | 1       | 1       | 0       | SELECT CARD/HEAD | SELECT CARD/HEAD |

| 1       | 0        | 1       | 1       | 1       | STATUS           | COMMAND          |

| 0       | 1        | 1       | 1       | 0       | ALL STATUS       | DEVICE CONTROL   |

| 0       | 1        | 1       | 1       | 1       | DRIVE ADDRESS    | RESERVED         |

Table 7: CF True IDE Mode I/O Decoding

After the pattern of the CF bus cycle is known, it also needs to know the protocol of the PIO data command( In/Out ), PIO non-data command which may be referenced by " Information Technology - AT Attachment with Packet Interface Extension (ATA/ATAPI-4) Working Draft, Revision 18, 19 August 1998" from p.223 to p.232. This protocol is used for the communication with C-Media CF flash cards that are viewed as the IDE device.

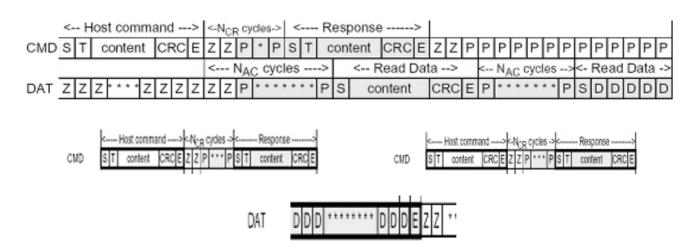

#### 4.5 SD/MMC INTERFACE PROTOCOL

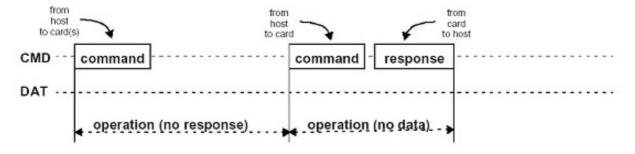

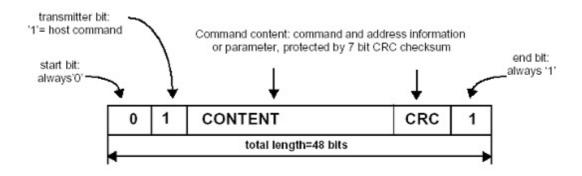

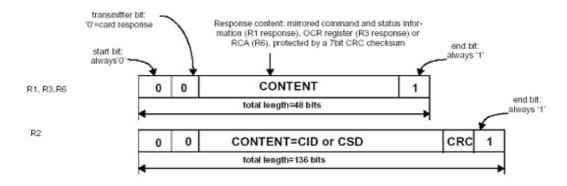

The SD/MMC communication is based on an advanced 9-pin interface (Clock, Command, Data bus and Power Line) designed to operate in a low voltage range. The both communication protocols are SD and SPI.

#### 1. SD/MMC bus

Figure 6:"no response" and "no data" operations

Date: 09/09/2003 Version: 1.3 - 18 -

Figure 7: Command token format

Figure 8:Response token format

Figure 9: Timing of multiple block read command and stop command, read status command

Figure 10: Timing of multiple block write command and stop command received after last data block programming, and the latter is the read status command

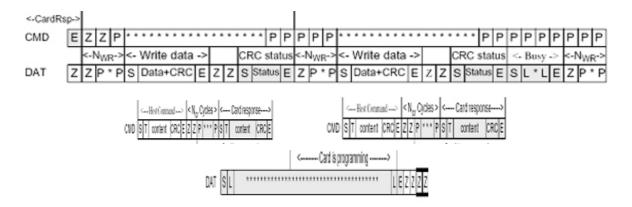

#### 4.6 SM / xD INTERFACE PROTOCOL

The Smart Media / eXtreme Digital card interface provides input and output frame data streams, corresponding to the complex bundles of all digital data targeting the CM120 , and control registers.

Figure 11: SmartMedia Card

| Pin | Signals |       |                      |                 | Signal Proces | sing               |

|-----|---------|-------|----------------------|-----------------|---------------|--------------------|

| No. | Pin     | Туре  | Function             | Pull<br>Up/Down | Note          |                    |

| 1   | GND     | (O)   | GND/(Card Detect)    |                 | Can double as | Card Detect signal |

| 2   | R/-B    | O(OD) | Ready/Busy           |                 | 2)            | Open drain         |

| 3   | -RE     | I     | Read Enable          | Up              | 1)            |                    |

| 4   | -CE     | I     | Card Enable          | Up              | 1)            |                    |

| 5   | CLE     | I     | Command Latch Enable | Down            | 1)            |                    |

| 6   | ALE     | I     | Address Latch Enable | Down            | 1)            |                    |

| 7   | -WE     | I     | Write Enable         | Up              | 1)            |                    |

| 8   | -WP     | I     | Write Protect        | Down            | 1)            |                    |

| 9   | GND     |       | GND                  |                 |               |                    |

| 10  | D0      | I/O   | Data0                | Down            |               |                    |

| 11  | D1      | I/O   | Data1                | Down            |               |                    |

| 12  | D2      | I/O   | Data2                | Down            |               |                    |

| 13  | D3      | I/O   | Data3                | Down            |               |                    |

| 14  | D4      | I/O   | Data4                | Down            |               |                    |

| 15  | D5      | I/O   | Data5                | Down            |               |                    |

| 16  | D6      | I/O   | Data6                | Down            |               |                    |

| 17  | D7      | I/O   | Data7                | Down            |               |                    |

| 18  | Vec     | S     | Vec                  |                 |               |                    |

S: Power supply; I: Input to Card, O: Output from Card, I/O: Bi-directional Signal names indicate Low True signals

Figure 11.1: xD Card

#### 4.6.1. Interface Timing Diagram Example (Smart Media / xD Card)

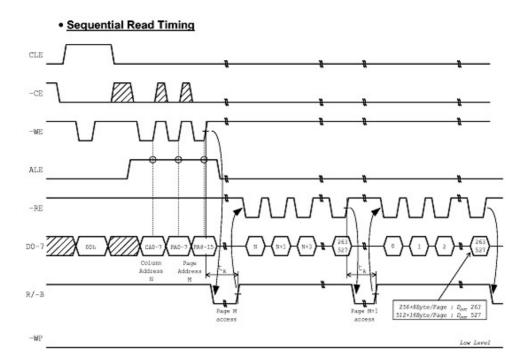

Figure 12: SM/xD Card Sequential Read Timing

#

Figure 13: SM/xD Card Auto Page Program Timing

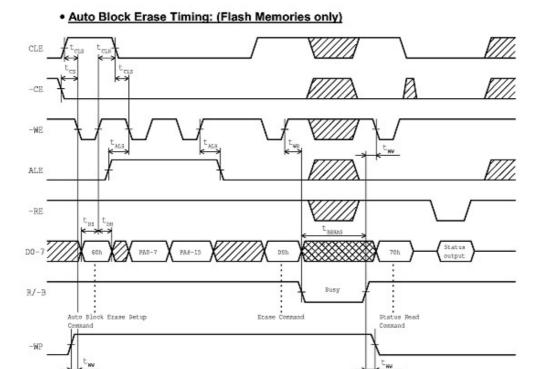

Figure 14: SM/xD Card Auto Block Erase Timing

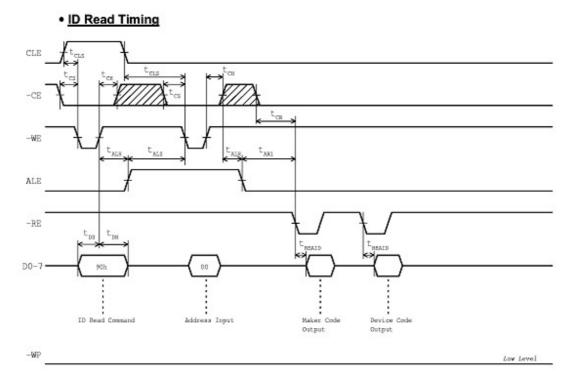

Figure 15: SM/xD Card ID Read Timing

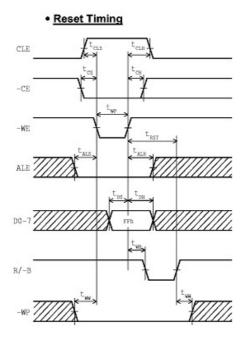

Figure 16: SM/xD Card Reset Timing

#### 4.6.2 Description

#### 4.6.2.1 Sequential Read

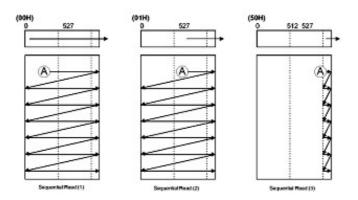

When a Data Read is executed, the initial address is specified at the start of the Data Read. Then, it is only necessary to input the -RE clock(without additional address input) in order to automatically increase the page address and continuously execute Read operation.

On the second page or the later, all data in the main and redundant sections are output using Read commands (1) and (2). Only the redundant section is output using Read command (3). The sequential Read Mode can be used only within a single block.

Figure 17: Sequential Read

#### 4.6.2.2 Precautions when Programming Pages

- a. Limit of the Write Operation to the Same Page

The data and redundant areas can only be written simultaneously for one time. If the system configuration requires, writing to the redundant area may occur for one more time.

- b. Writing to Pages within a Block

During the program operation, writing should be executed consecutively from a lower address

page to an upper address page. Random page programming should be avoided.

#### 4.6.2.3 Precautions for writing in the redundant section only

Writing only to the redundant section requires the Reset command to be input and the Read command to be used to change data/pointer mode, as indicated in the following sequence. To program the data section after writing into the redundant section, the Reset command or Read commands (1) or (2) must be issued to reset the data pointer mode.

FFb ... 50b ... 80b ......

$$\begin{cases}

FFh \\

00h \\

01h

\end{cases}$$

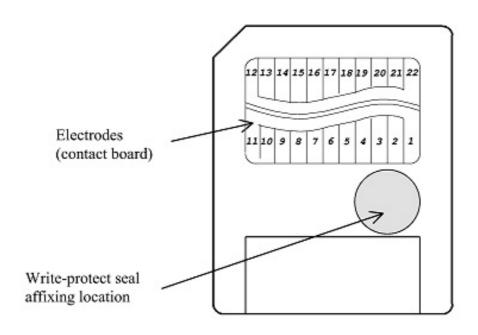

#### 4.7 MS INTERFACE PROTOCOL

#### **Pin Assignment**

| Pin No. | Pin Name |

|---------|----------|

| 1       | VSS      |

| 2       | BS       |

| 3       | VCC      |

| 4       | DIO      |

| 5       | Reserve  |

| 6       | INS      |

| 7       | Reserve  |

| 8       | SCLK     |

| 9       | VCC      |

| 10      | VSS      |

Reverse side of the card

# Host MemoryStick Flash Memory Flash Memory Controller Registers PageBuffer Serial I/F Solio BS Solio Sol

#### **Serial Interface for Memory Stick:**

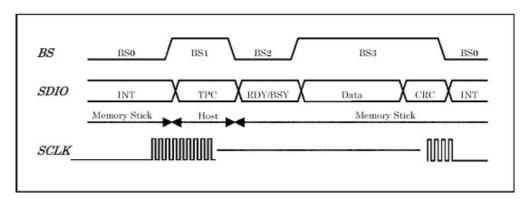

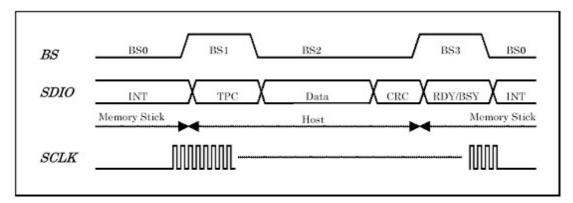

Figure 18: MS Serial Interface Block Diagram

Above is the Memory Stick block diagram. Host is on the left hand side whereas MS card on the right hand side, communicating by means of three signal lines: SDIO, BS, and SCLK. Data and command are converted on the SDIO, and regulation signals are controlled by host system via BS and SCLK. Basically, the serial interface protocol have four bus states: BSO – IDLE stage; BS1 – TPC stage; BS2 – handshake or data stage; BS3 - handshake or data stage. Bus state sequence are different between read and write operations.

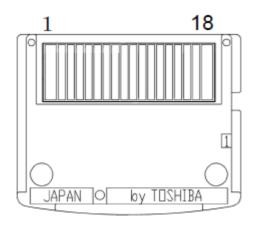

Figure 19: MS Read Protocol

Above is the MS read command running chart. It contains 4 stages: during BS1 stage, host sends the read command (all command called TPC here). During BS2 stage, MS card will tell the host if it is ready to send the data. And when data is ready, it will be sent during BS3 stage combined with 16bit CRC data. After all is done, both sides will return to BS0 stage and wait for another command or interruption.

Figure 20: MS Write Protocol

Above is the MS write command running chart. Just like the read command, it contains 4 stages: BS1 stage for command to transmit from host to card. And then data will be transmitted from host to card during BS2 state with CRC check immediately. After getting the reply during BS3 stage, both sides will return to BS0 stage and wait, just like what is mentioned in the read command section.

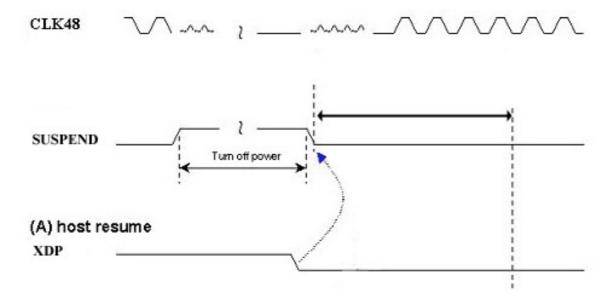

#### 4.8 USB LOW POWER MODE

The CM120 can be placed in the low power mode by host-issued suspend mode. Both crystal and PLL will turn off the power, and be held at a logic low power level. The CM120 USB device controller can wake up host resume signal when DP goes to low state.

Figure 21: Suspend and Resume wakeup state

#### 5. AC TIMING CHARACTERISTICS

(Tambient = 25 °C, AVdd =  $5.0V \pm 5\%$ , DVdd =  $3.3V \pm 5\%$ , AVss=DVss+0V; 50pF external load)

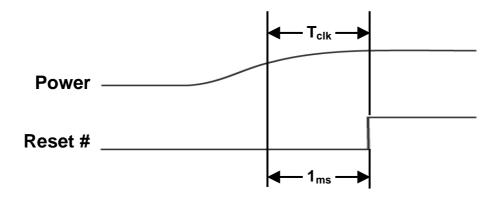

#### **5.1 POWER-ON RESET**

Figure 22: Power-On Reset Timing Diagram

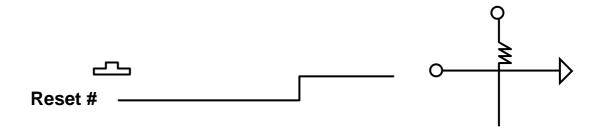

#### **5.2 SYSTEM RESET**

Figure 23. System Reset

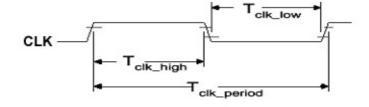

#### 5.3 CLOCKS

Figure 24: CLK Timing Diagram

Table 8: Clocks

| Parameter                    | Symbol      | Min | Тур  | Max | Units |

|------------------------------|-------------|-----|------|-----|-------|

| CLK frequency                |             | -   | 12   | -   | MHz   |

| CLK period                   | Tclk_period | -   | 83   | -   | ns    |

| CLK output jitter            |             | -   | -    | 750 | ps    |

| CLK high pulsewidth (note 1) | Tclk_high   | 36  | 41.5 | 45  | ns    |

| CLK low pulse width (note 1) | Tclk_low    | 36  | 41.5 | 45  | ns    |

Note: Worst case duty cycle restricted to 45/55.

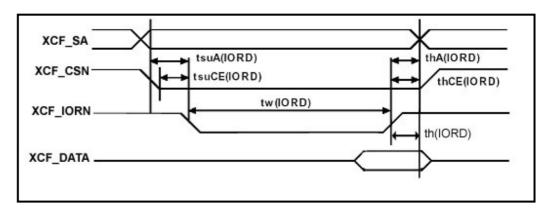

#### 5.4 CompactFlash Timing

Table 9: True IDE Mode I/O Input (Read) Timing

| Item                              | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

| Data Delay after IORD             | td(IORD)       | tIGLQV      |         | 100     |

| Data Hold following IORD          | th(IORD)       | tIGLQX      | 0       |         |

| IORD width Time                   | tw(IORD)       | tIGLIGH     | 165     |         |

| Address Setup before IORD         | tsuA(IORD)     | tAVIGL      | 70      |         |

| Address Hold following IORD       | thA(IORD)      | tIGHAX      | 20      |         |

| CE Setup before IORD              | tsuCE(IORD)    | tELIGL      | 5       |         |

| CE Hold following IORD            | thCE(IORD)     | tIGHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrIOIS16(ADR) | tAVISH      |         | 35      |

Note:The maximum load on –IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from –WAIT high to –IORD high is 0 nsec, but minimum –IORD width must still be met. Dout signifies data provided by the CompactFlash Storage Card or CF+ Card to the system.

Figure 25: True IDE Mode I/O Read Timing Diagram

| Table 10: True IDE Mode I/O Output | ut (Write | ) Timina |

|------------------------------------|-----------|----------|

|------------------------------------|-----------|----------|

| Item                              | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

| Data Setup before IOWR            | tsu(IOWR)      | tDVIWH      | 60      |         |

| Data Hold following IOWR          | th(IOWR)       | tIWHDX      | 30      |         |

| IOWR width Time                   | tw(IOWR)       | tIWLIWH     | 165     |         |

| Address Setup before IOWR         | tsuA(IOWR)     | tAVIWL      | 70      |         |

| Address Hold following IOWR       | thA(IOWR)      | tIWHAX      | 20      |         |

| CE Setup before IOWR              | tsuCE(IOWR)    | tELIWL      | 5       |         |

| CE Hold following IOWR            | thCE(IOWR)     | tIWHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrIOIS16(ADR) | tAVISH      |         | 35      |

Note:The maximum load on –IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from –WAIT high to –IOWR high is 0 nsec, but minimum –IOWR width must still be met. Din signifies data are provided by the CompactFlash Storage Card or CF+ Card to the system.

Figure 26: True IDE Mode I/O Write Timing Diagram

#### 5.5 SECURE DIGITAL Timing

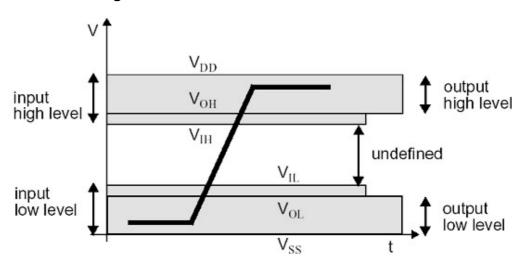

Figure 27 : SD/MMC bus signal levels

Table 11: SD/MMC bus I/O Signal Voltages

| Parameter           | Symbol | Min                   | Max.                  | Unit | Conditions                                   |

|---------------------|--------|-----------------------|-----------------------|------|----------------------------------------------|

| Output High Voltage | VOH    | 0.75*V <sub>DD</sub>  |                       | V    | 1 <sub>OH</sub> =-100μA @V <sub>DD</sub> min |

| Output Low Voltage  | VOL    |                       | 0.125*V <sub>DD</sub> | V    | 1 <sub>OL</sub> =-100μA @V <sub>DD</sub> min |

| Input High Voltage  | V1H    | 0.625*V <sub>DD</sub> | V <sub>DD</sub> +0.3  | V    |                                              |

| Input Low Voltage   | V1L    | VSS-0.3               | 0.25*V <sub>DD</sub>  | V    |                                              |

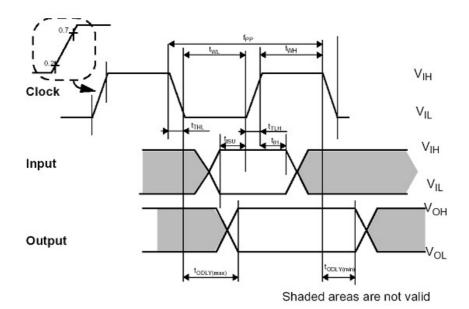

Figure 28 : Timing diagram data input/output referenced to clock

Table 12: SD/MMC Bus Timing, Parameter Value

| Parameter                               | Symbol            | Min    | Max.   | Unit | Remark                     |

|-----------------------------------------|-------------------|--------|--------|------|----------------------------|

| Clock high time                         | $t_WH$            | 50     |        | ns   | $CL \le 250 pF (21 cards)$ |

| Clock rise time                         | t <sub>TLH</sub>  |        | 50     | ns   | CL ≤ 250 pF ( 21 cards )   |

| Clock fall time                         | t <sub>THL</sub>  |        | 50     | ns   | $CL \le 250 pF (21 cards)$ |

| Inputs CMD, DAT (referenced to CLK)     |                   |        |        |      |                            |

| Input set-up time                       | t <sub>ISU</sub>  | 5      |        | ns   | CL ≤ 250 pF ( 1 cards )    |

| Input hold time                         | t <sub>IH</sub>   | 5      |        | ns   | CL ≤ 250 pF ( 1 cards )    |

| Outputs CMD, DAT (Referenced to Cl      | _K)               |        |        |      |                            |

| Output Delay time                       | t <sub>ODLY</sub> | 0      | 14     | ns   | CL ≤ 250 pF ( 1 cards )    |

| Clock CLK (All values are referred to r | min (V1H)a        | nd Max | (V1L)) |      |                            |

| Clock frequency Data Transfer Mode      | $f_{PP}$          | 2      | 25     | MHz  | CL ≤ 100 pF ( 7 cards )    |

| Clock frequency Identification Mode     |                   |        |        |      |                            |

| (The low freq. Si require for           | $f_{OD}$          | 0      | 400    | kHz  | CL ≤ 250 pF ( 21 cards )   |

| MultiMedia Card compatiblity).          |                   |        |        |      |                            |

| Clock low time                          | $t_{WL}$          | 10     |        | ns   | CL ≤ 100 pF ( 7 cards )    |

| Clock high time                         | t <sub>WN</sub>   | 10     |        | ns   | CL ≤ 100 pF ( 7 cards )    |

| Clock rise time                         | t <sub>TLH</sub>  |        | 10     | ns   | CL ≤ 100 pF ( 7 cards )    |

| Clock fall time                         | t <sub>THL</sub>  |        | 10     | ns   | CL ≤ 100 pF ( 7 cards )    |

| Clock low time                          | t <sub>WL</sub>   | 50     |        | ns   | CL ≤ 250 pF ( 21 cards )   |

# 5.6 SmartMedia Timing

#### 5.6.1 AC Characteristics

Table 13: AC Characteristics

| Symbol           | Parameter        | Min. | Max. | Unit |

|------------------|------------------|------|------|------|

| t <sub>CLS</sub> | CLE Set up Time  | 20   | -    | ns   |

| t <sub>CLH</sub> | CLE Hold Time    | 40   | -    | ns   |

| t <sub>CS</sub>  | -CE Set up Time  | 20   | -    | ns   |

| t <sub>CH</sub>  | -CE Hold Time    | 40   | -    | ns   |

| t <sub>WP</sub>  | -WE Pulse Width  | 40   | -    | ns   |

| t <sub>ALS</sub> | ALE Set up Time  | 20   | -    | ns   |

| t <sub>ALH</sub> | ALE Hold Time    | 40   | -    | ns   |

| t <sub>DS</sub>  | Data Set up Time | 30   | -    | ns   |

| Symbol             | Parameter                                   | Min. | Max. | Unit |

|--------------------|---------------------------------------------|------|------|------|

| t <sub>DH</sub>    | Data Hold Time                              | 20   | -    | ns   |

| t <sub>WC</sub>    | Write Cycle Time                            | 80   | -    | ns   |

| t <sub>WH</sub>    | -WE High Hold Time                          | 20   | -    | ns   |

| t <sub>WW</sub>    | -WE High to -WE Low                         | 100  | -    | ns   |

| t <sub>RR</sub>    | Ready to -RE Low                            | 20   | -    | ns   |

| t <sub>RP</sub>    | Read Pulse Width                            | 60   | -    | ns   |

| t <sub>RC</sub>    | Read Cycle Time                             | 80   | -    | ns   |

| t <sub>REA</sub>   | -RE Access Time(Serial Data Access)         | -    | 45   | ns   |

| t <sub>CEH</sub>   | -CE High Hold Time(at the Last Serial Read) | 250  | -    | ns   |

| t <sub>REAID</sub> | -RE Access Time(ID Read)                    | -    | 90   | ns   |

| t <sub>RHZ</sub>   | -RE High to Output Hi-Z                     | 5    | 30   | ns   |

| t <sub>CHZ</sub>   | -CE High to Output Hi-Z                     | -    | 30   | ns   |

| t <sub>REH</sub>   | -RE High Hold Time                          | 20   | -    | ns   |

| t <sub>IR</sub>    | Output Hi-Z to -RE Low                      | 0    | -    | ns   |

| t <sub>RSTO</sub>  | -RE Access Time(Status Read)                | -    | 45   | ns   |

| t <sub>CSTO</sub>  | -CE Access Time(Status Read)                | -    | 55   | ns   |

| t <sub>RHW</sub>   | -RE High to -WE Low                         | 0    | -    | ns   |

| t <sub>WHC</sub>   | -WE High to -CE Low                         | 50   | -    | ns   |

| t <sub>WHR</sub>   | -WE High to -RE Low                         | 60   | -    | ns   |

| t <sub>AR1</sub>   | ALE Low to -RE Low                          | 200  | -    | ns   |

|                    | (Address Register Read,ID Read)             |      |      |      |

| t <sub>CR</sub>    | -CE Low to -RE Low                          | 200  | -    | ns   |

|                    | (Data Register Read,ID Read)                |      |      |      |

| $t_{WB}$           | -WE High to Busy                            | -    | 200  | ns   |

| t <sub>AR2</sub>   | ALE Low to -RE Low(Read Cycle)              | 150  | -    | ns   |

| t <sub>RB</sub>    | Last -RE High to Busy(at Sequential Read)   | -    | 200  | ns   |

| t <sub>CRY</sub>   | -CE High to Ready (Note)                    | -    | 1    | μs   |

Note): The length of the period between -CE High and Ready depends on the pull-up resistance at the Ready/-Busy terminal.

#### 5.6.2 Program/Erase/Read/Reset

During programming ,erasing, reading, or resetting operations, it is necessary to monitor the Ready/Busy status. The Busy time during the execution of each operation is shown as follows.

Table 14: Parameter

| Symbol              | Parameter               |         | 1MB to 128MB |      | Unit |

|---------------------|-------------------------|---------|--------------|------|------|

|                     |                         |         | Тур.         | Max. |      |

| t <sub>PROG</sub>   | Program Time            |         | -            | 20   | ms   |

| t <sub>BERASE</sub> | Block Erase Time        |         | -            | 400  | ms   |

| t <sub>R</sub>      | Data Transfer Time      |         | -            | 100  | μs   |

|                     | (from Cell to Register) |         |              |      |      |

| t <sub>rst</sub>    | Device Resetting Time   | Program | -            | 80   | μs   |

|                     | (Program/Erase/Read)    | Erase   | -            | 6    | ms   |

|                     |                         | Read    | -            | 40   | μs   |

(Note): For details, see each company's technical data.

#### 5.7 xD Timing

#### 5.7.1 AC Characteristics

| Symbol           | Parameter                                   | Min. | Max.                      | Unit |

|------------------|---------------------------------------------|------|---------------------------|------|

| t <sub>CLS</sub> | CLE Setup Time                              | 20   | -                         | ns   |

| t <sub>CLH</sub> | CLE Hold Time                               | 40   | -                         | ns   |

| t <sub>CS</sub>  | -CE Setup Time                              | 20   | -                         | ns   |

| t <sub>CH</sub>  | -CE Hold Time                               | 40   | -                         | ns   |

| t <sub>WP</sub>  | -WE Pulse Width                             | 40   | -                         | ns   |

| t <sub>ALS</sub> | ALE Setup Time                              | 20   | -                         | ns   |

| t <sub>ALH</sub> | ALE Hold Time                               | 40   | -                         | ns   |

| t <sub>DS</sub>  | Data Setup Time                             | 30   | -                         | ns   |

| t <sub>DH</sub>  | Data Hold Time                              | 20   | -                         | ns   |

| t <sub>WC</sub>  | Write Cycle Time                            | 80   | -                         | ns   |

| t <sub>WH</sub>  | -WE High Hold Time                          | 20   | -                         | ns   |

| t <sub>WW</sub>  | -WP High to -WE Low                         | 100  | -                         | ns   |

| t <sub>RR</sub>  | Ready to -RE Low                            | 20   | -                         | ns   |

| t <sub>RP</sub>  | Read Pulse Width                            | 60   | -                         | ns   |

| t <sub>RC</sub>  | Read Cycle Time                             | 80   | -                         | ns   |

| t <sub>REA</sub> | -RE Access Time                             | -    | 45                        | ns   |

| t <sub>CEA</sub> | -CE Access Time                             | -    | 55                        | ns   |

| t <sub>CEH</sub> | -CE High Hold Time(at the Last Serial Read) | 100  | -                         | ns   |

| t <sub>OH</sub>  | Output Data Hold Time                       | 10   | -                         | ns   |

| t <sub>RHZ</sub> | -RE High to Output Hi-Z                     | -    | 30                        | ns   |

| t <sub>CHZ</sub> | -CE High to Output Hi-Z                     | -    | 20                        | ns   |

| t <sub>REH</sub> | -RE High Hold Time                          | 20   | -                         | ns   |

| t <sub>IR</sub>  | Output Hi-Z to -RE Low                      | 0    | -                         | ns   |

| t <sub>RHW</sub> | -RE High to -WE Low                         | 0    | -                         | ns   |

| t <sub>WHR</sub> | -WE High to -RE Low                         | 50   | -                         | ns   |

| t <sub>AR1</sub> | ALE Low to -RE Low(ID Read)                 | 100  | -                         | ns   |

| t <sub>AR2</sub> | ALE Low to -RE Low (Read Cycle)             | 50   | -                         | ns   |

| t <sub>CR</sub>  | -CE Low to -RE Low(ID Read)                 | 100  | -                         | ns   |

| t <sub>WB</sub>  | -WE High to Busy                            | -    | 200                       | ns   |

| t <sub>RB</sub>  | Last -RE High to Busy(at Sequential Read)   | -    | 200                       | ns   |

| t <sub>CRY</sub> | -CE High to Ready (Note)                    | -    | 6+t <sub>r</sub> (RY/-BY) | μs   |

Note: The time required to go from -CE High to Ready depends on the pull-up resistance applied to the Ready/-Busy pin.

# 5.7.2 Program/Erase/Read/Reset

| Symbol              | Parameter                                                 |         |      | Unit        |      |      |

|---------------------|-----------------------------------------------------------|---------|------|-------------|------|------|

| Symbol              |                                                           |         | Min. | Typ. (Note) | Max. | Cint |

| t <sub>PROG</sub>   | True Program Busy Time                                    |         | -    | (200)       | 1000 | μs   |

| t <sub>BERASE</sub> | Block Erase Busy Time                                     |         | -    | (2)         | 10   | ms   |

| t <sub>DBSY</sub>   | Dummy Program Busy Time during Multi<br>Block Programming |         | 0.5  | (2)         | 10   | μs   |

| t <sub>MBPBSY</sub> | Multi Block Program Busy Time                             |         | -    | (200)       | 1000 | μs   |

| t <sub>R</sub>      | Data Transfer Time<br>(from Cell to Register)             |         | -    | -           | 25   | μs   |

|                     | D ' D #' T'                                               | Program |      | -           | 20   | μs   |

|                     | Device Resetting Time<br>(Program/Erase/Read)             | Erase   | -    | -           | 0.5  | ms   |

|                     | (Flogram/Erase/Read)                                      |         | -    | -           | 6    | μs   |

Note: Details are in the suppliers data sheet.

#### 5.8 MemoryStick Timing

Table 15: ATE Test Mode Timing

| Signal | Parameter    | Stand | Unit |       |

|--------|--------------|-------|------|-------|

| Signal | Parameter    | Min   | Max  | Offic |

|        | Cycle        | 50    |      | ns    |

|        | H Pulse Time | 15    |      | ns    |

| SCLK   | L Pulse Time | 15    |      | ns    |

|        | Rise Time    |       | 10   | ns    |

|        | Fall Time    |       | 10   | ns    |

| BS     | Setup Time   | 5     |      | ns    |

|        | Hold Time    | 5     |      | ns    |

| DATA   | Setup Time   | 5     |      | ns    |

|        | Hold Time    | 5     |      | ns    |

|        | Output Delay |       | 15   | ns    |

#### 6. REFERENCES

- End of Specifications -

**C-MEDIA ELECTRONICS INC.**

6F., 100, Sec. 4, Civil Boulevard, Taipei, Taiwan 106 R.O.C.

TEL:886-2-8773-1100 FAX:886-2-8773-2211

E-mail: sales@cmedia.com.tw URL: http://www.cmedia.com.tw