# T8531/T8532 Multichannel Programmable Codec Chip Set

### **Features**

- Single 5 V power supply operation

- Per-channel programmable transmit gain

25.6 dB range, better than 0.01 dB steps

- Per-channel programmable receive gain

17.8 dB range, better than 0.01 dB steps

- Per-channel programmable hybrid balance

- Programmable termination impedances

- Programmable µ-law, A-law, or linear PCM output

- DTMF generator

- DTMF receiver

- Caller ID generator

- Call progress tones generator

- Automatic gain calibration

- Programmable time-slot assignment with bit offset

- Low-noise, balanced, receive SLIC interface

- Few or no SLIC/codec interface components required

- Analog and digital loopbacks

- Sigma-delta converters with dither noise reduction

- Serial microcontroller control interface

- Available in 64-pin MQFP and TQFP packages

### **General Description**

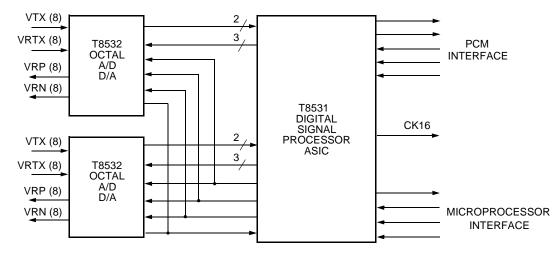

The multichannel programmable codec chip set is comprised of the T8531 16-channel line card signal processor and one or two custom T8532 octal A/D and D/A converters. A ROM-coded tone plant is included on the signal processor. Together these devices achieve a highly integrated and highly programmable multichannel voice codec solution.

Software is provided to compute the gain and filter coefficients required to program the codec.

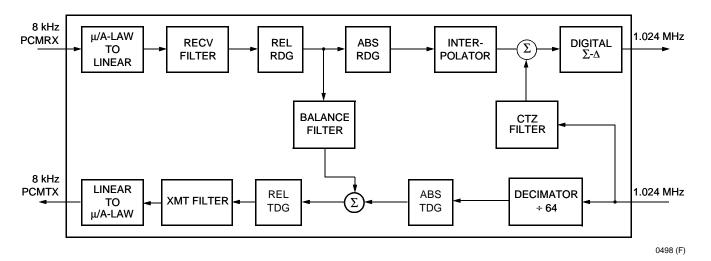

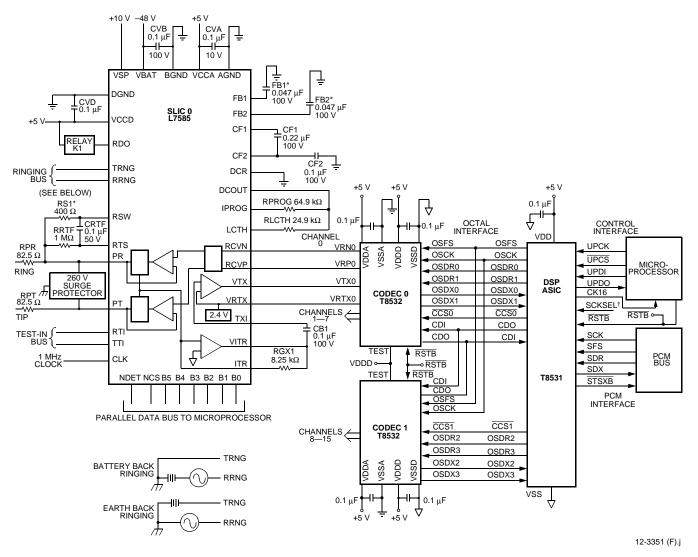

Figure 1. System Block Diagram

5-3793 (F).f

## **Table of Contents**

| Contents                                                            | Page | Contents                                        | Page |

|---------------------------------------------------------------------|------|-------------------------------------------------|------|

| eatures                                                             | 1    | T8531 Reset and Start-Up                        | 20   |

| General Description                                                 | 1    | Hardware Reset                                  | 20   |

| T8532 Description                                                   | 4    | Internal Reset                                  |      |

| T8531 Description                                                   | 5    | Reset of the T8532 Devices                      | 21   |

| Pin Information                                                     | 7    | Start-Up After Internal Reset                   | 21   |

| Chip Set Functional Description                                     |      | Autocalibration                                 |      |

| Transmit Path                                                       |      | Tone Plant                                      | 22   |

| Antialias Filter and $\Sigma$ - $\Delta$ Converter                  | 12   | DTMF Transceiver                                | 22   |

| Decimator                                                           |      | Caller Line Identification                      | 22   |

| Digital Transmit Gain Adjustment                                    | 12   | Call Progress Tones                             | 22   |

| Band Filtering                                                      |      | Absolute Maximum Ratings                        |      |

| μ-Law, A-Law, and Linear PCM Modes                                  |      | Handling Precautions                            |      |

| Receive Path                                                        |      | Electrical Characteristics                      |      |

| Receive Path Filtering                                              |      | dc Characteristics                              |      |

| Digital Receive Gain                                                |      | Transmission Characteristics                    |      |

| Interpolator and Digital Sigma-Delta                                |      | Timing Characteristics                          |      |

| Modulator                                                           | 13   | Software Interface                              |      |

| Decoder, Filters, and Receive Amplifier                             |      | Applications                                    |      |

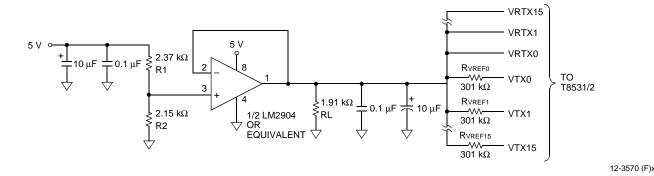

| Other Chip Set Functions                                            |      | Common Voltage Reference                        |      |

| Voltage Reference                                                   |      | Outline Diagrams                                |      |

| Hybrid Balance                                                      |      | 64-Pin MQFP                                     |      |

| Analog Termination Impedance Synthesis.                             |      | 64-Pin TQFP                                     |      |

| Digital Termination Impedance Synthesis                             |      | Ordering Information                            |      |

| Loopback Modes                                                      |      | Appendix A. Transmit Path Group Delay vs. Bit   |      |

| Interchip Control Interface                                         |      | Offset                                          | 48   |

| T8531 Functional Blocks                                             |      |                                                 |      |

| Clock Synthesizer                                                   |      |                                                 | _    |

| DSP Clock Frequency Selection                                       |      | Figures                                         | Page |

| T8531 System Interface                                              |      |                                                 |      |

| T8531 Microprocessor Interface                                      |      | Figure 1. System Block Diagram                  |      |

| T8532 Octal Control Interface                                       |      | Figure 2. Block Diagram of T8532 Octal Conve    |      |

| T8531 Time-Slot Assignment (TSA)                                    |      | Figure 3. Block Diagram of One T8532 Analog     |      |

| DSP Engine Timing                                                   |      | Channel                                         |      |

| T8531 Program Structure                                             |      | Figure 4. T8531 Block Diagram                   |      |

| Control of the DSP Engine via the                                   | 10   | Figure 5. T8531 Digital ac Path                 |      |

| <del>_</del>                                                        | 17   | Figure 6. Control, PCM, and Octal Interfaces    |      |

| Microprocessor Interface The DSP Engine Time-Slot Information       | 17   | Figure 7. T8532 64-Pin MQFP                     |      |

|                                                                     | 17   | Figure 8. T8531 64-Pin TQFP                     |      |

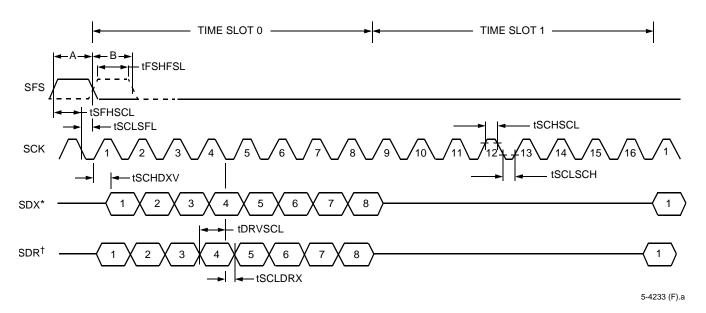

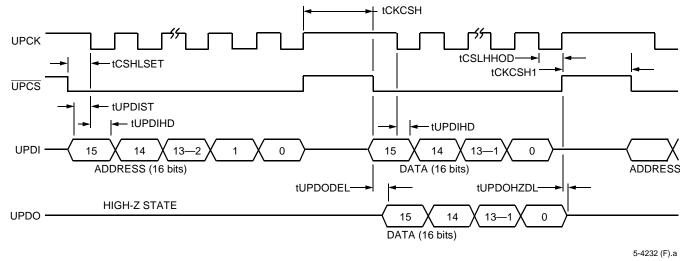

| Tables                                                              |      | Figure 9. Timing Characteristics of PCM Interfa |      |

| The DSP Engine ac Path Coefficient Table The Time-Slot Control Word |      | Assuming 2.048 MHz SCK Rate                     | 30   |

|                                                                     |      | Figure 10. Timing Diagram for Microprocessor    |      |

| Operations Performed by the DSP Engine                              |      | Write/Read to/from the DSP on the               |      |

| T8531 Start-Up                                                      |      | Control Interface                               | 31   |

| Microprocessor Start-Up of the DSP Engin                            |      | Figure 11. Line Card Solution Using the L7585   | j    |

| Powering Up a Time Slot in the T8531                                |      | SLIC                                            |      |

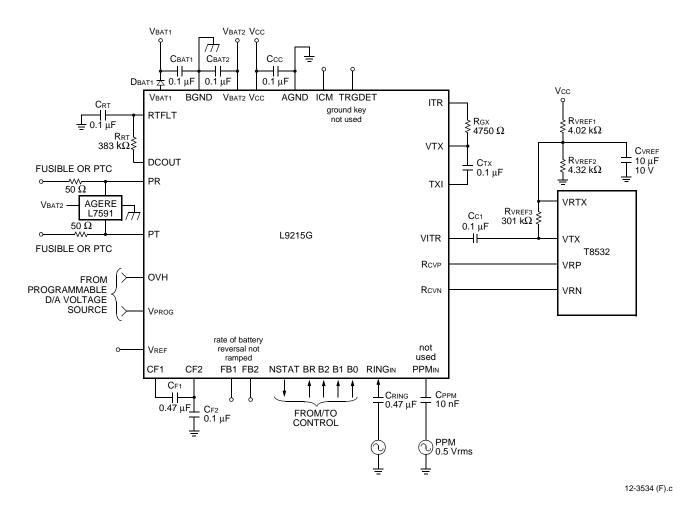

| Disabling a Time Slot in the T8531                                  |      | Figure 12. Line Card Solution Using the L9215   | iG   |

| T8532 Powerup/Powerdown                                             | 19   | SLIC                                            |      |

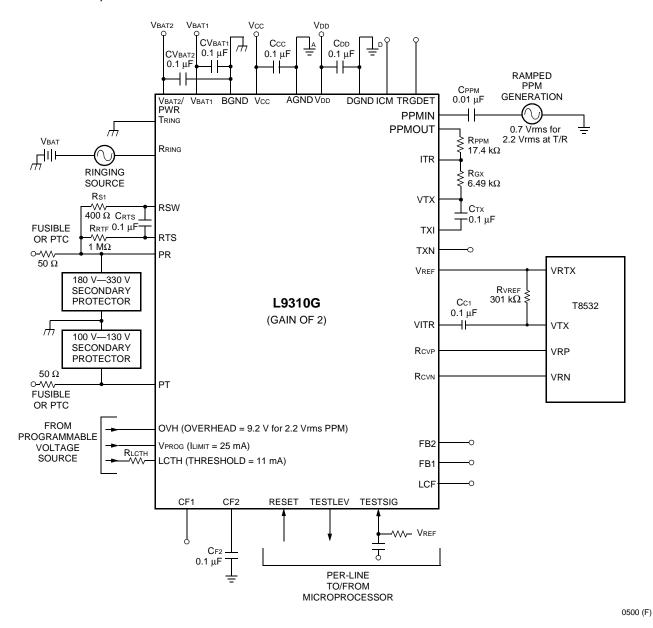

| Changing DSP RAM Space of an Active                                 |      | Figure 13. Line Card Solution Using the L9310   | )G   |

| Time Slot                                                           |      | SLIC                                            |      |

| DSP Engine Memory Requirements                                      | 20   | Figure 14. Common 2.4 V Voltage Reference.      |      |

## Table of Contents (continued)

| Tables                                        | Page  | Table 24. Bit Map for T8532 Channel Control<br>Register 1 at 0x1508—0x150F and |

|-----------------------------------------------|-------|--------------------------------------------------------------------------------|

| Table 1. T8532 Pin Descriptions               | 8     | 0x1548—0x154F36                                                                |

| Table 2. T8531 Pin Descriptions               |       | Table 25. T8532 Control Register 1: Transmit                                   |

| Table 3. Active Time-Slot Spacing in a PCM    |       | Gain36                                                                         |

| Bus Frame                                     | 15    | Table 26. T8532 Control Register 1: Analog                                     |

| Table 4. DSP Engine RAM Map for Channel_0     |       | Termination Impedance36                                                        |

| Path Coefficients                             |       | Table 27. T8532 Control Register 1: Digital                                    |

| Table 5A. Bit Map for DSP Engine Time-Slot    |       | Loopback37                                                                     |

| Control Word                                  | 18    | Table 28. Bit Map for T8532 All Channel Test                                   |

| Table 5B. Bit Map for Default Per-Board       |       | Register at 0x1510 and 0x155037                                                |

| Coefficient Tables                            | 18    | Table 29. Bits 3:0 of T8532 All Channel Test                                   |

| Table 6. DSP Engine RAM Map for Time-Slot     |       | Register at 0x1510 and 0x155037                                                |

| Information Table 0                           | 18    | Table 30. Bit Map for T8532 Channel Control                                    |

| Table 7. Summary of Microprocessor Comman     |       | Register 2 at 0x1518—0x151F and                                                |

| for Control of T8531 Data Processing          |       | 0x1558—0x155F38                                                                |

| Table 8. Digital Interface                    |       | Table 31. T8532 Control Register 2: Receive Gain38                             |

| Table 9. Analog Interface                     |       | Table 32. T8531 Control Register Map38                                         |

| Table 10. T8532 Power Dissipation             |       | Table 33. Bits 15:8 of T8531 Board Control Word 1                              |

| Table 11. T8531 Power Dissipation             |       | at 0x1FFE39                                                                    |

| Table 12. Gain and Dynamic Range              |       | Table 34. Bits 7:0 of T8531 Board Control Word 1                               |

| Table 13. Noise (per Channel)                 |       | at 0x1FFE39                                                                    |

| Table 14. Distortion and Group Delay          |       | Table 35. Bits 15:9 of T8531 Board Control Word 2                              |

| Table 15. Crosstalk                           |       | at 0x1FFC40                                                                    |

| Table 16. PCM Interface Timing                | 29    | Table 36. Bits 8:0 of T8531 Board Control Word 2                               |

| Table 17. Serial Control Port Timing          |       | at 0x1FFC40                                                                    |

| Table 18. DSP Engine RAM Memory Map           | 32    | Table 37. Bits 15:0 of T8531 Board Control Word 3                              |

| Table 19. T8531 Time-Slot Assignment Memor    | У     | at 0x1FFA40                                                                    |

| Map                                           | 34    | Table 38. Bits 15:0 of T8531 Board Control Word 4                              |

| Table 20A. Bit Map for T8531 Time-Slot Assign | nment | at 0x1FF840                                                                    |

| Registers at 0x1400—0x140F                    | 34    | Table 39. Bits 15:0 of T8531 Board Control Word 5                              |

| Table 20B. Bit Map for CTZ Disable and Null   |       | at 0x1FF640                                                                    |

| Channel                                       | 34    | Table 40. Bits 15:0 of T8531 Reset of                                          |

| Table 21. T8531 Channel Register Memory Ma    | ıp    | Microprocessor Commands at 0x7FFF40                                            |

| for T8532 Device 0                            | 35    | Table 41. DSP Engine ROM Memory Map41                                          |

| Table 22. T8531 Channel Register Memory Ma    | ıp    | Table 42. Transmit Path Group Delay vs. Bit Offset48                           |

| for T8532 Device 1                            | 35    |                                                                                |

| Table 23. Bit Map for T8532 Powerup/Powerdo   | own   |                                                                                |

| Registers at 0x1500—0x1507 and                |       |                                                                                |

| 0x1540—0x1547                                 | 35    |                                                                                |

### **General Description** (continued)

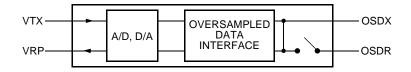

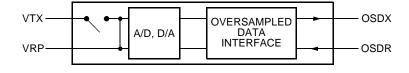

### **T8532 Description**

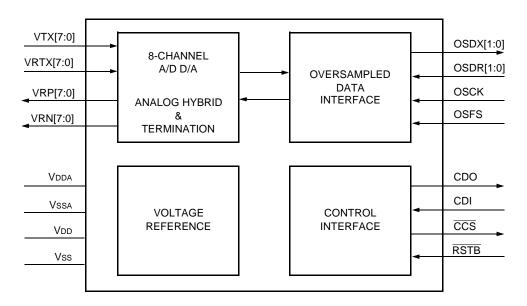

The T8532 block diagram is shown in Figure 2. Each of its eight channels consists of an antialias filter, sigma-delta A/D and D/A converters, reconstruction and smoothing filters, termination impedance synthesis, and selectable gain. The digital oversampled data is multiplexed onto a serial data port designed to interface with the T8531. Another serial interface accepts control data from the T8531 for activating the various gain settings, self-test, and powerdown modes. This chip also contains a precision voltage reference.

5-3794 (F).b

Figure 2. Block Diagram of T8532 Octal Converter

<sup>\*</sup> Antialiasing filter.

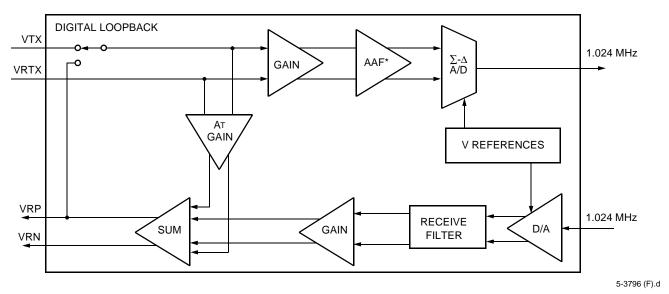

Figure 3. Block Diagram of One T8532 Analog Channel

### **General Description** (continued)

### **T8531 Description**

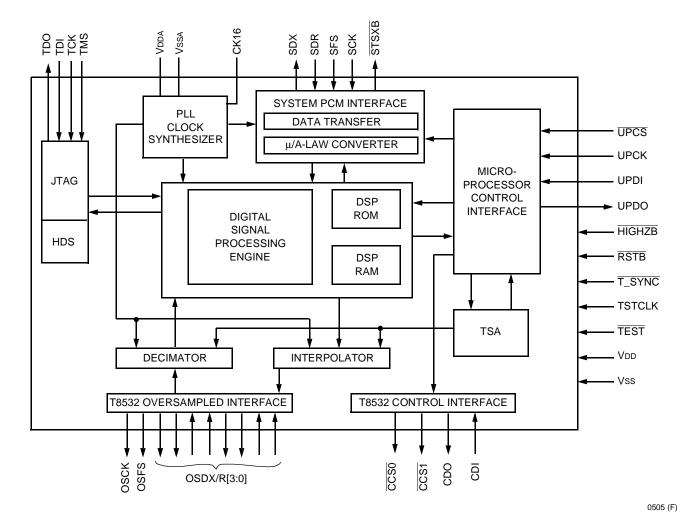

As shown in Figure 4, the T8531 contains a digital signal processor (DSP) engine surrounded by a customized input/output frame. The I/O frame performs the  $\mu$ -law or A-law conversion as well as the decimation and interpolation functions needed to interface the sigma-delta bit streams to the digital signal processor engine. The sigma-delta converters operate at a 1.024 MHz sample rate, while the signal processor operates at 16 ksamples/s. A key function of the I/O frame is to control the timing of the digital data going to the signal processor so that group delay is minimized.

The I/O frame also contains an integrated phase-locked loop which synthesizes all the required internal clocks for the chip set.

The microcontroller interface is used to run the ROM routines and to download the gain, filter, and balance network settings, powerup/powerdown commands, time-slot assignments, digital loopback settings, and commands for the T8532 octal chips.

Figure 4. T8531 Block Diagram

### **General Description** (continued)

### T8531 Description (continued)

Figure 5. T8531 Digital ac Path

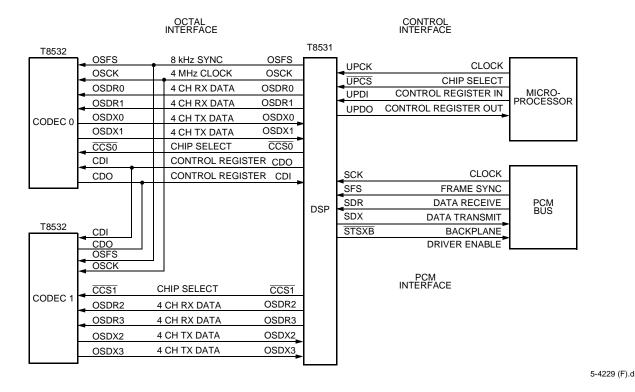

Figure 6. Control, PCM, and Octal Interfaces

### **Pin Information**

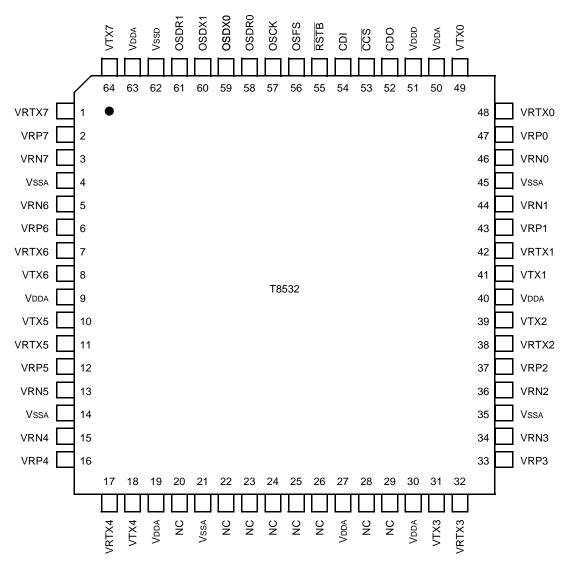

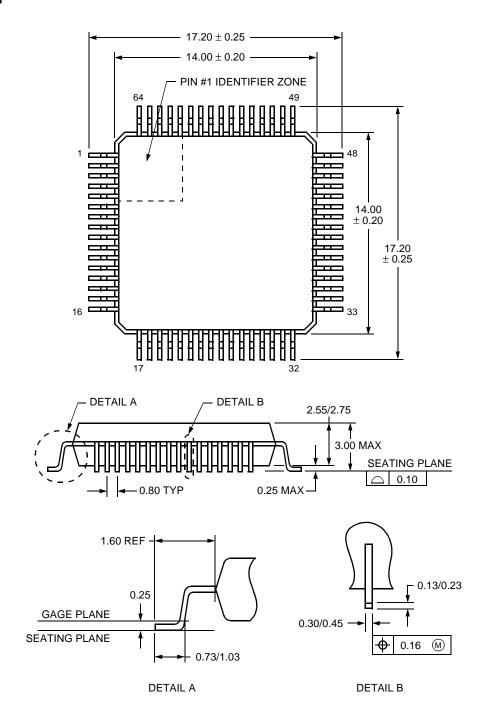

5-9214 (F)

Figure 7. T8532 64-Pin MQFP

**Table 1. T8532 Pin Descriptions**

| Number               | Name      | Туре            | Name/Function                                                                                                                                       |  |

|----------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 64, 8, 10, 18,       | VTX[7:0]  | ΑI              | Analog Input. Transmit signal voltage to be encoded.                                                                                                |  |

| 31, 39, 41, 49       |           |                 |                                                                                                                                                     |  |

| 1, 7, 11, 17, 32,    | VRTX[7:0] | ΑI              | <b>Transmit Reference Voltage.</b> 2.4 V reference. Each pin must have a sep-                                                                       |  |

| 38, 42, 48           |           |                 | arate supply associated with the corresponding VTX pin.                                                                                             |  |

| 2, 6, 12, 16, 33,    | VRP[7:0]  | AO              | Noninverting Receive Output. This pin can drive high-impedance loads                                                                                |  |

| 37, 43, 47           |           |                 | either differentially or single ended. It is the complement of the VRN output.                                                                      |  |

| 3, 5, 13, 15, 34,    | VRN[7:0]  | AO              | Inverting Receive Output. This pin can drive high-impedance loads either                                                                            |  |

| 36, 44, 46           |           |                 | differentially or single ended. It is the complement of the VRP output.                                                                             |  |

| 9, 19, 27, 30,       | Vdda      | _               | <b>5 V Analog Power Supply.</b> Power supply decoupling capacitor (0.1 μF)                                                                          |  |

| 40, 50, 63           |           |                 | should be connected from each VDDA pin to analog ground. Capacitors                                                                                 |  |

| 4 44 04              | 1/        |                 | should be located as close as possible to the device pins.                                                                                          |  |

| 4, 14, 21,<br>35, 45 | Vssa      | _               | Analog Ground.                                                                                                                                      |  |

| 51                   | VDDD      |                 | <b>5 V Digital Power Supply.</b> Decouple with a 0.1 μF capacitor to digital                                                                        |  |

|                      | *555      |                 | ground.                                                                                                                                             |  |

| 62                   | Vssd      | _               | Digital Ground.                                                                                                                                     |  |

| 60, 59               | OSDX[1:0] | CO              | Oversampled Transmit Data. Four channels of 1.024 MHz $\Sigma$ - $\Delta$ transmit                                                                  |  |

| ,                    |           |                 | data is transmitted to the T8531 through each of these pins. The data rate                                                                          |  |

|                      |           |                 | is 4.096 MHz.                                                                                                                                       |  |

| 61, 58               | OSDR[1:0] | CI              | Oversampled Receive Data. Four channels of 1.024 MHz $\Sigma$ - $\Delta$ receive                                                                    |  |

|                      |           |                 | data is received from the T8531 on each of these pins. The data rate is                                                                             |  |

|                      |           |                 | 4.096 MHz.                                                                                                                                          |  |

| 57                   | OSCK      | CI              | Interface Clock. The 4.096 MHz clock that enters this pin from the T8531                                                                            |  |

|                      |           |                 | serves as the bit clock for all the oversampled data transmission between                                                                           |  |

| 50                   | 0050      | 01              | this chip and the T8531. This is the master clock input for the T8532.                                                                              |  |

| 56                   | OSFS      | CI              | <b>Interface Frame Sync.</b> This signal serves as the frame sync for the oversampled data interface between the T8532 and the T8531.               |  |

| E A                  | CDI       | CI              | ·                                                                                                                                                   |  |

| 54                   | CDI       | CI              | <b>Control Data Interface Input.</b> The T8531 sends control register address and data to the T8532 through this pin. One address byte and one data |  |

|                      |           |                 | byte are accepted each time CCS is toggled.                                                                                                         |  |

| 52                   | CDO       | СО              | Control Data Interface Output. Control register contents are clocked out                                                                            |  |

| 02                   | 020       |                 | through this pin.                                                                                                                                   |  |

| 53                   | CCS       | CI              | Control Interface Chip Select (Active-Low). This active-low input                                                                                   |  |

|                      |           |                 | enables the control interface.                                                                                                                      |  |

| 55                   | RSTB      | TI <sup>u</sup> | Reset (Active-Low). This input must be pulled high for normal operation.                                                                            |  |

|                      |           |                 | When pulled momentarily low (at least 1 µs) while OSCK is active, all pro-                                                                          |  |

|                      |           |                 | grammable registers in the device are reset to the states specified under                                                                           |  |

| 22.22.22             | NO.       |                 | powerup initialization. This pin has an internal pull-up resistor.                                                                                  |  |

| 20, 22—26,           | NC        | _               | <b>No Connect.</b> No connection to chip. These pins can be used as logic level                                                                     |  |

| 28, 29               |           |                 | tie points.                                                                                                                                         |  |

Note: TI = TTL input, TO = TTL output; CI = CMOS input, CO = CMOS output; AI = analog input, AO = analog output; I<sup>u</sup> indicates a pull-up device is included on this lead, I<sup>d</sup> indicates a pull-down device is included on this lead.

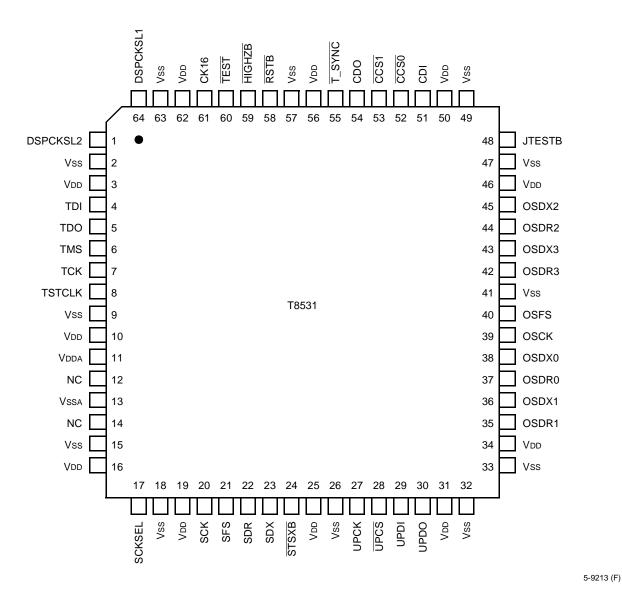

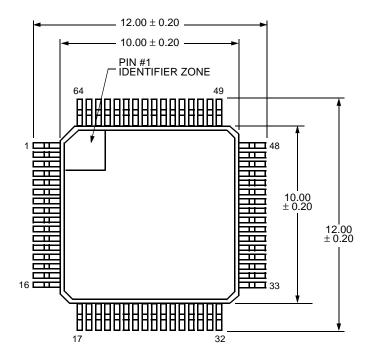

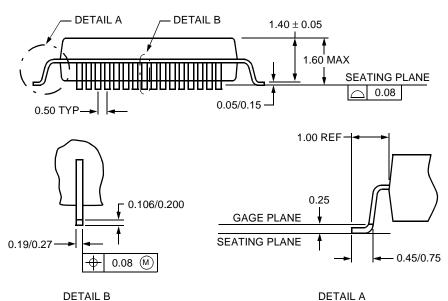

Figure 8. T8531 64-Pin TQFP

**Table 2. T8531 Pin Descriptions**

| Number            | Name      | Type            | Name/Function                                                                                                                                                                                                            |  |

|-------------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29                | UPDI      | TI              | <b>Control Data Interface Input.</b> The microcontroller sends control register address and data to the T8531 through this pin.                                                                                          |  |

| 30                | UPDO      | ТО              | <b>Control Data Interface Output.</b> The microcontroller receives control register contents from this pin. Inactive state is high impedance.                                                                            |  |

| 27                | UPCK      | TI              | <b>Control Data Interface Clock.</b> Bit clock for the control interface. Speed is limited to 4.096 MHz.                                                                                                                 |  |

| 28                | UPCS      | TI              | <b>Control Interface Chip Select (Active-Low).</b> This active-low input enables the control interface.                                                                                                                  |  |

| 43, 45,<br>36, 38 | OSDX[3:0] | CI              | Oversampled Transmit Data. Four channels of 1 Msamples/s $\Sigma$ - $\Delta$ transmit data are received from the T8532 chips through each of these pins. The data rate is 4.096 MHz.                                     |  |

| 42, 44,<br>35, 37 | OSDR[3:0] | СО              | Oversampled Receive Data. Four channels of 1 Msamples/s $\Sigma$ - $\Delta$ receive data is transmitted to the T8532 chips on each of these pins. The data rate is 4.096 MHz.                                            |  |

| 39                | OSCK      | CO              | 4.096 MHz Clock. Clock for data transfer to/from T8532 chips.                                                                                                                                                            |  |

| 40                | OSFS      | CO              | <b>Oversampling Sync.</b> 8 kHz synchronization pulse for data transfer to/from T8532 chips.                                                                                                                             |  |

| 11                | Vdda      | _               | Synthesizer VDD. Power supply for clock synthesizer block.                                                                                                                                                               |  |

| 13                | Vssa      | _               | Synthesizer Ground. Ground connection for the clock synthesizer block.                                                                                                                                                   |  |

| 24                | STSXB     | TO              | <b>Backplane Drive Enable (Active-Low).</b> Active when SDX is transmitting valid data; high impedance otherwise. This pin provides an enable signal for a backplane line driver.                                        |  |

| 20                | SCK       | Ξ               | <b>Master Clock Input.</b> This is the bit clock used to shift data into and out of th SDR and SDX pins. It is the input to the clock synthesizer and is used to generate all internal clocks. Rate is 4.096 MHz.        |  |

| 17                | SCKSEL    | TI <sup>u</sup> | <b>Master Clock Select Input.</b> A logic low selects the 2.048 MHz SCK. A logic high selects the 4.096 MHz SCK. An internal pull-up device is included, providing 4.096 MHz SCK operation with no external connections. |  |

| 22                | SDR       | TI              | <b>Receive PCM Input.</b> The data on this pin is shifted into the T8531 on the falling edges of SCK. Data is only entered for valid time slots as defined in the TSA registers.                                         |  |

Note: TI = TTL input, TO = TTL output; CI = CMOS input, CO = CMOS output; AI = analog input, AO = analog output; I<sup>u</sup> indicates a pull-up device is included on this lead.

Table 2. T8531 Pin Descriptions (continued)

| Number                                             | Name     | Туре            | Name/Function                                                                                                                                                                                                                                                 |  |

|----------------------------------------------------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23                                                 | SDX      | TO              | <b>Transmit PCM Output.</b> This pin remains in the high-impedance state except during the transmit time slots as defined in the TSA registers. Data is shifted out on the rising edge of SCK.                                                                |  |

| 21                                                 | SFS      | TI              | <b>Frame Sync.</b> Active-high pulse or square wave with an 8 kHz pulse repetition rate. The rising edge defines the start of the transmit and receive frames.                                                                                                |  |

| 54                                                 | CDO      | СО              | <b>T8532 Control Data Output</b> . Control register information for the T8532 chips. Data is valid only when either CCS0 or CCS1 is low.                                                                                                                      |  |

| 51                                                 | CDI      | TI <sup>u</sup> | T8532 Control Data Input. Control register information from the T8532 chips. Data is valid only when either CCS0 or CCS1 is low. An internal pull-up device is provided.                                                                                      |  |

| 53, 52                                             | CCS[1:0] | СО              | <b>Control Interface Chip Select (Active-Low).</b> These active-low outputs select one of the associated T8532 chips.                                                                                                                                         |  |

| 7                                                  | TCK      | Τ               | JTAG Test Port*—Common Test Clock. Rate ≤20 MHz.                                                                                                                                                                                                              |  |

| 4                                                  | TDI      | TI <sup>u</sup> | JTAG Test Port*—Serial Data Input. A pull-up device is provided.                                                                                                                                                                                              |  |

| 5                                                  | TDO      | TO              | JTAG Test Port*—Serial Data Output.                                                                                                                                                                                                                           |  |

| 6                                                  | TMS      | TI <sup>u</sup> | JTAG Test Port*—Mode Select. A pull-up device is provided.                                                                                                                                                                                                    |  |

| 48                                                 | JTESTB   | TI <sup>u</sup> | <b>JTAG Test.</b> Used for factory testing. Do not make any connection to this pin. A pull-up device is provided.                                                                                                                                             |  |

| 59                                                 | HIGHZB   | TI <sup>u</sup> | <b>3-State Control Pin (Active-Low).</b> When pulled low, the device output pins go into a high-impedance state. A pull-up device is provided.                                                                                                                |  |

| 60                                                 | TEST     | Clu             | <b>Test Mode Input (Active-Low).</b> This input allows bypass of clock synthesizer and uses TSTCLK to drive the chip. A pull-up device is provided.                                                                                                           |  |

| 61                                                 | CK16     | CO              | <b>16 MHz Clock Output.</b> 16.384 MHz clock output (50% duty cycle). Note that this clock divides down to a lower frequency (dependent upon the DSPCKSL setting) when the T8531 is in hardware reset. The frequency of CK16 is unaffected by software reset. |  |

| 8                                                  | TSTCLK   | CI              | Test Clock.                                                                                                                                                                                                                                                   |  |

| 12, 14                                             | NC       | _               | No Connect. This pin may be used as a tie point.                                                                                                                                                                                                              |  |

| 64                                                 | DSPCKSL1 | Cld             | DSP Clock Select. See DSP Clock Frequency Selection on page 14.                                                                                                                                                                                               |  |

| 1                                                  | DSPCKSL2 | Cld             | DSP Clock Select. See DSP Clock Frequency Selection on page 14.                                                                                                                                                                                               |  |

| 55                                                 | T_SYNC   | CI <sup>u</sup> | <b>Test Sync (Active-Low).</b> Used for factory testing. Do not make any connection to this pin. A pull-up device is provided.                                                                                                                                |  |

| 58                                                 | RSTB     | TI <sup>u</sup> | Reset (Active-Low). A logic low initiates reset. A pull-up device is provided.                                                                                                                                                                                |  |

| 3, 10, 16, 19,<br>25, 31, 34, 46,<br>50, 56, 62    | VDD      | _               | <b>5 V Digital Power Supply.</b> Power supply decoupling capacitors (0.1 $\mu$ F) should be connected from each VDD pin to ground. Capacitors should be located as close as possible to the device pins.                                                      |  |

| 2, 9, 15, 18, 26,<br>32, 33, 41, 47,<br>49, 57, 63 | Vss      | _               | Digital Ground.                                                                                                                                                                                                                                               |  |

$<sup>^{\</sup>ast}$  The DSP is  $\boldsymbol{not}$  configured for boundary-scan operation.

Note: TI = TTL input, TO = TTL output; CI = CMOS input, CO = CMOS output; AI = analog input, AO = analog output; I<sup>u</sup> indicates that a pull-up device is included on this lead, I<sup>d</sup> indicates that a pull-down device is included on this lead.

### **Transmit Path**

### Antialias Filter and $\Sigma$ - $\Delta$ Converter

The line interface circuit must provide a transmit signal, VTX, and a reference voltage, VRTX, which is the dc voltage of the VTX signal for that channel.

The input signal goes into a programmable-gain amplifier. The signal is then passed through an antialias filter followed by a  $\Sigma$ - $\Delta$  A/D converter. The  $\Sigma$ - $\Delta$  converter operates at 1.024 MHz. The processed output signals are multiplexed into two groups of four channels each onto output pins OSDX[1:0], each of which operates at 4.096 MHz.

A precision, on-chip voltage reference helps ensure accurate and highly stable transmission levels.

It is important to understand the difference between how the gain levels should be set in the T8532 and how these levels would be set in a standard codec. The T8532 is best thought of as a data acquisition system, not a codec. Hybrid balance, fine gain adjust, μ-law or A-law coding, filtering, and equalization are done after the A/D in the T8532 and by the DSP processor in the T8531. The analog gain adjust taps should not be used to set the absolute level at the PCM output. This can be done using the DSP gain adjust taps. The analog taps should be set so the signal at the input to the A/D converter is as close as possible to the full-scale input level of the A/D for the largest signal level that will be present at the VTX input. This optimizes the dynamic range of the A/D. The 0 dB gain tap should thus be used if the maximum signal level is in the range between 2.25 Vp-p and 3.2 Vp-p. The 3 dB tap should be used for signals with a maximum signal level in the range of 1.6 Vp-p and 2.25 Vp-p. The 6 dB tap should be used for signals with a maximum signal level in the range between 1.1 Vp-p and 1.6 Vp-p. Higher gain levels should be used for signals with smaller absolute levels.

The signal level to produce a 0 dBm0 level at the digital transmit output of the T8531 is not a fixed quantity as explained above. For a line with a complex impedance or an RX echo signal, extra headroom must be allowed and the TX signal level must be set to account for the headroom. In this specification, the largest possible 0 dBm0 level for the TX signal is assumed. This guarantees that the distortion specification will not be exceeded for all practical 0 dBm signal levels. The largest possible 0 dBm signal is one that has no headroom for TX gain equalization. For the case of 0 dB transmit gain, this level is found as:

$(3.2 \text{ V/log}^{-1} (3.15/20)) = 2.23 \text{ Vp-p.}$

This level is the worst-case 0 dBm0 level.

### Decimator

The decimator filters out the high-frequency components and down-samples to 16 kHz. It also reorders the 16 channels of transmit signals into a sequence that is determined by the time-slot assignment.

### **Digital Transmit Gain Adjustment**

The transmit absolute and relative gains are specified as 15-bit binary numbers representing their linear magnitude. These gains default to 4000 Hex. This equates to a 0 dB gain for the relative gain but equates to a 1.65 dB gain for the absolute gain. For a 0 dB gain, program the absolute gain for 34ED Hex. Gain can be varied from minus infinity dB (off) (0000 Hex) to 6 dB for relative gain or to 7.65 dB for absolute gain (7FFF Hex).

The relative gain control allows for TLP adjustment without hybrid balance or termination coefficient modification.

### **Band Filtering**

The bandpass filter in the transmit path removes power line and ringing frequencies, and eliminates most of the signal energy at 4 kHz and above. This allows the encoder to transmit the filtered signal at 8 ksamples/s, the worldwide standard.

The transmit filtering is implemented with a low-pass filter, followed by a high-pass filter. The data samples enter the filter at 16 ksamples/s. They are first low-pass filtered to 3.4 kHz. After low-pass filtering, the sampling rate is reduced to 8 ksamples/s. The samples are then high-pass filtered to 300 Hz.

The low-pass filter also serves as an equalizer for frequency response alterations. A set of equalizer coefficients that modify this filter are required for each complex termination impedance when using a voltage feed, current-sensed SLIC.

### $\mu$ -Law, A-Law, and Linear PCM Modes

In the transmit path, the 8 ksamples/s PCM signal output from the filter is processed prior to transmission over the system interface. The 16-bit linear PCM signal may be compressed according to either  $\mu\text{-law}$  or A-law, or transmitted as two consecutive 8-bit words. The selection is programmable via the microprocessor interface. Please note, when using A-law, a linear value of 0 is always encoded as 7F.

(continued)

### **Receive Path**

In the receive direction, the signal received from the system interface is converted to a 16-bit linear PCM signal.

### **Receive Path Filtering**

The 16-bit linear PCM signal is filtered and interpolated to 16 ksamples/s to meet the receive signal loss characteristics. This filter smooths the data following interpolation from 8 ksamples/s to 16 ksamples/s. The filter can also serve as an equalizer for frequency response alteration. This is required for complex termination impedance cases when using a current feed, voltage-sensed SLIC.

One of two receive filters can be used, the receive filter and the extended receive filter. The receive filter has two poles and three zeros. This filter can be used to minimize downloadable code (to use this receive filter, select the T7531x codec in the Aquarium coefficient software). The extended receive filter provides more flexibility in coefficient optimization by providing three poles and three zeros. The Aquarium coefficient software defaults to the extended receive filter when the T8531x codec is selected.

### **Digital Receive Gain**

The receive absolute and relative gains are specified as 15-bit binary numbers representing their linear magnitude. These gains default to 4000 Hex. This equates to a 0 dB gain for the relative gain but equates to a –0.211 dB gain for the absolute gain. For a 0 dB gain, program the absolute gain for 4193 Hex. Gain can be varied from minus infinity dB (0) (0000 Hex) to 6 dB for relative gain or to 5.8 dB for absolute gain (7FFF Hex).

The relative gain control allows for TLP adjustment without hybrid balance or termination coefficient modification.

### Interpolator and Digital Sigma-Delta Modulator

The sampling frequency of the receive signal from the digital gain adjustment is increased from 16 kHz to 64 kHz by the interpolator, which removes most of the high-frequency signal images above 8 kHz. The interpolator also maps each of 16 time slots to the appropriate line channel through the digital sigma-delta modulator.

The digital sigma-delta modulator converts the interpolated signal to a 1.024 MHz bit stream which is then sent to the T8532 device.

### Decoder, Filters, and Receive Amplifier

Receive data enters the T8532 on pins OSDR[1:0] at 4.096 MHz; four channels are time-division multiplexed onto each pin. The data is demultiplexed into eight individual channels. The processed signal for each channel passes through

switched-capacitor D/A and reconstruct filters, followed by a smoothing filter. A programmable gain amplifier is included, followed by an output amplifier capable of driving a 50 k $\Omega$  load to  $\pm 1.58$  V single-ended (relative to VOS) or  $\pm 3.16$  V differential at peak overload. For single-ended operation, the load must be ac coupled to VRP (or VRN).

### Other Chip Set Functions

### Voltage Reference

The T8532 has a precision on-chip voltage reference which ensures accurate and highly stable transmission levels.

### **Hybrid Balance**

The hybrid balance function is provided as a digital block in the T8531.

The T8531 implements a 9-tap FIR and a single-pole IIR digital balance filter in which a replica of the echo is digitally subtracted from the transmit plus near-end echo signal. The coefficients are user programmable on a per-line basis via the microprocessor interface.

### **Analog Termination Impedance Synthesis**

Termination impedance matching is implemented to maximize the power transfer capability at the loop interface and to minimize signal reflections between the transmit and receive paths.

The resistive component, implemented in the T8532 device, comprises a variable attenuated path between VTX and VRP. The capacitive component is implemented in the digital domain.

Analog termination impedance (ATI) is provided with 16 gain settings to match a voltage drive/current sense line interface circuit with the following characteristics:

where ZT is the termination impedance in ohms, RP is the resistance of each protection resistor (for stability RP  $\geq 50~\Omega),$  GTX is the SLIC transmit gain, GRX is the SLIC receive gain, and AT is the T8532 feedback gain. The polarity of the AT gain is positive (positive voltage swing on VTX gives a positive voltage swing on VRP). The gain values are shown in Table 26; gain tolerances are  $\pm 2\%.$  Differential receive output is assumed.

### **Digital Termination Impedance Synthesis**

The CTZ filter in the T8531 synthesizes complex termination impedances. The CTZ filter utilizes alpha and beta coefficients (board control words 4 and 5, respectively) to perform the synthesis. One set of alpha beta coefficients is required for each termination impedance and balance network.

(continued)

### Other Chip Set Functions (continued)

## **Digital Termination Impedance Synthesis** (continued)

Alpha bits [9:0] represent the RC time constant of the impedance that the filter is going to synthesize. The bits are formatted as two's complement. Alpha bits must be a nonzero value. Beta bits [7:0] represent the dc gain of the filter. Beta coefficients are also formatted as two's complement. Setting beta equal to zero turns off the CTZ function.

There is a constraint on the value of the protection resistor with regard to termination impedance synthesis and hybrid balance. For synthesis to operate properly, the combined series resistance of the tip protection resistor and the ring protection resistor must be 100  $\Omega$  or greater.

### **Loopback Modes**

There are four loopback modes in the T8532.

The first two loopback modes are controlled by the all-channel test (ACT) register. ACT bits 0 and 1 place all eight channels into loopback mode. Analog and digital loopback are described and shown in block diagram form in Table 29. Analog loopback allows one to check functionality from tip/ring up to and including the T8532. Digital loopback allows the T8531 to check T8532 functionality.

The third loopback mode is used in the autocalibration sequence (control register 2). This mode provides a loopback between a selected channel and channel four of a given T8532. The channel to be calibrated is selected via control register 1 (see Table 27). Channel four is the only channel in the T8532 that is trimmed for gain accuracy. Every other channel uses channel four as a reference and is calibrated to it during the autocalibration sequence.

The fourth loopback mode is a digital loopback mode located in control register 1. This operates like the digital loopback mode described in the notes for the ACT register (table 29). Unlike the ACT register, this digital loopback mode is selectable per channel. This loopback mode can be used to check T8532 functionality from the T8531 device. It is also used during the calibration sequence.

There is one loopback mode in the T8531. Loopback at the oversampled data interface is controlled by board control word 1. This mode allows the T8531 to test itself. When bit 0 of 0x1FFE is selected, all 16 channels of octal interface receive data (OSDRn) are looped back to the T8531 transmit inputs (OSDXn).

### **Interchip Control Interface**

The control interface is a 4-pin interface used to send control information to the T8532 from the T8531, and to read back the control register contents. The pins consist of a chip select input (CCS0/CCS1), a data input (CDI), and a data output (CDO). The transfer of control data is synchronous with the 4.096 MHz OSCK, which is also used for oversampled data transfer.

### **T8531 Functional Blocks**

### **Clock Synthesizer**

The clock synthesizer block is a phase-lock loop (PLL) circuit which takes SCK supplied by the backplane and uses it to produce the DSP engine clock. The input clock, SCK, can be 2.048 MHz or 4.096 MHz.

An on-chip clock synthesizer has the advantages shown below:

- Precludes the need for extra clocks to be fed over the backplane.

- Constrains the high-speed DSP engine clock within the device.

- Synchronizes all clocks used on the line card to the backplane clock, thus reducing board noise due to beat frequencies.

A clock generator block takes the PLL output and divides it down to produce all the lower-frequency clocks used by the T8531 and T8532.

Two pins, DSPCKSL1 (pin 64) and DSPCKSL2 (pin 1), select the DSP1627's operating clock frequency as shown below. The default frequency is 49.152 MHz (e.g., no connection to pins 1 and 64). Normal codec operations will perform at this frequency. For tone plant operation, 81.92 MHz must be used.

### **DSP Clock Frequency Selection**

| DSPCKSL2 | DSPCKSL1 | DSP Frequency (MHz) |

|----------|----------|---------------------|

| 0        | 0        | 49.152              |

| 0        | 1        | 65.536              |

| 1        | 0        | 81.920              |

| 1        | 1        | 93.304              |

(continued)

### T8531 Functional Blocks (continued)

### **T8531 System Interface**

The system interface is a full-duplex interface used for the exchange of PCM data with the system. The system is the master of this bus. No control information is transmitted over the system interface; all control instructions are routed over the microprocessor interface.

The system interface is used for all 16 lines serviced by the T8531. The PCM data rate is 8 ksamples/s/line, so the total required channel capacity is 16 x 8 = 128 Kwords/s in each direction. At the 4.096 MHz rate, each word takes 1.95  $\mu s$  to transmit interleaved with 5.86  $\mu s$  of dead time. The frame sync, SFS, is presented to the system interface at an 8 kHz rate.

A single bit clock and frame sync are used to control both the transmit and receive directions. The beginning of the first time slot in a frame is identified from the SFS input (see Figure 9). In nondelayed mode, SFS is active coincident with bit 0 of time slot 0 of the RX frame (and the TX frame if the programmed offset between TX and RX is 0). In delayed mode, SFS is active one cycle earlier.

The amount of skew or offset between the transmit and receive frames and time slots is programmable via board control word 2, 0x1FFC. The bit offset is up to a frame, i.e., up to 511 bits in 4 MHz mode. The bit offset skew takes place in the system PCM interface block.

The active transmit and receive time slots are determined by the card address. The number of time slots within a frame varies according to the rate of SCK. Only 16 time slots are ever active in a frame, as shown in Table 3.

The T8531 obtains its card address in board control word 1, 0x1FFE.

In  $\mu$ -law or A-law mode, each PCM word is only 8 bits long and occupies one time slot. In linear mode, the PCM word is 16 bits long and occupies two adjacent time slots. The MSB is the first bit clocked out in the valid time slot, and the LSB is the last bit of the following (invalid) time slot.

### **T8531 Microprocessor Interface**

This interface between the microprocessor (or other external controller) and the T8531 device carries usersupplied program variables and control and test instructions to both the T8531 and the T8532 octal converters. The external device is the master of the microprocessor interface. The interface is serial and asynchronous, and consists of four pins (UPCK, UPCS, UPDI, UPDO). The data rate is determined by the customer's choice of external device, but may not exceed 4.096 MHz. Microprocessor interface commands consist of two words, address and data. Address and data are 16 bits wide. The T8531 expects an address first. The first bit of the address word is the R/W flag, which tells the T8531 whether it must receive or send data (receive, R/W = 0; send, R/W = 1).

Addresses less than 0x1400 refer to the DSP engine RAM space. If a read from the DSP engine is required, the microprocessor interface issues a read interrupt to the DSP engine. If it's a write to the DSP engine, the microprocessor interface shifts in the data word and saves it into the data register before sending a write interrupt to the DSP engine. Once in every 7.8  $\mu s$  time segment, the DSP engine checks whether an interrupt is outstanding from the microprocessor interface block.

If so, the DSP engine reads the address register. If it's a read, the DSP engine fetches the word from RAM, places it in the data register, and shifts it out to the microprocessor. If it's a write, it puts the contents of the data register into RAM.

Table 3. Active Time-Slot Spacing in a PCM Bus Frame

| SCK Rate (MHz) | Total # of Time Slots | Card Address | Valid Time Slots | Invalid Time Slots    |

|----------------|-----------------------|--------------|------------------|-----------------------|

| 2.048          | 32                    | 0            | 0, 2, 4, 30      | 1, 3, 5, 31           |

|                |                       | 1            | 1, 3, 5, 31      | 0, 2, 4, 30           |

| 4.096          | 64                    | 0            | 0, 4, 8, 60      | 1—3, 5—7, 61—63       |

|                |                       | 1            | 1, 5, 9, 61      | 0, 2—4, 6—8, 62—63    |

|                |                       | 2            | 2, 6, 10, 62     | 0—1, 3—5, 7—9, 63     |

|                |                       | 3            | 3, 7, 11, 63     | 0—2, 4—6, 8—10, 60—62 |

(continued)

### T8531 Functional Blocks (continued)

A pause therefore exists between the external controller issuing an address and receiving a data read back. The data rate of 2.048 MHz allows 256 SCK cycles in a frame, i.e., eight address/data pairs with no pause between words. Since the DSP engine can process only one interrupt every 7.8 µs, the T8531 requires a separation between address and data on read and write instructions to the microprocessor interrupt (see Figure 10). This, in effect, requires UPCK to be gapped. Addresses ≥0x1400 refer to registers or TSA RAM external to the DSP engine. If the address word from the microprocessor is 0x1400 through 0x140F, it activates the TSA state machine. If the address word from the microprocessor is 0x1500 through 0x15FF, it activates the T8532 control state machine.

Microprocessor data and address words can be flushed out of the T8531 by addressing 0x7FFF with data word 0xFFFF (see Table 40).

#### T8532 Octal Control Interface

The two T8532 chips cannot be accessed by the micro-controller directly; the T8532's registers are all accessed via the T8531 microprocessor interface. The microprocessor communicates serially with the T8532 by simply writing or reading 16-bit address and 16-bit data. The octal control interface block translates this address and data into 8-bit address and 8-bit data needed by the T8532. The octal control interface block waits until the microprocessor interface block receives all 16 bits of the address word and determines whether this is a read or write operation by looking at bit 15. If this is a write operation for a T8532 chip, it receives another 16-bit data word.

### T8531 Time-Slot Assignment (TSA)

The TSA block contains a 16 x 6 dual-port RAM which is readable or writable via the microprocessor interface. Table 18 gives the bit map for TSA RAM words. The TSA RAM is in time-slot order, i.e., location 0x1400 is for time slot 0 and 0x1401 for time slot 1 and so on. The low 4 bits (B3—B0) indicate which of the 16 possible channel numbers is assigned to this time slot. The time-slot assignment is controlled by the microprocessor writing to address 0x1400 through 0x140F.

The TSA block also generates the control signals and flags used to synchronize the TSA, interpolator and decimator, and T8532 interface blocks. The TSA RAM is not preinitialized, so the microprocessor is required to write to all 16 locations of the TSA RAM at start-up to ensure proper operation. Twice a frame, the TSA state machine reads the entire TSA RAM from top to bottom in sequence and sends the contents of each RAM location to the interpolator as channel numbers for RX channels. The TSA state machine performs the same procedure for the decimator to provide it with the TX channel numbers. By performing TSA at the oversampled sigma-delta rate, round trip group delay is significantly minimized.

### **DSP Engine Timing**

The DSP engine processes all 16 lines every frame. In order to simplify synchronization of data exchanges, the processing frame is broken into 16 equal time segments of 7.8  $\mu s$  each. The ROM code is identical for each time segment.

Synchronization between the engine and the rest of the chip is enforced by the system interface block, which issues an interrupt every 7.8  $\mu s$ . This interrupt is the only unmasked interrupt processed by the engine. The interrupt service routine forces the ROM code to branch to the start of the processing loop.

### **T8531 Program Structure**

The DSP engine firmware performs three types of operations:

- 1. Signal processing of the ac path data.

- RAM accesses initiated by the microprocessor interface.

- 3. Data and program flow operations.

The signal processing algorithms performed by the T8531 are implemented in firmware and are held in ROM.

Many firmware parameters are user programmable via the microprocessor interface. Interrupts from the microprocessor interface are handled once every time segment (7.8  $\mu$ s), and the appropriate accesses are made to the DSP engine RAM registers.

(continued)

### **DSP Engine Timing** (continued)

## **Control of the DSP Engine via the Microprocessor Interface**

There are four types of commands that the external controlling device may issue to the DSP engine:

- 1. Downloading data to RAM.

- 2. Activating and deactivating lines.

- 3. Changing the RX and TX routine to be run.

- 4. Periodic read and/or refresh of RAM space.

All of these commands must only involve reading and writing to the DSP RAM so that the DSP engine does not have to perform test- and branch-type operations when a microprocessor interface command is received. The complete memory map for the DSP engine RAM is given in Table 18. The microprocessor interface is allowed to read any RAM location in the DSP engine and to write to specified addresses.

### The DSP Engine Time-Slot Information Tables

In the T8531, the DSP engine RAM has been set up to contain 16 tables which hold the pointers to the ac coefficients and data buffers required to process each time slot. Each table starts on a 32-word boundary and is accessed in the firmware using direct addressing instructions. Each table has an RX part and a TX part (see Table 18).

The tables are labeled 0 through 15 and are in time-slot order, i.e., table 0 is used when processing data for time slot 0. Time-slot number can vary between 0 and 15 and is used in conjunction with the card address to provide up to 64 time-slot positions on the PCM bus (see Table 3).

### The DSP Engine ac Path Coefficient Table

The microprocessor interface can control the DSP coefficients, shown in Table 4. The DSP engine RAM contains space to hold separate sets of coefficients for each channel, labeled channel\_0 through channel\_15. The coefficients are held in channel order, since they hold information that is channel specific and does not change with the time slot (see Table 18).

Table 4 shows the ac path coefficient space for channel 0.

Table 4. DSP Engine RAM Map for Channel\_0 ac Path Coefficients

| RAM<br>Address | Purpose                     | Number of Words | Initial<br>Value |

|----------------|-----------------------------|-----------------|------------------|

| rgain_rel_0    | RX path relative gain       | 1               | 1 (4000 H)       |

| Reserved       | _                           | 1               | _                |

| rgain_abs_0    | RX path absolute gain       | 1               | 1 (4000 H)       |

| tgain_abs_0    | TX path absolute gain       | 1               | 1 (4000 H)       |

| bf_coef_0      | Balance filter coefficients | 10              | Not initialized  |

| Reserved       | _                           | 1               | _                |

| tgain_rel_0    | TX path relative gain       | 1               | 1 (4000 H)       |

(continued)

### **DSP Engine Timing** (continued)

### The Time-Slot Control Word

The DSP engine works in time-slot order. The TSA function is performed by the decimator/interpolator. The DSP engine is not required to reorder the data in any way. The advantages of this approach are that the group delay introduced by the TSA function is very small, and the DSP code needed for context switching is small. When the microprocessor assigns a time slot via the TSA RAM, it also has to issue a new time-slot control word (TCW) instruction to the DSP engine to enable the time slot to link to the correct ac coefficients. The TCW contains the information shown in Tables 5A and 5B. The TCW is only looked at when a time slot is inactive. The initial setup of the TCWs assumes channel-order time-slot assignment.

## Operations Performed by the DSP Engine at T8531 Start-Up

The DSP engine performs its start-up code after it has been reset. All interrupts are disabled. First, the DSP engine computes the checksum for its ROM and RAM to verify their integrity. Next, the DSP engine walks through each time-slot information table and sets the data buffer and coefficient pointers. The DSP engine RAM is set up for channel-order time-slot assignment, i.e., table 0 points to channel\_0 and so on. The start-up settings for the Time-Slot Information Table (i.e., for time slot 0) are shown in Table 6.

The first 16 locations of RAM bank 1 hold the channel address table, where pointers to the start of the coefficient space for each channel are held. These pointers are set up during the start-up routine. Pointers to the three sets of default coefficients are also set up. The DSP engine then walks through all 16 ac coefficient tables and sets them to their initial values as shown in the previous section. The RX and TX filter coefficients (one set for all 16 lines) are taken from ROM and written to their RAM locations.

The DSP engine takes about 3 ms to execute the startup code. At the end of the code, the interrupt system is enabled and the DSP engine enters sleep mode.

Table 5A. Bit Map for DSP Engine Time-Slot Control Word

| Register Bit | Function                                 | Initial Value              |

|--------------|------------------------------------------|----------------------------|

| 0—3          | Channel Number                           | channel_(time-slot number) |

| 4            | Go to Powerup                            | 0                          |

| 5            | Modify Coefficients                      | 0                          |

| 6—7          | Use Default Per-Board Coefficient Tables | 0                          |

Table 5B. Bit Map for Default Per-Board Coefficient Tables

| Bit 7 | Bit 6 | Mode                            |

|-------|-------|---------------------------------|

| 0     | 0     | Do Not Select Default Tables    |

| 0     | 1     | Default Table 1 Coefficient Set |

| 1     | 0     | Default Table 2 Coefficient Set |

| 1     | 1     | Default Table 2 Coefficient Set |

Table 6. DSP Engine RAM Map for Time-Slot Information Table 0

| Variable     | Function                       | Initialized Address |

|--------------|--------------------------------|---------------------|

| tcw_0        | Time-slot Control Word         | See above           |

| rx_rtn_0     | Address of Receive ac Routine  | rpath_inactive      |

| tx_rtn_0     | Address of Transmit ac Routine | tpath_inactive      |

| data storage | Reserved                       | NA                  |

(continued)

### **DSP Engine Timing (continued)**

### Microprocessor Start-Up of the DSP Engine

Once the interrupt system is enabled, the DSP engine looks for a read or write interrupt from the microprocessor interface once every time segment, i.e., 16 times a frame.

If the ac coefficients for every channel are to be independently controlled, the microprocessor can write directly to the addresses of the 16 ac coefficient tables. This requires a total of 16 microprocessor commands to set up each channel, i.e., 16 frames to set up all 16 channels. Prior to activating any time slots, the microprocessor has the option of bulk downloading the coefficients to set up the ac coefficient tables.

When a channel needs to be set up and linked to its time slot, the microprocessor must send the TCW for that time slot with the modify coefficient (MC) bit (see Table 5A). The MC bit causes the inactive routine for that time slot to set pointers from that time-slot space to the channel space in RAM. The MC bit also causes the inactive routine to check the default coefficient bits of the TCW. If set, the appropriate default table coefficients are copied over to the RAM space for the channel. This mechanism allows the microprocessor to download a set of coefficients that can be used by multiple channels.

A mix-and-match approach can be used, i.e., some channels are set up with independent sets of coefficients, while other channels get a default setting.

During start-up, the microprocessor must also download the 16 TSA commands used by the TSA block to map physical channels to time slots. This is required to initialize the TSA RAM to known values. When all 16 locations have been set up, the microprocessor must send BCW2 (0x1FFC). This flags the TSA control to start normal operation.

### Powering Up a Time Slot in the T8531

Depending on the application, the microprocessor may choose to set up the ac coefficients for a channel just prior to enabling it for use. This requires 16 microprocessor commands if the coefficients must be set up from scratch, or no commands if an appropriate default set has already been set up. In either case, the microprocessor must ensure that all the TX and RX parts of a channel are set up prior to enabling the time slot.

If dynamic time-slot assignment is used, the microprocessor must next download a TSA command, which the TSA block uses to map the time slot to the required channel number.

The microprocessor must enable the time slot by setting the go to powerup bit of the TCW. This causes the DSP engine to change the TX and RX ac routine addresses to active.

A maximum of 17 commands or a minimum of one command is therefore needed to power up a channel.

### Disabling a Time Slot in the T8531

To disable a time slot, the microprocessor must send a command that sets the address of either the TX or RX ac routine to TX\_inactive and RX\_inactive, respectively.

The inactive routines come into use in the next TX or RX time segment for this time slot. Upon returning from the inactive routine, the DSP engine checks for a microprocessor interrupt and then enters sleep mode for the rest of the time segment.

### T8532 Powerup/Powerdown

Each channel can be powered up independently. There are two control register addresses that can be used to control the power for each channel. In both cases, the first bit of the address word controls the power. P = 1 for powerup, and P = 0 for powerdown.

One address is provided for each channel which controls the power (0x1508—0x150F and 0x1548—0x154F), and the address is followed by a data word which controls the other programmable functions for the same channel. A second address (0x1500—0x1507 and 0x1540—0x1547) is provided for each channel that controls only the power.

(continued)

### **DSP Engine Timing** (continued)

### **Changing DSP RAM Space of an Active Time Slot**

The microprocessor is only allowed to change four RAM locations for an active time slot:

- Relative transmit gain

- Relative receive gain

- Address of receive ac routine

- Address of transmit ac routine

Absolute gains and time-slot assignment can only be altered when the time slot is inactive. Note that the DSP engine does not check the TCW of active time slots.

Following the initial powerup, the line card is likely to be in service without being reset for as long as it continues to operate trouble-free. Therefore, the microprocessor has the option of continuously monitoring the variables it has programmed by reading them back from the DSP engine/microprocessor interface and rewriting them.

### **DSP Engine Memory Requirements**

The size of the DSP engine internal dual-port RAM is 4K x 16-bit words per DSP engine. RAM storage is used for user-programmable variables and for intermediate storage of the data being processed by the device. The RAM memory map is given in Table 18.

The on-chip ROM is used for both program and data. The DSP engine firmware is ROM based. The hardware development system code is also ROM based. The DSP engine ROM memory map is given in Table 41.

### T8531 Reset and Start-Up

The chips support both hardware and software reset.

#### **Hardware Reset**

The T8531 reset functions are handled by the reset control block. Hardware reset occurs if the board is powered up with RSTB low. Since RSTB has a Schmitt trigger buffer with an internal pull-up, a capacitor attached external to the RSTB pin causes the pin to pull high after a specified period of time. For power-on reset, the T8531 requires that this period of time be >1 ms to give the on-chip clock synthesizer block time to start producing clock edges for the T8531 and T8532 chips (although it may not have reached its final accuracy yet). Successful hardware reset of the device requires that:

- 1. The PCM bus signals SCK and SFS should be valid at the start of the 1 ms power-on reset period.

- VDD (and therefore RSTB) should have been low for at least 200 ms prior to commencing power-on reset to ensure that the JTAG controller powerup reset circuit has had time to clear the JTAG controller.

If, during normal operation, VDD falls below the defined minimum value, VDD min, the power-on reset procedure described above must be repeated.

Hardware reset occurs if RSTB is pulsed high-low-high for 1 ms during normal operation (i.e., no loss of power).

Table 7. Summary of Microprocessor Commands for Control of T8531 Data Processing

| Function Required                                                      | Number of Commands | When Issued                                 |

|------------------------------------------------------------------------|--------------------|---------------------------------------------|

| Bulk TSA register download & BCW2                                      | 17                 | Start-up                                    |

| Individual TSA register download                                       | 1                  | Prior to activating a time slot via the TCW |

| Coefficient download                                                   | 16 per channel     | Start-up or when time slot is inactive      |

| Set TCW to use/share coefficients already downloaded to default tables | 1                  | Start-up or when time slot is inactive      |

| Enable time slot via TCW (fixed TSA)                                   | 1                  | When time slot is inactive                  |

| Enable time slot via TCW (dynamic TSA)                                 | 2                  | When time slot is inactive                  |

| Disable time slot                                                      | 1                  | When time slot is active                    |

| Change gain value                                                      | 1 per gain         | Any time                                    |

(continued)

### T8531 Reset and Start-Up (continued)

### **Internal Reset**

Internal reset is defined as the process that starts when the internal reset line is brought low. This happens as a consequence of hardware (RTSB) or software (BCW1) reset. The internal reset process performs the following functions:

- The frequency synthesizer does not receive any reset signal, and is thus unaffected by reset. Following power-on reset of the T8531, the frequency synthesizer takes the mode determined by the SCKSEL pin.

- The T8531 custom logic jams all resettable latches, counters, and registers to their default values. No data is latched on any of the T8531 interfaces during internal reset.

- 3. The DSP engine is held in reset state.

- 4. The internal reset line is held low for a minimum of 18 ms to allow the frequency synthesizer to reach its final accuracy. An internal counter is started when the internal reset line goes low. It counts 80 frame sync pulses on SFS before releasing the internal reset line.

- When the internal reset line goes high and the EXM (internal) signal is held low, the DSP engine begins its start-up routine by fetching the first instruction from location 0 of the internal ROM.

- At the rising edge of the internal reset line, all the T8531 custom logic blocks commence their normal operation.

### Reset of the T8532 Devices

There are two options for reset of the T8532 chips.

The T8532s can make use of the same hardware reset pulse as the T8531. The T8531 supplies OSCK to the T8532s as soon as it is available, i.e., before the hardware reset has gone away. It is recommended that hardware reset be applied to all chips simultaneously.

Alternatively, the T8532s can be reset through software reset (Tables 21 and 22), which is generated by the external controlling device and routed to the T8532s via the T8531. This can only occur when OSCK is guaranteed to be valid, i.e., not within 10 ms of power-on hardware reset.

### **Start-Up After Internal Reset**

There is a specific sequence of microprocessor interface instructions that must be followed after internal reset in order to properly configure the T8531 and T8532s for normal operation.

- 1. If nondefault values are required, the T8531 board control word 1 (address 0x1FFE) must be updated.

- 2. The 16 TSA RAM locations must be written before 0x1FFC. CTZ must be disabled (see Table 20B).

- The all channel test register must be set for normal operation (addresses 0x1510 and 0x1550 set to 0x0004).

- The T8531 control registers must be set. All 16 channels must be powered up (addresses 0x1500—0x1507 and 0x1540—0x1547 must be set to 0x8000).

- The amplitude of the calibration sine wave must be set by writing address 0x0580 to coefficient 0xAA20, and address 0x0581 to coefficient 0xF49D.

- All 16 channels must be put into initialization mode (addresses 0x1518—0x151F and 0x1558—0x155F must be set to 0x0080).

- 7. The DSP engine RAM address 0x0002 must be set to 0x0700 to begin the first part of the T8532 calibration start-up sequence.

- After 70 ms, all 16 T8532 channels must be put into loopback mode (addresses 0x1508—0x151F and 0x1548—0x154F must be set to 0x8001).

- 9. The DSP engine RAM address 0x0002 must be set to 0x0720 to begin the second part of the T8532 calibration start-up sequence.