# **STPC® CONSUMER-II**

## X86 Core PC Compatible Information Appliance System-on-Chip

- POWERFUL x86 PROCESSOR

- 64-BIT SDRAM UMA CONTROLLER

- VGA & SVGA CRT CONTROLLER

- 135 MHz RAMDAC

- 2D GRAPHICS ENGINE

- VIDEO INPUT PORT

- VIDEO PIPELINE

- UP-SCALER

- VIDEO COLOUR SPACE CONVERTER

- CHROMA & COLOUR KEY SUPPORT

- TV OUTPUT

- THREE-LINE FLICKER FILTER

- ITU-R 601/656 SCAN CONVERTER

- NTSC / PAL COMPOSITE, RGB, S-VIDEO

- PCI MASTER / SLAVE / ARBITER

- ISA MASTER / SLAVE

- OPTIONAL 16-BIT LOCAL BUS INTERFACE

- EIDE CONTROLLER

- I C INTERFACE

- IPC

- DMA CONTROLLER

- INTERRUPT CONTROLLER

- TIMER / COUNTERS

- POWER MANAGEMENT UNIT

- JTAG IEEE1149.1

#### DESCRIPTION

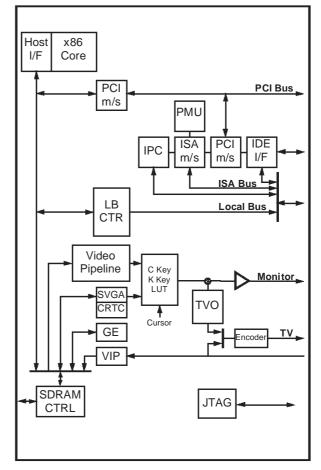

The STPC Consumer-II integrates a standard 5th generation x86 core, a Synchronous DRAM controller, a graphics subsystem, a video pipeline, and support logic including PCI, ISA, and IDE controllers to provide a single consumer orientated PC compatible subsystem on a single device.

The device is based on a tightly coupled Unified Memory Architecture (UMA), sharing memory between the CPU, the graphics and the video.

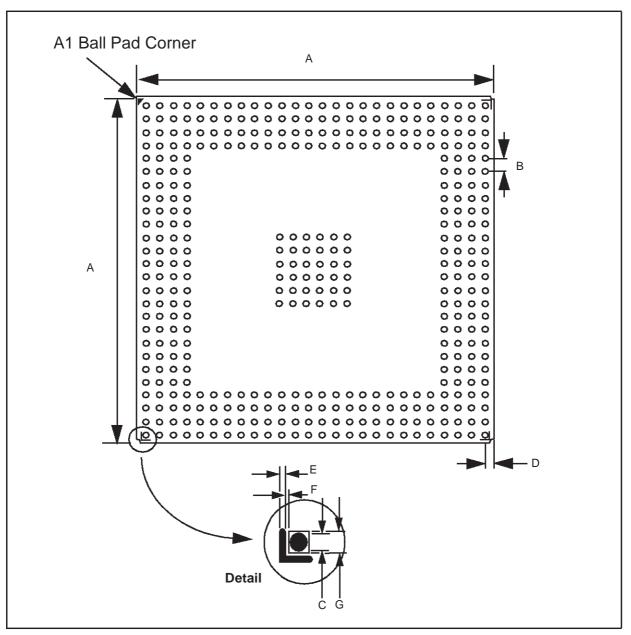

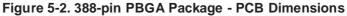

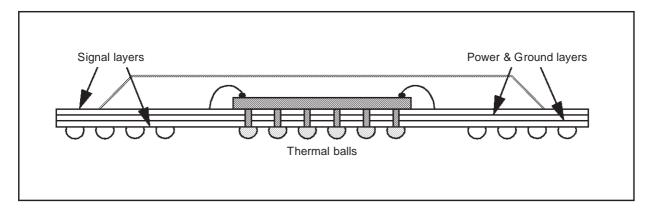

The STPC Consumer-II is packaged in a 388 Plastic Ball Grid Array (PBGA).

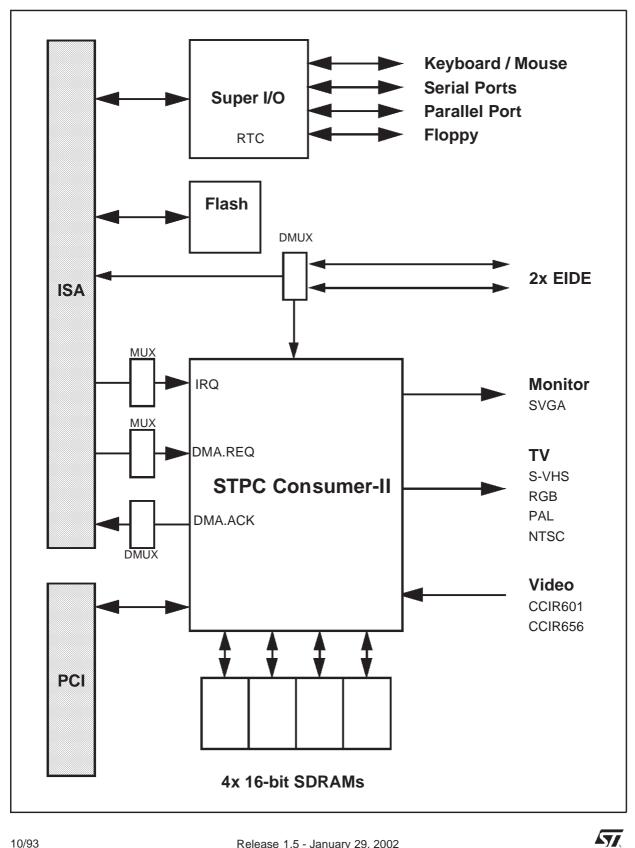

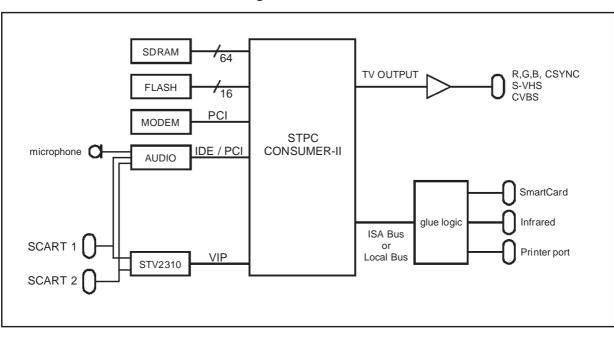

Figure 0-1. Logic Diagram

Release 1.5 - January 29, 2002

57.

## STPC<sup>®</sup> CONSUMER-II

- **X86 Processor core**

- Fully static 32-bit five-stage pipeline, x86 processor fully PC compatible.

- Can access up to 4 GB of external memory.

- 8 Kbyte unified instruction and data cache with write back and write through capability.

- Parallel processing integral floating point unit, with automatic power down.

- Runs up to 100 MHz (x1) or 133 MHz (x2).

- Fully static design for dynamic clock control.

- Low power and system management modes.

- Optimized design for 2.5 V operation.

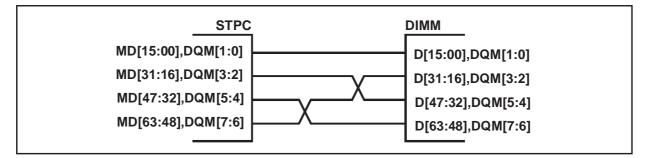

- SDRAM Controller

- 64-bit data bus.

- Up to 100 MHz SDRAM clock speed.

- Integrated system memory, graphic frame memory and video frame memory.

- Supports 2 MB up to 128 MB system memory.

- Supports 16-, 64-, and 128-Mbit SDRAMs.

- Supports 8, 16, 32, 64, and 128 MB DIMMs.

- Supports buffered, non buffered, and registered DIMMs

- Four-line write buffers for CPU to SDRAM and PCI to SDRAM cycles.

- Four-line read prefetch buffers for PCI masters.

- Programmable latency

- Programmable timing for SDRAM parameters.

- Supports -8, -10, -12, -13, -15 memory parts

- Supports memory hole between 1 MB and 8 MB for PCI/ISA busses.

- 2D Graphics Controller

- 64-bit windows accelerator.

- Backward compatibility to SVGA standards.

- Hardware acceleration for text, bitblts, transparent blts and fills.

- Up to 64 x 64 bit graphics hardware cursor.

- Up to 4MB long linear frame buffer.

- 8-, 16-, 24- and 32-bit pixels.

- Drivers availables for various OSes.

#### CRT Controller

- Integrated 135 MHz triple RAMDAC allowing for 1280 x 1024 x 75 Hz display.

- Requires external frequency synthesizer and reference sources.

- 8-bit, 16-bit, 24-bit pixels.

- Interlaced or non-interlaced output.

- Requires no external frequency synthesizer.

- Requires only external reference source.

#### Video Input port

- Accepts video inputs in ITU-R 601 mode.

- Optional 2:1 decimator

- Stores captured video in off setting area of the onboard frame buffer.

- Video pass through to the TV output for full screen video images.

- HSYNC and B/T generation or lock onto external video timing source.

#### Video Pipeline

- Two-tap interpolative horizontal filter.

- Two-tap interpolative vertical filter.

- Colour space conversion (RGB to YUV and YUV to RGB).

- Programmable window size.

- Chroma and colour keying for integrated video overlay.

#### Video Output

- NTSC-M; PAL-B, D, G, H, I, M, N encoding.

- ITU-R 601 encoding with programmable colour subcarrier frequencies.

- ITU-R 656 video output signal interface.

- Four analog outputs in two configurations:

R,G,B + CVBS

- C,YS,CVBS1 + CVBS2

- Flicker-free interlaced output.

- Programmable two tap filter with gamma correction or three tap flicker filter.

- Interlaced or non-interlaced operation mode.

- Progressive to interlaced scan converter.

- Cross colour reduction by specific trap filtering on luma within CVBS flow.

- Power down mode available on each DAC.

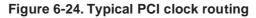

- PCI Controller

- Fully compliant with PCI 2.1 specification.

- Integrated PCI arbitration interface. Up to 3 masters can connect directly. External PAL allows for greater than 3 masters.

- Translation of PCI cycles to ISA bus.

- Translation of ISA master initiated cycle to PCI.

- Support for burst read/write from PCI master.

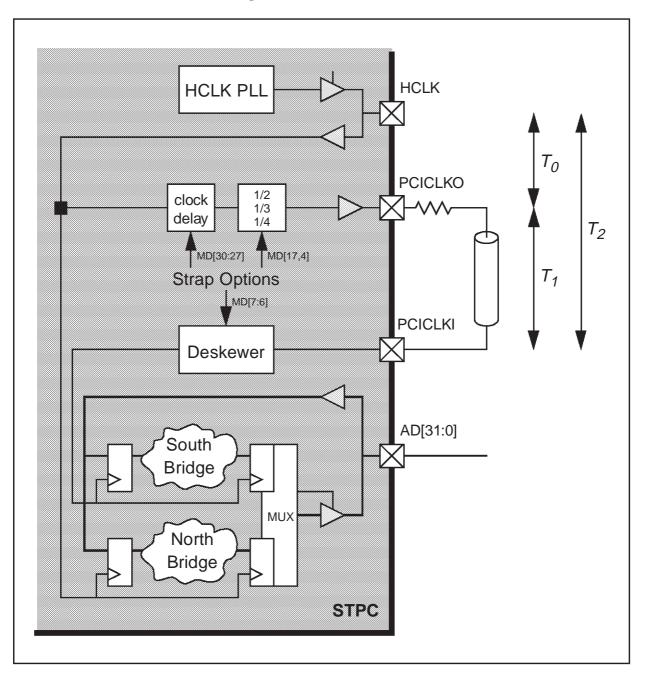

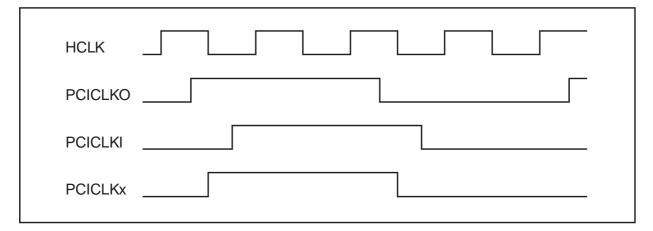

- PCI clock is 1/2, 1/3 or 1/4 cpu bus clock.

#### ISA master/slave

- Generates the ISA clock from either 14.318 MHz oscillator clock or PCI clock

- Supports programmable extra wait state for ISA cycles

- Supports I/O recovery time for back to back I/O cycles.

- Fast Gate A20 and Fast reset.

- Supports the single ROM that C, D, or E. blocks shares with F block BIOS ROM.

- Supports flash ROM.

- Supports ISA hidden refresh.

- Buffered DMA & ISA master cycles to reduce bandwidth utilization of the PCI and Host bus.

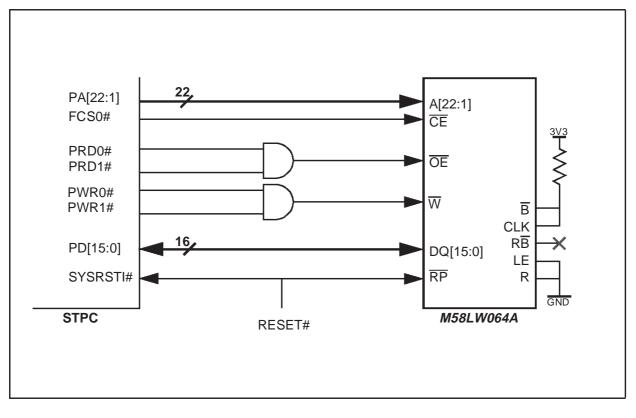

- Local Bus interface

- Multiplexed with ISA/DMA interface.

- Low latency asynchronous bus

- 22-bit address bus.

- 16-bit data bus with word steering capability.

- Programmable timing (Host clock granularity)

- Two Programmable Flash Chip Select.

- Four Programmable I/O Chip Select.

- Supports 32-bit Flash burst.

- Two-level hardware key protection for Flash boot block protection.

- Supports two banks of 16 MB flash devices with boot block shadowed to 0x000F0000.

- IDE Interface

- Supports PIO

- Transfer Rates to 22 MBytes/sec

- Supports up to 4 IDE devices

- Concurrent channel operation (PIO modes) -4 x 32-Bit Buffer FIFOs per channel

- Support for PIO mode 3 & 4.

- Individual drive timing for all four IDE devices

- Supports both legacy & native IDE modes

- Supports hard drives larger than 528MB

- Support for CD-ROM and tape peripherals

- Backward compatibility with IDE (ATA-1).

- Drivers for Windows and other Operating Systems

- Integrated Peripheral Controller

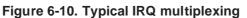

- 2X8237/AT compatible 7-channel DMA controller.

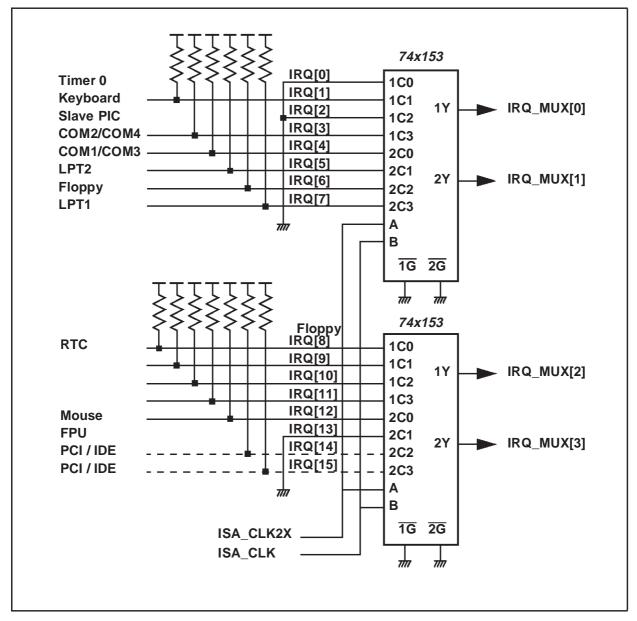

- 2X8259/AT compatible interrupt Controller.

16 interrupt inputs ISA and PCI.

- Three 8254 compatible Timer/Counters.

- Co-processor error support logic.

#### Power Management

- Four power saving modes: On, Doze, Standby, Suspend.

- Programmable system activity detector

- Supports Intel & Cyrix SMM and APM.

- Supports STOPCLK.

- Supports IO trap & restart.

- Independent peripheral time-out timer to monitor hard disk, serial & parallel port.

- 128K SM\_RAM address space from 0xA0000 to 0xB0000

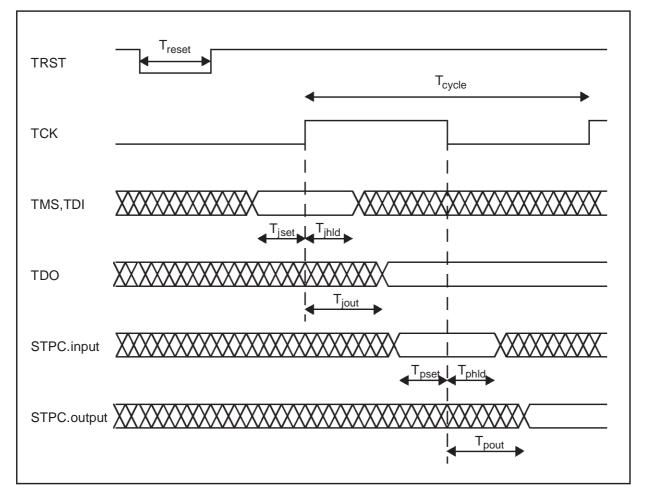

#### JTAG

- Boundary Scan compatible IEEE1149.1.

- Scan Chain control.

- Bypass register compatible IEEE1149.1.

- ID register compatible IEEE1149.1.

- RAM BIST control.

The STPC Consumer-II has undergone an errata fix upgrade. The different versions can be differenciated by the part number. Both versions are pin to pin compatible and there are some software extensions that have been added to the upgraded parts. The parts labeled STPCC5 are the upgraded parts and the differences are identified in both the Datasheet and Programming Manual. All parts labeled STPCC4 do not support the new features outlined in the documentation. Where nor C4 nor C5 are specified, the information or feature applies to both versions.

## **1. GENERAL DESCRIPTION**

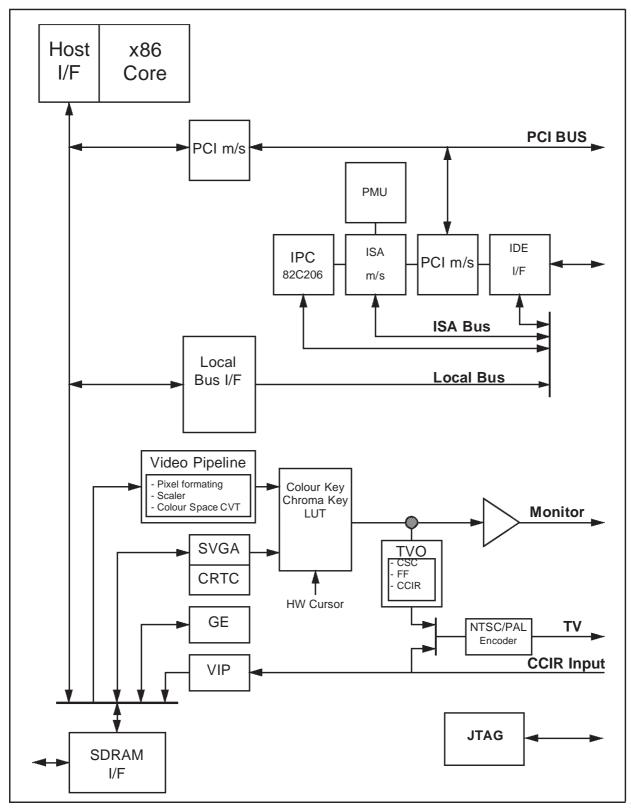

At the heart of the STPC Consumer-II is an advanced 64-bit x86 processor block. It includes a 64-bit SDRAM controller, advanced 64-bit accelerated graphics and video controller, a high speed PCI local-bus controller and Industry standard PC chip set functions (Interrupt controller, DMA Controller, Interval timer and ISA bus).

The STPC Consumer-II has in addition, an EIDE Controller, I<sup>2</sup>C Interface, a Local Bus interface and a JTAG interface.

#### 1.1. ARCHITECTURE

The STPC Consumer-II makes use of a tightly coupled Unified Memory Architecture (UMA), where the same memory array is used for CPU main memory and graphics frame-buffer. This means a reduction in total system memory for system performances that are equal to that of a comparable frame buffer and system memory based system, and generally much better, due to the higher memory bandwidth allowed by attaching the graphics engine directly to the 64-bit processor host interface running at the speed of the processor bus rather than the traditional PCI bus. The 64-bit wide memory array provides the system with 528MB/s peak bandwidth. This allows for higher resolution screens and greater color depth.

The 'standard' PC chipset functions (DMA, interrupt controller, timers, power management logic) are integrated together with the x86 processor core; additional functions such as communications ports are accessed by the STPC Consumer-II via internal ISA bus.

The PCI bus is the main data communication link to the STPC Consumer-II chip. The STPC Consumer-II translates appropriate host bus I/O and Memory cycles onto the PCI bus. It also supports generation of Configuration cycles on the PCI bus. The STPC Consumer-II, as a PCI bus agent (host bridge class), fully complies with PCI specification 2.1. The chip-set also implements the PCI mandatory header registers in Type 0 PCI configuration space for easy porting of PCI aware system BIOS. The device contains a PCI arbitration function for three external PCI devices.

The STPC Consumer-II has two functional blocks *sharing the same balls*: The ISA / IPC / IDE block and the Local Bus / IDE block (see Table 3). Any board with the STPC Consumer-II should be built using only one of these two configurations. The IDE pins are dynamically multiplexed in each of the blocks in ISA mode only.

Configuration is done by 'strap options'. It is a set of pull-up or pull-down resistors on the memory data bus, checked on reset, which auto-configure the STPC Consumer-II.

#### **1.2. GRAPHICS FEATURES**

Graphics functions are controlled through the onchip SVGA controller and the monitor display is produced through the 2D graphics display engine.

This Graphics Engine is tuned to work with the host CPU to provide a balanced graphics system with a low silicon area cost. It performs limited graphics drawing operations which include hardware acceleration of text, bitblts, transparent blts and fills. The results of these operations change the contents of the on-screen or offscreen frame buffer areas of SDRAM memory. The frame buffer can occupy a space up to 4 Mbytes anywhere in the physical main memory.

The graphics resolution supported is a maximum of 1280x1024 in 16M colors and 16M colors at 75Hz refresh rate, VGA and SVGA compatible. Horizontal timing fields are VGA compatible while the vertical fields are extended by one bit to accommodate above display resolution.

#### **1.3. VIDEO FUNCTIONS**

The STPC Consumer-II provides several additional functions to handle MPEG or similar video streams. The Video Input Port accepts an encoded digital video stream in one of a number of industry standard formats, decodes it, optionally decimates it, and deposits it into an off screen area of the frame buffer. An interrupt request can be generated when an entire field or frame has been captured. The video output pipeline incorporates a video-scaler and color space converter function and provisions in the CRT controller to display a video window. While repainting the screen the CRT controller fetches both the video as well as the normal non-video frame buffer in two separate internal FIFOs. The video stream can be color-space converted smooth scaled. (optionally) and Smooth interpolative scaling in both horizontal and vertical direction are implemented. Color and Chroma key functions are also implemented to allow mixing video stream with non-video frame buffer.

The video output passes directly to the RAMDAC for monitor output or through another optional color space converter (RGB to 4:2:2 YCrCb) to the programmable anti-flicker filter. The flicker filter is configured as either a two line filter with gamma correction (primarily designed for DOS type text) or a 3 line flicker filter (primarily designed for Windows type displays). The fliker filter is optional and can be software disabled for use with large screen area's of video.

The Video output pipeline of the STPC Consumer-II interfaces directly to the internal digital TV encoder. It takes a 24 bit RGB non-interlaced pixel stream and converts to a multiplexed 4:2:2 YCrCb 8 bit output stream, the logic includes a progressive to interlaced scan converter and logic to insert appropriate CCIR656 timing reference codes into the output stream. It facilitates the high quality display of VGA or full screen video streams received via the Video input port to standard NTSC or PAL televisions.

The digital PAL/NTSC encoder outputs interlaced or non-interlaced video in PAL-B,D,G,H,I PAL-N, PAL-M or NTSC-M standards and "NTSC- 4.43" is also possible.

The four frame (for PAL) or 2 frame (for NTSC) burst sequences are internally generated, subcarrier generation being performed numerically with CKREF as reference. Rise and fall times of synchronisation tips and burst envelope are internally controlled according to the relevant ITU-R and SMPTE recommendations.

Video output signals are directed to four analog output pins through internal D/A converters giving, simultaneous R,G,B and composite CVBS outputs.

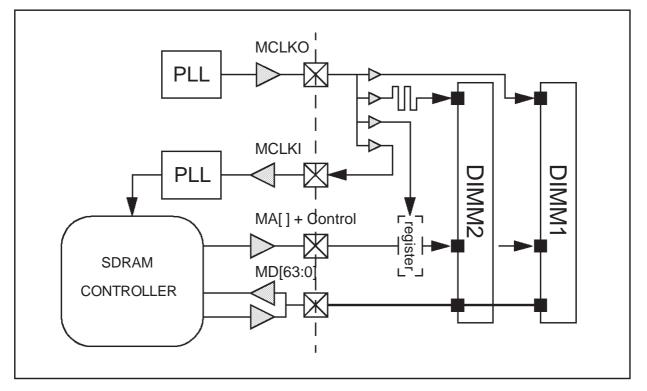

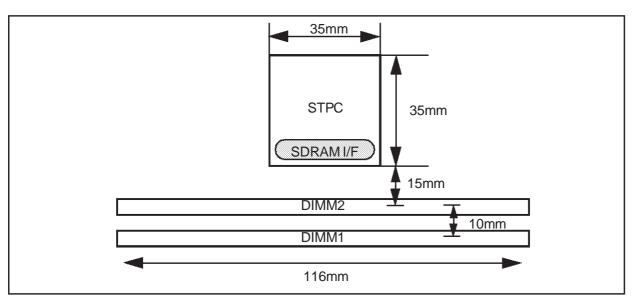

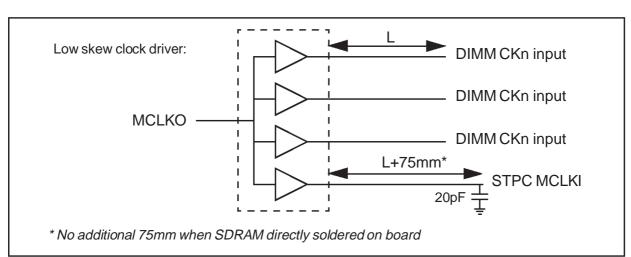

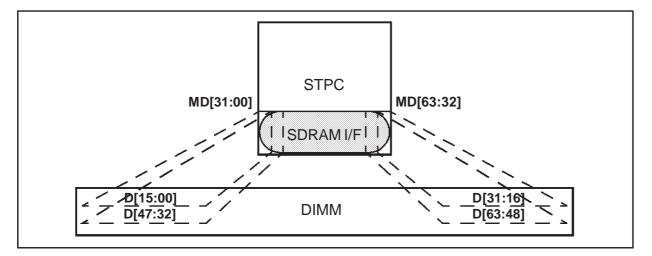

#### **1.4. MEMORY CONTROLLER**

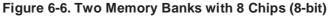

The STPC handles the memory data (DATA) bus directly, controlling from 2 to 128 MBytes. The SDRAM controller supports accesses to the Memory Banks to/from the CPU (via the host) from the VMI, to/from the CRTC, to the VIDEO & to/from the GE. (Banks 0 to 3) which can be populated with either single or double sided 72-bit (4 bit parity) DIMMs. Parity is not supported.

The SDRAM controller only supports 64 bit wide Memory Banks.

Four Memory Banks (if DIMMS are used; Single sided or two double-sided DIMMs) are supported in the following configurations (seeTable 1-1)

| Memory<br>Bank size | Number | Organisa<br>tion | Device<br>Size |

|---------------------|--------|------------------|----------------|

| 1Mx64               | 4      | 1Mx16            |                |

| 2Mx64               | 8      | 2Mx8             | 16Mbits        |

| 4Mx64               | 16     | 4Mx4             |                |

| Memory<br>Bank size | Number | Organisa<br>tion | Device<br>Size |  |

|---------------------|--------|------------------|----------------|--|

| 4Mx64               | 4      | 2Mx16x2          |                |  |

| 8Mx64               | 8      | 4Mx8x2           |                |  |

| 16Mx64              | 16     | 8Mx4x2           | 64Mbits        |  |

| 4Mx64               | 4      | 1Mx16x4          |                |  |

| 8Mx64               | 8      | 2Mx8x4           |                |  |

| 32Mx64              | 16     | 4Mx4x4           |                |  |

| 16Mx64              | 8      | 2Mx16x2          | 128Mbits       |  |

| 32Mx64              | 16     | 4Mx8x4           | I ZOIVIDIUS    |  |

The SDRAM Controller supports buffered or unbuffered SDRAM but not EDO or FPM modes. SDRAMs must support Full Page Mode Type access.

The STPC Memory Controller provides various programmable SDRAM parameters to allow the SDRAM interface to be optimized for different processor bus speeds SDRAM speed grades and CAS Latency.

#### **1.5. IDE INTERFACE**

An industry standard EIDE (ATA 2) controller is built into the STPC Consumer-II. The IDE port is capable of supporting a total of four devices.

#### **1.6. POWER MANAGEMENT**

The STPC Consumer-II core is compliant with the Advanced Power Management (APM) specification to provide a standard method by which the BIOS can control the power used by personal computers. The Power Management (PMU) power Unit module controls the consumption providing a comprehensive set of features that control the power usage and supports compliance with the United States Environmental Protection Agency's Energy Star Computer Program. The PMU provides following hardware structures to assist the software in managing the power consumption by the system.

- System Activity Detection.

- Three power down timers.

- Doze timer for detecting lack of system activity for short durations.

- Stand-by timer for detecting lack of system activity for medium durations

- Suspend timer for detecting lack of system activity for long durations.

- House-keeping activity detection.

- House-keeping timer to cope with short bursts of house-keeping activity while dozing or in standby state.

- Peripheral activity detection.

- Peripheral timer for detecting lack of peripheral activity

- SÚSP# modulation to adjust the system performance in various power down states of the system including full power on state.

- Power control outputs to disable power from different planes of the board.

Lack of system activity for progressively longer period of times is detected by the three power down timers. These timers can generate SMI interrupts to CPU so that the SMM software can put the system in decreasing states of power consumption. Alternatively, system activity in a power down state can generate SMI interrupt to allow the software to bring the system back up to full power on state. The chip-set supports up to three power down states: Doze state, Stand-by state and Suspend mode. These correspond to decreasing levels of power savings.

Power down puts the STPC Consumer-II into suspend mode. The processor completes

execution of the current instruction, any pending decoded instructions and associated bus cycles. During the suspend mode, internal clocks are stopped. Removing power down, the processor resumes instruction fetching and begins execution in the instruction stream at the point it had stopped. Because of the static nature of the core, no internal data is lost.

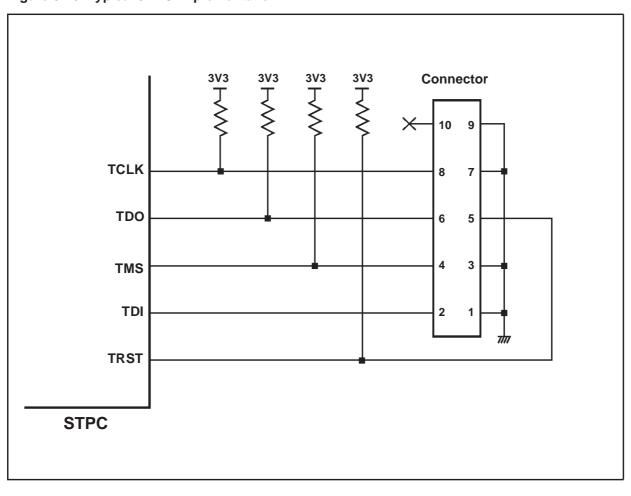

#### 1.7. JTAG

JTAG stands for Joint Test Action Group and is the popular name for IEEE Std. 1149.1, Standard Test Access Port and Boundary-Scan Architec-ture. This built-in circuitry is used to assist in the test, maintenance and support of functional circuit blocks. The circuitry includes a standard interface through which instructions and test data are communicated. A set of test features is defined, including a boundary-scan register so that a component is able to respond to a minimum set of test instructions.

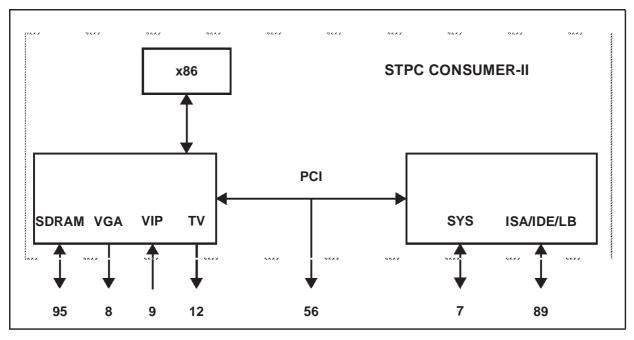

Figure 1-1. Functional description.

Release 1.5 - January 29, 2002

8/93

57

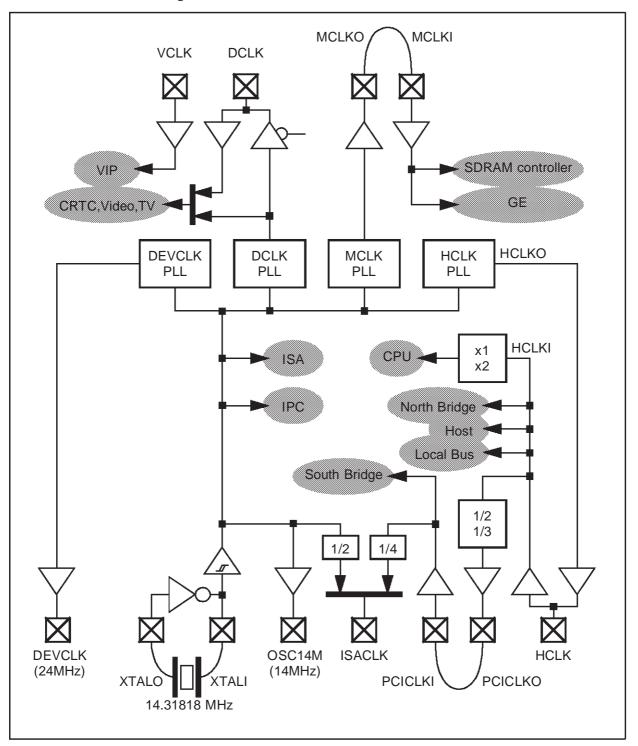

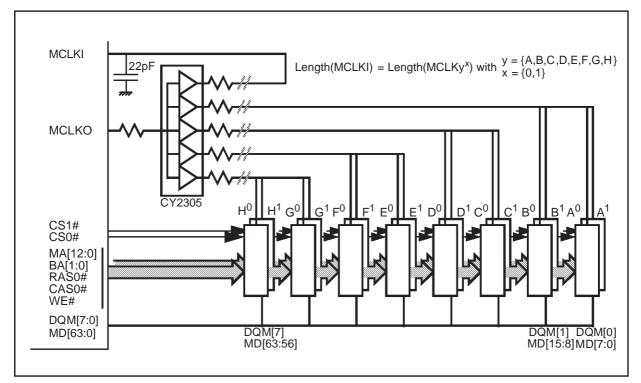

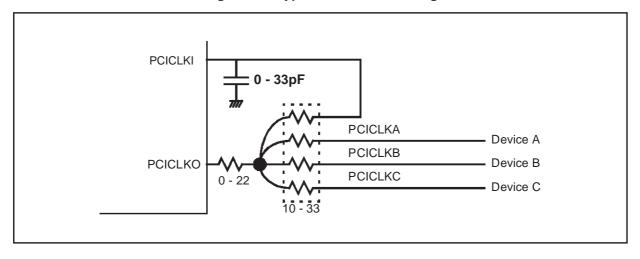

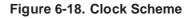

#### 1.8. CLOCK TREE

57

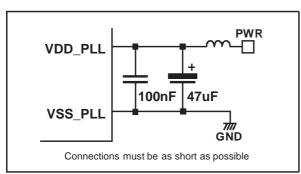

The STPC Atlas integrates many features and generates all its clocks from a single 14MHz oscillator. This results in multiple clock domains as described in Figure 1-2.

The speed of the PLLs is either fixed (DEVCLK), either programmable by strap option (HCLK) either programmable by software (DCLK, MCLK). When in synchronized mode, MCLK speed is fixed to HCLKO speed and HCLKI is generated from MCLKI.

Figure 1-2. STPC Consumer-II clock architecture

Release 1.5 - January 29, 2002

Figure 1-3. Typical ISA-based Application.

Release 1.5 - January 29, 2002

10/93

#### 2.1. INTRODUCTION

57

The STPC Consumer-II integrates most of the functionality of the PC architecture. As a result, many of the traditional interconnections between the host PC microprocessor and the peripheral devices are totally internal to the STPC Consumer-II. This offers improved performance due to the tight coupling of the processor core and these peripherals. As a result, many of the external pin connections are made directly to the on-chip peripheral functions.

Figure 2-1 shows the STPC Consumer-II external interfaces. It defines the main buses and their functions. Table 2-1 describes the physical implementation, listing signal type and functionality. Table 2-2 provides a full pin listing and description of pins. Table 2-7 provides a full listing of pin locations of the STPC Consumer-II package by physical connection.

#### Table 2-1. Signal Description

| Group name                      | ty |     |  |

|---------------------------------|----|-----|--|

| Basic Clocks reset & Xtal (SYS) | 7  |     |  |

| SDRAM Controller                | 95 |     |  |

| PCI interface                   | 56 |     |  |

| ISA                             | 79 |     |  |

| IDE                             | 34 | 89  |  |

| Local Bus                       | 49 |     |  |

| Video Input                     |    | 9   |  |

| TV Output                       |    |     |  |

| VGA Monitor interface           |    | 8   |  |

| Grounds                         |    | 71  |  |

| V <sub>DD</sub>                 | 26 |     |  |

| Miscellaneous                   | 9  |     |  |

| Unconnected                     | 6  |     |  |

| Total Pin Count                 |    | 388 |  |

Note: Several interface pins are multiplexed with other functions, refer to Table 2-4 and Table 2-5 for further details

#### Figure 2-1. STPC Consumer-II External Interfaces

| Signal Name                           | Dir | Dir Buffer Type <sup>2</sup> Description |                                                      | Qty |

|---------------------------------------|-----|------------------------------------------|------------------------------------------------------|-----|

| BASIC CLOCKS AND RESET                | S   | •                                        |                                                      |     |

| SYSRSETI#                             | 1   | SCHMITT_FT                               | System Power Good Input                              | 1   |

| SYSRSTO#                              | 0   | BD8STRP_FT                               | System Reset Output                                  |     |

| XTALI                                 | 1   | ANA                                      | 14.3 MHz Crystal Input- External<br>Oscillator Input |     |

| XTALO                                 | I/O | OSCI13B                                  | 14.3 MHz Crystal Output                              |     |

| HCLK                                  | I/O | BD4STRP_FT                               | Host Clock (Test)                                    | 1   |

| DEV_CLK                               | 0   | BT8TRP_TC                                | 24 MHz Peripheral Clock (floppy drive)               | 1   |

| DCLK                                  | I/O | BD4STRP_FT                               | 27-135 MHz Graphics Dot Clock                        | 1   |

| V <sub>DD</sub> _xxx_PLL <sup>1</sup> |     | VDDCO                                    | Power Supply for PLL Clocks                          |     |

| SDRAM CONTROLLER                      |     |                                          |                                                      |     |

| MCLKI                                 | 1   | TLCHT_TC                                 | Memory Clock Input                                   | 1   |

| MCLKO                                 | 0   | BT8TRP_TC                                | Memory Clock Output                                  | 1   |

| CS#[1:0]                              | 0   | BD8STRP_TC                               | DIMM Chip Select                                     | 2   |

| CS2# / MA11                           | 0   | BD16STARUQP_TC                           | DIMM Chip Select / Memory Address                    | 1   |

| CS3# / MA12 / BA1                     | 0   | BD16STARUQP_TC                           | DIMM Chip Select / Memory Address /<br>Bank Address  |     |

| BA[0]                                 | 0   | BD8STRP_TC                               | Bank Address                                         | 1   |

| MA[10:0]                              | 0   | BD16STARUQP_TC                           | Memory Row & Column Address                          | 12  |

| MD[63:49]                             | I/O | BD8STRUP_FT                              | Memory Data                                          | 15  |

| MD[48:1]                              | I/O | BD8TRP_TC                                | Memory Data                                          | 48  |

| MD[0]                                 | I/O | BD8STRUP_FT                              | Memory Data                                          | 1   |

| RAS#[1:0]                             | 0   | BD16STARUQP_TC                           | Row Address Strobe                                   | 2   |

| CAS#[1:0]                             | 0   | BD16STARUQP_TC                           | Column Address Strobe                                | 2   |

| MWE#                                  | 0   | BD16STARUQP_TC                           | Write Enable                                         | 1   |

| DQM[7:0]                              | 0   | BD8STRP_TC                               | Data Input/Output Mask                               | 8   |

| PCI CONTROLLER                        |     |                                          |                                                      |     |

| PCI_CLKI                              | 1   | TLCHT_FT                                 | 33 MHz PCI Input Clock                               | 1   |

| PCI_CLKO                              | 0   | BT8TRP_TC                                | 33 MHz PCI O/P Clk (from internal PLL)               | 1   |

| AD[31:0]                              | I/O | BD8PCIARP_FT                             | PCI Address / Data                                   | 32  |

| CBE[3:0]                              | I/O | BD8PCIARP_FT                             | Bus Commands / Byte Enables                          |     |

| FRAME#                                | I/O | BD8PCIARP_FT                             | Cycle Frame                                          |     |

| IRDY#                                 | I/O | BD8PCIARP_FT                             | Initiator Ready                                      | 1   |

| TRDY#                                 | I/O | BD8PCIARP_FT                             | Target Ready                                         |     |

| LOCK#                                 | 1   | TLCHT_FT                                 | PCI Lock                                             |     |

| DEVSEL#                               | I/O | BD8PCIARP_FT                             | Device Select                                        | 1   |

| STOP#                                 | I/O | BD8PCIARP_FT                             | Stop Transaction                                     | 1   |

| PAR                                   | I/O | BD8PCIARP_FT                             | Parity Signal Transactions                           | 1   |

| SERR#                                 | 0   | BD8PCIARP_FT                             | System Error                                         | 1   |

| PCIREQ#[2:0]                          | 1   | BD8PCIARP_FT                             | PCI Request                                          | 3   |

| PCIGNT#[2:0]                          | 0   | BD8PCIARP_FT                             | PCI Grant                                            | 3   |

| PCI_INT#[3:0]                         |     | BD4STRUP_FT                              | PCI Interrupt Request                                | 4   |

#### Table 2-2. Definition of Signal Pins

Note<sup>1</sup>: These pins are must be connected to the 2.5 V power supply. They **must not** be connected to the 3.3 V supply. Note<sup>2</sup>: See Table 2-3 for buffer type descriptions

57

12/93

## Table 2-2. Definition of Signal Pins

| ISA INTERFACE           ISA_CLK         O           ISA_CLK2X         O           OSC14M         O           LA[23:17]         O           SA[19:0]         I/O           SD[15:0]         I/O           ALE         O           MEMR#, MEMW#         I/O           SMEMR#, SMEMW#         O           IOR#, IOW#         I/O           MCS16#, IOCS16#         I           BHE#         O           ZWS#         I           REF#         O           MASTER#         I           AEN         O           IOCHCK#         I           IOCHCK#         I           IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RMRTCCS#         I/O           RTCRW#         I/O           RTCRW#         I/O           RTCDS#         I/O | BD8STRP_FT<br>BD4STRP_FT<br>BD8STRUP_FT<br>BD8STRP_FT                                                                                                                                                                                                                                                                                                                                                 | ISA Clock Output         Multiplexer Select Line For IPC         ISA Clock x2 Output         Multiplexer Select Line For IPC         ISA bus synchronisation clock         Unlatched Address         Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.         I/O Channel Read | 1<br>1<br>1<br>7<br>20<br>16<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1<br>1<br>1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| ISA_CLK2X       O         OSC14M       O         LA[23:17]       O         SA[19:0]       I/O         SD[15:0]       I/O         ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                                                       | BT&TRP_TC<br>BD&STRP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT                                                                                                                | Multiplexer Select Line For IPC         ISA Clock x2 Output         Multiplexer Select Line For IPC         ISA bus synchronisation clock         Unlatched Address         Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         I/O Read and Write         I/O Read and Write         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                               | 1<br>1<br>7<br>20<br>16<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                |

| ISA_CLK2X       O         OSC14M       O         LA[23:17]       O         SA[19:0]       I/O         SD[15:0]       I/O         ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                                                       | BT&TRP_TC<br>BD&STRP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT<br>BD&STRUP_FT                                                                                                                | ISA Clock x2 Output         Multiplexer Select Line For IPC         ISA bus synchronisation clock         Unlatched Address         Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         I/O Read and Write         I/O Read and Write         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                       | 1<br>1<br>7<br>20<br>16<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                |

| OSC14M         O           LA[23:17]         O           SA[19:0]         I/O           SD[15:0]         I/O           ALE         O           MEMR#, MEMW#         I/O           SMEMR#, SMEMW#         O           IOR#, IOW#         I/O           MCS16#, IOCS16#         I           BHE#         O           ZWS#         I           REF#         O           MASTER#         I           AEN         O           IOCHCK#         I           IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           RTCRW#         I/O           RTCRW#         I/O                                                                                                                  | BD8STRP_FT<br>BD8STRUP_FT<br>BD8STRUP_FT<br>BD8STRUP_FT<br>BD4STRP_FT<br>BD8STRUP_FT<br>BD8STRUP_FT<br>BD8STRUP_FT<br>BD8STRUP_FT<br>BD4STRUP_FT<br>BD4STRUP_FT<br>BD4STRUP_FT<br>BD4STRUP_FT<br>BD4STRUP_FT<br>BD4STRUP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD8STRUP_FT                                                                                                                              | Multiplexer Select Line For IPC         ISA bus synchronisation clock         Unlatched Address         Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         I/O Read and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                | 1<br>7<br>20<br>16<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                          |

| LA[23:17]       O         SA[19:0]       I/O         SD[15:0]       I/O         ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RTCAS       O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                            | BD8STRUP_FTBD8STRUP_FTBD8STRP_FTBD4STRP_FTBD8STRUP_FTBD8STRUP_FTBD8STRUP_FTBD4STRUP_FTBD4STRP_FTBD4STRP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FT                                                                                                                                             | ISA bus synchronisation clock         Unlatched Address         Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                               | 7<br>20<br>16<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                                    |

| LA[23:17]       O         SA[19:0]       I/O         SD[15:0]       I/O         ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RTCAS       O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                            | BD8STRUP_FTBD8STRUP_FTBD8STRP_FTBD4STRP_FTBD8STRUP_FTBD8STRUP_FTBD8STRUP_FTBD4STRUP_FTBD4STRP_FTBD4STRP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FT                                                                                                                                             | Unlatched Address         Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                     | 7<br>20<br>16<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                                    |

| SA[19:0]       I/O         SD[15:0]       I/O         ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RMRTCCS#       I/O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                                                                                                       | BD8STRUP_FT         BD8STRP_FT         BD4STRP_FT         BD8STRUP_FT         BD8STRUP_FT         BD8STRUP_FT         BD4STRUP_FT         BD4STRUP_FT | Latched Address         Data Bus         Address Latch Enable         Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                               | 20<br>16<br>1<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                                              |

| SD[15:0]       I/O         ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RMRTCCS#       I/O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                                                                                                    | BD8STRP_FT         BD4STRP_FT         BD8STRUP_FT         BD8STRUP_FT         BD8STRUP_FT         BD4STRUP_FT                     | Data Bus         Address Latch Enable         Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                       | 16<br>1<br>2<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                                                    |

| ALE       O         MEMR#, MEMW#       I/O         SMEMR#, SMEMW#       O         IOR#, IOW#       I/O         MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHCK#       I         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RMRTCCS#       I/O         RTCRW#       I/O         RTCRW#       I/O                                                                                                                                                                                                                                                                               | BD4STRP_FT         BD8STRUP_FT         BD8STRUP_FT         BD8STRUP_FT         BD4STRUP_FT                                        | Address Latch Enable         Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                                        | 1<br>2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                                                               |

| MEMR#, MEMW#         I/O           SMEMR#, SMEMW#         O           IOR#, IOW#         I/O           MCS16#, IOCS16#         I           BHE#         O           ZWS#         I           REF#         O           MASTER#         I           AEN         O           IOCHCK#         I           IOCHCK#         I           IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RTCAS         I/O           RTCRW#         I/O           RTCRW#         I/O                                                                                                                                                                                                                                        | BD8STRUP_FT         BD8STRUP_FT         BD8STRUP_FT         BD4STRUP_FT         BD4STRUP_FT         BD4STRP_FT         BD4STRUP_FT                                                            | Memory Read and Write         System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                                                                     | 2<br>2<br>2<br>2<br>1<br>1<br>1<br>1                                                                    |

| SMEMR#, SMEMW#         O           IOR#, IOW#         I/O           MCS16#, IOCS16#         I           BHE#         O           ZWS#         I           REF#         O           MASTER#         I           AEN         O           IOCHCK#         I           IOCHCK#         I           IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           RTCRW#         I/O           RTCRS#         I/O                                                                                                                                                                                                                                                                                                          | BD8STRP_FTBD8STRUP_FTBD4STRUP_FTBD4STRP_FTBD4STRP_FTBD4STRP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FTBD4STRUP_FT                                                                                                                                                                                                                                                                      | System MemoryRead and Write         I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                                                                                                   | 2<br>2<br>2<br>1<br>1<br>1<br>1                                                                         |

| IOR#, IOW#         I/O           MCS16#, IOCS16#         I           BHE#         O           ZWS#         I           REF#         O           MASTER#         I           AEN         O           IOCHCK#         I           IOCHCK#         I           IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           RTCRW#         I/O           RTCDS#         I/O                                                                                                                                                                                                                                                                                                           | BD8STRUP_FTBD4STRUP_FTBD8STRUP_FTBD4STRP_FTBD4STRP_FTBD4STRUP_FTBD8STRUP_FTBD8STRUP_FTBD8STRUP_FTBD8STRUP_FTBD8STRUP_FTBD4STRUP_FT                                                                                                                                                                                                                                                                    | I/O Read and Write         Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                       | 2<br>2<br>1<br>1<br>1<br>1                                                                              |

| MCS16#, IOCS16#       I         BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RMRTCCS#       I/O         RTCRW#       I/O         RTCDS#       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                              | BD4STRUP_FTBD8STRUP_FTBD4STRP_FTBD8STRP_FTBD4STRUP_FTBD8STRUP_FTBD4STRUP_FTBD8STRUP_FTBD8STRUP_FTBD4STRUP_FT                                                                                                                                                                                                                                                                                          | Memory and I/O ChipSelect16         System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                  | 2<br>1<br>1<br>1                                                                                        |

| BHE#       O         ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RMRTCCS#       I/O         RTCRW#       I/O         RTCDS#       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BD8STRUP_FT         BD4STRP_FT         BD8STRUP_FT         BD4STRUP_FT         BD8STRUP_FT         BD4STRUP_FT         BD8STRUP_FT         BD8STRUP_FT         BD8STRUP_FT         BD4STRUP_FT                                                                                                                                                                                                        | System Bus High Enable         Zero Wait State         Refresh Cycle.         Add On Card Owns Bus         Address Enable         I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1<br>1<br>1                                                                                             |

| ZWS#       I         REF#       O         MASTER#       I         AEN       O         IOCHCK#       I         IOCHRDY       I/O         ISAOE#       O         GPIOCS#       I/O         IRQ_MUX[3:0]       I         DREQ_MUX[1:0]       I         DACK_ENC[2:0]       O         TC       O         RTCAS       O         RMRTCCS#       I/O         RTCRW#       I/O         RTCDS#       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BD4STRP_FT<br>BD8STRP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRUP_FT                                                                                                                                                                                                                                                                                                   | Zero Wait State<br>Refresh Cycle.<br>Add On Card Owns Bus<br>Address Enable<br>I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                       |

| REF#         O           MASTER#         I           AEN         O           IOCHCK#         I           IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           RTCRW#         I/O           RTCDS#         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BD8STRP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRP_FT                                                                                                                                                                                                                                                                                                                  | Refresh Cycle.<br>Add On Card Owns Bus<br>Address Enable<br>I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                       |

| MASTER#IAENOIOCHCK#IIOCHRDYI/OISAOE#OGPIOCS#I/OIRQ_MUX[3:0]IDREQ_MUX[1:0]IDACK_ENC[2:0]OTCORTCASORMRTCCS#I/OKBCS#I/ORTCRW#I/ORTCDS#I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRP_FT                                                                                                                                                                                                                                                                                                                                | Add On Card Owns Bus<br>Address Enable<br>I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                         |

| AENOIOCHCK#IIOCHRDYI/OISAOE#OGPIOCS#I/OIRQ_MUX[3:0]IDREQ_MUX[1:0]IDACK_ENC[2:0]OTCORTCASORMRTCCS#I/ORTCRW#I/ORTCDS#I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BD8STRUP_FT<br>BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRP_FT                                                                                                                                                                                                                                                                                                                                               | Address Enable<br>I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                         |

| IOCHCK# I<br>IOCHRDY I/O<br>ISAOE# O<br>GPIOCS# I/O<br>IRQ_MUX[3:0] I<br>DREQ_MUX[1:0] I<br>DACK_ENC[2:0] O<br>TC O<br>RTCAS O<br>RMRTCCS# I/O<br>RMRTCCS# I/O<br>RTCRW# I/O<br>RTCRW# I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BD4STRUP_FT<br>BD8STRUP_FT<br>BD4STRP_FT                                                                                                                                                                                                                                                                                                                                                              | I/O Channel Check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                       |

| IOCHRDY         I/O           ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           RTCRW#         I/O           RTCDS#         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BD8STRUP_FT<br>BD4STRP_FT                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                       |

| ISAOE#         O           GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           KBCS#         I/O           RTCRW#         I/O           RTCDS#         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BD4STRP_FT                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                       |

| GPIOCS#         I/O           IRQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           KBCS#         I/O           RTCRW#         I/O           RTCDS#         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                       | ISA/IDE Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                       |

| RQ_MUX[3:0]         I           DREQ_MUX[1:0]         I           DACK_ENC[2:0]         O           TC         O           RTCAS         O           RMRTCCS#         I/O           KBCS#         I/O           RTCRW#         I/O           RTCDS#         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                       | General Purpose Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                       |

| DREQ_MUX[1:0] I<br>DACK_ENC[2:0] O<br>TC O<br>RTCAS O<br>RMRTCCS# I/O<br>KBCS# I/O<br>RTCRW# I/O<br>RTCRW# I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BD4STRP_FT                                                                                                                                                                                                                                                                                                                                                                                            | Time-Multiplexed Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                                       |

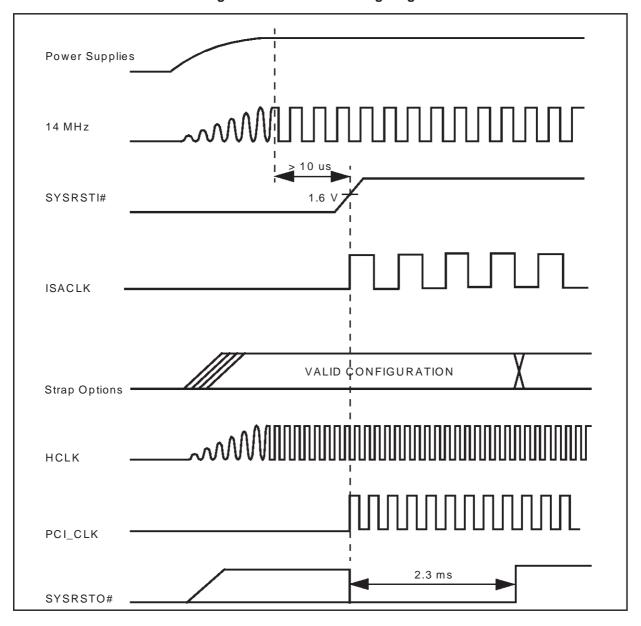

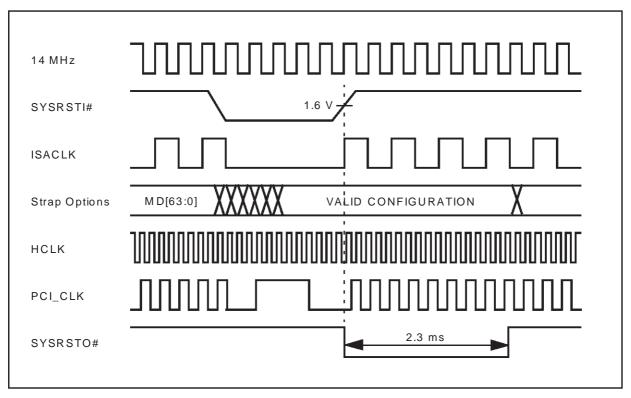

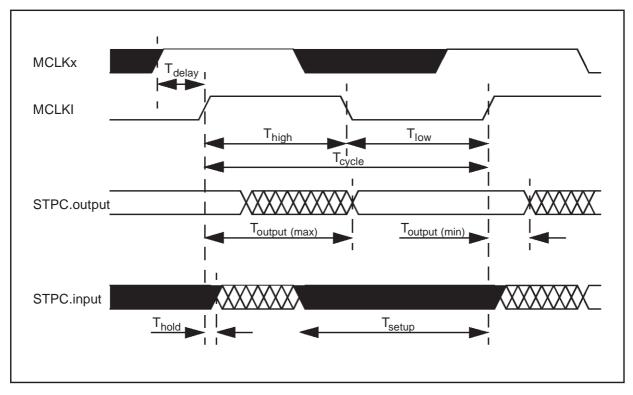

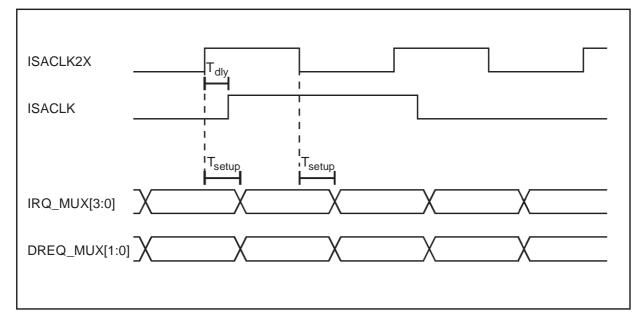

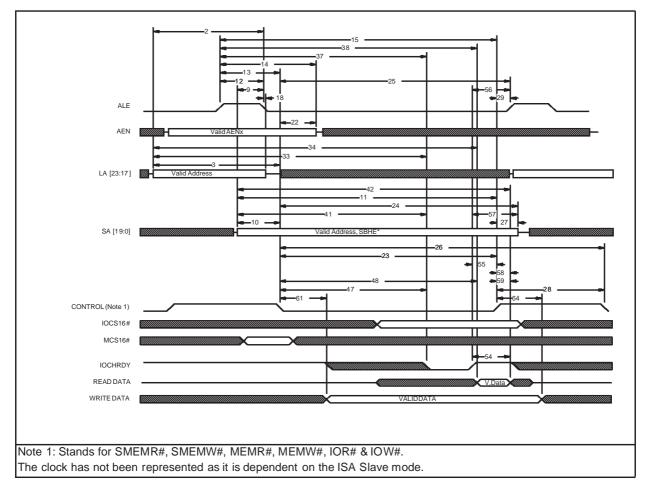

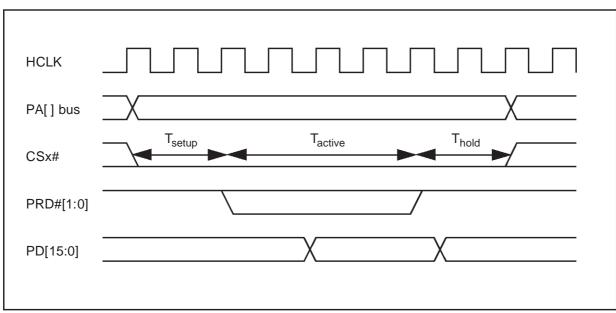

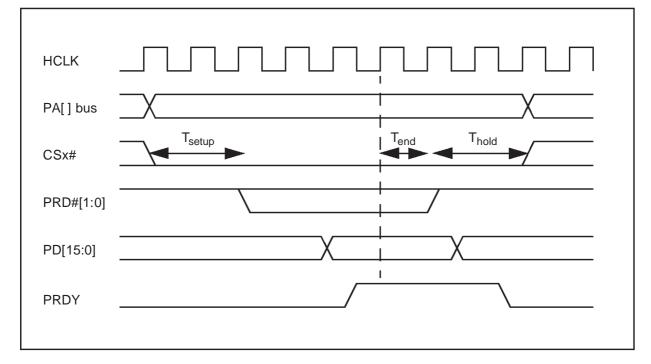

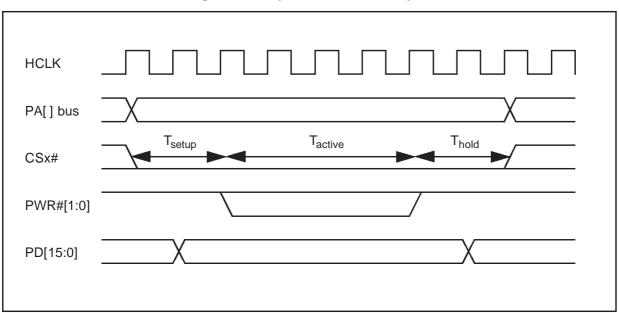

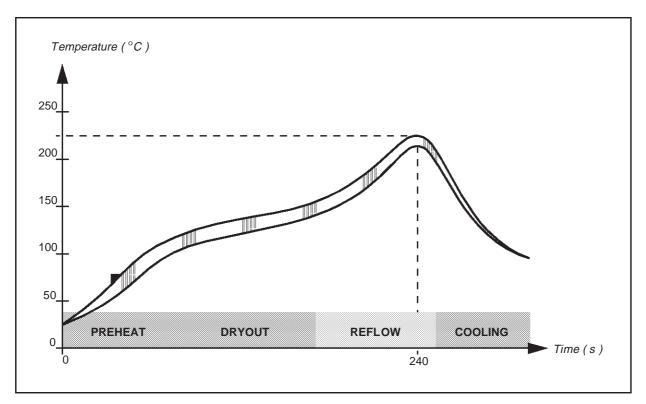

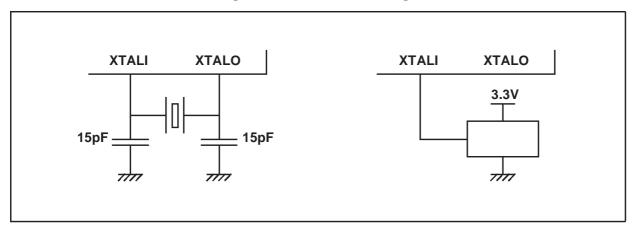

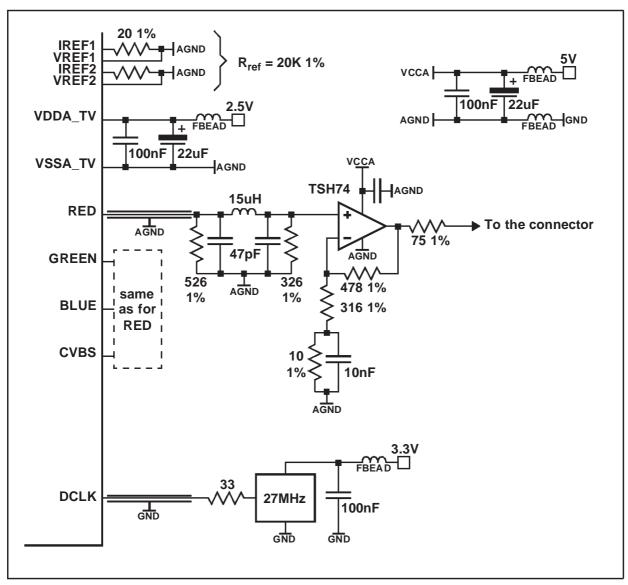

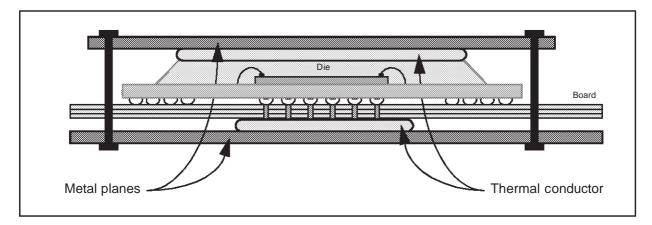

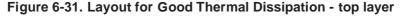

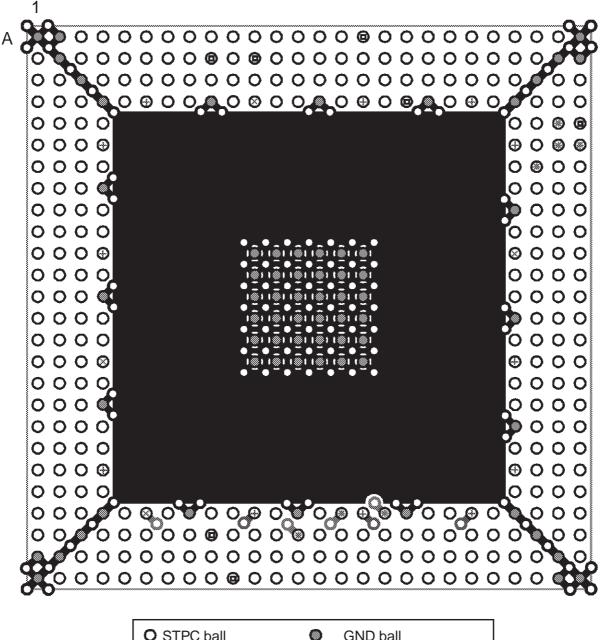

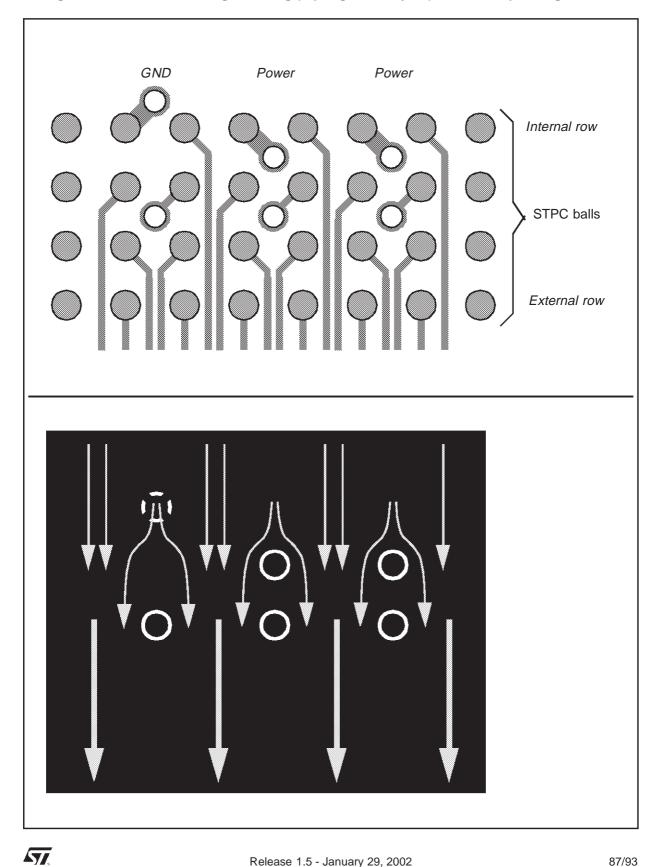

| DACK_ENC[2:0] O<br>TC O<br>RTCAS O<br>RMRTCCS# I/O<br>KBCS# I/O<br>RTCRW# I/O<br>RTCRW# I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BD4STRP_FT                                                                                                                                                                                                                                                                                                                                                                                            | Time-Multiplexed DMA Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                                                       |