## TDA2030

## 14W Hi-Fi AUDIO AMPLIFIER

#### DESCRIPTION

The TDA2030 is a monolithic integrated circuit in Pentawatt® package, intended for use as a low frequency class AB amplifier. Typically it provides 14W output power (d = 0.5%) at  $14V/4\Omega$ ; at  $\pm 14V$  or 28V, the guaranteed output power is 12W on a  $4\Omega$  load and 8W on a  $8\Omega$  (DIN45500).

The TDA2030 provides high output current and has very low harmonic and cross-over distortion.

Further the device incorporates an original (and patented) short circuit protection system comprising an arrangement for automatically limiting the dissipated power so as to keep the working point of the output transistors within their safe operating area. A conventional thermal shut-down system is also included.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                     | Value      | Unit |

|------------------|-----------------------------------------------|------------|------|

| Vs               | Supply voltage                                | ± 18 (36)  | V    |

| Vi               | Input voltage                                 | Vs         |      |

| Vi               | Differential input voltage                    | ± 15       | V    |

| Ιo               | Output peak current (internally limited)      | 3.5        | А    |

| P <sub>tot</sub> | Power dissipation at T <sub>case</sub> = 90°C | 20         | W    |

| $T_{stg},T_{j}$  | Stoprage and junction temperature             | -40 to 150 | °C   |

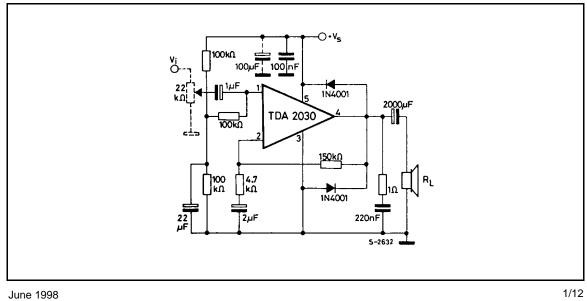

#### **TYPICAL APPLICATION**

### TDA2030

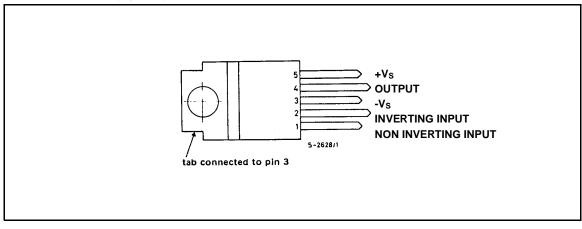

### **PIN CONNECTION** (top view)

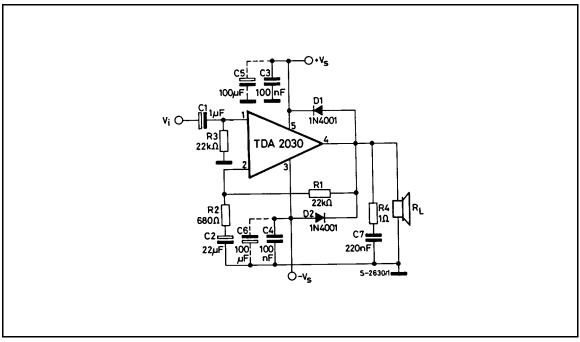

### **TEST CIRCUIT**

2/12

### THERMAL DATA

| Symbol                 | Parameter                            | Value | Unit |

|------------------------|--------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal resistance junction-case max | 3     | °C/W |

# **ELECTRICAL CHARACTERISTICS** (Refer to the test circuit, V<sub>s</sub> = $\pm$ 14V , T<sub>amb</sub> = 25°C unless otherwise specified) for single Supply refer to fig. 15 Vs = 28V

| Symbol          | Parameter                  | Test conditions                                                                                                                           | Min.          | Тур.       | Max.       | Unit     |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|------------|----------|

| Vs              | Supply voltage             |                                                                                                                                           | ±6<br>12      |            | ± 18<br>36 | V        |

| l <sub>d</sub>  | Quiescent drain current    |                                                                                                                                           |               | 40         | 60         | mA       |

| I <sub>b</sub>  | Input bias current         |                                                                                                                                           |               | 0.2        | 2          | μA       |

| Vos             | Input offset voltage       | $V_{s} = \pm 18V (Vs = 36V)$                                                                                                              |               | ± 2        | ± 20       | mV       |

| l <sub>os</sub> | Input offset current       |                                                                                                                                           |               | ± 20       | ± 200      | nA       |

| Po              | Output power               |                                                                                                                                           | 12<br>8       | 14<br>9    |            | W<br>W   |

|                 |                            |                                                                                                                                           |               | 18<br>11   |            | W<br>W   |

| d               | Distortion                 |                                                                                                                                           |               | 0.2        | 0.5        | %        |

|                 |                            |                                                                                                                                           |               | 0.1        | 0.5        | %        |

| В               | Power Bandwidth<br>(-3 dB) | $\begin{array}{l} G_v = 30 \text{ dB} \\ P_o = 12 W \\ \end{array}  R_L = 4 \Omega \end{array}$                                           | 10 to 140,000 |            | Hz         |          |

| Ri              | Input resistance (pin 1)   |                                                                                                                                           | 0.5           | 5          |            | MΩ       |

| Gv              | Voltage gain (open loop)   |                                                                                                                                           |               | 90         |            | dB       |

| Gv              | Voltage gain (closed loop) | f = 1 kHz                                                                                                                                 | 29.5          | 30         | 30.5       | dB       |

| e <sub>N</sub>  | Input noise voltage        | B = 22 Hz to 22 KHz                                                                                                                       |               | 3          | 10         | μV       |

| i <sub>N</sub>  | Input noise current        |                                                                                                                                           |               | 80         | 200        | pА       |

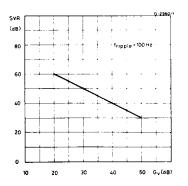

| SVR             | Supply voltage rejection   | $\begin{array}{l} R_{L}=4\Omega & G_{v}=30 \; dB \\ R_{g}=22 \; k\Omega \\ V_{ripple}=0.5 \; V_{eff} \\ f_{ripple}=100 \; Hz \end{array}$ | 40            | 50         |            | dB       |

| l <sub>d</sub>  | Drain current              |                                                                                                                                           |               | 900<br>500 |            | mA<br>mA |

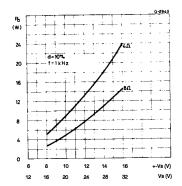

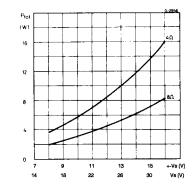

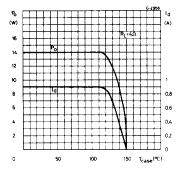

Figure 1. Output power vs. supply voltage

Figure 2. Output power vs. supply voltage

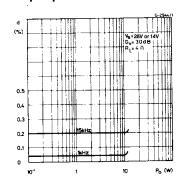

## Figure 3. Distortion vs. output power

Figure 4. Distortion vs. output power

Figure 5. Distortion vs. output power

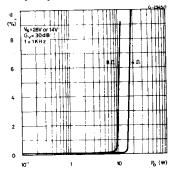

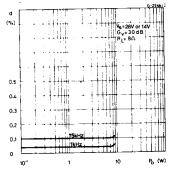

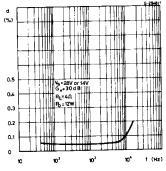

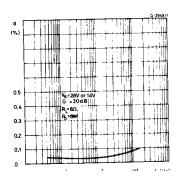

Figure 6. Distortion vs. frequency

Figure 7. Distortion vs. frequency

4/12

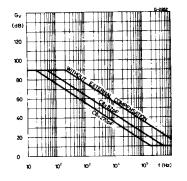

Figure 8. Frequency response with different values of the rolloff capacitor C8 (see fig. 13)

Figure 9. Quiescent current vs. supply voltage

## Figure 10. Supply voltage rejection vs. voltage gain

Figure 11. Power dissipation and efficiency vs. output power

12

а

4

16 Po (W)

40

30

x

Ptc

W

14

12

10

8

6

4

0

Figure 12. Maximum power dissipation vs. supply voltage (sine wave operation)

#### **APPLICATION INFORMATION**

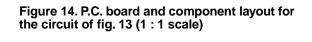

Figure 13. Typical amplifier with split power supply

#### **APPLICATION INFORMATION** (continued)

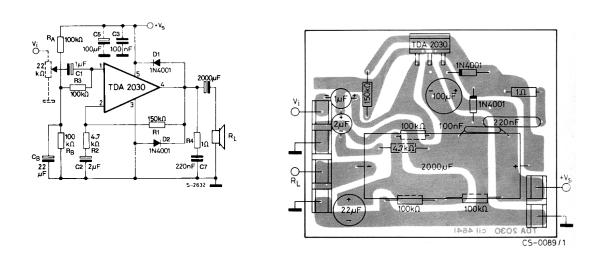

## Figure 15. Typical amplifier with single power supply

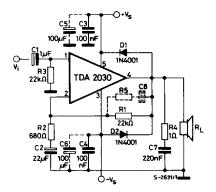

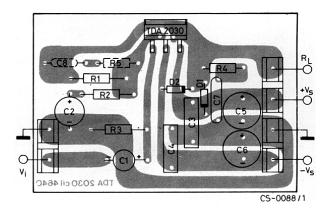

Figure 16. P.C. board and component layout for the circuit of fig. 15 (1 : 1 scale)

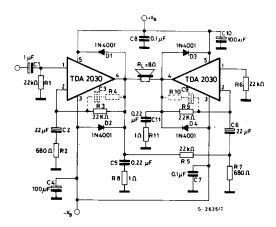

Figure 17. Bridge amplifier configuration with split power supply ( $P_o = 28W$ ,  $V_s = \pm 14V$ )

6/12

#### PRACTICAL CONSIDERATIONS

#### Printed circuit board

The layout shown in Fig. 16 should be adopted by the designers. If different layouts are used, the ground points of input 1 and input 2 must be well decoupled from the ground return of the output in which a high current flows.

#### Assembly suggestion

No electrical isolation is needed between the

package and the heatsink with single supply voltage configuration.

#### **Application suggestions**

The recommended values of the components are those shown on application circuit of fig. 13. Different values can be used. The following table can help the designer.

| Component | Recomm.<br>value                    | Purpose                                             | Larger than recommended value                                    | Smaller than recommended value        |  |

|-----------|-------------------------------------|-----------------------------------------------------|------------------------------------------------------------------|---------------------------------------|--|

| R1        | 22 kΩ                               | Closed loop gain setting                            | Increase of gain                                                 | Decrease of gain (*)                  |  |

| R2        | 680 Ω                               | Closed loop gain setting                            | Decrease of gain (*)                                             | Increase of gain                      |  |

| R3        | 22 kΩ                               | Non inverting input<br>biasing                      | Increase of input impedance                                      | Decrease of input<br>impedance        |  |

| R4        | 1 Ω                                 | Frequency stability                                 | Danger of osccilat. at<br>high frequencies<br>with induct. loads |                                       |  |

| R5        | ≅ 3 R2                              | Upper frequency cutoff                              | Poor high frequencies attenuation                                | Danger of oscillation                 |  |

| C1        | 1 μF                                | Input DC<br>decoupling                              |                                                                  | Increase of low<br>frequencies cutoff |  |

| C2        | 22 μF                               | Inverting DC decoupling                             |                                                                  | Increase of low<br>frequencies cutoff |  |

| C3, C4    | 0.1 μF                              | Supply voltage bypass                               |                                                                  | Danger of oscillation                 |  |

| C5, C6    | 100 μF                              | Supply voltage bypass                               |                                                                  | Danger of oscillation                 |  |

| C7        | 0.22 μF                             | Frequency stability                                 |                                                                  | Danger of oscillation                 |  |

| C8        | $\cong \frac{1}{2\pi \text{ B R1}}$ | Upper frequency cutoff                              | Smaller bandwidth                                                | Larger bandwidth                      |  |

| D1, D2    | 1N4001                              | To protect the device against output voltage spikes |                                                                  |                                       |  |

(\*) Closed loop gain must be higher than 24dB

## SINGLE SUPPLY APPLICATION

| Component                      | Recomm.<br>value                    | Purpose                        | Larger than recommended value                                    | Smaller than recommended value        |  |

|--------------------------------|-------------------------------------|--------------------------------|------------------------------------------------------------------|---------------------------------------|--|

| R1                             | 150 kΩ                              | Closed loop gain setting       | Increase of gain                                                 | Decrease of gain (*)                  |  |

| R2                             | 4.7 kΩ                              | Closed loop gain setting       | Decrease of gain (*)                                             | Increase of gain                      |  |

| R3                             | 100 kΩ                              | Non inverting input<br>biasing | Increase of input impedance                                      | Decrease of input impedance           |  |

| R4                             | 1 Ω                                 | Frequency stability            | Danger of osccilat. at<br>high frequencies<br>with induct. loads |                                       |  |

| R <sub>A</sub> /R <sub>B</sub> | 100 kΩ                              | Non inverting input Biasing    |                                                                  | Power Consumption                     |  |

| C1                             | 1 μF                                | Input DC<br>decoupling         |                                                                  | Increase of low<br>frequencies cutoff |  |

| C2                             | 22 μF                               | Inverting DC decoupling        |                                                                  | Increase of low<br>frequencies cutoff |  |

| C3                             | 0.1 μF                              | Supply voltage<br>bypass       |                                                                  | Danger of oscillation                 |  |

| C5                             | 100 μF                              | Supply voltage bypass          |                                                                  | Danger of oscillation                 |  |

| C7                             | 0.22 μF                             | Frequency stability            |                                                                  | Danger of oscillation                 |  |

| C8                             | $\cong \frac{1}{2\pi \text{ B R1}}$ | Upper frequency cutoff         | Smaller bandwidth                                                | Larger bandwidth                      |  |

| D1, D2                         | 1N4001                              | To protect the device agains   | st output voltage spikes                                         |                                       |  |

(\*) Closed loop gain must be higher than 24dB

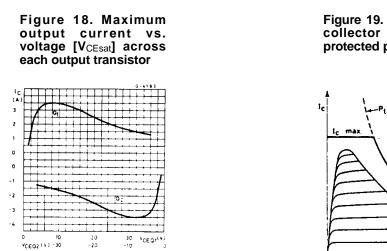

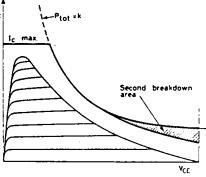

#### SHORT CIRCUIT PROTECTION

The TDA2030 has an original circuit which limits the current of the output transistors. Fig. 18 shows that the maximum output current is a function of the collector emitter voltage; hence the output transistors work within their safe operating area (Fig. 2). This function can therefore be considered as being

peak power limiting rather than simple current limiting.

It reduces the possibility that the device gets damaged during an accidental short circuit from AC output to ground.

Figure 19. Safe operating area and collector characteristics of the protected power transistor

#### **THERMAL SHUT-DOWN**

The presence of a thermal limiting circuit offers the following advantages:

- An overload on the output (even if it is permanent), or an above limit ambient temperature can be easily supported since the T<sub>j</sub> cannot be higher than 150°C.

- The heatsink can have a smaller factor of safety compared with that of a conventional circuit. There is no possibility of device damage due to high junction temperature. If for any reason, the

junction temperature increases up to 150°C, the thermal shut-down simply reduces the power dissipation at the current consumption.

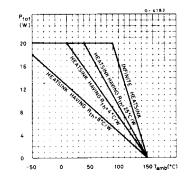

The maximum allowable power dissipation depends upon the size of the external heatsink (i.e. its thermal resistance); fig. 22 shows this dissipable power as a function of ambient temperature for different thermal resistance.

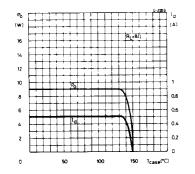

Figure 20. Output power and drain current vs. case temperature ( $R_{\perp} = 4\Omega$ )

Figure 21. Output power and drain current vs. case temperature ( $R_{L} = 8\Omega$ )

Figure 22. Maximum allowable power dissipation vs. ambient temperature

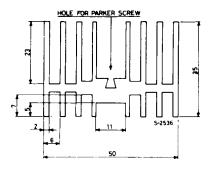

Figure 23. Example of heat-sink

Dimension : suggestion.

The following table shows the length that the heatsink in fig. 23 must have for several values of  $P_{tot}$  and  $R_{th}.$

| Ptot (W)                   | 12  | 8   | 6   |

|----------------------------|-----|-----|-----|

| Length of heatsink<br>(mm) | 60  | 40  | 30  |

| Rth of heatsink<br>(° C/W) | 4.2 | 6.2 | 8.3 |

10/12

| DIM. | mm         |       |       | inch  |       |       |

|------|------------|-------|-------|-------|-------|-------|

|      | MIN.       | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α    |            |       | 4.8   |       |       | 0.189 |

| С    |            |       | 1.37  |       |       | 0.054 |

| D    | 2.4        |       | 2.8   | 0.094 |       | 0.110 |

| D1   | 1.2        |       | 1.35  | 0.047 |       | 0.053 |

| E    | 0.35       |       | 0.55  | 0.014 |       | 0.022 |

| E1   | 0.76       |       | 1.19  | 0.030 |       | 0.047 |

| F    | 0.8        |       | 1.05  | 0.031 |       | 0.041 |

| F1   | 1          |       | 1.4   | 0.039 |       | 0.055 |

| G    | 3.2        | 3.4   | 3.6   | 0.126 | 0.134 | 0.142 |

| G1   | 6.6        | 6.8   | 7     | 0.260 | 0.268 | 0.276 |

| H2   |            |       | 10.4  |       |       | 0.409 |

| H3   | 10.05      |       | 10.4  | 0.396 |       | 0.409 |

| L    | 17.55      | 17.85 | 18.15 | 0.691 | 0.703 | 0.715 |

| L1   | 15.55      | 15.75 | 15.95 | 0.612 | 0.620 | 0.628 |

| L2   | 21.2       | 21.4  | 21.6  | 0.831 | 0.843 | 0.850 |

| L3   | 22.3       | 22.5  | 22.7  | 0.878 | 0.886 | 0.894 |

| L4   |            |       | 1.29  |       |       | 0.051 |

| L5   | 2.6        |       | 3     | 0.102 |       | 0.118 |

| L6   | 15.1       |       | 15.8  | 0.594 |       | 0.622 |

| L7   | 6          |       | 6.6   | 0.236 |       | 0.260 |

| L9   |            | 0.2   |       |       | 0.008 |       |

| М    | 4.23       | 4.5   | 4.75  | 0.167 | 0.177 | 0.187 |

| M1   | 3.75       | 4     | 4.25  | 0.148 | 0.157 | 0.167 |

| V4   | 40° (typ.) |       |       |       |       |       |

| Dia  | 3.65       |       | 3.85  | 0.144 |       | 0.152 |

### PENTAWATT PACKAGE MECHANICAL DATA

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics  $\circledast$  1998 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands -Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

۲7/

12/12