# 16-bit Proprietary Microcontroller cmos

## F<sup>2</sup>MC-16LX MB90495G Series

## MB90497G/F497G/F498G/V495G

### ■ DESCRIPTION

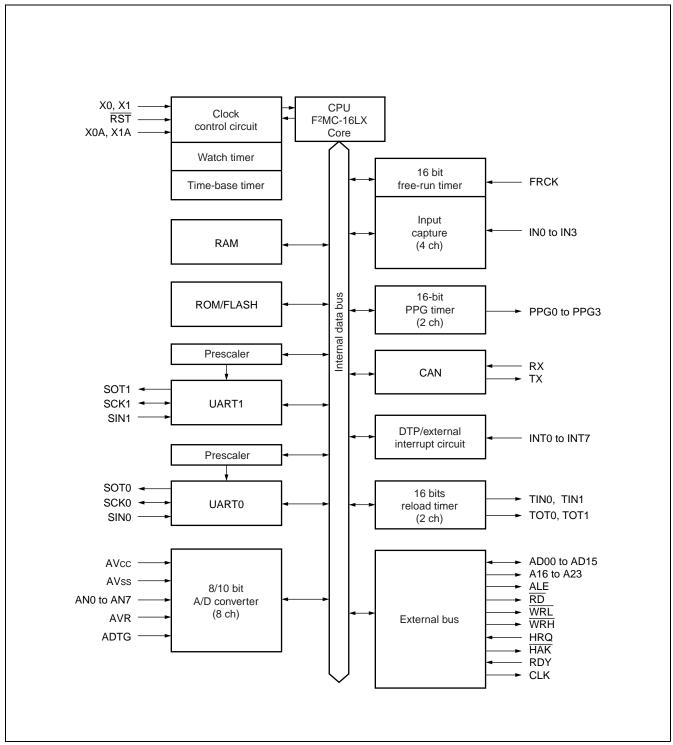

The MB90495G Series is a general-purpose, high-performance 16-bit microcontroller. It was designed for devices like consumer electronics, which require high-speed, real-time process control. This series features an on-chip full-CAN interface.

In addition to being backwards compatible with the F<sup>2</sup>MC\* family architecture, the instruction set has been expanded to add support for high-level language instructions, expanded addressing mode, and enhanced multiply/ divide and bit processing instructions. A 32-bit accumulator is also provided, making it possible to process long word (32-bit) data.

The MB90495G Series peripheral resources include on chip 8/10-bit A/D converter, UART (SCI) 0/1, 8/16-bit PPG timer, 16-bit I/O timer (16-bit free-run timer, input capture 0, 1, 2, 3 (ICU)), and CAN controller.

\*: F2MC is abbreviation for Fujitsu Flexible Microcontroller. F2MC is a registered trademark of Fujitsu Limited.

#### **■ FEATURES**

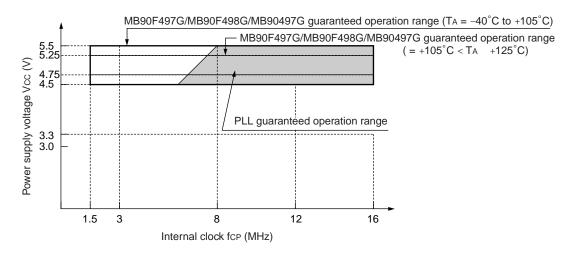

- Models that support +125 °C

- Clock

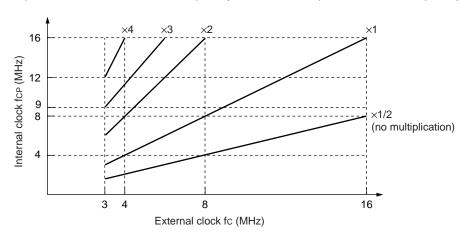

- •Built-in PLL clock multiplier circuit

- •Choose 1/2 oscillation clock or ×1 to ×4 multiplied oscillation clock (for a 4-MHz oscillation clock, 4 to 16 MHz) machine (PLL) clock

### (Continued)

- Select subclock behavior (8.192 kHz)

- •Minimum instruction execution time: 62.5 ns (operating with 4-MHz oscillation clock and × 4 PLL clock)

### • 16-MByte CPU memory space

- •24-bit internal addressing

- •External access possible through selection of 8/16-bit bus width (external bus mode)

### Optimum instruction set for controller applications

- •Wealth of data types (Bit, Byte, Word, Long Word)

- •Wealth of addressing modes (23 different modes)

- •Enhanced signed multiply-divide instructions and RETI instruction functions

- •Enhanced high-precision arithmetic employing 32-bit accumulator

### Instruction set supports high-level programming language (C) and multitasking

- •Employs system stack pointer

- •Enhanced indirect instructions with all pointer types

- Barrel shift instructions

### • Improved execution speed

•4-byte instruction queue

#### · Powerful interrupt feature

•Powerful 8-level, 34-condition interrupt feature

### · CPU-independent automated data forwarding

•Extended intelligent I/O service feature (EI2OS) : maximum 16 channels

#### • Low-power consumption (Standby) Mode

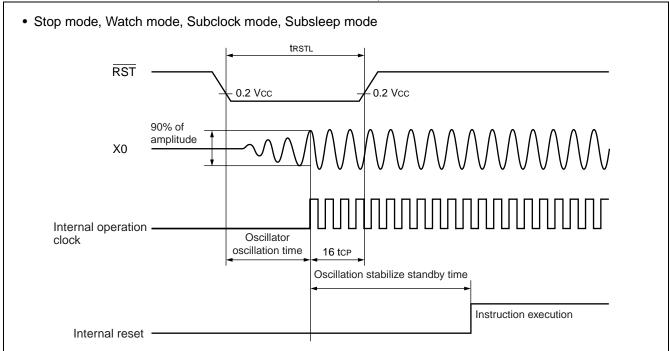

- •Sleep mode (CPU operation clock stopped)

- •Time-base timer mode (oscillation clock and subclock, time-base timer and watch timer only operational)

- •Watch mode (subclock and watch timer only operational)

- Stop mode (oscillation clock and subclock stopped)

- •CPU intermittent operation mode

#### • Process

CMOS technology

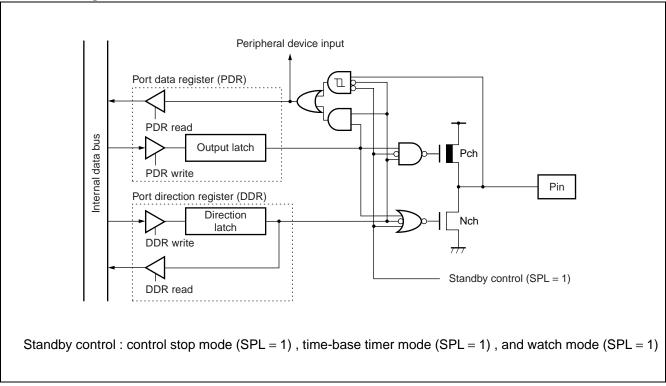

### • I/O Ports

•Generic I/O ports (CMOS output): 49

#### • Timer

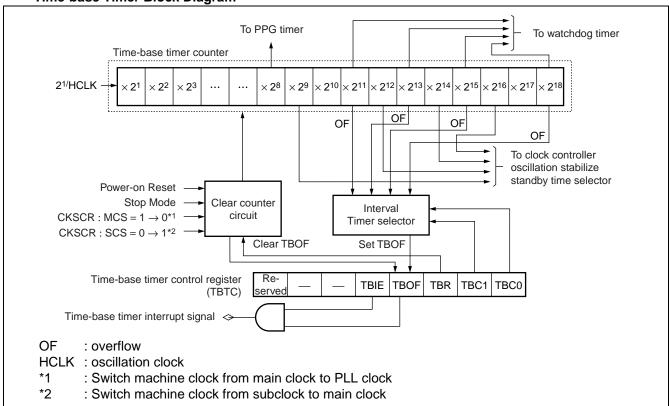

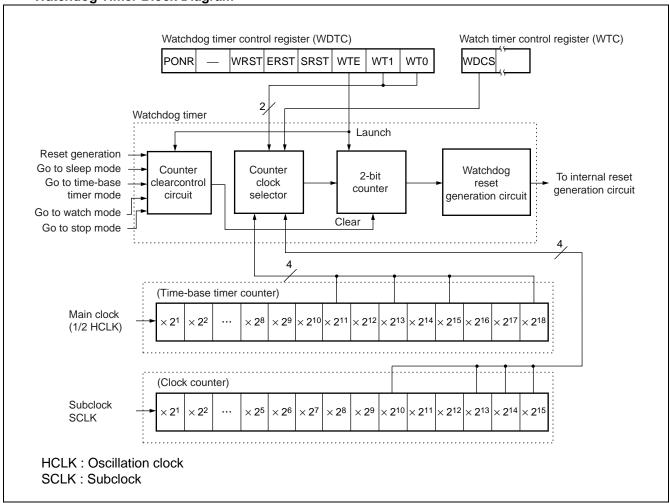

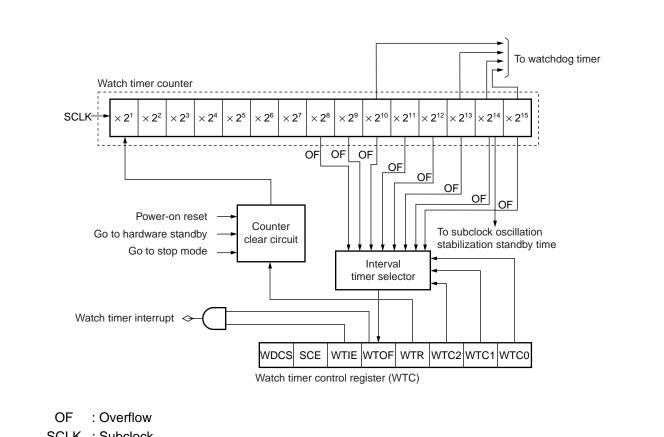

•Time-base timer, watch timer, watchdog timer: 1 channel

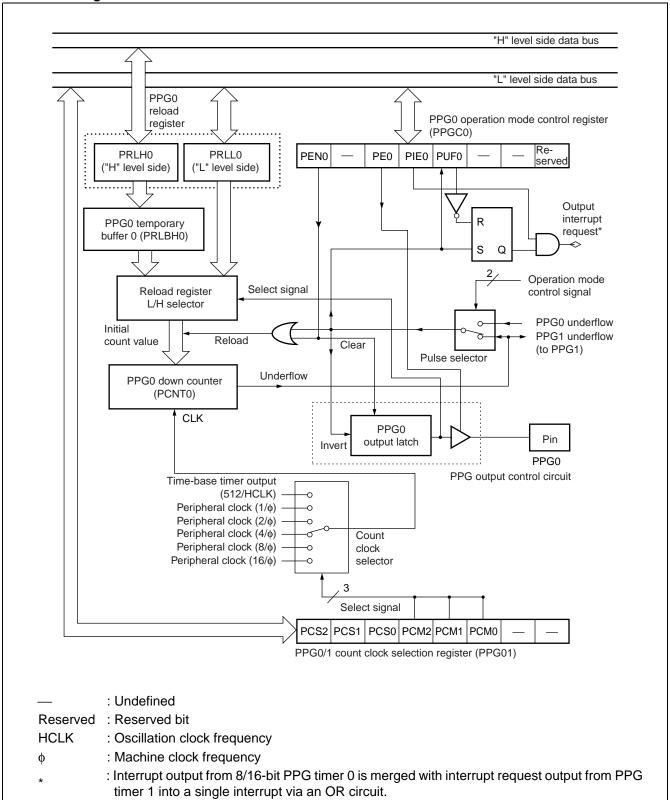

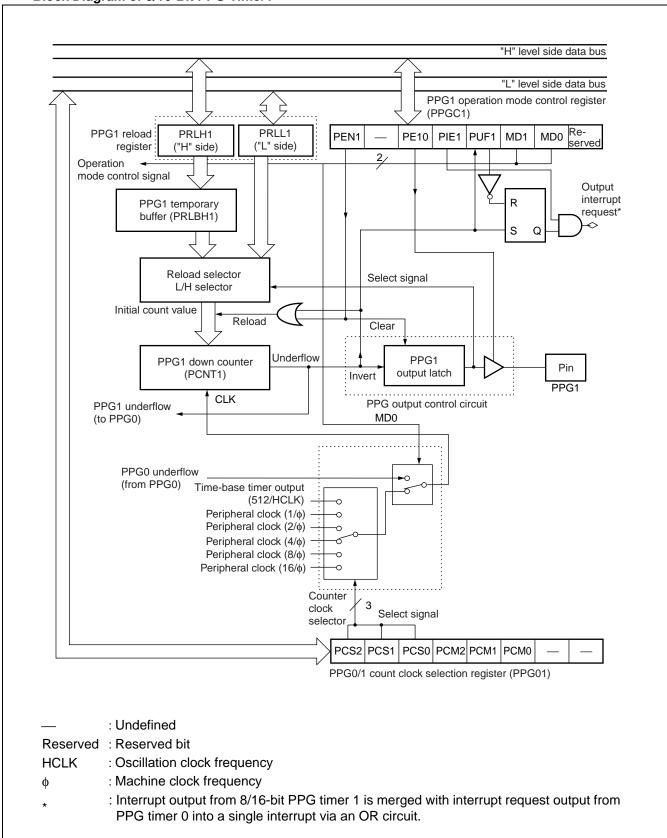

•8/16-bit PPG timer: four 8-bit channels, or two 16-bit channels

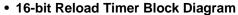

•16-bit reload timer: 2 channels

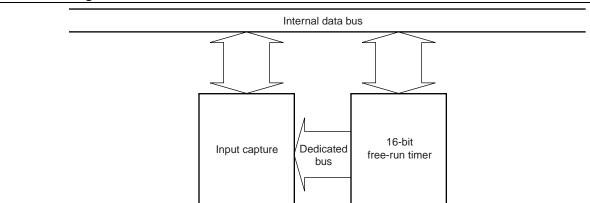

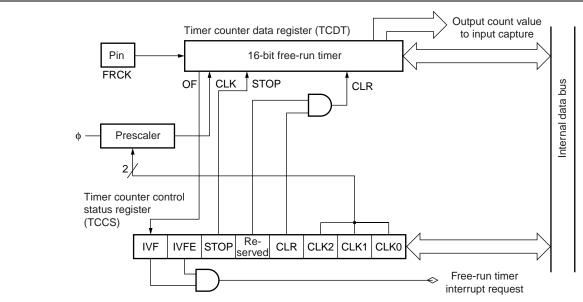

•16-bit I/O timer

•16-bit free-run timer: 1 channel

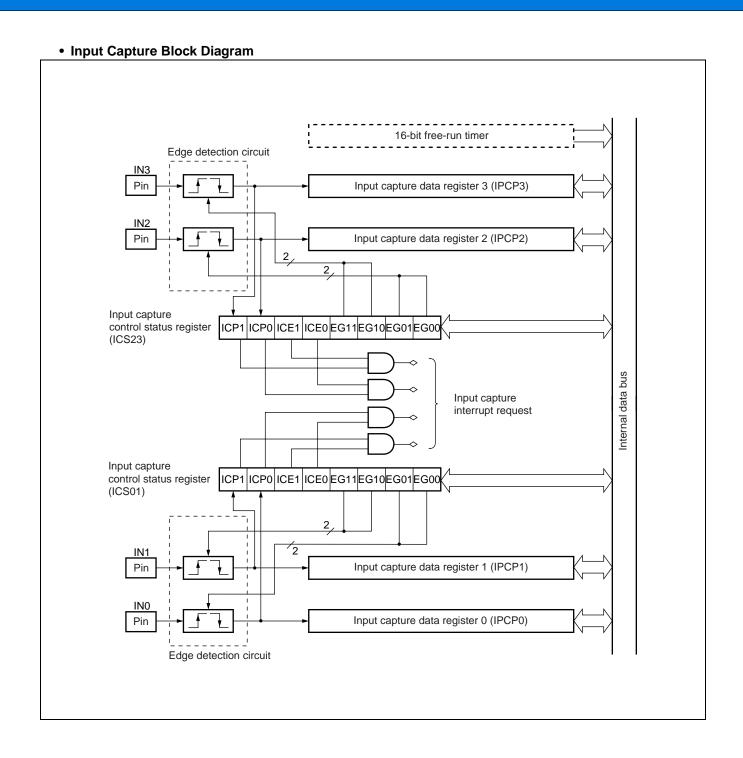

•16-bit input capture (ICU): 4 channels

Generates interrupt requests by latching onto the count value of the 16-bit free-run timer with pin input edge detection

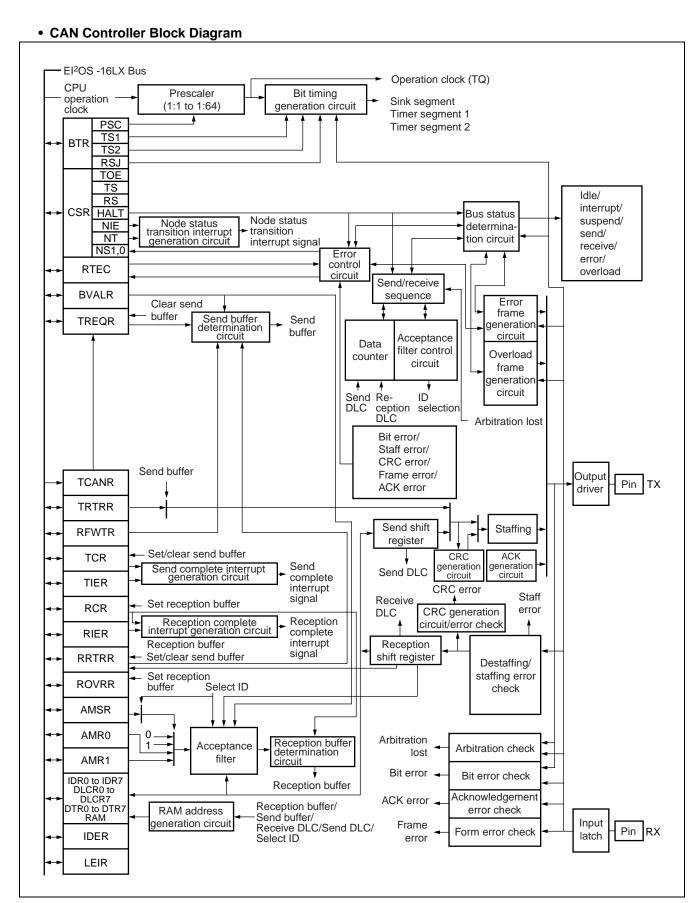

- CAN Controller : 1 channel

- •CAN specifications conform to versions 2.0A and 2.0B

- •8 on-chip message buffers

- •Forwarding rate 10 Kbps to 1 Mbps (with 16-MHz machine clock)

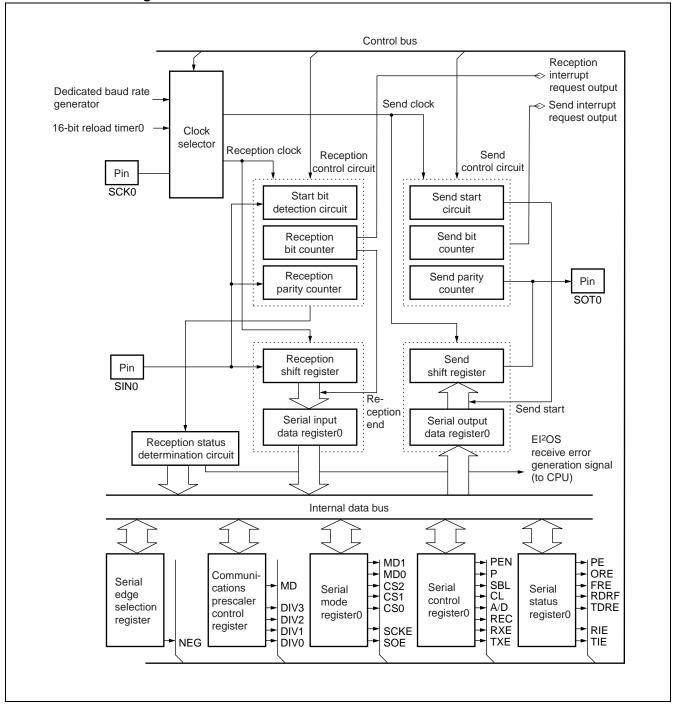

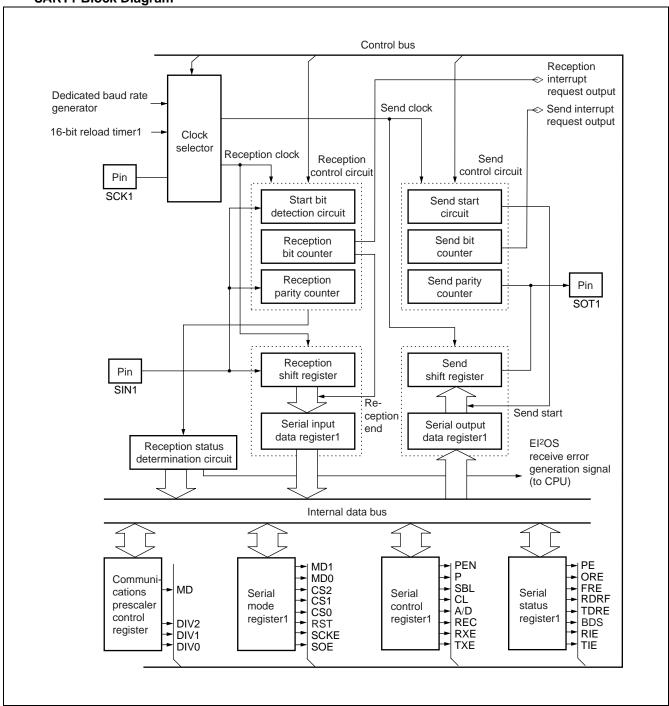

- UART0 (SCI) /UART1 (SCI) : 2 channels

- •All with full duplex double buffer

- •Use clock-asynchronous or clock-synchronous serial forwarding

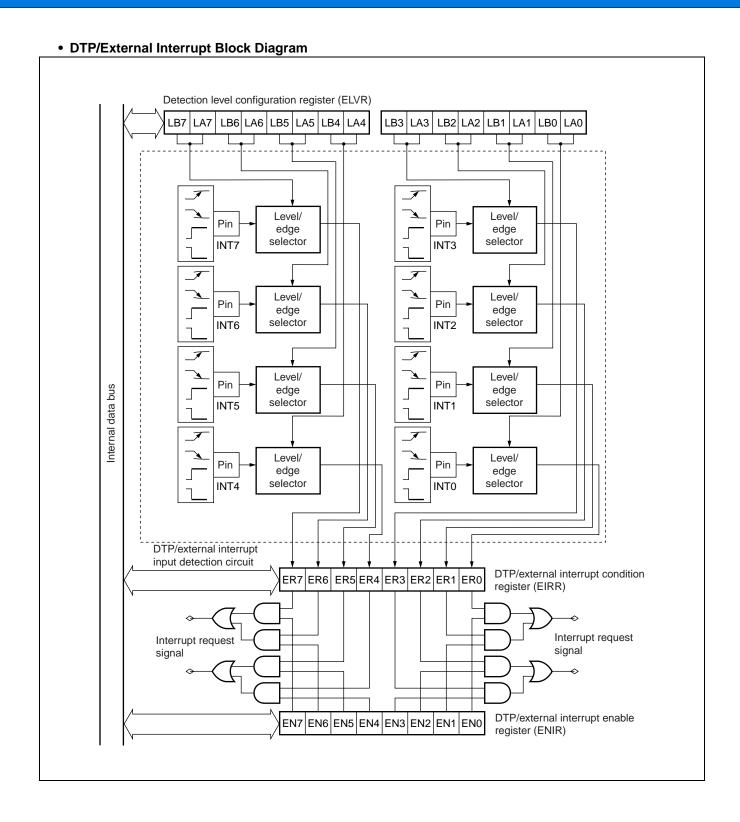

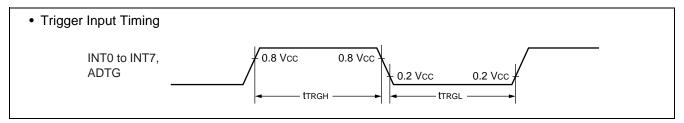

- DTP/external interrupt : 8 channels

- •A module for launching extended intelligent I/O service (EI<sup>2</sup>OS) and generating external interrupts through external output

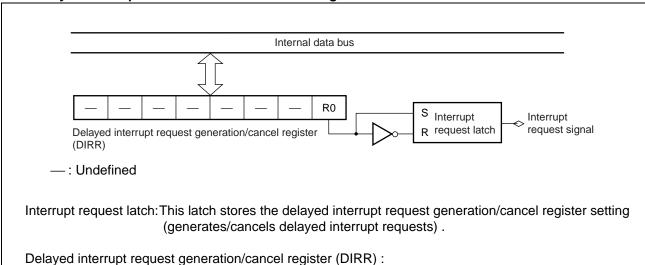

- Delayed interrupt generation module

- •Generates interrupt requests for switching tasks

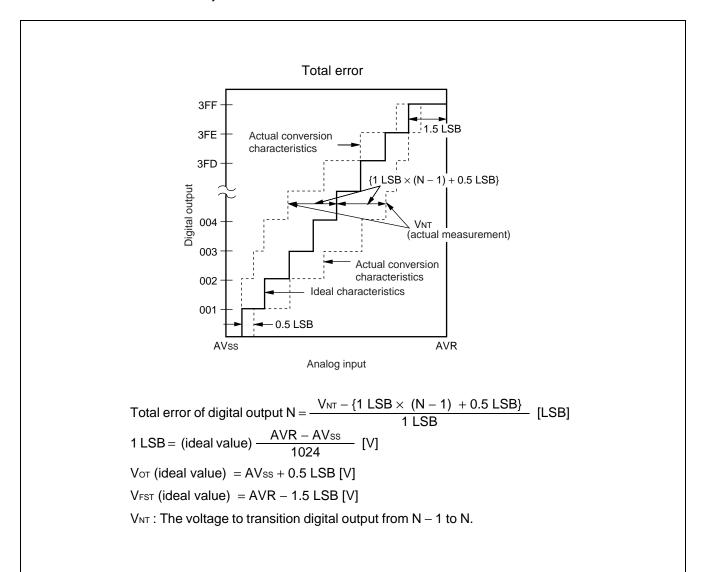

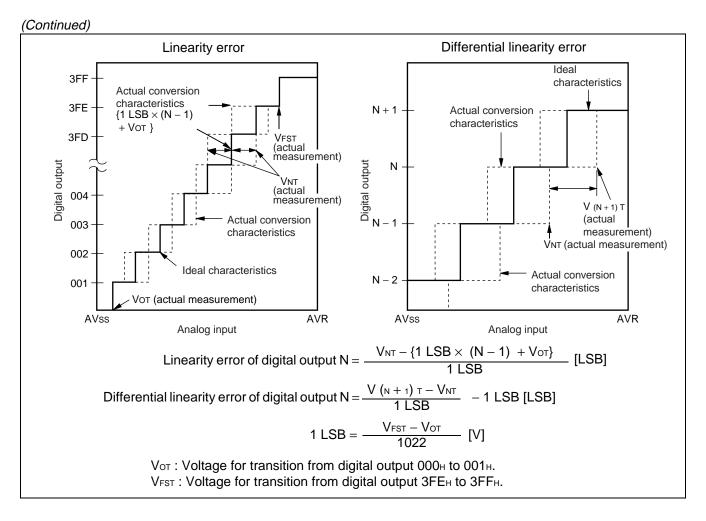

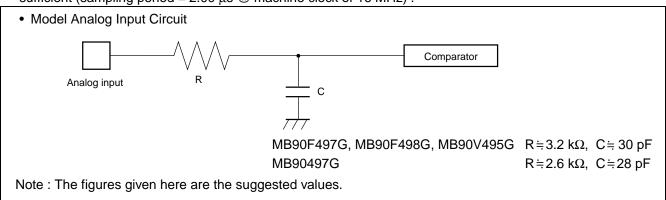

- 8/10-bit A/D converter: 8 channels

- •Switch between 8-bit and 10-bit resolution

- •Launch through external trigger input

- •Conversion time: 6.13 μs (with 16-MHz machine clock, including sampling time)

- Program batch function

- •2-address pointer ROM correction

- Clock output function

### **■ PRODUCT LINEUP**

| Part Number Paarmeter          |                          | MB90F497G                                                                                                                                                                                                               | MB90497G           | MB90F498G                                                                                  | MB90V495G         |  |

|--------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------|-------------------|--|

| Feature Classi                 | fication                 | FLASH ROM                                                                                                                                                                                                               | Mask ROM           | FLASH ROM                                                                                  | Product Evaluated |  |

| ROM Size                       |                          | 64 K                                                                                                                                                                                                                    | bytes              | 128 Kbytes                                                                                 | _                 |  |

| RAM Size                       |                          |                                                                                                                                                                                                                         | 2 Kbytes           |                                                                                            | 6 Kbytes          |  |

| Process                        |                          |                                                                                                                                                                                                                         | CM                 | 1OS                                                                                        | •                 |  |

| Package                        |                          | LQFP64 (width                                                                                                                                                                                                           | n 0.65 mm) , QFP64 | (width 1.0 mm)                                                                             | PGA256            |  |

| Operating Pow                  | er                       |                                                                                                                                                                                                                         | 4.5 V t            | o 5.5 V                                                                                    |                   |  |

| Emulator power                 | er supply*               |                                                                                                                                                                                                                         | _                  |                                                                                            | None              |  |

| CPU Functions                  | 3                        | Number of instruction Instruction bit length Instruction length Data bit length Minimum execution                                                                                                                       |                    | : 351<br>: 8-bit, 16-bit<br>: 1 to 7 bytes<br>: 1 bit, 8-bit, 16-bit<br>16-MHz machine clo |                   |  |

|                                |                          | Interrupt processing                                                                                                                                                                                                    | time : minimum 1.5 | μs (with 16-MHz ma                                                                         | achine clock)     |  |

| Low-power cor<br>(Standby) Mod |                          | Sleep mode/watch mode/time-base timer mode/stop mode / CPU intermittent mode                                                                                                                                            |                    |                                                                                            |                   |  |

| I/O Ports                      |                          | General-purpose I/O ports (CMOS output) : 49                                                                                                                                                                            |                    |                                                                                            |                   |  |

| Time-base time                 | er                       | 18-bit free-run counter<br>Interrupt interval: 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms<br>(with 4-MHz oscillation clock)                                                                                              |                    |                                                                                            |                   |  |

| Watchdog time                  | er                       | Reset generation intervals : 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (with 4-MHz oscillation clock)                                                                                                                      |                    |                                                                                            |                   |  |

| 16-bit                         | 16-bit<br>free-run timer | Number of channels : 1 Interrupts from overflow generation                                                                                                                                                              |                    |                                                                                            |                   |  |

| I/O Timer                      | Input capture            | Number of channels : 4 Maintenance of free-run timer value through pin input (rising, falling or both edges)                                                                                                            |                    |                                                                                            |                   |  |

| 16-bit reload timer            |                          | Number of channels : 2 16-bit reload timer operation Count clock interval : 0.25 μs, 0.5 μs, 2.0 μs (with 16-MHz machine clock) External event count enabled                                                            |                    |                                                                                            |                   |  |

| Watch timer                    |                          | 15-bit free-run counter<br>Interrupt intervals : 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s<br>(with 8.192-kHz subclock)                                                                                    |                    |                                                                                            |                   |  |

| 8/16-bit PPG ti                | mer                      | Number of channels : 2 (two 8-bit channels can be used) Two 8-bit or one 16-bit channel PPG operation possible Free interval, free duty pulse output possible Count clock : 62.5 ns to 1 µs (with 16-MHz machine clock) |                    |                                                                                            |                   |  |

<sup>\*:</sup> The S2 dipswitch setting when using the MB2145-507 emulation baud. For details, see the MB2145-507 hardware manual (2.7 Emulator Power Pin) .

### (Continued)

| Part Number Parameter               | MB90F497G                                                                                                                                                                                                               | MB90497G                                                                      | MB90F498G                                                          | MB90V495G           |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|--|

| Delayed interrupt generation module | Module for delayed interrupt generation switching tasks Used in real-time OS                                                                                                                                            |                                                                               |                                                                    |                     |  |

| DTP/external interrupt circuit      | Number of inputs: 8 Starting by rising edge, falling edge, "H" level input, or "L" level input, external interrupts or extended intelligent I/O service (EI2OS) can be used                                             |                                                                               |                                                                    |                     |  |

| 8/10-bit A/D converter              | Continuous convers<br>(up to 8 channels of<br>One-shot conversion<br>Continuous conversion                                                                                                                              | bit or 8-bit<br>.13 µs (with 16-MHz<br>sion of multiple linked                | d channels possible<br>elected channel only<br>selected channel co | once<br>intinuously |  |

| UARTO (SCI)                         | Clock-asynchronou                                                                                                                                                                                                       | s : 1<br>forwarding : 62.5 Kb<br>s forwarding : 1,202<br>se performed by two- | bps to 62,500 bps                                                  | ion or by master/   |  |

| UART1 (SCI)                         | Number of channels: 1 Clock-synchronous forwarding: 62.5 Kbps to 2 Mbps Clock-asynchronous forwarding: 9,615 bps to 500 Kbps Transmission can be performed by two-way serial transmission or by master/slave connection |                                                                               |                                                                    |                     |  |

| CAN                                 | Send/receive mess                                                                                                                                                                                                       | N specification version<br>age buffers : 8<br>: 10 Kbps to 1 Mbps             |                                                                    | ne clock)           |  |

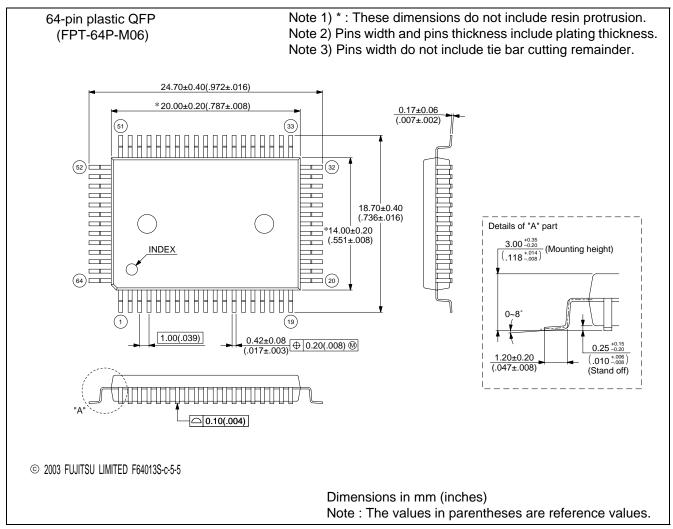

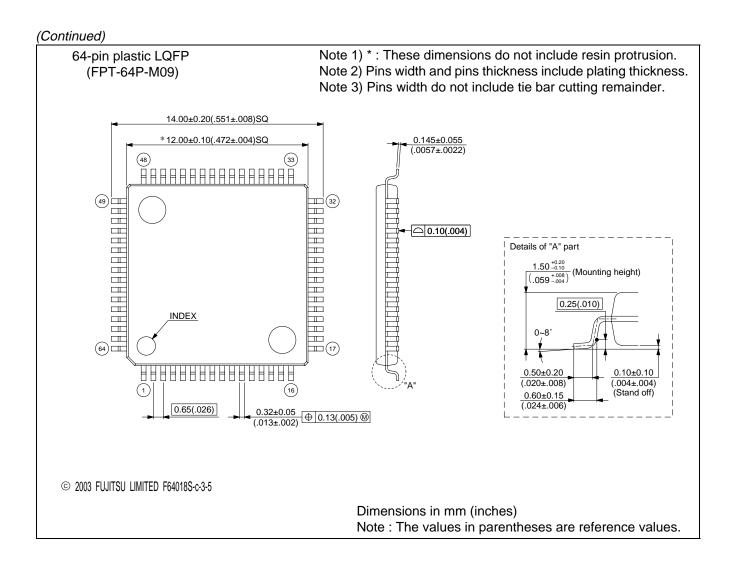

### ■ PACKAGES AND CORRESPONDING PRODUCTS

| Package     | MB90F497G | MB90497G | MB90F498G |

|-------------|-----------|----------|-----------|

| FPT-64P-M06 | 0         | 0        | 0         |

| FPT-64P-M09 | 0         | 0        | 0         |

$\bigcirc$  : available  $\times$  : not available

Note: See "Package Dimensions" for details.

#### ■ PRODUCT COMPARISON

### **Memory Size**

When evaluating with evaluation chips and other means, take careful note of the different between the evaluation chip and the chip actually used. Take particular note of the following.

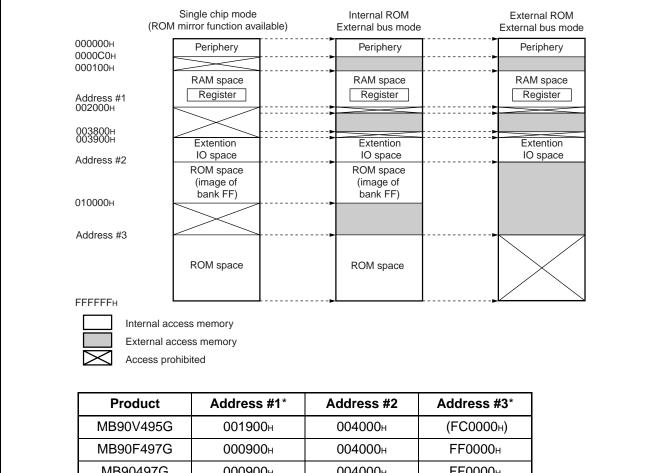

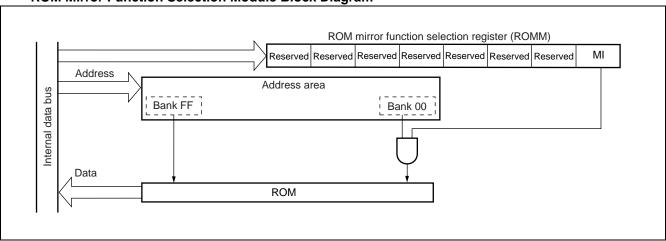

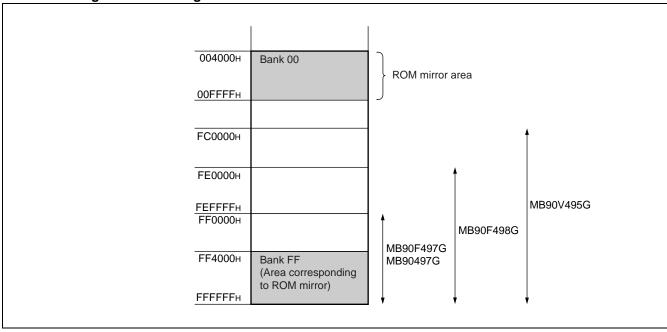

- While the MB90V495G does not feature an on-chip ROM, the dedicated development tool can be used to achieve operation equivalent to a product with built-in ROM. Therefore, the ROM size is configured by the development tool.

- On the MB90V495G, the FF4000H to FFFFFFH image is only visible in the 00 bank, and the FE0000H to FF3FFFH is only visible in the FE and FF banks (configurable on development tool) .

- On the MB90F497G/F498G/497G, the FF4000<sub>H</sub> to FFFFFF<sub>H</sub> image is visible in the 00 bank, and the FF0000<sub>H</sub> to FF3FFF<sub>H</sub> is visible only in the FF bank.

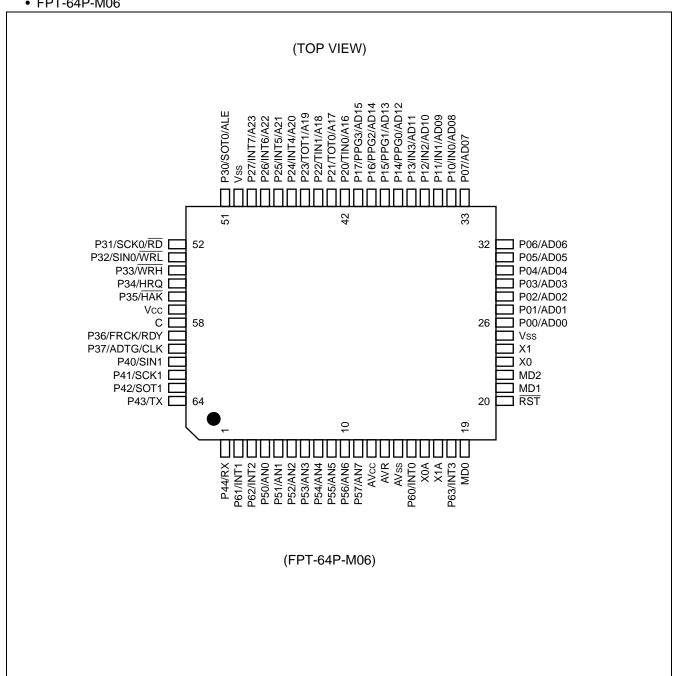

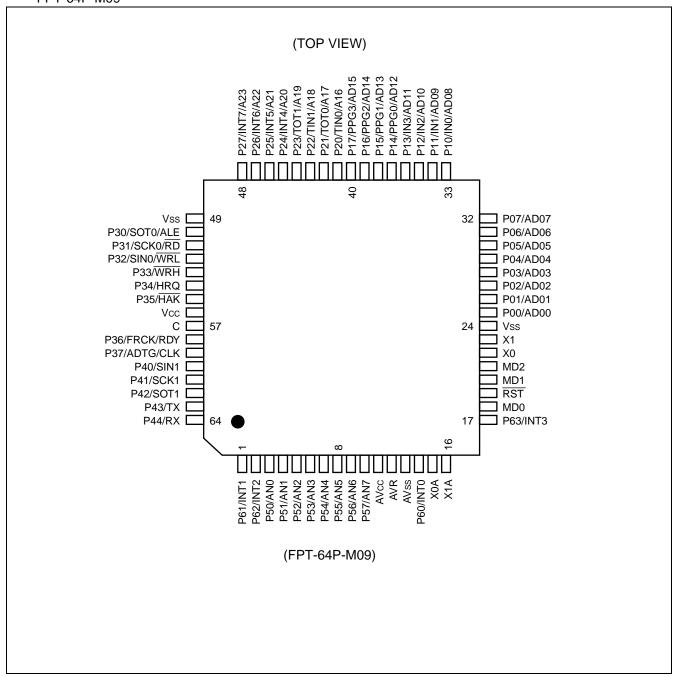

### **■ PIN ASSIGNMENTS**

• FPT-64P-M06

### **■ PIN DESCRIPTION**

| Pin No.     |             | B: N            | Circuit | Description                                                                                                                               |  |  |

|-------------|-------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| M06         | M09         | Pin Name        | Туре    | Description                                                                                                                               |  |  |

|             | 4           | P61             | -       | General-purpose I/O port                                                                                                                  |  |  |

| 2           | 1           | INT1            | D       | Functions as external interrupt input pin. Set this to input port.                                                                        |  |  |

| 2           | _           | P62             | _       | General-purpose I/O port                                                                                                                  |  |  |

| 3           | 3 2 INT2    |                 | D       | Functions as external interrupt input pin. Set this to input port.                                                                        |  |  |

|             |             | P50 to P57      |         | General-purpose I/O port                                                                                                                  |  |  |

| 4 to 11     | 3 to 10     | AN0 to<br>AN7   | E       | Functions as analog input port of A/D converter. This is enabled if analog input configuration is permitted.                              |  |  |

| 12          | 11          | AVcc            | _       | Vcc power input pin of A/D converter.                                                                                                     |  |  |

| 13          | 12          | AVR             | _       | Reference voltage (+) input pin for the A/D converter. This voltage must not exceed Vcc and AVcc. Reference voltage (-) is fixed to AVss. |  |  |

| 14          | 13          | AVss            | _       | Vss power input pin of A/D converter.                                                                                                     |  |  |

| 15          | 14          | P60             | D       | General-purpose I/O port                                                                                                                  |  |  |

| 15          | 14          | INT0            | D       | Functions as external interrupt input pin. Set this to input port.                                                                        |  |  |

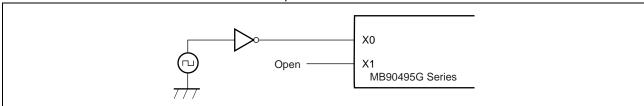

| 16          | 15          | X0A             | А       | Low-speed oscillation pin. Perform pull-down processing if not connected to an oscillator.                                                |  |  |

| 17          | 16          | X1A             | А       | Low-speed oscillation pin. Set to open if not connected to an oscillator.                                                                 |  |  |

| 10          | 17          | P63             | _       | General-purpose I/O port                                                                                                                  |  |  |

| 18          | 17          | INT3            | D       | Functions as external interrupt input pin. Set this to input port.                                                                        |  |  |

| 19          | 18          | MD0             | С       | Input pin for specifying operation mode.                                                                                                  |  |  |

| 20          | 19          | RST             | В       | External reset input pin.                                                                                                                 |  |  |

| 21          | 20          | MD1             | С       | Input pin for specifying operation mode.                                                                                                  |  |  |

| 22          | 21          | MD2             | F       | Input pin for specifying operation mode.                                                                                                  |  |  |

| 23          | 22          | X0              | Α       | High-speed oscillation pin.                                                                                                               |  |  |

| 24          | 23          | X1              | Α       | High-speed oscillation pin.                                                                                                               |  |  |

| 25          | 24          | Vss             |         | Power supply (0 V) input pin.                                                                                                             |  |  |

| 26 to       | 25 to       | P00 to P07      | D       | General-purpose I/O port Only enabled in single-chip mode.                                                                                |  |  |

| 33          | 32          | AD00 to<br>AD07 | to      | I/O pin for the lower 8-bit of the external address data bus. Only enabled during external bus mode.                                      |  |  |

|             |             | P10 to P13      |         | General-purpose I/O port. Only enabled in single-chip mode.                                                                               |  |  |

| 34 to<br>37 | 33 to<br>36 | IN0 to IN3      | D       | Functions as trigger input pin for input capture channels 0 to 3. Set this to input port.                                                 |  |  |

|             |             | AD08 to<br>AD11 |         | I/O pin for upper 4-bit of external address data bus. Only enabled during external bus mode.                                              |  |  |

### (Continued)

| Pin         | No.         | Din Nama        | Circuit | Description                                                                                                                                                             |  |  |

|-------------|-------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| M06         | M09         | Pin Name        | Type    | Description                                                                                                                                                             |  |  |

|             |             | P14 to P17      |         | General-purpose I/O port. Only enabled in single-chip mode.                                                                                                             |  |  |

| 38 to<br>41 | 37 to<br>40 | PPG0 to<br>PPG3 | D       | Functions as output pin of PPG timer 01, 23. Only valid if output configuration is enabled.                                                                             |  |  |

|             |             | AD12 to<br>AD15 |         | I/O pin for upper 4-bit of external address data bus. Only enabled during external bus mode.                                                                            |  |  |

|             |             | P20             |         | General-purpose I/O port.  When the bits of high address control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports. |  |  |

| 42          | 41          | TIN0            | D       | Functions as event input pin of TIN0 reload timer 0.<br>Set this to input port.                                                                                         |  |  |

|             |             | A16             |         | Output pin of external address bus (A16) . Only valid when the bits of high address control register (HACR) are set to "0" in external bus mode.                        |  |  |

|             |             | P21             |         | General-purpose I/O port. When the bits of high address control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports.  |  |  |

| 43          | 42          | ТОТ0            | D       | Functions as event output pin of TOT0 reload timer 0. Only valid if output configuration enabled.                                                                       |  |  |

|             |             |                 |         | Output pin of external address bus (A17) . Only valid when the bits of high address control register (HACR) are set to "0" in external bus mode.                        |  |  |

|             |             | P22             |         | General-purpose I/O port. When the bits of high address control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports.  |  |  |

| 44          | 43          | TIN1            | D       | Functions as event input pin of TIN1 reload timer 1. Set this to input port.                                                                                            |  |  |

|             |             | A18             |         | Output pin of external address bus (A18) . Only valid when the bits of high address control register (HACR) are set to "0" in external bus mode.                        |  |  |

|             |             | P23             |         | General-purpose I/O port. When the bits of high address control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports.  |  |  |

| 45          | 44          | TOT1            | D       | Functions as event output pin for TOT1 reload timer 1. Only valid if output configuration enabled.                                                                      |  |  |

|             |             | A19             |         | Output pin for external address bus (A19). Only valid when the bits of high address control register (HACR) are set to "0" in external bus mode.                        |  |  |

### (Continued)

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No.         | Din Nama     | Circuit | Description                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M09         | Pin Name     | Туре    | Description                                                                                                                                                            |

| 40.45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45.45       | P24 to P27   |         | General-purpose I/O port. When the bits of high address control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports. |

| 46 to<br>49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45 to<br>48 | INT4 to INT7 | D       | Functions as external interrupt input pin. Set this to input port.                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | A20 to A23   |         | Output pin for external address bus (A20 to A23) . Only valid when the bits of high address control register (HACR) are set to "0" in external bus mode.               |

| 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49          | Vss          |         | Power supply (0 V) input pin.                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | P30          |         | General-purpose I/O port. Only enabled in single-chip mode.                                                                                                            |

| 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50          | SOT0         | D       | UART0 serial data output pin. Only valid if UART0 serial data output configuration is enabled.                                                                         |

| AL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             | ALE          |         | Address latch authorization output pin. Only enabled during external bus mode.                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | P31          |         | General-purpose I/O port. Only enabled in single-chip mode.                                                                                                            |

| 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52 51       | SCK0         | D       | UART0 serial clock I/O pin. Only valid if UART0 serial clock I/O configuration is enabled.                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | RD           |         | Lead strobe output pin. Only enabled during external bus mode.                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | P32          |         | General-purpose I/O port.                                                                                                                                              |

| 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52          | SIN0         | D       | UART0 serial data input pin.<br>Set this to input port.                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | WRL          |         | Write strobe output pin for lower 8-bit of data bus. Only valid if WRL pin output is enabled, in external bus mode.                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | P33          |         | General-purpose I/O port.                                                                                                                                              |

| 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53          | WRH          | D       | Write strobe output pin for upper 8-bit of data bus. Only valid if external bus mode/16-bit bus mode/WRH pin output enabled.                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | P34          |         | General-purpose I/O port.                                                                                                                                              |

| 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54          | HRQ          | D       | Hold request input pin. Only valid if hold input is enabled, in external bus mode.                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | P35          |         | General-purpose I/O port.                                                                                                                                              |

| 56 This is the state of the sta |             |              |         |                                                                                                                                                                        |

| 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56          | Vcc          | _       | Power supply (5 V) input pin.                                                                                                                                          |