# M66591GP

ASSP (USB2.0 Peripheral Controller)

REJ03F0101-0100Z Rev.1.00 Nov. 30, 2004

# 1 Overview

#### 1.1 Overview

The M66591 is a general-purpose USB (Universal Serial Bus) device controller compliant with the Universal Serial Bus Specification Revision 2.0 and supports both Hi-Speed and Full-Speed transfer.

The USB Hi-Speed and Full-Speed transceiver are built-in, and the M66591 meets control, bulk and interrupt transfer types which are defined in the Universal Serial Bus Specification Revision 2.0.

The M66591 has a 3.5K byte FIFO and 7 endpoints (maximum) for data transfer.

Further, being equipped with the split bus (DMA interface) which is independent from the CPU bus interface, the M66591 is suitable for use in systems that require large capacity data transfer at Hi-Speed.

#### 1.2 Features

- ♦ Universal Serial Bus Specification Revision 2.0 compliant

- ♦ Built-in USB transceiver

- ♦ Supports both Hi-Speed (480M bps) and Full-Speed (12M bps)

- USB protocol layer by hardware

- · Bit stuffing encoding and decoding

- CRC (Cyclic Redundancy Check) generation and checking

- NRZI (Non Return Zero Invert) encoding and decoding

- · Packet detection

- USB address checking

- ♦ Hi-Speed and Full-Speed detection by hardware

- ♦ Supports the following USB transfer types

- Control transfer (PIPE0)

- Bulk transfer (PIPE1~PIPE4)

- Interrupt transfer (PIPE5~PIPE6)

- ♦ Built-in FIFO buffer (3.5K bytes) for endpoints

- ♦ Up to 7 endpoints selectable

- ♦ Data transfer condition selectable for each PIPE

- Hi-Speed

- PIPEO: Control transfer, continuous transfer mode, 256-byte FIFO

- PIPE1~2: Bulk in or bulk out transfer, 512-byte FIFO, double buffer

- PIPE3~4: Bulk in or bulk out transfer, 512-byte FIFO, single buffer

- PIPE5~6: Interrupt in transfer, 64-byte FIFO, single buffer

- Full-Speed

- PIPE0: Control transfer, continuous transfer mode, 256-byte FIFO

- PIPE1~2: Bulk in or bulk out transfer, continuous transfer mode, 512-byte FIFO, double buffer

- PIPE3~4: Bulk in or bulk out transfer, continuous transfer mode, 512-byte FIFO, single buffer

- PIPE5~6: Interrupt in transfer, 64-byte FIFO, single buffer

- ♦ Automatic response for Set Address request

- ♦ Supports the following input frequency

- 12 / 24 / 48MHz

- ♦ Supports 16-bit CPU I/F and 8/16-bit DMA transfer

- ♦ Supports separate/multiplex bus

- 16-bit separate/multiplex bus

- ♦ Supports 8-bit split bus (DMA interface)

- ♦ USB status output for power management

- ♦ 1.8V/3.3V interface power supply

- ♦ Application

- Digital camera, printer, external storage device and all Hi-Speed USB PC peripheral device

# 1.3 Pin Configuration

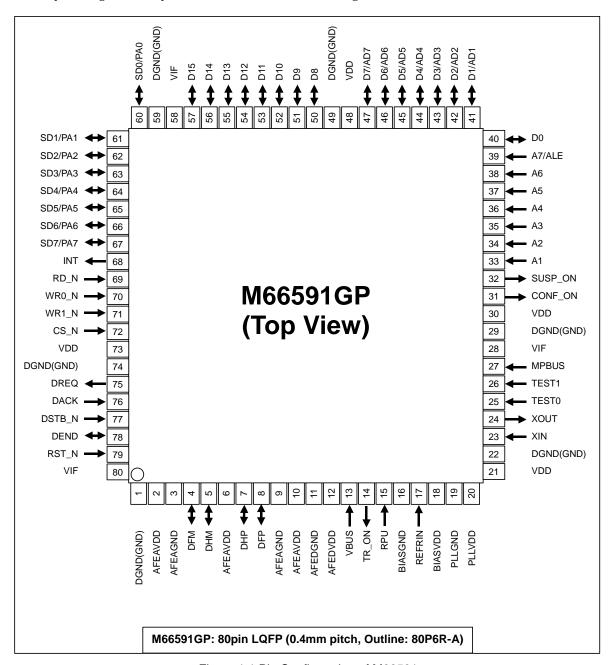

The pin configuration (top view) of the M66591 is shown in Figure 1.1.

Figure 1.1 Pin Configuration of M66591

The pin functions of the M66591 are shown in Table 1.1.

Table 1.1 Pin Functions of M66591

|           |               |                  | Table 1.1 FIII FUNCTIONS OF WIGOS91                                                   |              |

|-----------|---------------|------------------|---------------------------------------------------------------------------------------|--------------|

| Item      | Pin Name      | Input/Output     | Name / Function                                                                       | Pin<br>Count |

| CPU       | D15-D8        | Input/Output     | Data Bus                                                                              | 8            |

| interface |               |                  | These are data bus to access the registers from the CPU.                              |              |

|           | D7/AD7-D1/AD  | Input/Output     | Data Bus / Address Bus                                                                | 8            |

|           | 1, D0         |                  | When select to 16-bit separate bus, these pins are used as D7-D0 of data bus.         |              |

|           |               |                  | When select to 16-bit multiplex bus, D7-D0 input/output and AD7-AD1 input are         |              |

|           |               |                  | performed at time-sharing. In this case, AD0 is not used.                             |              |

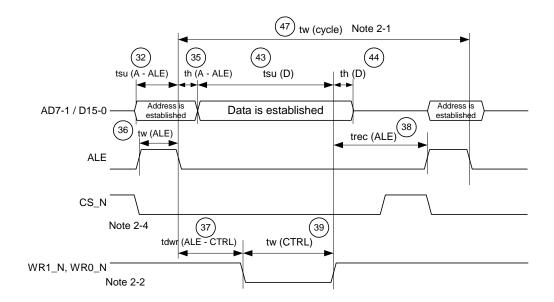

|           | A7/ALE, A6-A1 | Input            | Address Bus / Address Latch Enable                                                    | 7            |

|           | ·             | ·                | When select to 16-bit separate bus, these pins are address bus to access the          |              |

|           |               |                  | registers from the CPU.                                                               |              |

|           |               |                  | When select to 16-bit multiplex bus, A7 becomes the ALE pin, latching addresses       |              |

|           |               |                  | at the falling edge. A6-A1 are not used.                                              |              |

|           | CS_N          | Input            | Chip Select                                                                           | 1            |

|           | 00_1          | mpat             | When this pin is low level, M66591 is selected.                                       | '            |

|           | DD N          | la a t           | Read Strobe                                                                           | 1            |

|           | RD_N          | Input            |                                                                                       | '            |

|           | 14/D4 N       |                  | Data are read from registers at low level.                                            |              |

|           | WR1_N         | Input            | D15-D8 Byte Write Strobe                                                              | 1            |

|           |               |                  | The data (D15-D8) are written to the registers at the rising edge.                    |              |

|           | WR0_N         | Input            | D7-0 Byte Write Strobe                                                                | 1            |

|           |               |                  | The data (D7-D0) are written to the registers at the rising edge.                     |              |

|           | MPBUS         | Input            | Bus Mode Select                                                                       | 1            |

|           |               |                  | The 16-bit separate bus is selected at low level.                                     |              |

|           |               |                  | The 16-bit multiplex bus is selected at high level.                                   |              |

|           |               |                  | This pin should not be switched after H/W reset.                                      |              |

| Interrupt | INT           | Output           | Interrupt                                                                             | 1            |

| interface |               |                  | Interrupts are requested to the CPU. Polarity of this pin can be selected by register |              |

|           |               |                  | setting.                                                                              |              |

| DMA       | SD7/PA7-SD0/  | Input/Output     | Split Bus / General-purpose Port                                                      | 8            |

| interface | PA0           |                  | These pins are used to select either split bus (DMA Interface) or general-purpose     |              |

| mionaco   | 1710          |                  | port (GPIO).                                                                          |              |

|           | DREQ          | Output           | DMA Request                                                                           | 1            |

|           | DILLO         | Output           | This pin is used to request DMA transfer of the D0_FIFO port. Polarity of this pin    | '            |

|           |               |                  | can be selected by register setting.                                                  |              |

|           | DACK          | la a v st        |                                                                                       | 1            |

|           | DACK          | Input            | DMA Acknowledge                                                                       |              |

|           |               |                  | DMA transfer of the D0_FIFO port is enabled in either low or high level. Polarity of  |              |

|           |               |                  | this pin can be selected by register setting.                                         |              |

|           | DSTB_N        | Input            | Split Bus Strobe                                                                      | 1            |

|           |               |                  | This pin is used as data strobe signal when the D0_FIFO port has been set to the      |              |

|           |               |                  | split bus (DMA Interface).                                                            |              |

|           |               |                  | When the RWstb bit of the Data Pin & FIFO/DMA Control Pin Configuration               |              |

|           |               |                  | Register 2 is set to "1" (RD/WR strobe mode), this pin is used as data strobe signal. |              |

|           | DEND          | Input/Output     | Transfer Terminal                                                                     | 1            |

|           |               |                  | When the PIPE direction is "IN", this pin receives transfer complete signal as an     |              |

|           |               |                  | input signal from any other peripheral chip or the CPU.                               |              |

|           |               |                  | When the PIPE direction is "OUT", this pin indicates the last data transferred as the |              |

|           |               |                  | output signal. Polarity of this pin can be set by a register.                         |              |

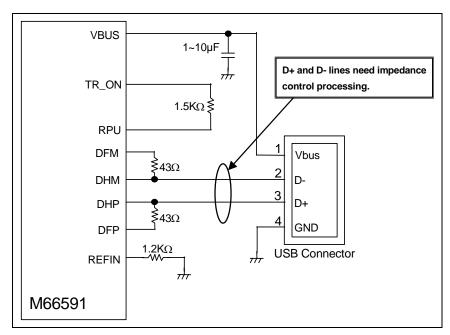

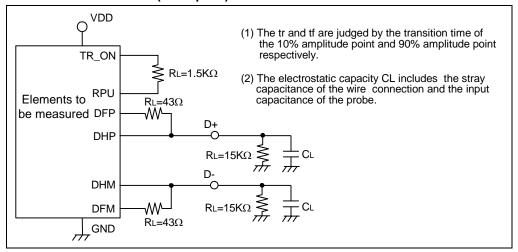

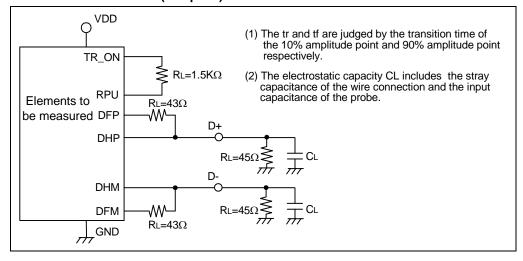

| USB       | DHP           | Input/Output     | USB Hi-Speed Data                                                                     | 1            |

| interface |               |                  | Connect the D+ signal of USB bus.                                                     |              |

|           | DHM           | Input/Output     | USB Hi-Speed Data                                                                     | 1            |

|           | 5             | Inpat Output     | Connect the D- signal of USB bus.                                                     | '            |

|           | DFP           | Input/Output     | USB Full-Speed Data                                                                   | 1            |

|           |               | inputOutput      | ·                                                                                     | '            |

|           | DEM           | In must/Contract | Connect this pin to DHP via a 43Ω 1% resistance.                                      | _            |

|           | DFM           | Input/Output     | USB Full-Speed Data                                                                   | 1            |

|           |               |                  | Connect this pin to DHM via a $43\Omega$ 1% resistance.                               | ĺ            |

| Item              | Pin Name   | Input/Output | Name / Fun                                                                                                                                      | ction                                                                        | Pin<br>Count |  |  |  |  |  |

|-------------------|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------|--|--|--|--|--|

|                   | RPU        | Input        | Pull-up Con                                                                                                                                     | ntrol s pin to TR_ON pin via a 1.5K $\Omega$ 5% resistance.                  | 1            |  |  |  |  |  |

|                   | TR_ON      | Output       |                                                                                                                                                 | wer Supply Output                                                            | 1            |  |  |  |  |  |

|                   | _          | · ·          |                                                                                                                                                 | supply output for pull-up. This supply internally converts VBUS input        |              |  |  |  |  |  |

|                   |            |              | from 5V to 3                                                                                                                                    | 3.3V and outputs it.                                                         |              |  |  |  |  |  |

|                   | VBUS       | Input        | VBUS Inpu                                                                                                                                       | t                                                                            | 1            |  |  |  |  |  |

|                   |            |              |                                                                                                                                                 | the Vbus of USB bus. Connection or shutdown of the Vbus can be               |              |  |  |  |  |  |

|                   |            |              | detected.                                                                                                                                       |                                                                              |              |  |  |  |  |  |

|                   | REFRIN     | Input        | Reference                                                                                                                                       | •                                                                            | 1            |  |  |  |  |  |

| LICD status       | CONE ON    | Outout       |                                                                                                                                                 | s pin to BIASGND via a 1.2KΩ 1% resistance.                                  | 1            |  |  |  |  |  |

| USB status output | CONF_ON    | Output       | USB Configured Output  This pin is used to indicate the transition to configured state. This pin is N-ch open drain output.  USB Suspend Output |                                                                              |              |  |  |  |  |  |

| σαιραι            |            |              |                                                                                                                                                 |                                                                              |              |  |  |  |  |  |

|                   | SUSP_ON    | Output       |                                                                                                                                                 |                                                                              |              |  |  |  |  |  |

|                   |            | 3 3 4 3 3    | This pin is used to indicate the transition to suspend state. This pin is N-ch open drain output.                                               |                                                                              |              |  |  |  |  |  |

|                   |            |              |                                                                                                                                                 |                                                                              |              |  |  |  |  |  |

| Clock             | XIN        | Input        | Oscillator                                                                                                                                      | These pins are used to input/output the signals of internal clock            | 1            |  |  |  |  |  |

|                   |            |              | Input                                                                                                                                           | oscillation circuits. Connect a crystal unit between Xin and Xout pins.      |              |  |  |  |  |  |

|                   | XOUT       | Output       | Oscillator                                                                                                                                      | If an external clock signal is used, input it to the Xin pin. Leave Xout     |              |  |  |  |  |  |

|                   |            |              | Output                                                                                                                                          | open.                                                                        |              |  |  |  |  |  |

| System            | RST_N      | Input        | Reset                                                                                                                                           |                                                                              | 1            |  |  |  |  |  |

| control           |            |              |                                                                                                                                                 | used to initialize the values of the internal register or the counter at low |              |  |  |  |  |  |

|                   | TEST1-0    | Input        | level.                                                                                                                                          |                                                                              | 2            |  |  |  |  |  |

|                   | 12311-0    | lliput       |                                                                                                                                                 | are input for the test. Fix to low level or keep open.                       | 2            |  |  |  |  |  |

| Power             | AFEAVDD    | Input        | - <del> </del>                                                                                                                                  | wer Supply                                                                   | 3            |  |  |  |  |  |

| supply            | 7 27.17.22 |              |                                                                                                                                                 | the 3.3V power supply.                                                       |              |  |  |  |  |  |

| ,                 | AFEAGND    | Input        | Analog Gro                                                                                                                                      |                                                                              | 2            |  |  |  |  |  |

|                   | AFEDVDD    | Input        | USB Trans                                                                                                                                       | ceiver Digital Power Supply                                                  | 1            |  |  |  |  |  |

|                   |            |              | Connect to                                                                                                                                      | the 3.3V power supply.                                                       |              |  |  |  |  |  |

|                   | AFEDGND    | Input        | USB Trans                                                                                                                                       | ceiver Digital Power Ground                                                  | 1            |  |  |  |  |  |

|                   | BIASVDD    | Input        | BIAS Powe                                                                                                                                       | er Supply                                                                    | 1            |  |  |  |  |  |

|                   |            |              |                                                                                                                                                 | the 3.3V power supply.                                                       |              |  |  |  |  |  |

|                   | BIASGND    | Input        | BIASGND                                                                                                                                         |                                                                              | 1            |  |  |  |  |  |

|                   | PLLVDD     | Input        | PLL Power                                                                                                                                       | • • •                                                                        | 1            |  |  |  |  |  |

|                   | DI LOND    | la a cot     |                                                                                                                                                 | the 3.3V power supply.                                                       |              |  |  |  |  |  |

|                   | PLLGND     | Input        | PLLGND 1 Core Power Supply 4                                                                                                                    |                                                                              |              |  |  |  |  |  |

|                   | VDD        | Input        |                                                                                                                                                 | r Suppiy<br>the 3.3V power supply.                                           | 4            |  |  |  |  |  |

|                   | VIF        | Input        | IO Power S                                                                                                                                      | Supply                                                                       | 3            |  |  |  |  |  |

|                   |            |              | Connect to                                                                                                                                      | the 1.8V or 3.3V power supply.                                               |              |  |  |  |  |  |

|                   | DGND       | Input        | Digital Gro                                                                                                                                     | und                                                                          | 6            |  |  |  |  |  |

The care method of non-used pin of M66591 are shown in Table 1.2.

Table 1.2 The care method of non-used pin of M66591

|                   | Table 1.2 The care i | method of hon-used pin of Moose i              |

|-------------------|----------------------|------------------------------------------------|

| Item              | Pin Name             | Care Method                                    |

| CPU interface     | A6-A1                | Open                                           |

| DMA interface     | SD7/PA7-SD0/PA0      | Pull-up or pull-down or setting to output port |

|                   | DREQ                 | Open                                           |

|                   | DACK, DEND           | Pull-up or pull-down or connect to VIF         |

|                   | DSTB_N               | Pull-up or connect to VIF                      |

| System control    | TEST1-0              | Open or connect to GND                         |

| USB status output | CONF_ON, SUSP_ON     | Open                                           |

## 1.4 Pin Functions

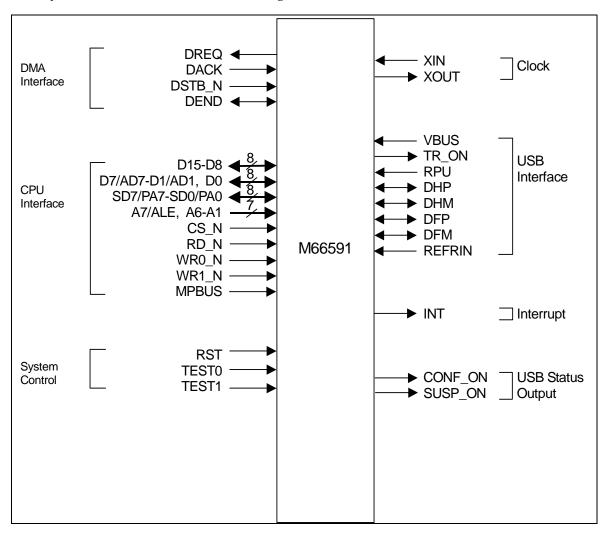

The pin functions of the M66591are shown in Figure 1.2.

Figure 1.2 Pin Function Diagram of M66591

# 1.5 Block Diagram

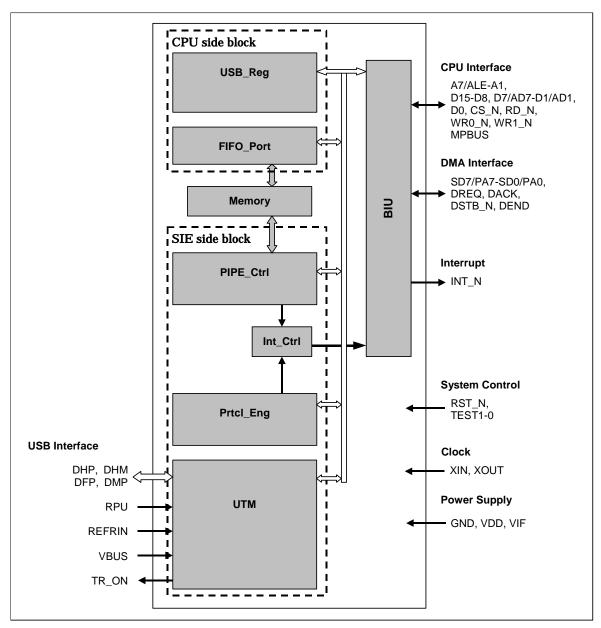

M66591 contains four blocks, SIE (Serial Interface Engine) side block and CPU side block and bus interface unit (BIU) and FIFO memory. SIE side block includes USB transceiver (UTM), protocol engine (Prtcl\_Eng), PIPE controller (PIPE\_Ctrl), and interrupt controller (Int\_Ctrl). CPU side block includes FIFO port (FIFO\_Port), and register block (USB\_Reg).

The block diagram of M66591 is shown in Figure 1.3.

Figure 1.3 Block Diagram of M66591

# 2 Registers

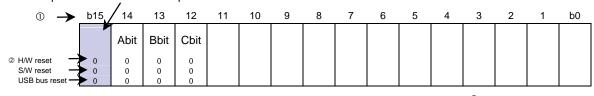

# **How to Read Register Tables**

① Bit Numbers: Each register is connected with an internal bus of 16-bit wide, so the bit numbers of the

registers located at odd addresses are b15-b8, and those at even addresses are b7-b0.

② State of Register at Reset:

Represents the initial state of each register immediately after reset with hexadecimal numbers.

The "H/W reset" is the reset by an external reset signal; the "S/W reset" is the reset by the

USBE bit of the USB Operation Enable Register.

3 At Read: O ... Read enabled

? ... Read disabled (Read value invalid)

0 ... Read always as 01 ... Read always as 1

At Write:

O ... Write enabled

$\Delta \;\; \dots$  Write enable conditionally (includes some conditions at write)

- ... Write disabled (Don't care "0" and "1" at write)

X ... Write disabled

<Example of representation>

Not implemented in the shaded portion.

<H/W reset: H'0000>

<S/W reset: ->

<USB bus reset: ->

| b  | Bit name  | Function | R | W |

|----|-----------|----------|---|---|

| 15 | Reserved. |          | 0 | - |

| 14 | A bit     | 0:       | 0 | 0 |

|    | ()        | 1:       |   |   |

| 13 | B bit     | 0:       | 0 | 0 |

|    | ()        | 1:       |   |   |

| 12 | C bit     | 0:       | Ó | Ō |

|    | ()        | 1:       | ↑ | ↑ |

|    |           |          | 3 | 4 |

# 2.1 Register Mapping

M66591 register mapping is shown in Figure 2.1, Figure 2.2 and Figure 2.3, each register is described below.

| Address  | +1 ad | dress          | +0 ac           | ddress |       | Reset state |           |           |  |  |

|----------|-------|----------------|-----------------|--------|-------|-------------|-----------|-----------|--|--|

|          | b15   | b8             | b7              |        | 00    | H/W         | S/W       | USB bus   |  |  |

| H'00     | USI   | B Transceiver  | Control Regist  | er 0   |       | 0000h       | -         | -         |  |  |

| H'02     |       |                | Control Regist  |        |       | 0000 0000   |           |           |  |  |

|          |       |                | J               |        |       | 0100        | ??b       | 00b       |  |  |

|          |       |                |                 |        |       | 00??b       |           |           |  |  |

| H'04     |       | HS/FS Mod      | de Register     |        |       | 0000h       | -000 0000 | -000 0000 |  |  |

|          |       |                |                 |        |       | 0000        | 0000 00b  |           |  |  |

|          |       |                |                 |        |       |             | 0000b     |           |  |  |

| H'06     |       | Test Mode      | e Register      |        |       | 0000h       | 0000h     | 00        |  |  |

| <br>     |       |                |                 |        |       |             |           | b         |  |  |

| H'08     | Da    | ita Pin & FIFO | DMA Control F   | Pin    |       | 00??h       | -         | -         |  |  |

| <br>     |       | Configuratio   | n Register 0    |        |       |             |           |           |  |  |

| H'0A     | Da    | ita Pin & FIFO | DMA Control F   |        | 0000h | -           | -         |           |  |  |

|          |       | Configuratio   | n Register 1    |        |       |             |           |           |  |  |

| H'0C     | Da    |                | DMA Control F   | Pin    |       | 0000h       | -         | -         |  |  |

|          |       | Configuratio   | n Register 2    |        |       |             |           |           |  |  |

| H'0E     |       |                |                 |        |       |             |           |           |  |  |

| H'10     |       |                |                 |        |       |             |           |           |  |  |

| H'12     |       |                |                 |        |       |             |           |           |  |  |

| H'14     |       | C_FIFO Poi     | rt Register 0   |        |       | 0000h       | ????h     | -         |  |  |

| H'16     |       |                |                 |        |       |             |           |           |  |  |

| H'18     |       | D0_FIFO Po     | rt Register 0   |        |       | 0000h       | ????h     | -         |  |  |

| H'1A     |       |                |                 |        |       |             |           |           |  |  |

| H'1C     |       |                |                 |        |       |             |           |           |  |  |

| H'1E     |       |                |                 |        |       |             |           |           |  |  |

| H'20     |       |                |                 |        |       |             |           |           |  |  |

| H'22     |       |                |                 |        |       |             |           |           |  |  |

| H'24     |       |                |                 |        |       |             |           |           |  |  |

| H'26     |       | DCP Continu    | ous Transmit    |        |       | 0000h       | 0000h     | -         |  |  |

| <u>_</u> |       | Data Leng      | th Register     |        |       |             |           |           |  |  |

| H'28     | С     | _FIFO Port Co  | ontrol Register | 0      |       | 0000h       | 0000h     | -         |  |  |

| H'2A     |       |                |                 |        |       |             |           |           |  |  |

| H'2C     | С     | _FIFO Port Co  | ontrol Register | 1      |       | 0000h       | 0000h     | -         |  |  |

| H'2E     | С     | _FIFO Port Co  | ontrol Register | 2      |       | 0000h       | 0000h     | -         |  |  |

| H'30     | D     | D_FIFO Port C  | ontrol Register | r 0    |       | 0000h       | 0000h     | -         |  |  |

| H'32     |       |                |                 |        |       |             |           |           |  |  |

| H'34     | D     | D_FIFO Port C  | ontrol Register | r 2    |       | 0000h       | 0000h     | -         |  |  |

| H'36     | D     | D_FIFO Port C  | ontrol Register | r 3    |       | 0000h       | 0000h     | -         |  |  |

| H'38     |       |                |                 |        |       |             |           |           |  |  |

| H'3A     |       |                |                 |        |       |             |           |           |  |  |

| H'3C     |       |                |                 |        |       |             |           |           |  |  |

| H'3E     |       |                |                 |        |       |             |           |           |  |  |

| H'40     | IN    | IT Pin Configu | ration Register | . 0    |       | 0000h       | 0000h     | -         |  |  |

| H'42     | IN    | IT Pin Configu | ration Register | 1      |       | 0000h       | -         | -         |  |  |

| H'44     | IN    | IT Pin Configu | ration Register | 2      |       | 0000h       | 0000h     | -         |  |  |

| H'46     |       |                |                 |        |       |             |           |           |  |  |

Note: Refer to each register described below.

Figure 2.1 Register Mapping (1)

| Address | +1 address                                                                                                     | +0 address        |           | Reset state |         |

|---------|----------------------------------------------------------------------------------------------------------------|-------------------|-----------|-------------|---------|

|         | b15 b8                                                                                                         | b7 b0             | H/W       | S/W         | USB bus |

| H'48    | INT Pin Configur                                                                                               | ation Register 3  | 0000h     | 0000h       | -       |

| H'4A    |                                                                                                                |                   |           |             |         |

| H'4C    | INT Pin Configur                                                                                               | ation Register 4  | 0000h     | 0000h       | -       |

| H'4E    |                                                                                                                |                   |           |             |         |

| H'50    |                                                                                                                |                   |           |             |         |

| H'52    |                                                                                                                |                   |           |             |         |

| H'54    |                                                                                                                |                   |           |             |         |

| H'56    |                                                                                                                |                   |           |             |         |

| H'58    |                                                                                                                |                   |           |             |         |

| H'5A    |                                                                                                                |                   |           |             |         |

| H'5C    |                                                                                                                |                   |           |             |         |

| H'5E    |                                                                                                                |                   |           |             |         |

| H'60    | Interrupt Statu                                                                                                | us Register 0     | 0000 0000 | 0000 0000   | 1       |

|         |                                                                                                                |                   | ?000      | ?000        | -001l   |

|         |                                                                                                                |                   | 0000b     | 0000b       |         |

| H'62    |                                                                                                                |                   |           |             |         |

| H'64    | Interrupt Statu                                                                                                | ıs Register 1     | 0000h     | 0000h       | -       |

| H'66    |                                                                                                                |                   |           |             |         |

| H'68    | Interrupt Statu                                                                                                | ıs Register 2     | 0000h     | 0000h       |         |

| H'6A    |                                                                                                                |                   |           |             |         |

| H'6C    | Interrupt Statu                                                                                                | ıs Register 3     | 0000h     | 0000h       | -       |

| H'6E    |                                                                                                                |                   |           |             |         |

| H'70    |                                                                                                                |                   |           |             |         |

| H'72    |                                                                                                                |                   |           |             |         |

| H'74    | USB Addres                                                                                                     | ss Register       | 0000h     | 0000h       | 0000h   |

| H'76    |                                                                                                                |                   |           |             |         |

| H'78    | USB Reques                                                                                                     | t Register 0      | 0000h     | 0000h       | 0000h   |

| H'7A    | USB Reques                                                                                                     |                   | 0000h     | 0000h       | 0000h   |

| H'7C    | USB Reques                                                                                                     | t Register 2      | 0000h     | 0000h       | 0000h   |

| H'7E    | USB Reques                                                                                                     |                   | 0000h     | 0000h       | 0000h   |

| H'80    | ·                                                                                                              | - J               |           |             |         |

| H'82    | DCP Configura                                                                                                  | tion Register 1   | 0000h     | 0000h       | -       |

| H'84    | DCP Configura                                                                                                  |                   | 0000h     | 0000h       | -       |

| H'86    |                                                                                                                |                   |           |             |         |

| H'88    | DCP Contro                                                                                                     | ol Register       | 0000h     | 0000h       |         |

|         |                                                                                                                | 5                 |           |             | 0001    |

| H'8A    |                                                                                                                |                   |           |             |         |

| H'8C    | PIPE Configuratio                                                                                              | n Select Register | 0000h     | 0000h       | -       |

| H'8E    | , and the second se |                   |           |             |         |

| H'90    | PIPE Configuration                                                                                             | Window Register 0 | 0000h     | 0000h       | 00      |

|         | <b>y</b>                                                                                                       | Ŭ                 |           |             | b       |

| H'92    |                                                                                                                |                   |           |             |         |

| H'94    |                                                                                                                |                   |           |             |         |

| H'96    |                                                                                                                |                   |           |             |         |

| H'98    |                                                                                                                |                   |           |             |         |

|         |                                                                                                                |                   |           |             |         |

Figure 2.2 Register Mapping (2)

| Address | +1 a | ddress    | +0 ac         | ldress |       | Reset state |         |

|---------|------|-----------|---------------|--------|-------|-------------|---------|

|         | b15  | b8        | b7            | b0     | H/W   | S/W         | USB bus |

| H'9A    |      |           |               |        |       |             |         |

| H'9C    |      |           |               |        |       |             |         |

| H'9E    |      |           |               |        |       |             |         |

| H'A0    |      | PIPE1 Con | trol Register |        | 0000h | 0000h       |         |

|         |      |           |               |        |       |             | 00b     |

| H'A2    |      | PIPE2 Con | trol Register |        | 0000h | 0000h       |         |

|         |      |           |               |        |       |             | 00b     |

| H'A4    |      | PIPE3 Con | trol Register |        | 0000h | 0000h       |         |

|         |      |           |               |        |       |             | 00b     |

| H'A6    |      | PIPE4 Con | trol Register |        | 0000h | 0000h       |         |

|         |      |           |               |        |       |             | 00b     |

| H'A8    |      | PIPE5 Con | trol Register |        | 0000h | 0000h       |         |

|         |      |           |               |        |       |             | 00b     |

| H'AA    |      | PIPE6 Con | trol Register |        | 0000h | 0000h       |         |

|         |      |           |               |        |       |             | 00b     |

Note: Refer to each register described below.

Figure 2.3 Register Mapping (3)

# 2.2 Register Bit Map

|          |           |            | Odd nu            | ımber a   | address        | (001h)     |           |         | Even number address (000h) |         |         |           |          |       |          |         |

|----------|-----------|------------|-------------------|-----------|----------------|------------|-----------|---------|----------------------------|---------|---------|-----------|----------|-------|----------|---------|

|          | 15        | 14         | 13                | 12        | 11             | 10         | 9         | 8       | 7                          | 6       | 5       | 4         | 3        | 2     | 1        | 0       |

| USB Tra  | ansceiver | Control    | Registe           | r 0 (USE  | TrnsCtrl       | 0)         |           |         |                            |         |         |           |          |       |          |         |

| 0 0      | XTAL      | _ [1:0]    | XCKE              | RCKE      | PLLC           | SCKE       |           |         | HSE                        |         |         | RpuE      |          |       |          | USBE    |

| USB Tra  | ansceiver | Control    | Registe           | r 1 (USE  | TrnsCtrl       | 1)         |           |         |                            |         |         |           |          |       |          |         |

| 0 2      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       | LNS      | T [1:0] |

| HS/FS I  | Mode Reg  | gister (H  | SFSMod            | e)        |                |            |           | 1       |                            |         |         |           |          |       |          |         |

| 0 4      |           |            |                   |           |                |            |           | WKUP    |                            |         |         |           |          |       | RHS      | T [1:0] |

| Test Mo  | de Regis  | ter (Test  | tMd)              |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 0 6      | SUSPEN    | CONFEN     |                   |           |                |            |           |         |                            |         |         |           |          |       | TST [2:0 | )]      |

| Data Pir | & FIFO/   | DMA Co     | ntrol Pir         | Config    | uration F      | Register ( | ) (PinCtı | (ICfg0  | 1                          |         |         |           |          |       |          |         |

| 0 8      |           |            |                   |           |                |            |           |         |                            |         |         | PA [      | [7:0]    |       |          |         |

| Data Pir | & FIFO/   | DMA Co     | ontrol Pir        | Config    | uration F      | egister '  | 1 (PinCtı | (Cfg1)  |                            |         |         |           |          |       |          |         |

| 0 A      | LDRV      |            |                   |           |                |            |           | big_end |                            |         |         |           |          | PAdir |          | DB_Cfg  |

| Data Pir | n & FIFO/ | DMA Co     | ontrol Pir        | Config    | uration F      | Register 2 | 2 (PinCtı | (Cfg2)  |                            | 1       | 1       | ı         |          |       |          |         |

| 0 C      |           | DreqA      | Burst             | DreqE     |                | DackA      | RWstb     | DackE   |                            | DendA   | Pktmd   | DendE     |          | Obus  |          |         |

| 0 E      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 1 0      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 1 2      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

|          | Port Reg  | gister 0 ( | C_FIFOI           | Port0)    |                |            |           |         |                            |         |         |           |          |       |          |         |

| 1 4      |           | 1          |                   |           |                |            | C         | _FIFO_F | Port [15:0                 | 0]<br>I |         |           |          |       |          |         |

| 1 6      |           |            | /= = <b>-</b>     |           |                |            |           |         |                            |         |         |           |          |       |          |         |

|          | O Port Re | egister 0  | (D0_FIF           | OPort0)   | 1              |            |           |         | D                          |         |         |           |          |       |          |         |

| 1 8      |           |            |                   |           |                |            | D(        | _FIFO_  | Port [15:                  | :0]<br> |         |           |          |       |          |         |

| 1 A      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 1 C      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 1 E      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 2 0      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 2 2      |           |            |                   |           |                |            |           |         |                            |         |         |           |          |       |          |         |

| 2 4      | ntinuous  | Transmi    | it Doto I         | on ath D  | ogiotor (      | DCDS41*    | -/        |         |                            |         |         |           |          |       |          |         |

| 2 6      | ontinuous | Transm     | li Dala L         | engin K   | egister (      | DCPSuii    | 1)        |         |                            |         |         | DLN [8:0  | <b>1</b> |       |          |         |

|          | Port Cor  | trol Poo   | istor 0 ((        | C EIEOI   | PortCtrl0      | \          |           |         |                            |         |         | DLIN [O.  | J]       |       |          |         |

| 2 8      | RCNT      | REW        | ister 0 (t        | 5_FIFOI   | - OTICITO      | MBW        |           |         |                            |         | ISEL    |           |          | Curre | ent_PIPI | E [3:0] |

| 2 A      | KCIVI     | KEVV       |                   |           |                | IVIDVV     |           |         |                            |         | ISEL    |           |          | Curre | III_FIFI | [2.0]   |

|          | Port Cor  | trol Rea   | istor 1 <i>((</i> | FIFO      | <br>Port€trl1  | )          |           |         |                            |         |         |           |          |       |          |         |

| 2 C      | BVAL      | 1          | FRDY              | J_1 11 OI | SHOUT          | ,          |           |         |                            |         | בט וופט | LN [9:0]  | 1        |       |          |         |

|          | Port Cor  | L          |                   | C FIFO    | l<br>PortCtrl? | )          |           |         |                            | '       | O. O_D1 | _14 [3.0] | 1        |       |          |         |

| 2 E      | TGL       |            | SBUSY             | J_1 11 OI | JILOUIZ        | ,          |           |         |                            |         |         |           |          |       |          |         |

| _ L      | IGL       | JOLK       | 30031             |           |                |            |           |         |                            |         |         |           |          |       |          |         |

|           |                 |            | )dd pu     | mhoro     | ddroo         | . (001) | .,        | Even number address (000h) |          |                |                |                |       |                |                |             |

|-----------|-----------------|------------|------------|-----------|---------------|---------|-----------|----------------------------|----------|----------------|----------------|----------------|-------|----------------|----------------|-------------|

|           | 45              |            | Odd nu     |           |               |         | ĺ         | 0                          |          |                |                |                |       |                |                |             |

| DO EIEC   | 15<br>O Port Co | 14         | 13         | 12        | 11<br>OPortCt | 10      | 9         | 8                          | 7        | 6              | 5              | 4              | 3     | 2              | 1              | 0           |

| 3 0       | RCNT            | REW        | ABCR       | (DU_FIF   | OFUIC         | MBW     | TREnb     | TRclr                      |          |                |                |                |       | Curre          | ent_PIPE       | [0.0]       |

| 3 2       | TON             | TKEVV      | ABOR       |           |               | WIDVV   | TIVELID   | TTOIL                      |          |                |                |                |       | Odire          | )              | . [2.0]     |

|           | D Port Co       | ntrol Re   | gister 2   | (D0 FIF   | OPortCt       | rl2)    |           |                            |          |                |                |                |       |                |                |             |

| 3 4       | BVAL            |            | FRDY       | _         |               |         |           |                            |          | ı              | DMA_D          | ΓLN [9:0       | ]     |                |                |             |

| D0_FIFC   | O Port Co       | ntrol Re   | gister 3   | (D0_FIF   | OPortCt       | rl3)    |           |                            |          |                |                |                |       |                |                |             |

| 3 6       |                 |            |            |           |               |         |           | TRNCN                      | T [15:0] |                |                |                |       |                |                |             |

| 3 8       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 3 A       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 3 C       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 3 E       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

|           | Configura       |            | gister 0 ( |           |               |         | I <u></u> |                            |          | I              | l              | I              |       | T              | l              |             |

| 4 0       |                 | RSME       | -1-14 (    | DVSE      |               | BEMPE   | INTNE     | INTRE                      | URST     | SADR           | SCFG           | SUSP           | WDST  | RDST           | CMPL           | SERR        |

| 4 2       | Configura       | ation Re   | gister 1 ( | INTPINC   | Jig1)         |         |           |                            |          |                |                |                |       |                | INTL           | INTA        |

|           | Configura       | ation Re   | nistar 2 ( | INTPinC   | `fa2\         |         |           |                            |          |                |                |                |       |                | IINIL          | INTA        |

|           | Comigare        | ation reg  | gister Z ( | 114111111 | ngz)          |         |           |                            |          | PIPEB          | PIPEB          | PIPEB          | PIPEB | PIPEB          | PIPEB_         | DCP_        |

| 4 4       |                 |            |            |           |               |         |           |                            |          | RE6            | RE5            | RE4            | RE3   | RE2            | RE1            | RE          |

| 4 6       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| INT Pin   | Configura       | ation Re   | gister 3 ( | INTPinC   | Cfg3)         |         |           |                            |          | ı              | I              | I              | ı     |                | I              |             |

| 4 8       |                 |            |            |           |               |         |           |                            |          | PIPEB_<br>NRE6 | PIPEB_<br>NRE5 | PIPEB_<br>NRE4 |       | PIPEB_<br>NRE2 | PIPEB_<br>NRE1 | DCP_<br>NRE |

| 4 A       |                 |            |            |           |               |         |           |                            |          | INICLO         | INICLO         | NIXL4          | MIXES | MIXEZ          | INIXL          | INIXL       |

| INT Pin   | Configura       | ation Re   | gister 4 ( | INTPinC   | Cfg4)         |         |           |                            |          |                |                |                |       |                |                |             |

| 4 C       |                 |            |            |           |               |         |           |                            |          |                |                |                |       | PIPEB_         |                | DCP_        |

|           |                 |            |            |           |               |         |           |                            |          | EMPE6          | EMPE5          | EMPE4          | EMPE3 | EMPE2          | EMPE1          | EMPE        |

| 4 E       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 0       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 2       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 6       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 8       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 A       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 C       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| 5 E       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| Interrupt | Status R        | egister (  | 0 (INTSt   | atus0)    |               |         |           |                            |          |                |                |                |       |                |                |             |

| 6 0       | VBUSINT         | RESM       |            | DVST      | CTRT          | ВЕМР    | INTN      | INTR                       | VBUSSTS  | D              | VSQ [2:        | 0]             | VALID | С              | TSQ [2:        | 0]          |

| 6 2       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

| Interrupt | Status R        | egister    | 1 (INTSt   | atus1)    |               |         |           |                            |          | I              | I              |                | L     |                | I              |             |

| 6 4       |                 |            |            |           |               |         |           |                            |          | PIPEB_<br>RDY6 |                | PIPEB_<br>RDY4 |       | l l            | PIPEB_<br>RDY1 | DCP<br>_RDY |

| 6 6       |                 |            |            |           |               |         |           |                            |          | אומא           | נוטוו          | 114            | נוטוז | אטוצ           | ווטוו          | _1/1/1      |

|           | Status R        | legister : | 2 (INTSt   | atus2)    |               |         |           |                            |          |                |                |                |       |                |                |             |

| 6 8       |                 |            |            |           |               |         |           |                            |          | l .            |                |                |       | PIPEB_         |                | DCP_        |

|           |                 |            |            |           |               |         |           |                            |          | NRDY6          | NRDY5          | NRDY4          | NRDY3 | NRDY2          | NRDY1          | NRDY        |

| 6 A       |                 |            |            |           |               |         |           |                            |          |                |                |                |       |                |                |             |

|               | Odd number address (001h) |            |           |           |           |      |      |        |          | Even number address (000h) |           |           |           |           |           |         |

|---------------|---------------------------|------------|-----------|-----------|-----------|------|------|--------|----------|----------------------------|-----------|-----------|-----------|-----------|-----------|---------|

|               | 15                        | 14         | 13        | 12        | 11        | 10   | 9    | 8      | 7        | 6                          | 5         | 4         | 3         | 2         | 1         | 0       |

| Interrup      | t Status F                | Register   | 3 (INTSt  | atus3)    |           | •    | •    |        |          | •                          | •         |           |           |           |           |         |

| 6 C           |                           |            |           |           |           |      |      |        |          | PIPEB_EM                   | PIPEB_EMP | PIPEB_EMP | PIPEB_EMP | PIPEB_EMP | PIPEB_EMP | DCP_EMP |

|               |                           |            |           |           |           |      |      |        |          | P_OVR6                     | _OVR5     | _OVR4     | _OVR3     | _OVR2     | _OVR1     | _OVR    |

| 6 E           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 7 0           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

|               | dress Re                  | aister (I  | SBAddr    | 066)      |           |      |      |        |          |                            |           |           |           |           |           |         |

| 7 4           | acress ive                | gister (C  | ODAddi    | (33)      |           |      |      |        |          |                            |           | USF       | 3_Addr    | [6:0]     |           |         |

| 7 6           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| USB Re        | equest Re                 | gister 0   | (USBRe    | q0)       |           |      |      |        |          |                            |           |           |           |           |           |         |

| 7 8           |                           | _          | •         | bReque    | est [7:0] |      |      |        |          |                            | bn        | Reques    | tType [7  | 7:0]      |           |         |

| USB Re        | equest Re                 | gister 1   | (USBRe    | q1)       |           |      |      |        |          |                            |           |           |           |           |           |         |

| 7 A           |                           |            |           |           |           |      |      | wValue | [15:0]   |                            |           |           |           |           |           |         |

| $\overline{}$ | equest Re                 | gister 2   | (USBRe    | q2)       |           |      |      |        |          |                            |           |           |           |           |           |         |

| 7 C           |                           |            |           |           |           |      |      | wIndex | [15:0]   |                            |           |           |           |           |           |         |

| $\overline{}$ | equest Re                 | gister 3   | (USBRe    | q3)       |           |      |      |        |          |                            |           |           |           |           |           |         |

| 7 E           |                           |            |           |           |           |      |      | wLengt | n [15:0] |                            |           |           |           |           |           |         |

| 8 0           | <i>r</i>                  | _ ·        | 1 (D)     | 200( 4)   |           |      |      |        |          |                            |           |           |           |           |           |         |

| 8 2           | onfiguration              | n Regis    | ter 1 (DC | PCfg1)    |           |      |      | CNITMD |          |                            |           |           |           |           |           |         |

|               | <br>onfiguratio           | n Regis    | ter 2 (DC | `P(fa2)   |           |      |      | CNTMD  |          |                            |           |           |           |           |           |         |

| 8 4           | Jiliguratio               | n regis    | 161 2 (DC | or Orgz)  |           |      |      |        |          |                            |           | DCP       | _MXPS     | [6:0]     |           | -       |

| 8 6           |                           |            |           |           |           |      |      |        |          |                            |           | 20.       |           | [0.0]     |           |         |

|               | ontrol Reg                | jister (D0 | CPCtrl)   |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 8 8           | BSTS                      |            |           |           |           |      |      | SQCLR  |          |                            |           | NYETMD    |           | CCPL      | PID       | [1:0]   |

| 8 A           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

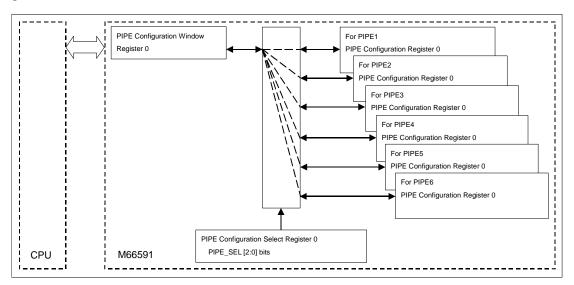

| PIPE Co       | onfiguration              | on Selec   | t Registe | er (Pipe0 | CfgSel)   |      |      |        |          |                            |           |           |           |           |           |         |

| 8 C           |                           |            |           |           |           |      |      |        |          |                            |           |           |           | PIP       | E_SEL[    | 2:0]    |

| 8 E           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

|               | onfiguration              | on Wind    |           | ster 0 (P | ipeCfgV   |      | ı    | 1      |          |                            |           |           |           |           |           |         |

| 9 0           | PEN                       |            | ITMD      |           |           | BFRE | DBLB | CNTMD  |          |                            |           | DIR       |           | EP.       | _NUM [2   | 2:0]    |

| 9 2           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 9 4           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 9 8           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 9 A           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 9 C           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| 9 E           |                           |            |           |           |           |      |      |        |          |                            |           |           |           |           |           |         |

| PIPE i C      | Control Re                | egister (i | =1~6) (F  | ipeiCtrl( | i=1-6))   |      |      |        |          |                            |           |           |           |           |           |         |

| A 0           | BSTS                      |            |           |           |           |      | ACLR | SQCLR  |          |                            |           | NYETMD    |           |           | PID       | [1:0]   |

| A 2           | BSTS                      |            |           |           |           |      |      | SQCLR  |          |                            |           | NYETMD    |           |           | PID       | [1:0]   |

| A 4           | BSTS                      |            |           |           |           |      |      | SQCLR  |          |                            |           | NYETMD    |           |           |           | [1:0]   |

| A 6           | BSTS                      |            |           |           |           |      |      | SQCLR  |          |                            |           | NYETMD    |           |           |           | [1:0]   |

| A 8           | BSTS                      |            |           |           |           |      |      | SQCLR  |          |                            |           |           |           |           |           | [1:0]   |

| A A           | BSTS                      |            |           |           |           |      | ACLR | SQCLR  |          |                            |           |           |           |           | PID       | [1:0]   |

# 2.3 USB Transceiver Control Register 0

■ USB Transceiver Control Register 0 (USBTrnsCtrl0)

<Address: H'00>

| B15  | 14    | 13   | 12   | 11   | 10   | 9 | 8 | 7   | 6 | 5 | 4    | 3 | 2 | 1 | b0   |

|------|-------|------|------|------|------|---|---|-----|---|---|------|---|---|---|------|

| Xtal | [1:0] | XCKE | RCKE | PLLC | SCKE |   |   | HSE |   |   | RpuE |   |   |   | USBE |

| 0    | 0     | 0    | 0    | 0    | 0    | 0 | 0 | 0   | 0 | 0 | 0    | 0 | 0 | 0 | 0    |

| -    | -     | -    | -    | -    | -    | - | - | -   | - | - | -    | - | - | - | -    |

| -    | -     | -    | -    | -    | -    | - | - | -   | - | - | -    | - | - | - | -    |

<H/W reset: H'0000>

<S/W reset: ->

|       |                                        |     | <usb< th=""><th>bus re</th><th>:set: -:</th></usb<>   | bus re | :set: -: |

|-------|----------------------------------------|-----|-------------------------------------------------------|--------|----------|

| b     | Bit name                               |     | Function                                              | R      | W        |

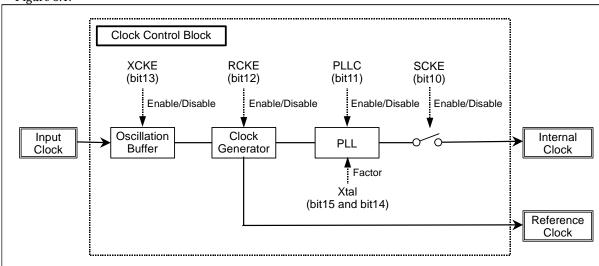

| 15~14 | Xtal [1:0]                             | 00: | External clock frequency: 12MHz                       | 0      | 0        |

|       | Clock Select                           | 01: | External clock frequency: 24MHz                       |        |          |

|       |                                        | 10: | External clock frequency: 48MHz                       |        |          |

|       |                                        | 11: | Reserved                                              |        |          |

| 13    | XCKE                                   | 0:  | Disable oscillation buffer                            | 0      | 0        |

|       | Oscillation Buffer Enable              | 1:  | Enable oscillation buffer                             |        |          |

| 12    | RCKE                                   | 0:  | Disable reference clock (RCK) supply                  | 0      | 0        |

|       | Internal Reference Clock Supply Enable | 1:  | Enable reference clock (RCK) supply                   |        |          |

| 11    | PLLC                                   | 0:  | Disable PLL                                           | 0      | 0        |

|       | PLL Operation Enable                   | 1:  | Enable PLL                                            |        |          |

| 10    | SCKE                                   | 0:  | Disable internal clock supply                         | 0      | 0        |

|       | USB Clock Supply Enable                | 1:  | Enable internal clock supply                          |        |          |

| 9~8   | Reserved. Set it to "0".               |     |                                                       | "0"    | "0"      |

| 7     | HSE                                    | 0:  | Disable Hi-Speed mode                                 | 0      | 0        |

|       | Hi-Speed Enable                        | 1:  | Enable Hi-Speed mode                                  |        |          |

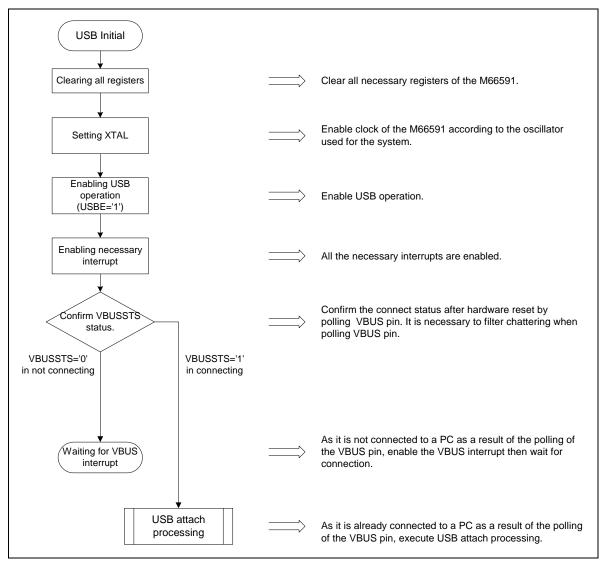

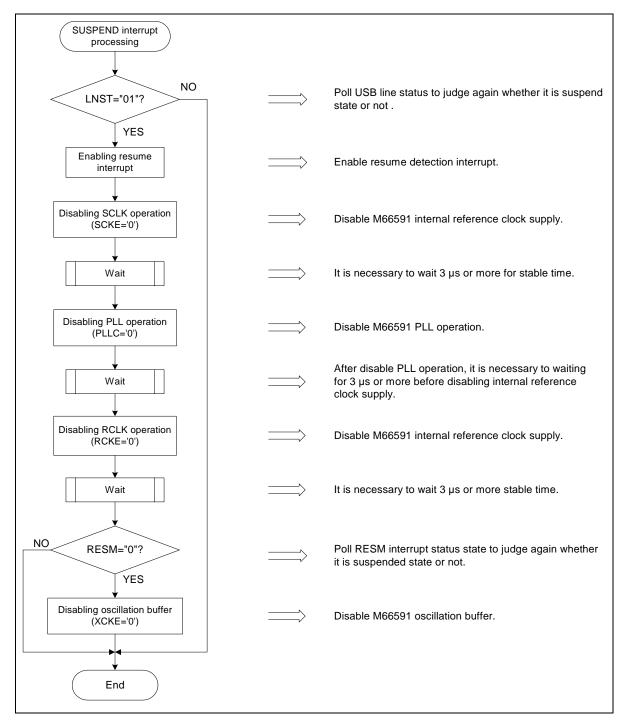

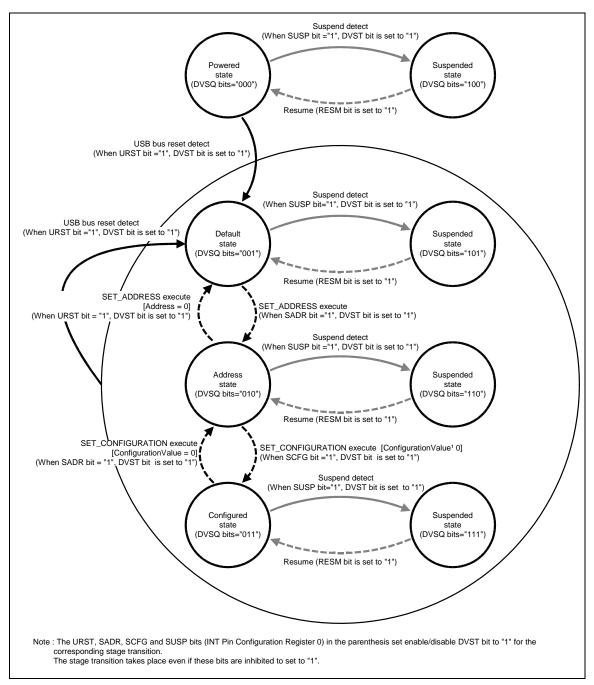

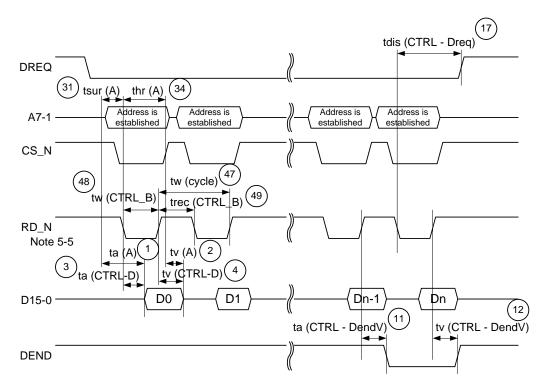

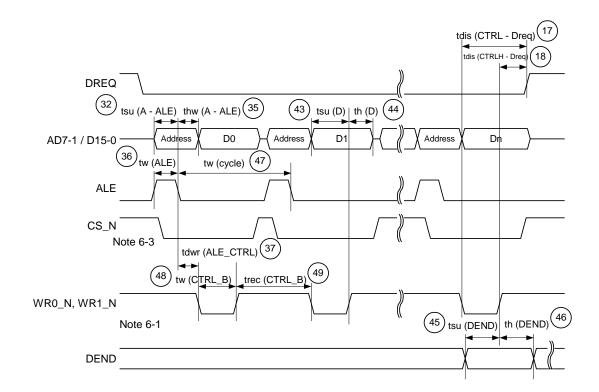

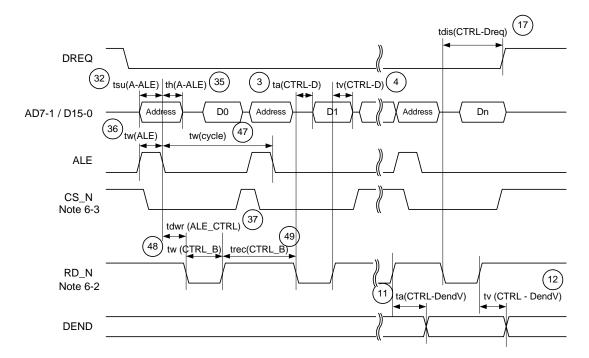

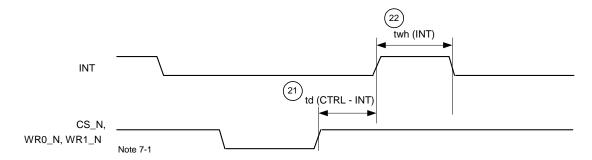

| 6~5   | Reserved. Set it to "0".               |     |                                                       | "0"    | "0"      |