# SANYO Semiconductors DATA SHEET

## CMOSIC CB Transceiver PLL Frequency Synthesizer and Controller

## Overview

This 27 MHz band, PLL frequency synthesizer LSI chip is designed specifically for CB transceivers. The specifications are suited for use in U.S.A.(FCC).

## Functions

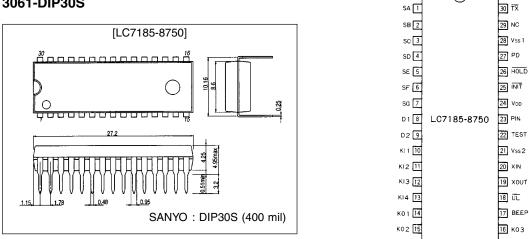

The LC7185-8750 incorporates PLL circuitry and a controller for CB applications on a single CMOS chip. The controller handles the PLL circuitry, frequency data ROM, channel preset/recall RAM, and LED display driver. It also supports channel scan, channel preset/recall, and emergency channel call.

## Features

- 1. A built-in programmable divider for the 16 MHz VCO

- 2. Transmission is inhibited when the PLL is unlocked (digital lock monitor).

- 3. Direct channel 9 or 19 selection (sliding switch)

- 4. A 7-segment, 2-character LED display

- 5. "PA" is displayed in public announcement mode.

- 6. Output beep-tone control circuitry

- 7. Up to 5 channel settings can be stored in memory.

- 8.  $4 \times 3$  key matrix implementation

## Specifications

#### Absolute Maximum Ratings at Ta = $25^{\circ}$ C, V<sub>ss</sub> = 0 V

| Parameter                      | Symbol                | Conditions                                  | Ratings                      | Unit |

|--------------------------------|-----------------------|---------------------------------------------|------------------------------|------|

| Maximum supply voltage         | V <sub>DD</sub> max   | Pin V <sub>DD</sub>                         | -0.3 to +9.0                 | V    |

| Input voltage                  | V <sub>IN</sub> 1 max | Pins HOLD, TX                               | -0.3 to +15                  | V    |

|                                | V <sub>IN</sub> 2 max | Input pins other than V <sub>IN</sub> 1 max | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage                 | V <sub>O</sub> 1 max  | Pins SA, SB, SC, SD, SE, SF, SG, D1, D2     | -0.3 to +15                  | V    |

|                                | V <sub>O</sub> 2 max  | Pins UL, BEEP                               | -0.3 to +15                  | V    |

|                                | V <sub>O</sub> 3 max  | Pin PD                                      | –0.3 to V <sub>DD</sub> +0.3 | V    |

|                                | V <sub>O</sub> 4 max  | Output pins other than mentioned above      | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Output Current                 | I <sub>O</sub> 1 max  | Pins SA, SB, SC, SD, SE, SF, SG             | 0 to +30                     | mA   |

|                                | I <sub>O</sub> 2 max  | Pins D1, D2                                 | 0 to +10                     | mA   |

|                                | I <sub>O</sub> 3 max  | Pins UL                                     | 0 to +20                     | mA   |

|                                | I <sub>O</sub> 4 max  | Pin BEEP                                    | 0 to +10                     | mA   |

| Allowable power<br>dissipation | Pd max                | (Ta ≤ 85°C)                                 | 350                          | mW   |

| Operating temperature          | Topr                  |                                             | -40 to +85                   | °C   |

| Storage temperature            | Tstg                  |                                             | -55 to +125                  | °C   |

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before usingany SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

## SANYO Semiconductor Co., Ltd.

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

| Parameter                         | Symbol             | Conditions                              | min                | typ   | max                | Unit |

|-----------------------------------|--------------------|-----------------------------------------|--------------------|-------|--------------------|------|

| Supply voltage                    | V <sub>DD</sub>    |                                         | 5.0                |       | 8.0                | V    |

|                                   | V <sub>IH</sub> 1  | Pins HOLD, TX                           | 0.7V <sub>DD</sub> |       | 12                 | V    |

| Input high-level voltage          | V <sub>IH</sub> 2  | Pin INIT                                | 3.2                |       | V <sub>DD</sub>    | V    |

|                                   | V <sub>IH</sub> 3  | Pins KI1, KI2, KI3, KI4                 | 0.6V <sub>DD</sub> |       | V <sub>DD</sub>    | V    |

|                                   | V <sub>IL</sub> 1  | Pins HOLD, TX                           | 0                  |       | 0.3V <sub>DD</sub> | V    |

| Input low-level voltage           | V <sub>IL</sub> 2  | Pin INIT                                | 0                  |       | 1.3                | V    |

|                                   | V <sub>IL</sub> 3  | Pins KI1, KI2, KI3, KI4                 | 0                  |       | 0.4V <sub>DD</sub> | V    |

| Output voltage                    | V <sub>OUT</sub> 1 | Pins SA, SB, SC, SD, SE, SF, SG, D1, D2 | 0                  |       | 13                 | V    |

| Oulput voltage                    | V <sub>OUT</sub> 2 | Pins UL, BEEP                           | 0                  |       | 8                  | V    |

| Input froquency                   | f <sub>IN</sub> 1  | Pin XIN (sine wave, capacitor coupled)  | 1.0                | 10.24 | 15                 | MHz  |

| Input frequency                   | f <sub>IN</sub> 2  | Pin PIN (sine wave, capacitor coupled)  | 10                 |       | 30                 | MHz  |

| Input emplitude                   | V <sub>IN</sub> 1  | Pin XIN (sine wave, capacitor coupled)  | 0.5                |       | 1.5                | Vrms |

| Input amplitude                   | V <sub>IN</sub> 2  | Pin PIN (sine wave, capacitor coupled)  | 0.15               |       | 1.5                | Vrms |

| Required oscillating<br>frequency | X'tal              | Pins XIN, XOUT (CI $\leq 50 \Omega$ )   | 5.0                | 10.24 | 15                 | MHz  |

## Allowable Operating Conditions at Ta = -40 to $+85^{\circ}C$ , $V_{SS} = 0$ V

### Electrical Characteristics at under allowable operating conditions

| Parameter                           | Symbol             | Conditions                                                                              | min                  | typ                  | max                  | Unit |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| Internal feedback resistance        | Rf1                | Pin XIN                                                                                 |                      | 1.0                  |                      | MΩ   |

| Internal reedback resistance        | Rf2                | Pin PIN                                                                                 |                      | 500                  |                      | kΩ   |

| Pull-down resistor                  | RpdN               | Pins KI1, KI2, KI3, KI4, TEST                                                           | 30                   | 50                   | 70                   | kΩ   |

|                                     | I <sub>IH</sub> 1  | Pins $\overline{\text{HOLD}}$ , $\overline{\text{TX}}$ V <sub>I</sub> = 12 V            |                      |                      | 5.0                  | μA   |

| Input high-level current            | I <sub>IH</sub> 2  | Pin $\overline{\text{INIT}}$ V <sub>I</sub> = V <sub>DD</sub>                           |                      |                      | 5.0                  | μA   |

| input high-level current            | I <sub>IH</sub> 3  | Pin XIN $V_I = V_{DD}$                                                                  |                      |                      | 25                   | μA   |

|                                     | I <sub>IH</sub> 4  | Pin PIN $V_I = V_{DD}$                                                                  |                      |                      | 50                   | μA   |

|                                     | I <sub>IL</sub> 1  | Pins $\overline{\text{HOLD}}$ , $\overline{\text{TX}}$ V <sub>I</sub> = V <sub>SS</sub> |                      |                      | 5.0                  | μA   |

| Input low-level current             | I <sub>IL</sub> 2  | Pin $\overline{\text{INIT}}$ V <sub>I</sub> = V <sub>SS</sub>                           |                      |                      | 5.0                  | μA   |

| input low-level current             | I <sub>IL</sub> 3  | Pin XIN $V_I = V_{SS}$                                                                  |                      |                      | 25                   | μA   |

|                                     | I <sub>IL</sub> 4  | Pin PIN $V_I = V_{SS}$                                                                  |                      |                      | 50                   | μA   |

| Output high-level voltage           | V <sub>OH</sub> 1  | Pins KO1, KO2, KO3 I <sub>O</sub> = 1 mA                                                | V <sub>DD</sub> -2.0 | V <sub>DD</sub> -1.0 | V <sub>DD</sub> -0.5 | V    |

| Output high-level voltage           | V <sub>OH</sub> 2  | Pin PD $I_{O} = 0.5 \text{ mA}$                                                         | V <sub>DD</sub> -1.0 |                      |                      | V    |

|                                     | V <sub>OL</sub> 1  | Pins KO1, KO2, KO3 Ι <sub>Ο</sub> = 20 μA                                               | 0.6                  | 1.0                  | 1.4                  | V    |

|                                     | V <sub>OL</sub> 2  | Pin PD I <sub>O</sub> = 0.5 mA                                                          |                      |                      | 1.0                  | V    |

|                                     | V <sub>OL</sub> 3  | Pin BEEP I <sub>O</sub> = 2 mA                                                          |                      |                      | 1.0                  | V    |

| Output low-level voltage            | V <sub>OL</sub> 4  | Pins SA, SB, SC, SD, SE, SF, SG $I_{O} = 20 \text{ mA}$                                 |                      |                      | 1.0                  | V    |

|                                     | V <sub>OL</sub> 5  | Pins D1, D2 I <sub>O</sub> = 5 mA                                                       |                      |                      | 1.0                  | V    |

|                                     | V <sub>OL</sub> 6  | Pin $\overline{\text{UL}}$ I <sub>O</sub> = 10 mA                                       |                      |                      | 1.0                  | V    |

| Output leakage current              | I <sub>OFF</sub> 1 | Pins SA, SB, SC, SD, SE, SF, SG, D1, D2<br>$V_{O}$ = 13 V                               |                      |                      | 5.0                  | μA   |

|                                     | I <sub>OFF</sub> 2 | Pins UL, BEEP V <sub>O</sub> = 8 V                                                      |                      |                      | 5.0                  | μA   |

| High-level tristate leakage current | IOFFH              | Pin PD $V_0 = V_{DD}$                                                                   |                      | 0.01                 | 10.0                 | nA   |

| Low-level tristate leakage current  | IOFFL              | Pin PD V <sub>O</sub> = V <sub>SS</sub>                                                 |                      | 0.01                 | 10.0                 | nA   |

| Supply current                      | I <sub>DD</sub> 1  | Normal mode<br>*1 (PLL operates)                                                        |                      | 5                    | 10                   | mA   |

|                                     | I <sub>DD</sub> 2  | Hold mode V <sub>DD</sub> = 3.2 V<br>*2 (memory backup)                                 |                      |                      | 5                    | μA   |

|                                     |                    | $V_{DD} = 8.0 V$                                                                        |                      |                      | 15                   | μA   |

\*1:  $f_{IN}2 = 20 \text{ MHz}$  (PIN)  $V_{IN}2 = 0.15 \text{ Vrms}$  X'tal = 10.240 MHz  $\overline{TX} = \overline{HOLD} = \overline{INIT} = V_{DD}$ Other inputs =  $V_{SS}$ Other outputs = open \*2:  $\overline{HOLD} = V_{SS}$  $\overline{TX} = \overline{INIT} = V_{DD}$ Other inputs = V<sub>SS</sub> Other outputs = open

Note: Be careful that the dielectric strength of pins SA, SB, SC, SD, SE, SF, D1, D2, UL, BEEP are weak.

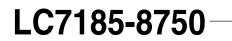

## **Package Dimensions**

#### **Pin Assignment**

unit : mm

## 3061-DIP30S

Top view

#### **Block Diagram**

## **Pin Descriptions**

| TX                                                     | Transmit/receive select                          | PD         | Charge pump output           |

|--------------------------------------------------------|--------------------------------------------------|------------|------------------------------|

| HOLD                                                   | Hold mode select                                 | NC         | NC pin                       |

| INIT                                                   | Initial input                                    | SA to SG   | Segment driver (for display) |

| TEST                                                   | Test point (input)                               | D1, D2     | Digit output (for display)   |

| V <sub>DD</sub> , V <sub>SS</sub> 1, V <sub>SS</sub> 2 | Power supply                                     | KI1 to KI4 | Key inputs                   |

| PIN                                                    | Programmable divider input                       | KO1 to KO3 | Key scan outputs             |

| XIN, XOUT                                              | Crystal oscillator input, output<br>(10.240 MHz) | BEEP       | Beep-tone control output     |

| ŪL                                                     | Unlock detection signal output                   |            |                              |

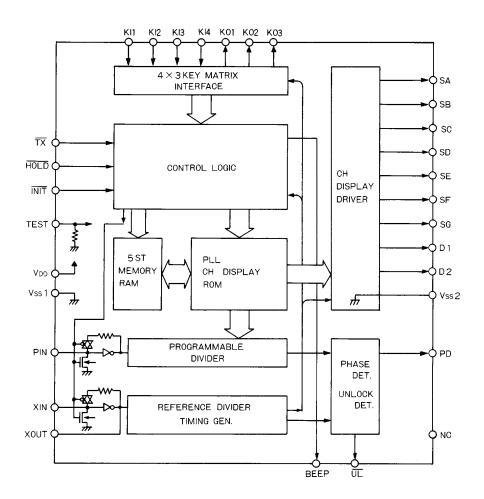

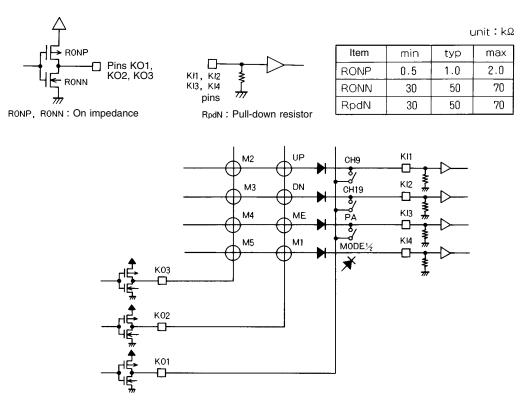

## Key Matrix

| СН9      | Emergency CH9 recall        | ME               | Station Memory Enable |

|----------|-----------------------------|------------------|-----------------------|

| CH19     | Emergency CH19 recall       | M1 to M5         | Station Memory recall |

| PA       | Public announcement display | UP/DN/ME/M1 to 5 | Momentary SW          |

| MODE 1/2 | Display Mode                | CH9/CH19/PA      | Slide SW              |

| UP       | CH up/scan                  | MODE 1/2         | Diode                 |

| DN       | CH down/scan                |                  |                       |

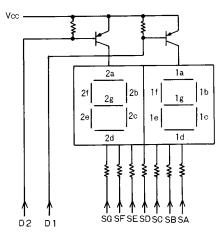

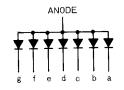

## LED Display Configuration (Common anode/7 segment)

| $\square$ | SG | SF | SE | SD | sc | SB | SA |

|-----------|----|----|----|----|----|----|----|

| D1        | 1g | 1f | 1e | 1d | 1c | 1b | 1a |

| D2        | 2g | 2f | 2e | 2d | 2c | 2b | 2a |

## **Pin Description**

| Pin Name                | Pin No.  | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX                      | 30       | ┎──┥╱── | • Transmit/receive select<br>$\overline{TX} = "0"$ Transmit, TX = "1"Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HOLD                    | 26       |         | Hold mode select     HOLD = "0"Hold mode select     = "1"Normal mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ĪNIT                    | 25       |         | • <u>Res</u> et line<br>INIT = "0"Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TEST                    | 22       |         | • Test point (input)<br>Tie to ground or leave floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>         | 24       |         | • Power supply (+)<br>Normal mode: 5.0 to 8.0 V<br>Hold mode: ≧ 3.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub> 2       | 21       |         | Channel display LED driver ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIN                     | 23       |         | <ul> <li>Programmable divider input<br/>150 mVrms min<br/>Hold mode: Programmable divider is disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XIN<br>XOUT             | 20<br>19 |         | <ul> <li>Crystal oscillator<br/>Frequency: 10.24 MHz<br/>Hold mode: Oscillator is disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PD                      | 27       |         | <ul> <li>Charge pump output from the phase comparator. If the frequency of fV (the signal obtained by dividing the PIN input by N) is higher than that of fR (the reference signal), or if the phase of fV leads that of fR, positive pulses are output on this pin. If the frequency is lower or the phase lags, negative pulses are output on this pin. If they match, the pin goes to high impedance.</li> <li>fV &gt; fR OR leading: Positive Pulses</li> <li>fV &lt; fR OR leading: Negative Pulses</li> <li>fV = fR and phase muched: High impedance</li> </ul> |

| V1                      | 28       |         | Hold mode: High impedance     PLL circuit and controller ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub> 1<br>NC | 28       |         | No-connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | 18       |         | Unlock detected output<br>Fixed to low level when unlocked, when changing channels, in PA mode,<br>or in hold mode.<br>Open: Locked                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BEEP                    | 17       |         | <ul> <li>Beep-tone control output<br/>During station memory operation<br/>During I/O on emergency channel<br/>When changing channels<br/>During reset<br/>During hold mode recovery<br/>Fixed to low level in hold mode</li> <li>Transistor: Off (50 ms cycle)<br/>→ Open</li> </ul>                                                                                                                                                                                                                                                                                  |

| SA to SG                | 1 to 7   |         | Segment drivers for the display<br>(Common anode/7 segments)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D1<br>D2                | 8<br>9   |         | <ul> <li>Digit output (150 Hz) for the display<br/>(common anode/7 segments)<br/>Hold mode: Transistor goes off.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Continued on next page.

Continued from preceding page.

| Pin Name   | Pin No.  | Туре | Description                                                                                                  |

|------------|----------|------|--------------------------------------------------------------------------------------------------------------|

| KI1 to KI4 | 10 to 13 |      | Key inputs     Input from the key matrix                                                                     |

| KO1 to KO3 | 14 to 16 |      | <ul> <li>Key scan output (75 Hz)<br/>Output to the key matrix<br/>Hold mode: Low (scanning stops)</li> </ul> |

#### Operation

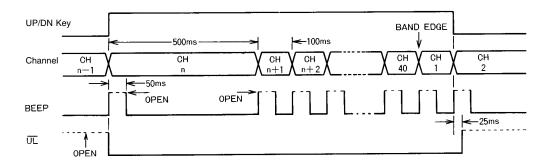

- (1) Channel Selection (up/down)

- Manual scanning (up/down)

Pressing the UP key increments by one channel and pressing the DN key decrements by channel.

When scanning reaches the end of the band, it automatically wraps around to the beginning.

- Auto scanning (up/down) Holding the UP (or DN) key down for 500 ms or longer starts auto scanning. For both up and down scanning, each channel takes 100 ms to scan.

- 3. The unlock detected line  $(\overline{UL})$  is asserted (low) when the UP (or DN) key is pressed and deactivated 25 ms after the key is released.

- 4. The beep-tone control line (BEEP) is asserted (open) for 50 ms after each new channel is selected.

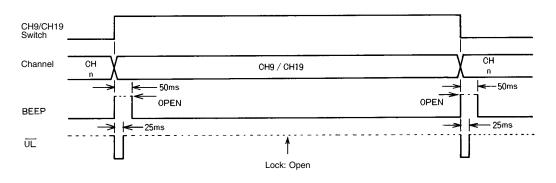

- (2) Selecting an Emergency Channel (CH9/CH19)

- 1. If the CH9 or CH19 switch is turned on, the LC7185 stores the value of the previous channel and asserts the beep-tone control line for 50 ms.

- 2. While the CH9 or CH19 switch is turned on, the LC7185 disables all keys except  $\overline{\text{TX}}$  and PA (UP/DN, ME, and M1 to M5 switches).

- 3. Even if the CH9 or CH19 switch is turned off while transmitting using the CH9 or CH19 switch, keep the emergency channel open until the LC7185 is in the receive mode.

- 4. After the CH9 or CH19 switch is turned back off, the beep-tone control line is asserted for 50 ms and the LC7185 reopens the previous channel.

- 5. Note the CH9 has a higher priority over CH19. As a result, if both switches are turned on, CH9 will be opened.

- 6. The  $\overline{\text{UL}}$  line is asserted for 25 ms after the CH9 or CH19 switch is turned off or on.

- 7. Causes either "9" or "19" to blink on the display.

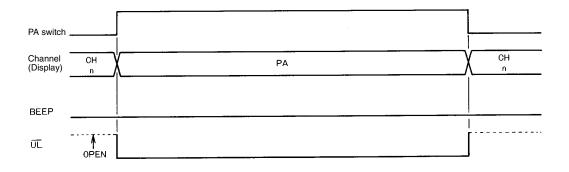

- (3) Public Announcement (PA) Mode

- 1. When the PA switch is turned on, the LC7185 stores the value of the previous channel and enters the PA mode.

- 2. While the PA switch is turned on, the LC7185 disables all keys (TX, CH9/CH19, UP/DN, ME, M1 to M5)

- 3. "PA" is displayed on the channel display.

- 4. When the PA switch is turned back off, the LC7185 enters the CB mode and reopens the previous channel.

- 5. The  $\overline{\text{UL}}$  line is asserted while the PA switch is turned on.

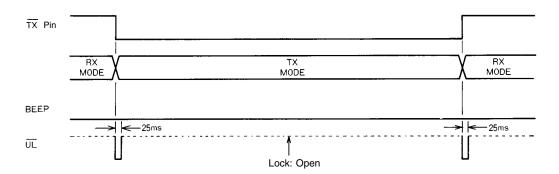

- (4) Transmit/Receive Selection

- 1. When the  $\overline{TX}$  line is asserted, the LC7185 enters TX mode.

- If the PA switch is turned on while the LC7185 is in TX mode, the device enters PA mode. However, if any other switch (other than the PA switch) or key (UP/DN, ME, M1 through M5, CH9, CH19) is pressed while the LC7185 is in TX mode, that switch or key has no effect.

- 3. The unlock detected signal is output each time the device switches between transmitting and receiving.

- (5) Channel Preset/Recall Facility

- 1. The LC7185 allows up to 5 channels to be preset (assigned to M1 to M5).

- After a reset (when the power is turned on, etc.), M1 to M5 are assigned to CH33.

- 2. Recalling preset channels

- A preset channel is recalled by pressing one of the preset memory keys (M1 to M5) to which the channel was previously assigned.

- There are two different display modes as shown below. <u>Mode 1</u> (without diode) Each time a key is pressed (M1 to M5), the new channel is displayed. Example: Display 21 → 15 key <u>M1</u> <u>Mode 2</u> (with diode) Each time a key is pressed (M1 to M5), a key mnemonic ("P1" to "P5") is displayed for 400 ms, then the new channel is displayed. Example: Display 21 → P1 → 15 400 ms Key <u>M1</u>

#### 3. Presetting channels

- First select the channel to be preset, then hold down the ME key and press the preset memory key (M1 to M5) to which you would like to assign the current channel.

- In the following cases, a channel will not be preset:

- $\bullet$  M1 to M5 is pressed and in the memory preset mode.

- Emergency channels CH9 or CH19 are currently selected.

- The  $\overline{TX}$  line is asserted.

- The PA switch is turned on (PA mode).

- The  $\overline{\text{HOLD}}$  line is asserted (hold mode).

Even if the above key operations are not performed, the preset mode will be canceled automatically after 9 seconds.

• There are two different display modes as shown below.

$\underline{Mode 1}$  (without diode)

The current channel is displayed throughout the preset process.

Example: Display 15  $\longrightarrow$  15 Key ME M1

$\underline{Mode \ 2}$  (with diode)

When the ME key is held down, "PE" is flashed on the display, indicating that presetting is possible. Once a preset memory key (M1 to M5) is pressed, the key mnemonic ("P1" to "P5") is displayed for 400 ms before the current channel is redisplayed.

Example: Display  $15 \rightarrow PE \rightarrow P1 \rightarrow 15$ 400 ms

ME M1

- Note that if two or more keys are pressed at the same time, priority is assigned as follows: M1>M2>M3>M4>M5

- (6) Beep-tone Control Output (BEEP pin)

Key

After each of the following events, the BEEP line is asserted for 50 ms:

- A reset, such as a battery replacement  $(\overline{\text{INIT}} = 0)$

- Any key press associated with the channel memory

- Any emergency channel switch activation

- A new channel is selected

- Leaving hold mode

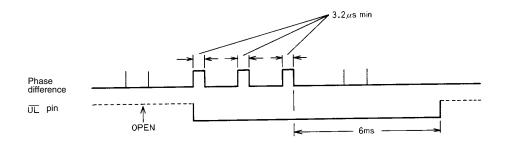

- (7) Unlock Detected Output ( $\overline{\text{UL}}$  pin)

In the following cases, the  $\overline{UL}$  line is asserted.

• When the phase difference between the programmable and reference divider outputs exceeds 3.2  $\mu$ s, the UL line is held low for 6 ms after the last out-of-range phase sample is detected, as shown below.

• After a new transmit/receive or channel selection, the  $\overline{\text{UL}}$  line is asserted for 25 ms.

• While the PA switch is turned on, the  $\overline{\text{UL}}$  line is asserted during PA mode.

• The  $\overline{\text{UL}}$  pin is open while the device is in the PLL LOCK state (when the phase difference is < 3.2 µs).

(8) Key Matrix

It is normal to put diodes in series with the key scanning lines to avoid creating a short with the output lines. But KO1, KO2 and KO3 lines (key scan signal output) do not need diodes.

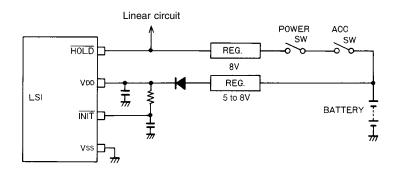

#### **Explanation Regarding Power On and Hold Mode**

(1) Operation in hold mode

When in hold mode ( $\overline{\text{HOLD}} = 0$ ), the LC7185-8750 does not accept any operation other than the  $\overline{\text{INIT}}$  pin being asserted (reset). The primary function of hold mode is to maintain the contents of station memory.

- In hold mode, the programmable divider, crystal oscillator and reference divider are all stopped.

- The PD pin (charge pump output) goes to high impedance. The  $\overline{\text{UL}}$  pin goes to V<sub>SS</sub>.

- The channel display pins D1 and D2 go to high impedance.

- The BEEP pin goes to  $V_{SS}$ .

- $\bullet$  The key scan signal outputs (KO1 to KO3) go to  $V_{SS}.$

When the LC7185-8750 leaves hold mode, the previously selected channel is reopened.

(2) Initial state settings

The LC7185-8750 can be reset to its initial state settings (reset) after the battery has been replaced, etc., by setting  $\overline{INIT} = 0$ . The initial state that is established by an initial reset is as follows:

- •When the V<sub>DD</sub> pin turned on, CH9 or CH33 is selected.

- •When the  $V_{DD}$  pin operate voltage already, CH9 is selected.

- •All of station memory is set to CH33.

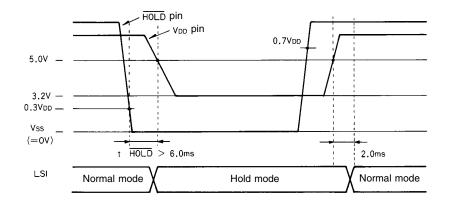

#### (3) Timing Requirements for Hold Mode

$V_{DD}$  must remain at 5.0 V or higher (crystal oscillator requirement) for 6.0 ms (t  $\overline{HOLD}$ ) after the  $\overline{HOLD}$  line is asserted ( $\overline{HOLD}$  = 0 (< 0.3  $V_{DD}$ ). After this,  $V_{DD}$  may go as low as 3.2 V.

There are no constraints on timing for the  $\overline{HOLD}$  and  $V_{DD}$  pins when the chip is leaving hold mode. The signal can be activated in one of two orders.

If  $\overline{\text{HOLD}}$  is already deactivated (> 0.7 V<sub>DD</sub>), the LC7185-8750 leaves hold mode within 2.0 ms after V<sub>DD</sub> rises to >5.0 V. If V<sub>DD</sub> is > 5.0 V, the LC7185-8750 enters normal mode within 2.0 ms after  $\overline{\text{HOLD}}$  is deactivated.

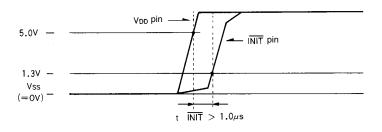

#### (4) Reset Timing

1. Reset timing (e.g. battery replacement)

Note: tINIT should be greater than 1.0 μs.

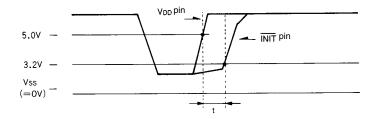

Reset caused by a sudden voltage (V<sub>DD</sub>) drop

If  $V_{DD}$  drops momentarily down to less than 3.2 V and rises up to more than 5.0 V t > t $\overline{INIT}$  (t > 1.0 µs), a reset may be generated.

## Frequency Table (U.S.A.: LC7185-8750)

|         | FREQUENCY | RX (1 | <u>TX</u> = 1) | TX ( | <u>(X</u> = 0) |

|---------|-----------|-------|----------------|------|----------------|

| CHANNEL | (MHz)     | N     | Fvco           | N    | Fvco           |

| 1       | 26.965    | 6508  | 16.27          | 5393 | 13.4825        |

| 2       | 26.975    | 6512  | 16.28          | 5395 | 13.4875        |

| 3       | 26.985    | 6516  | 16.29          | 5397 | 13.4925        |

| 4       | 27.005    | 6524  | 16.31          | 5401 | 13.5025        |

| 5       | 27.015    | 6528  | 16.32          | 5403 | 13.5075        |

| 6       | 27.025    | 6532  | 16.33          | 5405 | 13.5125        |

| 7       | 27.035    | 6536  | 16.34          | 5407 | 13.5175        |

| 8       | 27.055    | 6544  | 16.36          | 5411 | 13.5275        |

| 9       | 27.065    | 6548  | 16.37          | 5413 | 13.5325        |

| 10      | 27.075    | 6552  | 16.38          | 5415 | 13.5375        |

| 11      | 27.085    | 6556  | 16.39          | 5417 | 13.5425        |

| 12      | 27.105    | 6564  | 16.41          | 5421 | 13.5525        |

| 13      | 27.115    | 6568  | 16.42          | 5423 | 13.5575        |

| 14      | 27.125    | 6572  | 16.43          | 5425 | 13.5625        |

| 15      | 27.135    | 6576  | 16.44          | 5427 | 13.5675        |

| 16      | 27.155    | 6584  | 16.46          | 5431 | 13.5775        |

| 17      | 27.165    | 6588  | 16.47          | 5433 | 13.5825        |

| 18      | 27.175    | 6592  | 16.48          | 5435 | 13.5875        |

| 19      | 27.185    | 6596  | 16.49          | 5437 | 13.5925        |

| 20      | 27.205    | 6604  | 16.51          | 5441 | 13.6025        |

| 21      | 27.215    | 6608  | 16.52          | 5443 | 13.6075        |

| 22      | 27.225    | 6612  | 16.53          | 5445 | 13.6125        |

| 23      | 27.255    | 6624  | 16.56          | 5451 | 13.6275        |

| 24      | 27.235    | 6616  | 16.54          | 5447 | 13.6175        |

| 25      | 27.245    | 6620  | 16.55          | 5449 | 13.6225        |

| 26      | 27.265    | 6628  | 16.57          | 5453 | 13.6325        |

| 27      | 27.275    | 6632  | 16.58          | 5455 | 13.6375        |

| 28      | 27.285    | 6636  | 16.59          | 5457 | 13.6425        |

| 29      | 27.295    | 6640  | 16.60          | 5459 | 13.6475        |

| 30      | 27.305    | 6644  | 16.61          | 5461 | 13.6525        |

| 31      | 27.315    | 6648  | 16.62          | 5463 | 13.6575        |

| 32      | 27.325    | 6652  | 16.63          | 5465 | 13.6625        |

| 33      | 27.335    | 6656  | 16.64          | 5467 | 13.6675        |

| 34      | 27.345    | 6660  | 16.65          | 5469 | 13.6725        |

| 35      | 27.355    | 6664  | 16.66          | 5471 | 13.6775        |

| 36      | 27.365    | 6668  | 16.67          | 5473 | 13.6825        |

| 37      | 27.375    | 6672  | 16.68          | 5475 | 13.6875        |

| 38      | 27.385    | 6676  | 16.69          | 5477 | 13.6925        |

| 39      | 27.395    | 6680  | 16.70          | 5479 | 13.6975        |

| 40      | 27.405    | 6684  | 16.71          | 5481 | 13.7025        |

$V_{CO}(TX) = RF \div 2$

$V_{CO} (IX) = IXI + 2$   $V_{CO} (RX) = RF - 10.695 \text{ MHz (IF)}$ CH1:  $V_{CO} (TX) = 26.965 \div 2 = 13.4825$   $V_{CO} (RX) = 26.965 - 10.965 = 16.27$

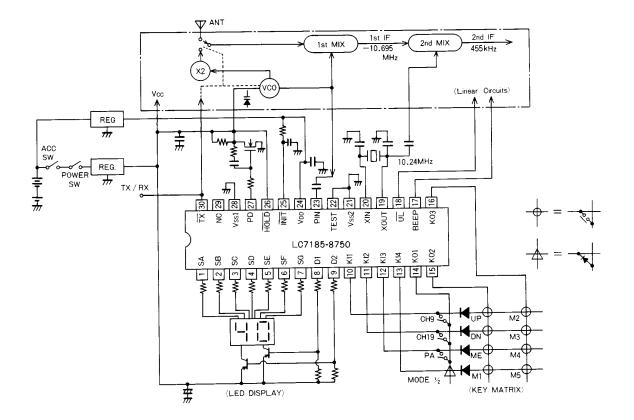

#### **Sample Application Circuit**

- Specifications of any and all SANYO Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor products (including technical data,services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Semiconductor Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of October, 2006. Specifications and information herein are subject to change without notice.