### 8 x Digital Sensor Interface

### FZE 1658G

### Features

- Input protection against 2000 V burst/500 V surge pulse according to IEC 801 4/5

- Input characteristic according to IEC 65 A, type 2 (24 V DC)

- Digital filter

- Serial in/out for easy cascading

- Low power dissipation

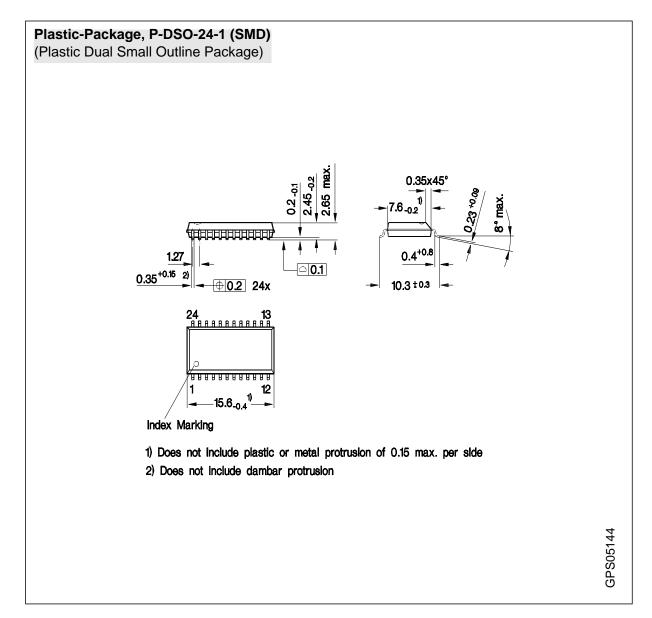

- SMD package

| Туре      | Ordering Code | Package    |

|-----------|---------------|------------|

| FZE 1658G | Q67000-A8361  | P-DSO-24-1 |

The FZE 1658G is an integrated interface for digital sensors - i.e. proximity switches - in industrial automation equipment. The IC has eight integrated highly protected and failsafe inputs with status LED and a serial synchronous output for direct MC-interfacing.

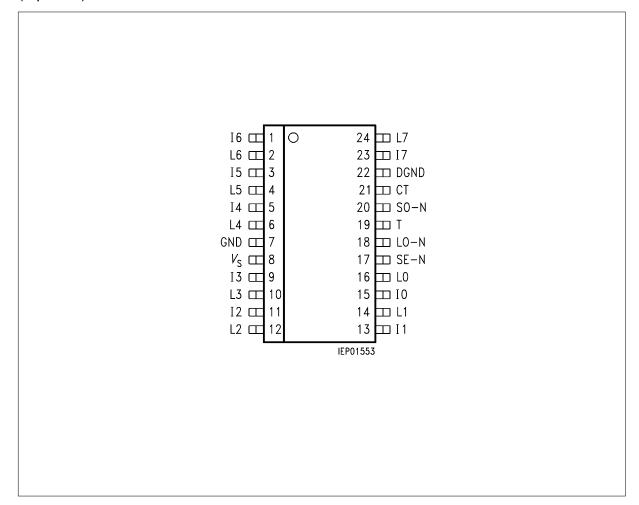

### **Pin Configuration**

(top view)

### **Pin Definitions and Functions**

| Pin                            | Symbol  | Function                                                                                                                                                                  |

|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15, 13, 11, 9,<br>5, 3, 1, 23  | 10 - 17 | Inputs for 24-V signals, in conjunction with $R_{\rm V}$ and $R_{\rm EXT}$ current sink characteristic.                                                                   |

| 16, 14, 12,<br>10, 6, 4, 2, 24 | L0 - L7 | Outputs for the status LEDs; LED lights when H-signal is present at input.                                                                                                |

| 21                             | СТ      | Pin for connecting the frequency-determining capacitor for the filter clock; also reset input if CT is connected to DGND.                                                 |

| 7                              | GND     | Ground for all 24-V signals, substrate.                                                                                                                                   |

| 22                             | DGND    | Ground for all 5-V signals, no internal connection to GND.<br>Any interruption of GND or DGND with the supply voltage<br>present may result in destruction of the device. |

| 8                              | Vs      | Supply voltage; undervoltage activates internal reset.                                                                                                                    |

| 20                             | SO-N    | Serial output, open drain.                                                                                                                                                |

| 17                             | SE-N    | Extention input for serial cascading with pull-up current source.                                                                                                         |

| 18                             | LO-N    | Latch input, edge H-L results in transfer of data from the digital filters to the output register.                                                                        |

| 19                             | Т       | Clock for serial output, positive edge triggered.                                                                                                                         |

### **Functional Description and Application**

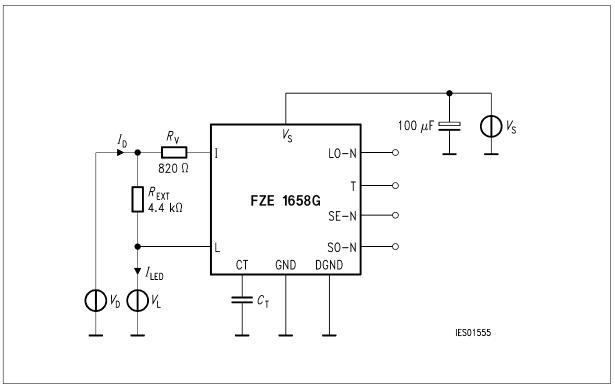

The Integrated circuit FZE 1658G is used to detect the signal states of eight independent input lines according to IEC 65A Type 2 (e.g. two-wire proximity switches) with a common ground (GND). For operation in accordance with IEC 65A, it is necessary for the device to be wired with resistors rated  $R_V = 820 \Omega$  and  $R_{EXT} = 4.4 \text{ k}\Omega$  with  $\pm 2 \%$  tolerance and 200 ppm TK. The input device has the following characteristics:

- Minimization of power dissipation due to constant current characteristic

- Inputs protected against reverse polarity and transient overvoltages

- Status LED output for each input

- Digital averaging of the input signals to suppress interference pulses

- Serial output of the detected signals (cascadable)

|                                                           | Voltage Range                 | Notes                                         |

|-----------------------------------------------------------|-------------------------------|-----------------------------------------------|

| DC voltage                                                | - 3 V + 32 V<br>- 32 V + 32 V | full function<br>non-destructive, no latch-up |

| Overvoltage 500 ms                                        | - 3 V + 35 V<br>- 35 V + 35 V | full function<br>non-destructive, no latch-up |

| Overvoltage 1.3 ms<br>to VDE 0160                         | - 3 V + 55 V<br>± 55          | full function<br>non-destructive, no latch-up |

| Surge pulse 50 $\mu$ s to IEC 801-5, $Z_i$ = 2 $\Omega$   | ± 0.5 kV                      | 1)                                            |

| Burst pulse 50 ns to IEC 801-4, $Z_{\rm i}$ = 50 $\Omega$ | ± 2 kV                        | 2)                                            |

### Maximum voltage ratings at inputs D0 ... D7 within test circuit 2.

<sup>1)</sup> Non-destructive in temperature range 15 °C  $\leq$   $T_A \leq$  35 °C.

<sup>2)</sup> In temperature range 15 °C  $\leq$   $T_A \leq$  35 °C: Data retained if the supply voltage remains within the operating range; without supply voltage non-destructive.

The rated voltage may be applied to all inputs simultaneously.

The values given in the table may be regarded as guaranteed, but are only checked as part of a qualification (no 100 % series testing).

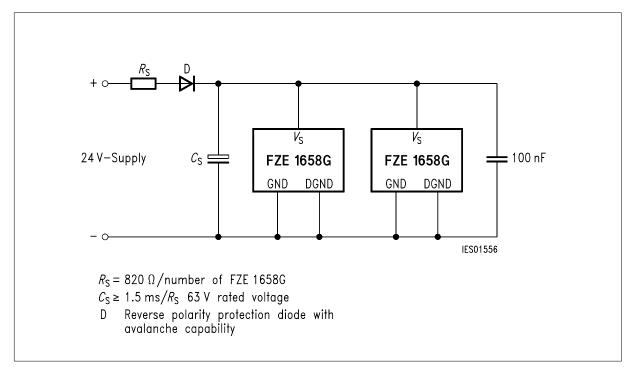

Within the application circuit given the same voltage ratings as above apply for the supply line.

### **Circuit Description**

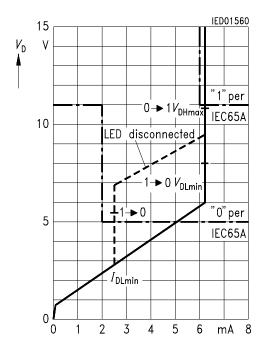

In IEC 65A, the following values are specified for 24-VDC input stages of type 2:

| Level  | Input Voltage                         | Input Current          |

|--------|---------------------------------------|------------------------|

| 1<br>0 | min. 11 V<br>max. 11 V<br>or max. 5 V | min. 6 mA<br>max. 2 mA |

The current in the input circuit is determined by the switching element in state "0" and by characteristics of the input stage in state "1".

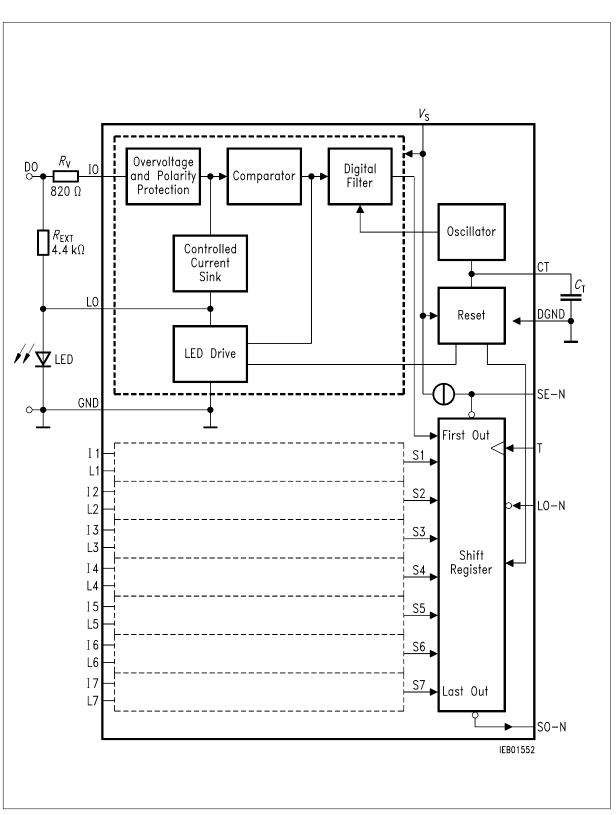

The octal input device FZE 1658G is intended for a configuration comprising two specified external resistors per channel, as shown in the block diagram. As a result the power dissipation within the P-DSO-24-1 package is at a minimum.

The voltage dependent current through the external resistor  $R_{EXT}$  is compensated by a negative differential resistance of the current sink across pins E and L, therefore input D behaves like a constant current sink.

The comparator assigns level 1 or 0 to the voltage present at input E. To improve interference protection, the comparator is provided with hysteresis and a delay element.

A status LED is connected in series with the input circuit ( $R_{EXT}$  and current sink). The LED drive short-circuits the status LED if the comparator detects "0". A constant current sink in parallel with the LED reduces the operating current of the LED, and a voltage limiter ensures that the input circuit remains operational if the LED is interrupted. The specified switching thresholds may change if the LED is interrupted.

For each channel a digital filter is provided which samples the comparator signal at a rate provided by the clock oscillator. The digital filter is designed as a 5-section shift register. If any four out of 5 sampling values are identical, the output S changes to the corresponding state.

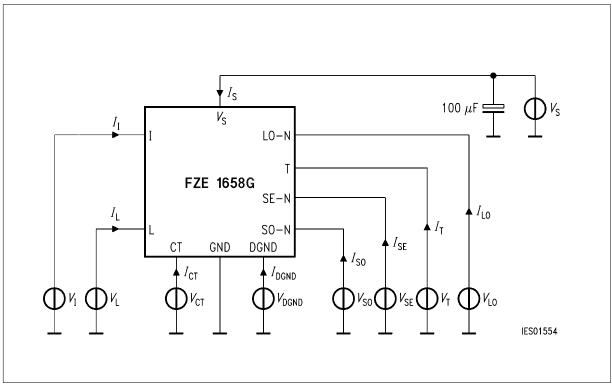

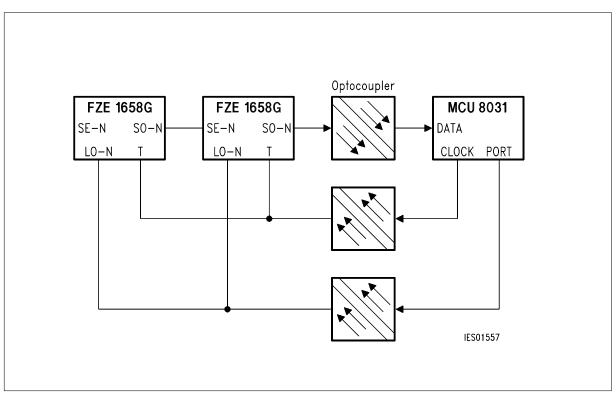

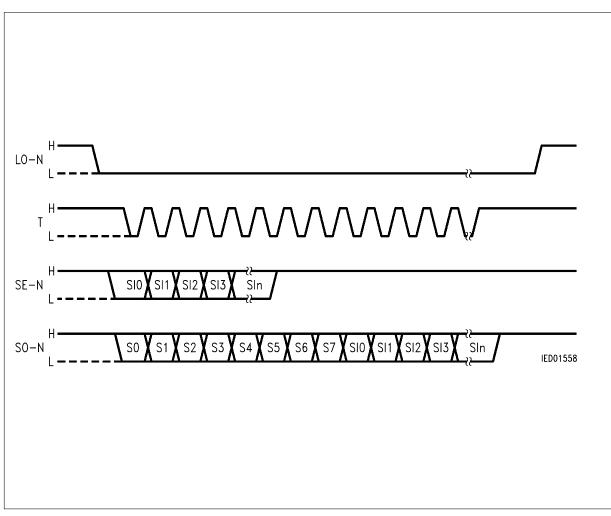

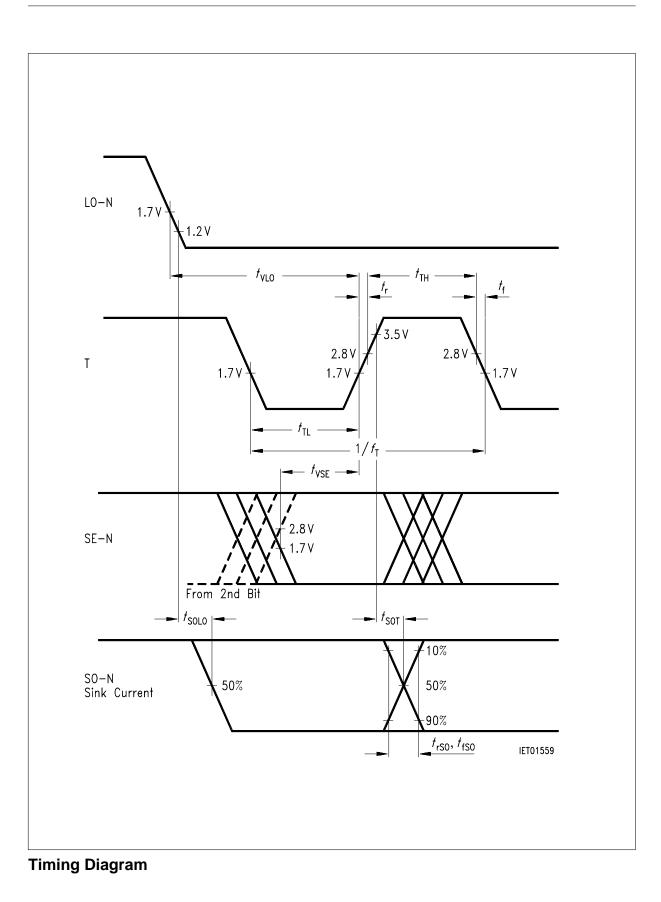

On a falling edge at input LO-N, the parallel data S0 - S7 are clocked into the output shift register. The data can be shifted out serially to the output SO-N by the clock signal T, with a "1" at the input being represented by a L-signal at the output SO-N. The serial interface of the shift register fits the synchronous interface of the 8051 microcontroller (**see diagram Serial Data Output Function**). By connecting output SO-N to input SE-N of the next device, several FZE 1658G can be cascaded (**see Application Circuit**). SO-N is designed as an open-drain output. SE-N has an internal pull-up current source. Inputs SE-N, T and SO-N have Schmitt trigger characteristics. The device has separate ground pins for the input circuitry (GND) and for the logic (DGND). If the supply voltage falls below  $V_{\rm USR}$  or CT is connected to DGND, the output shift register will be cleared and the output SO-N disabled. If the supply voltage is too low, the LED drives will also be disabled, i.e. the LED lights as soon as current flows in the input circuit.

**Block Diagram**

### Absolute Maximum Ratings

$T_{\rm i} = -40$  to 150 °C

| Parameter                                                                   | Symbol                                             | Limit                           | Values                  | Unit                 | Notes                                                                                |

|-----------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|-------------------------|----------------------|--------------------------------------------------------------------------------------|

|                                                                             |                                                    | min.                            | max.                    | -                    |                                                                                      |

| Transient input current inputs 10 - 17                                      | I                                                  | - 0.6<br>- 1.2<br>- 2.5         | 0.6<br>1.2<br>2.5       | A<br>A<br>A          | $t_{50\%} \le 50 \ \mu s$<br>$t_{50\%} \le 1.2 \ \mu s$<br>$t_{50\%} \le 50 \ ns$    |

| Ground current                                                              |                                                    | - 5<br>- 10                     | 5<br>10                 | A<br>A               | t <sub>50 %</sub> ≤ 50 μs<br>t <sub>50 %</sub> ≤ 50 ns                               |

| Junction temperature                                                        | Tj                                                 | - 40                            | 150                     | °C                   |                                                                                      |

| Storage temperature                                                         | Ts                                                 | - 50                            | 125                     | °C                   |                                                                                      |

| Thermal resistance<br>System/air                                            | R <sub>thja</sub>                                  |                                 | 95                      | K/W                  | soldered-in                                                                          |

| Transient thermal resistance;<br>Same current through all<br>inputs I0 - I7 | $egin{array}{c} Z_{ m th} \ Z_{ m th} \end{array}$ |                                 | 0.15<br>0.4             | K/W<br>K/W           | 50 μs pulse<br>120 μs pulse                                                          |

| Supply voltage                                                              | Vs                                                 | - 0.3                           | 65                      | V                    |                                                                                      |

| Ground offset DGND to GND                                                   |                                                    | - 4                             | 4                       | V                    | $V_{\rm DGND}$ < $V_{\rm S}$                                                         |

| Current at the LED outputs                                                  | IL                                                 | - 15<br>- 500<br>- 250<br>- 125 | 15<br>500<br>250<br>125 | mA<br>mA<br>mA<br>mA | t <sub>50 %</sub> ≤ 50 μs<br>t <sub>50 %</sub> ≤ 1.2 μs<br>t <sub>50 %</sub> ≤ 50 μs |

| Voltage at<br>T, LO-N, SO-N, SE-N                                           | V <sub>LOG</sub>                                   | - 4<br>- 0.3                    | 9<br>9                  | V<br>V               | referred to DGND                                                                     |

| Capacitance at CT                                                           | Сст                                                |                                 | 2                       | μF                   | when $V_{\rm S}$ falls below $V_{\rm CT}$                                            |

| ESD voltage 100 pF / 1.5 k $\Omega$                                         | V <sub>ESD</sub>                                   | 1000                            | 1000                    | V                    | MIL Std. 883<br>Meth. 3015                                                           |

All voltages are, unless otherwise specified, referred to GND. This also applies to the operating range and the characteristics.

### **Operating Range**

| Parameter                                          | Symbol                                        | Limit        | Values   | Unit   | Notes                                |  |

|----------------------------------------------------|-----------------------------------------------|--------------|----------|--------|--------------------------------------|--|

|                                                    |                                               | min.         | max.     |        |                                      |  |

| Supply voltage                                     | Vs                                            | 10           | 48       | V      | Note power dissipation <sup>1)</sup> |  |

| Supply voltage rise                                | SR <sub>VS</sub>                              | - 0.1        | 1        | V/µs   |                                      |  |

| Supply voltage                                     | $V_{\rm S}$ - $V_{\rm DGND}$                  | 9            |          | V      | 2)                                   |  |

| GND potential difference                           | $V_{DGND}$                                    | - 1.5        | 1.5      | V      |                                      |  |

| Input terminal current                             | I <sub>IT</sub>                               | - 10         | 10       | mA     |                                      |  |

| Input voltage SE-N, T, LO-N                        | $V_{IH} = V_{IL}$                             | 2.8<br>- 0.5 | 6<br>1.7 | V<br>V |                                      |  |

| Input current SE-N, T, LO-N                        | I                                             | - 1          | 1        | mA     | Clamp current                        |  |

| Junction temperature                               | T <sub>j</sub>                                | - 25         | 150      | °C     |                                      |  |

| Ambient temperature                                | T <sub>A</sub>                                | - 25         | 105      | °C     | Dependent on $R_{\rm th}$            |  |

| Clock frequency                                    | $f_{T}$                                       |              | 1        | MHz    |                                      |  |

| Clock pulse width H or L                           | $t_{\rm TH}, t_{\rm TL}$                      | 300          |          | ns     |                                      |  |

| SE-N set up time to T $\uparrow$                   | t <sub>VSE</sub>                              | 300          |          | ns     |                                      |  |

| LO-N set up time to T $\uparrow$                   | t <sub>VLO</sub>                              | 1.2          |          | μs     |                                      |  |

| SE-N, LO-N, T rise and fall time within thresholds | <i>t</i> <sub>r</sub> , <i>t</i> <sub>f</sub> |              | 3        | μs     | 3)                                   |  |

<sup>1)</sup> Input voltages may rise before the supply voltage. Full function at  $V_{\rm S} > V_{\rm VSRO}$  (see Characteristics).

- <sup>2)</sup> Limits GND potential difference at minimum supply voltage.

- <sup>3)</sup> Also applies to several cascaded FZE 1658G (note dependence with clock frequency).

For definition of timing items, see timing diagram.

### Characteristics

$V_{\rm S}$  = 15 V to 30 V;  $V_{\rm DGND}$  = 0,  $T_{\rm j}$  = - 25 °C <  $T_{\rm j}$  < 125 °C

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |         |  |  |  |

|-----------|--------|--------------|------|------|------|----------------|---------|--|--|--|

|           |        | min.         | typ. | max. |      |                | Circuit |  |  |  |

|           |        |              |      |      |      |                |         |  |  |  |

| $V_{DH}$         |                                                                                        |                                                                                                        | 10.85<br>1)                                                                                            | V                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DL}$         | 8                                                                                      |                                                                                                        |                                                                                                        | V                                                                                                                                                                                                                                                                                        | $V_{\rm L} \leq 2.2 \ {\rm V}$                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{DHY}$        | 1                                                                                      |                                                                                                        |                                                                                                        | V                                                                                                                                                                                                                                                                                        | $V_{\rm L} \leq 2.2 \ {\rm V}$                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sub>DLL</sub> | 2.5                                                                                    |                                                                                                        |                                                                                                        | mA                                                                                                                                                                                                                                                                                       | $I_{\text{LED}} = 0$                                                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $I_{DH}$         | 6.2 <sup>1)</sup>                                                                      |                                                                                                        | 8                                                                                                      | mA                                                                                                                                                                                                                                                                                       | $V_{\rm L} \le 3.5 \text{ V},$<br>$V_{\rm D} = 11 \dots 30 \text{ V}$                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $I_{DL}$         | 5                                                                                      |                                                                                                        | 7                                                                                                      | mA                                                                                                                                                                                                                                                                                       | $V_{\rm L} = V_{\rm LL},$<br>$V_{\rm D} = 5 \text{ V}$                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $I_{\rm IC  +}$  |                                                                                        |                                                                                                        | 1                                                                                                      | mA                                                                                                                                                                                                                                                                                       | $V_{\rm I}$ = 30 V <sup>2)</sup>                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{\rm IT +}$   | 35                                                                                     |                                                                                                        | 75                                                                                                     | V                                                                                                                                                                                                                                                                                        | $I_1 = 10 \text{ mA},$<br>$T_j = 25 \ ^{\circ}\text{C}^{2)}$                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $I_{\rm IC-}$    | - 1                                                                                    |                                                                                                        |                                                                                                        | mA                                                                                                                                                                                                                                                                                       | $V_{\rm I} = -30 \ {\rm V}^{2)}$                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{IT}$ –       | - 75                                                                                   |                                                                                                        | - 35                                                                                                   | V                                                                                                                                                                                                                                                                                        | $I_1 = -10 \text{ mA},$<br>$T_j = 25 \text{ °C}^{2}$                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | $V_{DL}$<br>$V_{DHY}$<br>$I_{DLL}$<br>$I_{DH}$<br>$I_{DL}$<br>$I_{IC +}$<br>$I_{IC -}$ | $V_{DL}$ 8 $V_{DHY}$ 1 $I_{DLL}$ 2.5 $I_{DH}$ 6.2 <sup>1)</sup> $I_{DL}$ 5 $I_{IC +}$ 35 $I_{IC -}$ -1 | $V_{DL}$ 8 $V_{DHY}$ 1 $I_{DLH}$ 2.5 $I_{DL}$ 6.2 <sup>1)</sup> $I_{DL}$ 5 $I_{IC +}$ 35 $I_{IC -}$ -1 | Image: 1 min matrix1 min matrix $V_{\text{DL}}$ 8Image: 1 min matrix $V_{\text{DHY}}$ 1Image: 2 min matrix $I_{\text{DL}}$ 2.5Image: 2 min matrix $I_{\text{DH}}$ 6.2 <sup>1)</sup> 8 $I_{\text{DH}}$ 57 $I_{\text{DL}}$ 51 $I_{\text{IC}+}$ 3575 $I_{\text{IC}-}$ -1Image: 2 min matrix | VDN       I       I       I       I       V $V_{DL}$ 8       I       V       V $V_{DHY}$ 1       I       V $I_{DLY}$ 2.5       I       mA $I_{DL}$ 6.2 <sup>1)</sup> 8       mA $I_{DL}$ 5       7       mA $I_{IC+}$ 35       75       V $I_{IC-}$ -1       I       mA | VDHII $V_{DL}$ 8 $V$ $V_L \le 2.2 V$ $V_{DHY}$ 1 $V$ $V_L \le 2.2 V$ $I_{DLL}$ 2.5 $mA$ $I_{LED} = 0$ $I_{DH}$ $6.2^{10}$ 8 $mA$ $V_L \le 3.5 V, V_D = 11 \dots 30 V$ $I_{DL}$ 57 $mA$ $V_L = V_{LL}, V_D = 5 V$ $I_{IC+}$ 1 $mA$ $V_I = 30 V^{20}$ $V_{IT+}$ 3575 $V$ $I_I = 10 mA, T_I = 25 °C^{20}$ $I_{IC-}$ $-1$ $mA$ $V_I = -30 V^{20}$ $V_{IT-}$ $-75$ $-35$ $V$ $I_I = -10 mA, T_I = -10 m$ |

### Inputs I0 - I7 or D0 - D7 Respectively

<sup>1)</sup> Headroom to IEC 65 A for tolerance of ext. resistor.

<sup>2)</sup> Also valid at  $V_{\rm S}$  = 0.

**Characteristics** (cont'd)  $V_{\rm S}$  = 15 V to 30 V;  $V_{\rm DGND}$  = 0,  $T_{\rm j}$  = - 25 °C <  $T_{\rm j}$  < 125 °C

| Parameter                                       | Symbol           | Limit Values |      |       | Unit | Test Condition                                                                |         |

|-------------------------------------------------|------------------|--------------|------|-------|------|-------------------------------------------------------------------------------|---------|

|                                                 |                  | min.         | typ. | max.  |      |                                                                               | Circuit |

| LED Drive L0 - L7                               |                  |              |      |       |      |                                                                               |         |

| Open-load voltage                               | $V_{\sf LO}$     | 3.5          |      | 5     | V    | $V_{\rm D}$ = 24 V,<br>$I_{\rm LED}$ = 0                                      | 2       |

| "Low"- voltage                                  | $V_{ m LL}$      | 0            |      | 0.75  | V    | $V_{\rm D}$ = 5 V,<br>$I_{\rm LED}$ = 0                                       | 2       |

| Output current                                  | I <sub>LED</sub> | 3            |      | 5     | mA   | $V_{\rm D} = 11 \dots 30 \text{ V},$<br>$V_{\rm L} = 1.5 \dots 3 \text{ V}$   | 2       |

| Output current                                  | I <sub>LED</sub> | 1.5          |      | 6     | mA   | $V_{\rm D} = 11 \dots 30 \text{ V},$<br>$V_{\rm L} = 1.2 \dots 3.5 \text{ V}$ | 2       |

| Power down<br>output current                    | IL               | - 0.12       |      |       | mA   | $V_{\rm S}$ < $V_{\rm VSRU}$                                                  | 1       |

| Propagation delay<br>rising and falling<br>edge | t <sub>DL</sub>  | 7.5          |      | 75    | μs   | $V_{\rm D}$ = 12 V $\leftrightarrows$ 7 V                                     | 2       |

| Oscillator                                      |                  |              |      |       |      |                                                                               |         |

| CT source/sink current                          | I <sub>CT</sub>  | 150          |      | 250   | μA   |                                                                               | 1       |

| Frequency                                       | fст              | 1            |      | 1.5   | kHz  | <i>C</i> <sub>T</sub> = 39 nF                                                 | 2       |

| Upper switching threshold                       | $V_{\rm CTP}$    | 3.3          |      | 4.3   | V    |                                                                               | 2       |

| Lower switching threshold                       | $V_{\rm CTN}$    | 1.4          |      | 2.2   | V    |                                                                               | 2       |

| Reset threshold                                 | V <sub>CTR</sub> | 0.8          |      | 1.4   | V    |                                                                               | 1       |

| Reset input current                             | I <sub>CTR</sub> | - 300        |      | - 150 | μA   | $V_{\rm CT}$ = 0.8 V                                                          | 1       |

| Signal delay                                    | t <sub>DFI</sub> | 2            |      | 4     | ms   | <i>C</i> <sub>T</sub> = 39 nF                                                 | 2       |

**Characteristics** (cont'd)  $V_{\rm S}$  = 15 V to 30 V;  $V_{\rm DGND}$  = 0,  $T_{\rm j}$  = - 25 °C <  $T_{\rm j}$  < 125 °C

| Parameter                                             | Symbol                     | Liı   | mit Valu | les   | Unit | Test Condition                           | Test<br>Circuit |

|-------------------------------------------------------|----------------------------|-------|----------|-------|------|------------------------------------------|-----------------|

|                                                       |                            | min.  | typ.     | max.  |      |                                          |                 |

| 5-V Logic                                             |                            |       |          |       |      |                                          |                 |

| Input current<br>T, LO-N                              | I                          | - 10  |          | 10    | μA   | $V_{\rm i} = 0 \dots 5  {\rm V}$         | 1               |

| Input current SE-N                                    | I <sub>ISE</sub>           | - 600 |          | - 400 | μA   | $V_{i} = 0 3 V$                          | 1               |

| Input current<br>T, LO-N, SE-N                        | <i>I</i> <sub>10</sub>     | 0     |          | 20    | μA   | $V_{\rm i}$ = 0 5 V<br>$V_{\rm S}$ = 0 V | 1               |

| Input capacitance                                     | $C_{I}$                    |       |          | 10    | pF   |                                          | 1               |

| L-output current<br>SO-N                              | I <sub>SOL</sub>           | 5.5   |          | 8     | mA   | <i>V</i> <sub>Q</sub> = 3 5 V            | 1               |

| L-output level SO-N                                   | $V_{\rm SOL}$              | 0     |          | 0.5   | V    | $I_{\rm SO}$ = 2 mA                      | 1               |

| H-leakage current<br>SO-N                             | I <sub>SOH</sub>           | 0     |          | 50    | μA   | $V_{\rm SO}$ = 5 V                       | 1               |

| Output<br>capacitance SO-N                            | $C_{\mathrm{SOH}}$         |       |          | 20    | pF   | $V_{\rm SO}$ = 1.5 V                     | 1               |

| Rise/fall time of<br>output current<br>SO-N           | $t_{\rm rSO}, t_{\rm fSO}$ |       |          | 50    | ns   | V <sub>SO</sub> = 2.5 V                  | 1               |

| Delay time<br>T to SO-N<br>(see timing<br>diagram)    | t <sub>SOT</sub>           |       |          | 150   | ns   | V <sub>SO</sub> = 2.5 V                  | 1               |

| Delay time<br>LO-N to SO-N<br>(see timing<br>diagram) | t <sub>SOLO</sub>          |       |          | 300   | ns   | V <sub>SO</sub> = 2.5 V                  | 1               |

| Hysteresis SE-N,<br>LO-N                              |                            |       | 60       |       | mV   | no 100% testing                          |                 |

**Characteristics** (cont'd)  $V_{\rm S}$  = 15 V to 30 V;  $V_{\rm DGND}$  = 0,  $T_{\rm j}$  = - 25 °C <  $T_{\rm j}$  < 125 °C

| Parameter                                      | Symbol            | Limit Values |      |      | Unit | <b>Test Condition</b>                                                                                                  | Test    |

|------------------------------------------------|-------------------|--------------|------|------|------|------------------------------------------------------------------------------------------------------------------------|---------|

|                                                |                   | min.         | typ. | max. | -    |                                                                                                                        | Circuit |

| Hysteresis<br>Clock input                      |                   |              | 200  |      | mV   | no 100% testing                                                                                                        |         |

| Voltage Supply                                 |                   |              | 1    |      |      |                                                                                                                        |         |

| Current drain static                           | I <sub>S</sub>    | 2            |      | 5    | mA   | $V_{\rm S} = 10 \dots 30 \text{ V}$<br>$V_{\rm LO-N} = 5 \text{ V}$<br>$V_{\rm T} = 5 \text{ V}$<br>$I_{\rm SE-N} = 0$ | 2       |

| Current drain<br>during serial<br>readout      | Is                | 2            |      | 6    | mA   | $V_{\rm S}$ = 10 40 V<br>$V_{\rm LO-N}$ = 0 V<br>$f_{\rm T}$ = 1 MHz                                                   | 2       |

| Current drain<br>during high supply<br>voltage | I <sub>SMAX</sub> |              |      | 7    | mA   | V <sub>S</sub> < 45 V                                                                                                  | 2       |

| Logic ground current                           |                   | - 2.5        |      | 0    | mA   | V <sub>DGND</sub> =<br>- 1.5 1.5 V,<br>LO-N = H                                                                        | 1       |

| Under voltage<br>lockout                       | $V_{\rm VSRO}$    |              |      | 10   | V    | upper switching<br>treshold                                                                                            | 2       |

|                                                | $V_{ m VSRU}$     | 8            |      |      | V    | lower switching threshold                                                                                              | 2       |

|                                                | $V_{ m VSRH}$     | 0.2          |      |      | V    | hysteresis                                                                                                             | 2       |

### **Test Circuit 1**

### **Test Circuit 2**

### **Application Circuit**

Supply Voltage Decoupling Circuit

### Cascading Multiple FZE 1658G

**Serial Data Output Function**

### Input Characteristic with Worst-Case Values per IEC 65A Input D Rest Circuit D

### **Package Outlines**

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

Semiconductor Group

Dimensions in mm