### 1. GENERAL DESCRIPTION

EM78P156EL is an 8-bit microprocessor designed and developed with low-power and high-speed CMOS technology. It is equipped with 1K\*13-bits Electrical One Time Programmable Read Only Memory (OTP-ROM). It provides a PROTECTION bit to prevent user's code in the OTP memory from being intruded. 6 OPTION bits are also available to meet user's requirements.

With its OTP-ROM feature, the EM78P156EL is able to offer a convenient way of developing and verifying user's programs. Moreover, user can take advantage of EMC Writer to easily program his development code.

### 2. FEATURES

- Operating voltage range : 2.3V~5.5V

- Operating temperature range: 0°C~70°C

- Operating frequency rang (base on 2 clocks ):

- \* Crystal mode: DC~20MHz at 5V, DC~8MHz at 3V, DC~4MHz at 2.3V.

- \* ERC mode: DC~4MHz at 5V, DC~4MHz at 3V, DC~4MHz at 2.3V.

- Low power consumption:

- \* Less then 1.6 mA at 5V/4MHz

- \* Typically 15 µA at 3V/32KHz

- \* Typically 1 µA during sleep mode

- 1K × 13 bits on chip ROM

- One security register to prevent intrusion of OTP memory codes

- One configuration register to accommodate user's requirements

- 48× 8 bits on chip registers (SRAM, general purpose register)

- 2 bi-directional I/O ports

- 5 level stacks for subroutine nesting

- 8-bit real time clock/counter (TCC) with selective signal sources, trigger edges, and overflow interrupt

- Two clocks per instruction cycle

- Power down (SLEEP) mode

- Three available interruptions

- \* TCC overflow interrupt

- \* Input-port status changed interrupt (wake up from sleep mode)

- \* External interrupt

- Programmable free running watchdog timer

- 8 programmable pull-high pins

- 7 programmable pull-down pins

- 8 programmable open-drain pins

- 2 programmable R-option pins

- Package types:

\* 18 pin DIP 300mil : EM78P156ELP \* 18 pin SOP(SOIC) 300mil : EM78P156ELM

\* 20 pin SSOP 209mil : EM78P156ELAS \* 20 pin SSOP 209mil : EM78P156ELKM

- 99.9% single instruction cycle commands

- The transient point of system frequency between HXT and LXT is around 400KHz

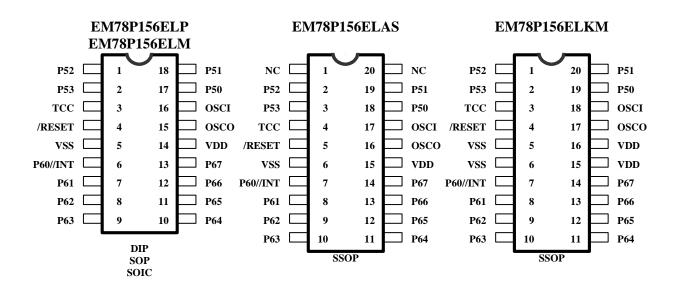

## 3. PIN ASSIGNMENTS

Fig. 1 Pin Assignment

Table 1 EM78P156ELP and EM78P156ELM Pin Description

| Symbol  | Pin No.         | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Function                                                                           |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| VDD     | 14              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | * Power supply.                                                                    |

| OSCI    | 16              | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | * XTAL type: Crystal input terminal or external clock input pin.                   |

| 0001    | 10              | <u>'</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

|         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | * XTAL type: Output terminal for crystal oscillator or external clock input pin.   |

| osco    | 15              | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,                                                                                  |

|         |                 | * Power supply.  * XTAL type: Crystal input terminal or external clock input pin.  * ERC type: RC oscillator input pin.  * XTAL type: Output terminal for crystal oscillator or external clock I/O  * RC type: Instruction clock output.  * External clock signal input.  * The real time clock/counter (with Schmitt trigger input pin), must VDD or VSS if not in use.  * Input pin with Schmitt trigger. If this pin remains at logic low, the will also remain in reset condition.  * P50~P53 are bi-directional I/O pins.  * P50 and P51 can also be defined as the R-option pins.  * P50~P52 can be pulled-down by software.  * P60~P67 are bi-directional I/O pins.  * These can be pulled-high or can be open-drain by software prog P60~P63 can also be pulled-down by software.  I * External interrupt pin triggered by falling edge. | ÿ i                                                                                |

| тсс     | 3               | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | * The real time clock/counter (with Schmitt trigger input pin), must be tied to    |

| 100     | )               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 = 0. 100                                                                         |

| /RESET  | 4               | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | * Input pin with Schmitt trigger. If this pin remains at logic low, the controller |

| /KLOL1  | Τ               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

|         | 17 18           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

| P50~P53 | 17, 18,<br>1. 2 | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · · ·                                                                              |

|         | 1, 2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

|         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

| P60~P67 | 6~13            | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

|         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    |

| /INT    | 6               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | * External interrupt pin triggered by falling edge.                                |

| VSS     | 5               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | * Ground.                                                                          |

### Table 2 EM78P156ELAS Pin Description

| Symbol  | Pin No.         | Туре | Function                                                                                                                                                         |

|---------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD     | 15              | -    | * Power supply.                                                                                                                                                  |

| osci    | 17              | I    | * XTAL type: Crystal input terminal or external clock input pin. * ERC type: RC oscillator input pin.                                                            |

| osco    | 16              | I/O  | * XTAL type: Output terminal for crystal oscillator or external clock input pin. * RC type: Instruction clock output. * External clock signal input.             |

| тсс     | 4               | I    | * The real time clock/counter (with Schmitt trigger input pin), must be tied to VDD or VSS if not in use.                                                        |

| /RESET  | 5               | I    | * Input pin with Schmitt trigger. If this pin remains at logic low, the controller will also remain in reset condition.                                          |

| P50~P53 | 18, 19,<br>2, 3 | I/O  | * P50~P53 are bi-directional I/O pins.  * P50 and P51 can also be defined as the R-option pins.  * P50~P52 can be pulled-down by software.                       |

| P60~P67 | 7~14            | I/O  | * P60~P67 are bi-directional I/O pins.  * These can be pulled-high or can be open-drain by software programming.  * P60~P63 can also be pulled-down by software. |

| /INT    | 7               | I    | * External interrupt pin triggered by falling edge.                                                                                                              |

| VSS     | 6               | -    | * Ground.                                                                                                                                                        |

### Table 3 EM78P156ELKM Pin Description

| Symbol  | Pin No.         | Type | Function                                                                                                                                                         |

|---------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD     | 15,16           | -    | * Power supply.                                                                                                                                                  |

| osci    | 18              | I    | * XTAL type: Crystal input terminal or external clock input pin. * ERC type: RC oscillator input pin.                                                            |

| osco    | 17              | I/O  | * XTAL type: Output terminal for crystal oscillator or external clock input pin. * RC type: Instruction clock output. * External clock signal input.             |

| TCC     | 3               | 1    | * The real time clock/counter (with Schmitt trigger input pin), must be tied to VDD or VSS if not in use.                                                        |

| /RESET  | 4               | I    | * Input pin with Schmitt trigger. If this pin remains at logic low, the controller will also remain in reset condition.                                          |

| P50~P53 | 19, 20,<br>1, 2 | I/O  | * P50~P53 are bi-directional I/O pins.  * P50 and P51 can also be defined as the R-option pins.  * P50~P52 can be pulled-down by software.                       |

| P60~P67 | 7~14            | I/O  | * P60~P67 are bi-directional I/O pins.  * These can be pulled-high or can be open-drain by software programming.  * P60~P63 can also be pulled-down by software. |

| /INT    | 7               | I    | * External interrupt pin triggered by falling edge.                                                                                                              |

| VSS     | 5, 6            | •    | * Ground.                                                                                                                                                        |

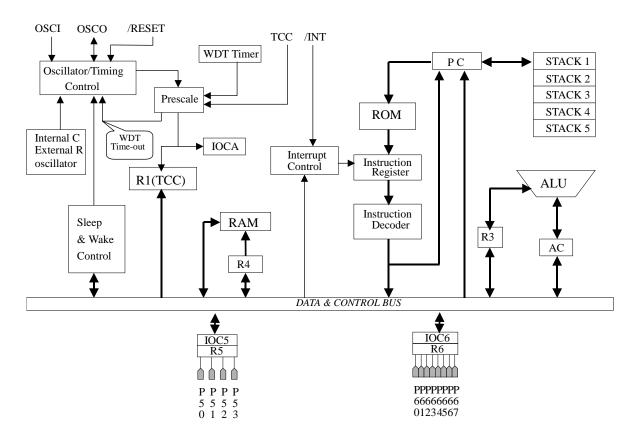

### 4. FUNCTION DESCRIPTION

Fig. 2 Function Block Diagram

# 4.1 Operational Registers

### 1. R0 (Indirect Addressing Register)

R0 is not a physically implemented register. Its major function is to perform as an indirect addressing pointer. Any instruction using R0 as a pointer actually accesses data pointed by the RAM Select Register (R4).

### 2. R1 (Time Clock /Counter)

- Increased by an external signal edge, which is defined by TE bit (CONT-4) through the TCC pin, or by the instruction cycle clock.

- Writable and readable as any other registers.

- Defined by resetting PAB(CONT-3).

- The prescaler is assigned to TCC, if the PAB bit (CONT-3) is reset.

- The contents of the prescaler counter will be cleared only when TCC register is written with a value.

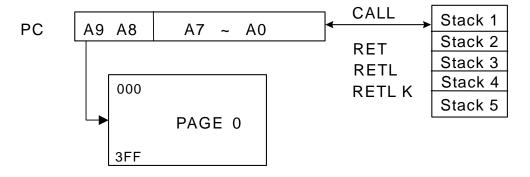

### 3. R2 (Program Counter) & Stack

- Depending on the device type, R2 and hardware stack are 10-bit wide. The structure is depicted in Fig.3.

- Generating 1024×13 bits on-chip OTP ROM addresses to the relative programming instruction codes. One program page is 1024 words long.

- R2 is set as all "0"s when under RESET condition.

- "JMP" instruction allows direct loading of the lower 10 program counter bits. Thus, "JMP" allows PC to go to any location within a page.

- "CALL" instruction loads the lower 10 bits of the PC, and then PC+1 is pushed into the stack. Thus, the subroutine entry address can be located anywhere within a page.

- "RET" ("RETL k", "RETI") instruction loads the program counter with the contents of the top-level stack.

- "ADD R2, A" allows the contents of 'A' to be added to the current PC, and the ninth and tenth bits of the PC are cleared.

- "MOV R2, A" allows to load an address from the "A" register to the lower 8 bits of the PC, and the ninth and tenth bits of the PC are cleared.

- Any instruction that writes to R2 (e.g., "ADD R2,A", "MOV R2,A", "BC R2,6",.....) will cause the ninth and tenth bits (A8~A9) of the PC to be cleared. Thus, the computed jump is limited to the first 256 locations of a page.

- All instruction are single instruction cycle (fclk/2 or fclk/4) except for the instruction that would change the contents of R2. Such instruction will need one more instruction cycle.

Fig. 3 Program Counter Organization

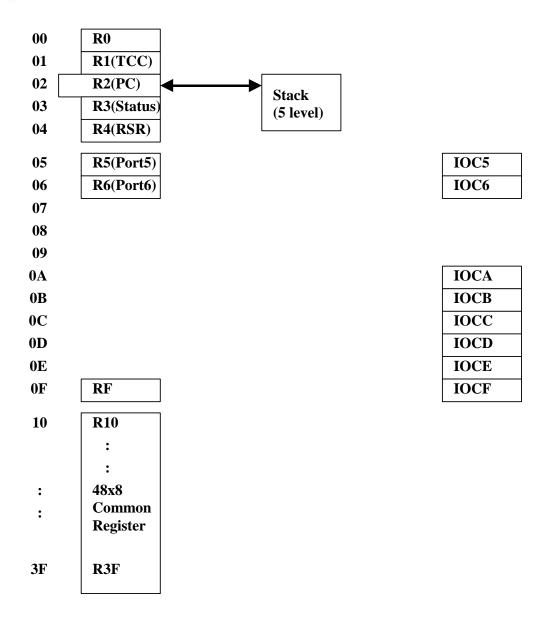

Fig. 4 Data Memory Configuration

### 4. R3 (Status Register)

| 7   | 6   | 5   | 4 | 3 | 2 | 1  | 0 |

|-----|-----|-----|---|---|---|----|---|

| GP2 | GP1 | GP0 | Т | Р | Z | DC | С |

- Bit 0 (C) Carry flag

- Bit 1 (DC) Auxiliary carry flag

- Bit 2 (Z) Zero flag.

Set to "1" if the result of an arithmetic or logic operation is zero.

• Bit 3 (P) Power down bit.

Set to 1 during power on or by a "WDTC" command and reset to 0 by a "SLEP" command.

• Bit 4 (T) Time-out bit.

Set to 1 with the "SLEP" and "WDTC" commands, or during power up and reset to 0 by WDT time-out.

• Bit5 ~7 (GP0 ~ 2) General-purpose read/write bits.

#### 5. R4 (RAM Select Register)

- Bits 0~5 are used to select registers (address: 00~06, 0F~3F) in the indirect addressing mode.

- Bits 6~7 are not used (read only).

- The Bits 6~7 set to "1" at all time.

- Z flag of R3 will set to "1" when R4 content is equal to "3F." When R4=R4+1, R4 content will select as R0.

- See the configuration of the data memory in Fig. 4.

### 6. R5 ~ R6 (Port 5 ~ Port 6)

- R5 and R6 are I/O registers.

- Only the lower 4 bits of R5 are available.

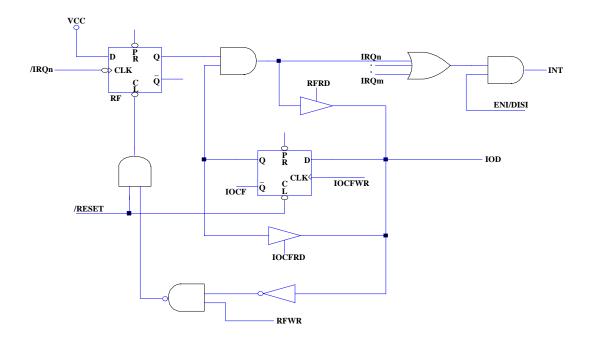

### 7. RF (Interrupt Status Register)

| 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---|---|---|---|---|------|------|------|

| - | - | - | - | - | EXIF | ICIF | TCIF |

<sup>&</sup>quot;1" means interrupt request, and "0" means no interrupt occurs.

- Bit 0 (TCIF) TCC overflow interrupt flag. Set when TCC overflows, reset by software.

- Bit 1 (ICIF) Port 6 input status change interrupt flag. Set when Port 6 input changes, reset by software.

- Bit 2 (EXIF) External interrupt flag. Set by falling edge on /INT pin, reset by software.

- Bits 3 ~ 7 Not used.

- RF can be cleared by instruction but cannot be set.

- IOCF is the interrupt mask register.

- Note that the result of reading RF is the "logic AND" of RF and IOCF.

#### 8. R10 ~ R3F

• All of these are 8-bit general-purpose registers.

### 4.2 Special Purpose Registers

### 1. A (Accumulator)

- Internal data transfer, or instruction operand holding

- It cannot be addressed.

### 2. CONT (Control Register)

|   | 7 | 6    | 5  | 4  | 3   | 2    | 1    | 0    |

|---|---|------|----|----|-----|------|------|------|

| Ī | - | /INT | TS | TE | PAB | PSR2 | PSR1 | PSR0 |

• Bit 0 (PSR0) ~ Bit 2 (PSR2) TCC/WDT prescaler bits.

| PSR2 | PSR1 | PSR0 | TCC Rate | WDT Rate |

|------|------|------|----------|----------|

| 0    | 0    | 0    | 1:2      | 1:1      |

| 0    | 0    | 1    | 1:4      | 1:2      |

| 0    | 1    | 0    | 1:8      | 1:4      |

| 0    | 1    | 1    | 1:16     | 1:8      |

| 1    | 0    | 0    | 1:32     | 1:16     |

| 1    | 0    | 1    | 1:64     | 1:32     |

| 1    | 1    | 0    | 1:128    | 1:64     |

| 1    | 1    | 1    | 1:256    | 1:128    |

- Bit 3 (PAB) Prescaler assignment bit.

- 0: TCC

- 1: WDT

- Bit 4 (TE) TCC signal edge

- 0: increment if the transition from low to high takes place on TCC pin

- 1: increment if the transition from high to low takes place on TCC pin

- Bit 5 (TS) TCC signal source

- 0: internal instruction cycle clock

- 1: transition on TCC pin

- Bit 6 (/INT) Interrupt enable flag

- 0: masked by DISI or hardware interrupt

- 1: enabled by ENI/RETI instructions

- Bit 7 Not used.

- CONT register is both readable and writable.

### 3. IOC5 ~ IOC6 (I/O Port Control Register)

- "1" put the relative I/O pin into high impedance, while "0" defines the relative I/O pin as output.

- Only the lower 4 bits of IOC5 can be defined.

- IOC5 and IOC6 registers are both readable and writable.

#### 4. IOCA (Prescaler Counter Register)

- IOCA register is readable.

- The value of IOCA is equal to the contents of Prescaler counter.

- Down counter.

#### 5. IOCB (Pull-down Control Register)

| 7    | 6    | 5    | 4    | 3 | 2    | 1    | 0    |

|------|------|------|------|---|------|------|------|

| /PD7 | /PD6 | /PD5 | /PD4 | - | /PD2 | /PD1 | /PD0 |

- Bit 0 (/PD0) Control bit is used to enable the pull-down of P50 pin.

- 0: Enable internal pull-down

- 1: Disable internal pull-down

- Bit 1 (/PD1) Control bit is used to enable the pull-down of P51 pin.

- Bit 2 (/PD2) Control bit is used to enable the pull-down of P52 pin.

- Bit 3 Not used.

- Bit 4 (/PD4) Control bit is used to enable the pull-down of P60 pin.

- Bit 5 (/PD5) Control bit is used to enable the pull-down of P61 pin.

- Bit 6 (/PD6) Control bit is used to enable the pull-down of P62 pin.

- Bit 7 (/PD7) Control bit is used to enable the pull-down of P63 pin.

- IOCB Register is both readable and writable.

#### 6. IOCC (Open-drain Control Register)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| OD7 | OD6 | OD5 | OD4 | OD3 | OD2 | OD1 | OD0 |

- Bit 0 (OD0) Control bit is used to enable the open-drain of P60 pin.

- 0: Disable open-drain output

- 1: Enable open-drain output

- Bit 1 (OD1) Control bit is used to enable the open-drain of P61 pin.

- Bit 2 (OD2) Control bit is used to enable the open-drain of P62 pin.

- Bit 3 (OD3) Control bit is used to enable the open-drain of P63 pin.

- Bit 4 (OD4) Control bit is used to enable the open-drain of P64 pin.

- Bit 5 (OD5) Control bit is used to enable the open-drain of P65 pin.

- Bit 6 (OD6) Control bit is used to enable the open-drain of P66 pin.

- Bit 7 (OD7) Control bit is used to enable the open-drain of P67 pin.

- IOCC Register is both readable and writable.

### 7. IOCD (Pull-high Control Register)

| ĺ | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---|------|------|------|------|------|------|------|------|

| I | /PH7 | /PH6 | /PH5 | /PH4 | /PH3 | /PH2 | /PH1 | /PH0 |

- Bit 0 (/PH0) Control bit is used to enable the pull-high of P60 pin.

- 0: Enable internal pull-high

- 1: Disable internal pull-high

- Bit 1 (/PH1) Control bit is used to enable the pull-high of P61 pin.

- Bit 2 (/PH2) Control bit is used to enable the pull-high of P62 pin.

- Bit 3 (/PH3) Control bit is used to enable the pull-high of P63 pin.

- Bit 4 (/PH4) Control bit is used to enable the pull-high of P64 pin.

- Bit 5 (/PH5) Control bit is used to enable the pull-high of P65 pin.

- Bit 6 (/PH6) Control bit is used to enable the pull-high of P66 pin.

- Bit 7 (/PH7) Control bit is used to enable the pull-high of P67 pin.

- IOCD Register is both readable and writable.

### 8. IOCE (WDT Control Register)

| 7    | 6   | 5 | 4   | 3 | 2 | 1 | 0 |

|------|-----|---|-----|---|---|---|---|

| WDTE | EIS | - | ROC | - | - | - | - |

- Bit 7 (WDTE) Control bit used to enable Watchdog timer.

- 0: Disable WDT.

- 1: Enable WDT.

WDTE is both readable and writable.

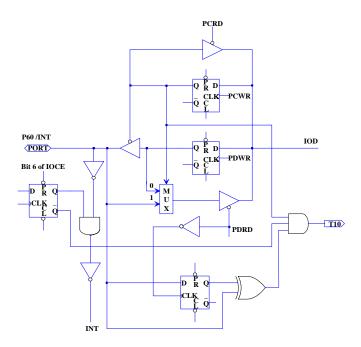

- Bit 6 (EIS) Control bit is used to define the function of P60 (/INT) pin.

- 0: P60, bi-directional I/O pin.

- 1: /INT, external interrupt pin. In this case, the I/O control bit of P60 (bit 0 of IOC6) must be set to "1". When EIS is "0", the path of /INT is masked. When EIS is "1", the status of /INT pin can also be read by way of reading Port 6 (R6). Refer to Fig. 7(a).

EIS is both readable and writable.

- Bit 4 (ROC) ROC is used for the R-option.

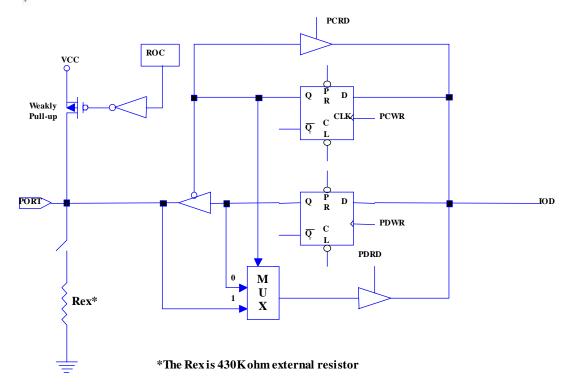

- Setting the ROC to "1" will enable the status of R-option pins (P50~P51) that are read by the controller. Clearing the ROC will disable the R-option function. If the R-option function is selected, user must connect the P51 pin or/and P50 pin to VSS with a  $430 \text{K}\Omega$  external resistor (Rex). If the Rex is connected/disconnected, the status of P50 (P51) is read as "0"/"1". Refer to Fig. 8.

- Bits 0~3,5 Not used.

### 9. IOCF (Interrupt Mask Register)

| 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---|---|---|---|---|------|------|------|

| - | - | - | = | - | EXIE | ICIE | TCIE |

- Bit 0 (TCIE) TCIF interrupt enable bit.

- 0: disable TCIF interrupt

- 1: enable TCIF interrupt

- Bit 1 (ICIE) ICIF interrupt enable bit.

- 0: disable ICIF interrupt

- 1: enable ICIF interrupt

- Bit 2 (EXIE) EXIF interrupt enable bit.

- 0: disable EXIF interrupt

- 1: enable EXIF interrupt

- Bits 3~7 Not used.

- Individual interrupt is enabled by setting its associated control bit in the IOCF to "1".

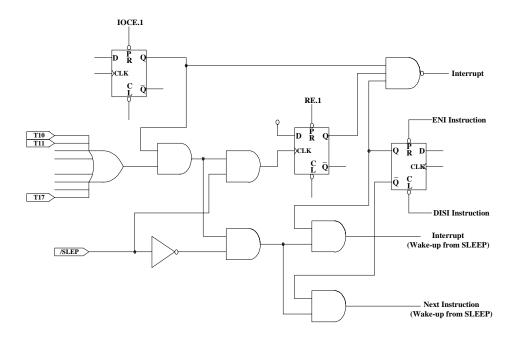

- Global interrupt is enabled by the ENI instruction and is disabled by the DISI instruction. Refer to Fig.

10

- IOCF register is both readable and writable.

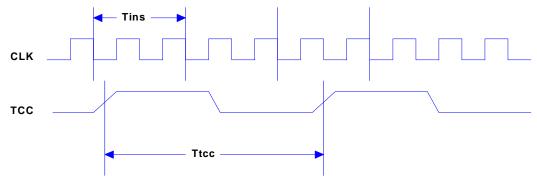

#### 4.3 TCC/WDT & Prescaler

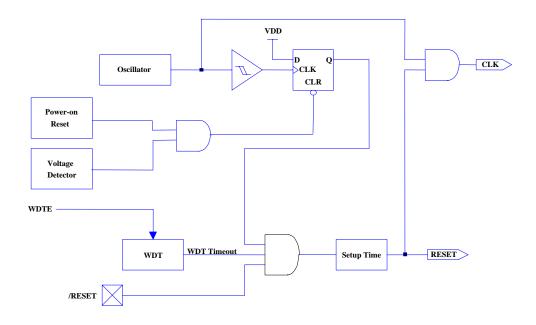

An 8-bit counter available as prescaler for the TCC or WDT. The prescaler is available for either the TCC or WDT only at any given time, and the PAB bit of the CONT register is used to determine the prescaler assignment. The PSR0~PSR2 bits determine the ratio. The prescaler is cleared each time the instruction is written to TCC under TCC mode. The WDT and prescaler, when assigned to WDT mode, are cleared by the "WDTC" or "SLEP" instructions. Fig. 5 depicts the circuit diagram of TCC/WDT.

- R1 (TCC) is an 8-bit timer/counter. The clock source of TCC can be internal or external clock input (edge selectable from TCC pin). If TCC signal source is from internal clock, TCC will increase by 1 at every instruction cycle (without prescaler). Referring to Fig. 5, CLK=Fosc/2 or CLK=Fosc/4 application is determined by the CODE Option bit CLK status. CLK=Fosc/2 is used if CLK bit is "0", and CLK=Fosc/4 is used if CLK bit is "1". If TCC signal source comes from external clock input, TCC is increased by 1 at every falling edge or rising edge of TCC pin.

- The watchdog timer is a free running on-chip RC oscillator. The WDT will keep on running even when the oscillator driver has been turned off (i.e. in sleep mode). During normal operation or sleep mode, a WDT time-out (if enabled) will cause the device to reset. The WDT can be enabled or disabled any time during normal mode by software programming. Refer to WDTE bit of IOCE register. Without prescaler, the WDT time-out period is approximately 18 ms<sup>1</sup> (default).

Fig. 5 Block Diagram of TCC and WDT

This specification is subject to change without prior notice.

<sup>&</sup>lt;sup>1</sup> <Note>: Vdd = 5V, set up time period = 16.8ms ± 30% Vdd = 3V, set up time period = 18ms ± 30%

### 4.4 I/O Ports

The I/O registers, both Port 5 and Port 6, are bi-directional tri-state I/O ports. Port 6 can be pulled high internally by software. In addition, Port 6 can also have open-drain output by software. Input status change interrupt (or wake-up) function on Port 6. P50 ~ P52 and P60 ~ P63 pins can be pulled down by software. Each I/O pin can be defined as "input" or "output" pin by the I/O control register (IOC5 ~ IOC6). P50~P51 are the R-option pins enabled by setting the ROC bit in the IOCE register to 1. When the R-option function is used, it is recommended that P50~P51 are used as output pins. When R-option is in enable state, P50~P51 must be programmed as input pins. Under R-option mode, the current/power consumption by Rex should be taken into the consideration to promote energy conservation.

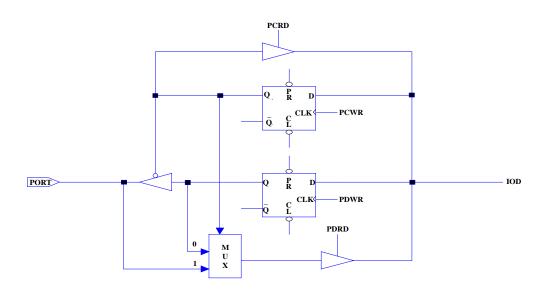

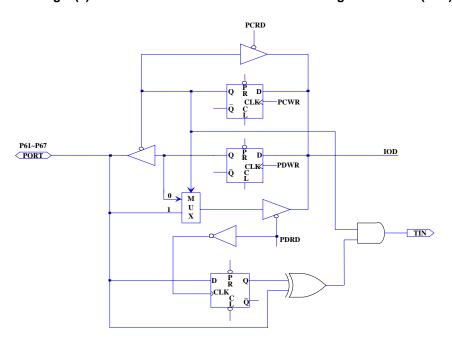

The I/O registers and I/O control registers are both readable and writable. The I/O interface circuits for Port 5 and Port 6 are shown in the following Figures 6, 7(a), 7(b), and Figure 8.

NOTE: Pull-down is not shown in the figure.

Fig. 6 The Circuit of I/O Port and I/O Control Register for Port 5

NOTE: Pull-high (down) and Open-drain are not shown in the figure.

Fig. 7(a) The Circuit of I/O Port and I/O Control Register for P60 (/INT)

NOTE: Pull-high (down) and Open-drain are not shown in the figure.

Fig. 7(b) The Circuit of I/O Port and I/O Control Register for P61~P67

Fig. 7(c) Block Diagram of I/O Port 6 with Input Change Interrupt/Wake-up

Table 4 Usage of Port 6 Input Change Wake-up/Interrupt Function

#### Usage of Port 6 input status changed Wake-up/Interrupt (I) Wake-up from Port 6 Input Status Change (II) Port 6 Input Status Change Interrupt (a) Before SLEEP 1. Read I/O Port 6 (MOV R6,R6) 1. Disable WDT<sup>1</sup> (using very carefully) 2. Execute "ENI" 2. Read I/O Port 6 (MOV R6,R6) 3. Enable interrupt (Set IOCF.1) 3. Execute "ENI" or "DISI" 4. IF Port 6 change (interrupt) 4. Enable interrupt (Set IOCF.1) → Interrupt vector (008H) 5. Execute "SLEP" instruction (b) After Wake-up 1. IF "ENI" → Interrupt vector (008H) 2. IF "DISI" → Next instruction

<sup>&</sup>lt;sup>1</sup> NOTE: Software disables WDT (watchdog timer) but hardware must be enabled before applying Port 6 Change Wake-Up function. (CODE Option Register and Bit 11 (ENWDTB-) set to "1").

Fig. 8 The Circuit of I/O Port with R-option(P50,P51)

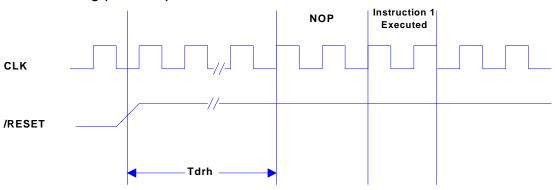

### 4.5 RESET and Wake-up

#### 1. RESET

A RESET is initiated by one of the following events-

- (1) Power on reset.

- (2) /RESET pin input "low", or

- (3) WDT time-out (if enabled).

The device is kept in a RESET condition for a period of approx. 18ms<sup>1</sup> (one oscillator start-up timer period) after the reset is detected. Once the RESET occurs, the following functions are performed. Refer to Fig.9.

- The oscillator is running, or will be started.

- The Program Counter (R2) is set to all "0".

- All I/O port pins are configured as input mode (high-impedance state).

- The Watchdog timer and prescaler are cleared.

- When power is switched on, the upper 3 bits of R3 are cleared.

- The bits of the CONT register are set to all "1" except for the Bit 6 (INT flag).

- The bits of the IOCA register are set to all "1".

- The bits of the IOCB register are set to all "1".

- The IOCC register is cleared.

- The bits of the IOCD register are set to all "1".

- Bit 7 of the IOCE register is set to "1", and Bits 4 and 6 are cleared.

- Bits 0~2 of RF and bits 0~2 of IOCF register are cleared.

The sleep (power down) mode is asserted by executing the "SLEP" instruction. While entering sleep mode, WDT (if enabled) is cleared but keeps on running. The controller can be awakened by-

- (1) External reset input on /RESET pin,

- (2) WDT time-out (if enabled), or

- (3) Port 6 input status changes (if enabled).

The first two cases will cause the EM78P156EL to reset. The T and P flags of R3 can be used to determine the source of the reset (wake-up). The last case is considered the continuation of program execution and the global interrupt ("ENI" or "DISI" being executed) decides whether or not the

<sup>&</sup>lt;sup>1</sup> NOTE: Vdd = 5V, set up time period = 16.8ms  $\pm 30\%$ Vdd = 3V, set up time period = 18ms  $\pm 30\%$

controller branches to the interrupt vector following wake-up. If ENI is executed before SLEP, the instruction will begin to execute from the address 008H after wake-up. If DISI is executed before SLEP, the operation will restart from the succeeding instruction right next to SLEP after wake-up.

Only one of Cases 2 and 3 can be enabled before entering the sleep mode. That is,

[a] if Port 6 Input Status Change Interrupt is enabled before SLEP, WDT must be disabled. by software. However, the WDT bit in the option register remains enabled. Hence, the EM78P156EL can be awakened only by Case 1 or 3.

[b] if WDT is enabled before SLEP, Port 6 Input Status Change Interrupt must be disabled. Hence, the EM78P156EL can be awakened only by Case 1 or 2. Refer to the section on Interrupt.

If Port 6 Input Status Change Interrupt is used to wake-up the EM78P156EL (Case [a] above), the following instructions must be executed before SLEP:

MOV A, @xx000110b ; Select internal TCC clock

**CONTW**

CLR R1 ; Clear TCC and prescaler

MOV A, @xxxx1110b ; Select WDT prescaler

CONTW

WDTC ; Clear WDT and prescaler

MOV A, @0xxxxxxxb ; Disable WDT

**IOW RE**

MOV R6, R6 ; Read Port 6

MOV A, @00000x1xb; Enable Port 6 input change interrupt

**IOW RF**

ENI (or DISI) ; Enable (or disable) global interrupt

SLEP ; Sleep

NOP

One problem user should be aware of, is that after waking up from the sleep mode, WDT would enable automatically. The WDT operation (being enabled or disabled) should be handled appropriately by software after waking up from the sleep mode.

Table 5 The Summary of the Initialized Values for Registers

| Address      | Name           | Reset Type              | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|--------------|----------------|-------------------------|-------|-------|-------|-------|-------|-------|-------|--------|

|              |                | Bit Name                | Χ     | Χ     | Χ     | Χ     | C53   | C52   | C51   | C50    |

| N/A          | IOC5           | Power-On                | U     | U     | U     | U     | 1     | 1     | 1     | 1      |

| IN/A         | 1005           | /RESET and WDT          | U     | U     | U     | U     | 1     | 1     | 1     | 1      |

|              |                | Wake-Up from Pin Change | U     | U     | U     | U     | Р     | Р     | Р     | Р      |

|              |                | Bit Name                | C67   | C66   | C65   | C64   | C63   | C62   | C61   | C60    |

| NI/A         | IOCE           | Power-On                | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1      |

| N/A IOC6     | /RESET and WDT | 1                       | 1     | 1     | 1     | 1     | 1     | 1     | 1     |        |

|              |                | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р     | Р      |

|              |                | Bit Name                | Χ     | /INT  | TS    | TE    | PAB   | PSR2  | PSR1  | PSR0   |

| N/A          | CONT           | Power-On                | 1     | 0     | 1     | 1     | 1     | 1     | 1     | 1      |

| IN/A         | CONT           | /RESET and WDT          | 1     | 0     | 1     | 1     | 1     | 1     | 1     | 1      |

|              |                | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р     | Р      |

|              |                | Bit Name                | -     | -     | -     | -     | -     | -     | -     | -      |

| 0x00         | DO(IAD)        | Power-On                | U     | U     | U     | U     | U     | U     | U     | U      |

| UXUU         | R0(IAR)        | /RESET and WDT          | Р     | Р     | Р     | Р     | Р     | Р     | Р     | Р      |

|              |                | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р     | Р      |

|              |                | Bit Name                | -     | -     | -     | -     | -     | -     | -     | -      |

| 0.01         | D4/TCC\        | Power-On                | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0      |

| 0x01         | R1(TCC)        | /RESET and WDT          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0      |

|              |                | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р     | 0<br>P |

|              |                | Bit Name                | -     | -     | -     | -     | -     | -     | -     | -      |

| 000          | DO(DO)         | Power-On                | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0      |

| 0x02         | R2(PC)         | /RESET and WDT          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0      |

|              |                | Wake-Up from Pin Change | **0/P | **0/P | **0/P | **0/P | **1/P | **0/P | **0/P | **0/P  |

|              |                | Bit Name                | GP2   | GP1   | GP0   | Т     | Р     | Z     | DC    | С      |

| 002          | DO/CD)         | Power-On                | 0     | 0     | 0     | 1     | 1     | U     | U     | U      |

| 0x03         | R3(SR)         | /RESET and WDT          | 0     | 0     | 0     | t     | t     | Р     | Р     | Р      |

|              |                | Wake-Up from Pin Change | Р     | Р     | Р     | t     | t     | Р     | Р     | Р      |

|              |                | Bit Name                | -     | -     | -     | -     | -     | -     | -     | -      |

| 0,04         | D4/DCD)        | Power-On                | 1     | 1     | U     | U     | U     | U     | U     | U      |

| 0x03<br>0x04 | R4(RSR)        | /RESET and WDT          | 1     | 1     | Р     | Р     | Р     | Р     | Р     | Р      |

|              |                | Wake-Up from Pin Change | 1     | 1     | Р     | Р     | Р     | Р     | Р     | Р      |

|              |                | Bit Name                | Χ     | Χ     | Χ     | Χ     | P53   | P52   | P51   | P50    |

| 0.05         | D.             | Power-On                | 0     | 0     | 0     | 0     | U     | U     | U     | U      |

| 0x05         | P5             | /RESET and WDT          | 0     | 0     | 0     | 0     | Р     | Р     | Р     | Р      |

|              |                | Wake-Up from Pin Change | 0     | 0     | 0     | 0     | Р     | Р     | Р     | Р      |

| 0x06         | P6             | Bit Name                | P67   | P66   | P65   | P64   | P63   | P62   | P61   | P60    |

|              |                | Power-On                | U     | U     | U     | U     | U     | U     | U     | U      |

|              |                | /RESET and WDT          | Р     | Р     | Р     | Р     | Р     | Р     | Р     | Р      |

| Address    | Name                                                                                                       | Reset Type              | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                                                                 | Bit 0 |

|------------|------------------------------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|-------|-------|-------|-----------------------------------------------------------------------|-------|

|            |                                                                                                            | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р                                                                     | Р     |

|            |                                                                                                            | Bit Name                | Χ     | Χ     | Χ     | Χ     | Χ     | EXIF  | ICIF                                                                  | TCIF  |

| 0x0F       | DE(IQD)                                                                                                    | Power-On                | U     | U     | U     | U     | U     | 0     | 0                                                                     | 0     |

| OXOI       | IXI (ISIX)                                                                                                 | /RESET and WDT          | U     | U     | U     | U     | U     | 0     | 0                                                                     | 0     |

|            |                                                                                                            | Wake-Up from Pin Change | U     | U     | U     | U     | U     | Р     | Р                                                                     | Р     |

|            |                                                                                                            | Bit Name                | -     | -     | -     | -     | -     | -     | -                                                                     | -     |

| 0x0A       | IOCA                                                                                                       | Power-On                | 1     | 1     | 1     | 1     | 1     | 1     | 1                                                                     | 1     |

| UXUA       | IOCA                                                                                                       | /RESET and WDT          | 1     | 1     | 1     | 1     | 1     | 1     | 1                                                                     | 1     |

|            |                                                                                                            | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р                                                                     | Р     |

|            |                                                                                                            | Bit Name                | /PD7  | /PD6  | /PD5  | /PD4  | Χ     | /PD2  | /PD1                                                                  | /PD0  |

| 0x0B       | IOCB                                                                                                       | Power-On                | 1     | 1     | 1     | 1     | U     | 1     | 1                                                                     | 1     |

| OXOD       | ЮСВ                                                                                                        | /RESET and WDT          | 1     | 1     | 1     | 1     | J     | 1     | 1                                                                     | 1     |

|            |                                                                                                            | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | U     | Р     | Р                                                                     | Р     |

|            |                                                                                                            | Bit Name                | OD7   | OD6   | OD5   | OD4   | OD3   | OD2   | OD1                                                                   | OD0   |

| 0x0C       | IOCC                                                                                                       | Power-On                | 0     | 0     | 0     | 0     | 0     | 0     | 0                                                                     | 0     |

| UXUC       | 1000                                                                                                       | /RESET and WDT          | 0     | 0     | 0     | 0     | 0     | 0     | 0                                                                     | 0     |

|            |                                                                                                            | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р                                                                     | Р     |

|            |                                                                                                            | Bit Name                | /PH7  | /PH6  | /PH5  | /PH4  | /PH3  | /PH2  | /PH1                                                                  | /PH0  |

| 0x0D       | IOCD                                                                                                       | Power-On                | 1     | 1     | 1     | 1     | 1     | 1     | 1                                                                     | 1     |

| OXOD       | ЮСЬ                                                                                                        | /RESET and WDT          | 1     | 1     | 1     | 1     | 1     | 1     | 1                                                                     | 1     |

|            |                                                                                                            | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | P ICIF 0 0 P - 1 1 P /PD1 1 1 P OD1 0 P /PH1 1                        | Р     |

|            |                                                                                                            | Bit Name                | WDTE  | EIS   | Х     | ROC   | Χ     | Χ     | Χ                                                                     | Х     |

| 0x0E       | IOCE                                                                                                       | Power-On                | 1     | 0     | U     | 0     | U     | U     | U                                                                     | U     |

| OXOL       | IOOL                                                                                                       | /RESET and WDT          | 1     | 0     | U     | 0     | U     | U     | U                                                                     | U     |

|            |                                                                                                            | Wake-Up from Pin Change | 1     | Р     | U     | Р     | U     | U     | U                                                                     | U     |

|            |                                                                                                            | Bit Name                | Χ     | Χ     | Χ     | Χ     | Χ     | EXIE  | ICIE                                                                  | TCIE  |

| 0x0F       | IOCE                                                                                                       | Power-On                | U     | U     | U     | U     | U     | 0     | 0                                                                     | 0     |

| 0.01       | IOCA  IOCA  Wake  IOCD  Wake  IOCE  Wake  IOCF  Wake  IOCF  Wake  IOCF  Wake  IOCF  Wake  IOCF  Wake  IOCF | /RESET and WDT          | U     | U     | U     | U     | U     | 0     | 0                                                                     | 0     |

|            |                                                                                                            | Wake-Up from Pin Change | U     | U     | U     | U     | U     | Р     | Р                                                                     | Р     |

|            |                                                                                                            | Bit Name                | -     | -     | -     | -     | -     | -     | -                                                                     | -     |

| 0x10~0x2F  | R10~R2F                                                                                                    | Power-On                | U     | U     | U     | U     | U     | U     | U                                                                     | U     |

| UX 1U~UXZF | 1110~1121                                                                                                  | /RESET and WDT          | Р     | Р     | Р     | Р     | Р     | Р     | P ICIF 0 0 P 1 1 P //PD1 1 1 P OD1 0 P //PH1 1 1 Y U U ICIE 0 0 P U P | Р     |

|            |                                                                                                            | Wake-Up from Pin Change | Р     | Р     | Р     | Р     | Р     | Р     | Р                                                                     | Р     |

<sup>\*\*</sup> To jump address 0x08, or to execute the instruction which is next to the "SLEP" instruction.

X: Not used. U: Unknown or don't care. P: Previous value before reset. t: Check Table 6

### 2. The Status of RST, T, and P of STATUS Register

A RESET condition is initiated by the following events:

- 1. A power-on condition,

- 2. A high-low-high pulse on /RESET pin, and

### 3. Watchdog timer time-out.

The values of T and P, listed in Table 6 are used to check how the processor wakes up. Table 7 shows the events that may affect the status of T and P.

Table 6 The Values of RST, T and P after RESET

| Reset Type                              | Т  | Р  |

|-----------------------------------------|----|----|

| Power on                                | 1  | 1  |

| /RESET during Operating mode            | *P | *P |

| /RESET wake-up during SLEEP mode        | 1  | 0  |

| WDT during Operating mode               | 0  | *P |

| WDT wake-up during SLEEP mode           | 0  | 0  |

| Wake-Up on pin change during SLEEP mode | 1  | 0  |

<sup>\*</sup>P: Previous status before reset

Table 7 The Status of T and P Being Affected by Events.

| Event                                   | Т | Р  |

|-----------------------------------------|---|----|

| Power on                                | 1 | 1  |

| WDTC instruction                        | 1 | 1  |

| WDT time-out                            | 0 | *P |

| SLEP instruction                        | 1 | 0  |

| Wake-Up on pin change during SLEEP mode | 1 | 0  |

<sup>\*</sup>P: Previous value before reset

Fig. 9 Block Diagram of Controller Reset

### 4.6 Interrupt

The EM78P156EL has three falling-edge interrupts listed below:

- (1) TCC overflow interrupt

- (2) Port 6 Input Status Change Interrupt

- (3) External interrupt [(P60, /INT) pin].

Before the Port 6 Input Status Change Interrupt is enabled, reading Port 6 (e.g. "MOV R6,R6") is necessary. Each pin of Port 6 will have this feature if its status changed. Any pin configured as output or P60 pin configured as /INT is excluded from this function. The Port 6 Input Status Changed Interrupt can wake up the EM78P156EL from the sleep mode if Port 6 is enabled prior to going into the sleep mode by executing SLEP. When the chip wakes-up, the controller will continue to execute the succeeding address if the global interrupt is disabled or branch to the interrupt vector 008H if the global interrupt is enabled.

RF is the interrupt status register that records the interrupt requests in the relative flags/bits. IOCF is an interrupt mask register. The global interrupt is enabled by the ENI instruction and is disabled by the DISI instruction. When one of the interrupts (enabled) occurs, the next instruction will be fetched from address 008H. Once in the interrupt service routine, the source of an interrupt can be determined by polling the flag bits in RF. The interrupt flag bit must be cleared by instructions before leaving the interrupt service routine and before interrupts are enabled to avoid recursive interrupts.

The flag (except ICIF bit) in the Interrupt Status Register (RF) is set regardless of the status of its mask bit or the execution of ENI. Note that the outcome of RF will be the logic AND of RF and IOCF (refer to Fig. 10). The RETI instruction ends the interrupt routine and enables the global interrupt (the execution of ENI).

When an interrupt is generated by the INT instruction (enabled), the next instruction will be fetched from address 001H.

Fig. 10 Interrupt Input Circuit

### 4.7 Oscillator

#### 1. Oscillator Modes

The EM78P156EL can be operated in three different oscillator modes, such as External RC oscillator mode (ERC), High XTAL oscillator mode (HXT), and Low XTAL oscillator mode (LXT). User can select one of them by programming MS and HLF in the CODE option register. Table 8 depicts how these three modes are defined.

The up-most limited operation frequency of crystal/resonator on the different VDDs is listed in Table 9.

Table 8 Oscillator Modes Defined by MS and HLP

| Mode                             | MS | HLF | HLP |

|----------------------------------|----|-----|-----|

| ERC(External RC oscillator mode) | 0  | *X  | *X  |

| HXT(High XTAL oscillator mode)   | 1  | 1   | *X  |

| LXT(Low XTAL oscillator mode)    | 1  | 0   | 0   |

<Note> 1. X, Don't care

2. The transient point of system frequency between HXT and LXY is around 400 KHz.

**Table 9 The Summary of Maximum Operating Speeds**

| Conditions                 | VDD | Fxt max.(MHz) |

|----------------------------|-----|---------------|

|                            | 2.3 | 4.0           |

| Two cycles with two clocks | 3.0 | 8.0           |

|                            | 5.0 | 20.0          |

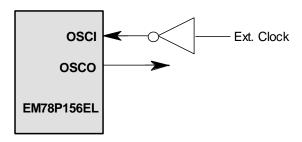

### 2. Crystal Oscillator/Ceramic Resonators (XTAL)

EM78P156EL can be driven by an external clock signal through the OSCI pin as shown in Fig. 11 below.

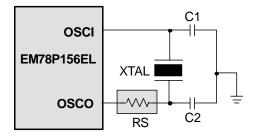

Fig. 11 Circuit for External Clock Input

In the most applications, pin OSCI and pin OSCO can connected with a crystal or ceramic resonator to generate oscillation. Fig. 12 depicts such circuit. The same thing applies whether it is in the HXT mode or in the LXT mode. Table 10 provides the recommended values of C1 and C2. Since each resonator has its own attribute, user should refer to its specification for appropriate values of C1 and C2. RS, a serial resistor, may be necessary for AT strip cut crystal or low frequency mode.

Fig. 12 Circuit for Crystal/Resonator

Table 10 Capacitor Selection Guide for Crystal Oscillator or Ceramic Resonator

| Oscillator Type    | Frequency Mode | Frequency | C1(pF)  | C2(pF)  |

|--------------------|----------------|-----------|---------|---------|

|                    |                | 455 kHz   | 100~150 | 100~150 |

| Ceramic Resonators | HXT            | 2.0 MHz   | 20~40   | 20~40   |

|                    |                | HXT       | 10~30   | 10~30   |

|                    |                | 32.768kHz | 25      | 15      |

|                    | LXT            | 100KHz    | 25      | 25      |

|                    |                | 200KHz    | 25      | 25      |

| Crystal Oscillator |                | 455KHz    | 20~40   | 20~150  |

|                    | HYT            | 1.0MHz    | 15~30   | 15~30   |

|                    | I IXI          | 2.0MHz    | 15      | 15      |

|                    |                | 4.0MHz    | 15      | 15      |

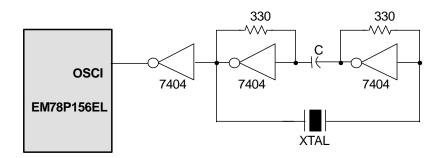

Fig. 13 Circuit for Crystal/Resonator-Series Mode

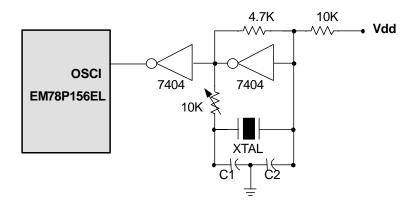

Fig. 14 Circuit for Crystal/Resonator-Parallel Mode

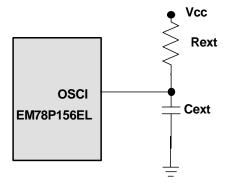

#### 3. External RC Oscillator Mode

For some applications that do not need a very precise timing calculation, the RC oscillator (Fig. 15) offers a lot of cost savings. Nevertheless, it should be noted that the frequency of the RC oscillator is influenced by the supply voltage, the values of the resistor (Rext), the capacitor (Cext), and even by the operation temperature. Moreover, the frequency also changes slightly from one chip to another due to the manufacturing process variation.

In order to maintain a stable system frequency, the values of the Cext should not be less than 20pF, and that the value of Rext should not be greater than 1 M ohm. If they cannot be kept in this range, the frequency is easily affected by noise, humidity, and leakage.

The smaller the Rext in the RC oscillator, the faster its frequency will be. On the contrary, for very low Rext values, for instance, 1  $K\Omega$ , the oscillator becomes unstable because the NMOS cannot discharge the current of the capacitance correctly.

Based on the above reasons, it must be kept in mind that all of the supply voltage, the operation temperature, the components of the RC oscillator, the package types, the way the PCB is layout, will affect the system frequency.

Fig. 15 Circuit for External RC Oscillator Mode

**Table 11 RC Oscillator Frequencies**

| Cext  | Rext | Average Fosc 5V,25°C | Average Fosc 3V,25°C |

|-------|------|----------------------|----------------------|

| 20 pF | 3.3k | 3.92 MHz             | 3.65 MHz             |

|       | 5.1k | 2.67 MHz             | 2.60 MHz             |

|       | 10k  | 1.39MHz              | 1.40 MHz             |

|       | 100k | 149 KHz              | 156 KHz              |

| 100 pF | 3.3k | 1.39 MHz | 1.33 MHz |

|--------|------|----------|----------|

|        | 5.1k | 940 KHz  | 920 KHz  |

| 100 με | 10k  | 480 KHz  | 475 KHz  |

|        | 100k | 52 KHz   | 50 KHz   |

|        | 3.3k | 595 KHz  | 560 KHz  |

| 200 pE | 5.1k | 400 KHz  | 390 KHz  |

| 300 pF | 10k  | 200 KHz  | 200 KHz  |

|        | 100k | 21 KHz   | 20 KHz   |

<Note> 1. Measured on DIP packages.

2. For design reference only.

### 4.8 CODE Option Register

The EM78P156EL has a CODE option word that is not a part of the normal program memory. The option bits cannot be accessed during normal program execution.

Code Option Register and Customer ID Register arrangement distribution:

| Word 0     | Word 1     |

|------------|------------|

| Bit12~Bit0 | Bit12~Bit0 |

#### 1. Code Option Register (Word 0)

| WORD 0 |        |       |      |      |      |      |      |      |      |      |      |      |

|--------|--------|-------|------|------|------|------|------|------|------|------|------|------|

| Bit12  | Bit11  | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| MS     | /ENWDT | CLK   | CS   | HLF  | -    | HLP  | -    | -    | -    | -    | -    | -    |

- Bit 12 (MS):Oscillator type selection.

- 0: RC type

- 1: XTAL type (XTAL1 and XTAL2)

- Bit 11 (/ENWDT): Watchdog timer enable bit.

- 0: Enable

- 1: Disable

- Bit 10 (CLK): Instruction period option bit.

- 0: two oscillator periods.

- 1: four oscillator periods.

Refer to the section on Instruction Set.

- Bit 9 (CS): Code Security Bit

- 0: Security On

- 1: Security Off

- Bit 8 (HLF): XTAL frequency selection

- 0: XTAL2 type (low frequency, 32.768KHz)

1: XTAL1 type (high frequency)

This bit will affect system oscillation only when Bit12 (MS) is "1". When MS is "0", HLF must be "0". <Note>: The transient point of system frequency between HXT and LXY is around 400 KHz.

• Bit 7: Reserved.

The bit set to "1" all the time.

• Bit 6 (HLP): Power selection.

0: Low power

1: High power

• Bit 5~0 : Customer's ID code

#### 2. Customer ID Register (Word 1)

| Bit 12~Bit 0 |  |

|--------------|--|

| XXXXXXXXXXX  |  |

• Bit 12~0: Customer's ID code

#### 4.9 Power On Considerations

Any microcontroller is not guaranteed to start to operate properly before the power supply stays at its steady state. EM78P156EL is equipped with Power On Voltage Detector (POVD) with a detecting level of 1.8V. It will work well if Vdd rise quick enough (50 ms or less). In many critical applications, however, extra devices are still required to assist in solving power-up problems.

#### 4.10 External Power On Reset Circuit

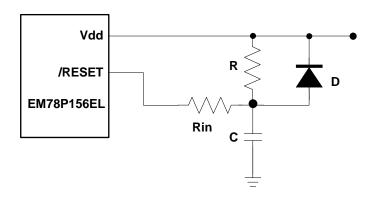

The circuit shown in Fig.16 implements an external RC to produce the reset pulse. The pulse width (time constant) should be kept long enough for Vdd to reached minimum operation voltage. This circuit is used when the power supply has slow rise time. Because the current leakage from the /RESET pin is about  $\pm 5\mu A$ , it is recommended that R should not be greater than 40 K. In this way, the /RESET pin voltage is held below 0.2V. The diode (D) acts as a short circuit at the moment of power down. The capacitor C will discharge rapidly and fully. Rin, the current-limited resistor, will prevent high current or ESD (electrostatic discharge) from flowing to pin /RESET.

Fig. 16 External Power-Up Reset Circuit

## 4.11 Residue-Voltage Protection

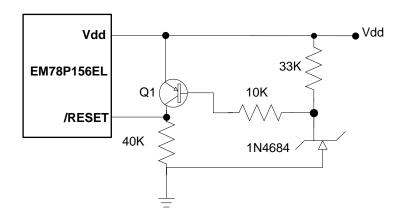

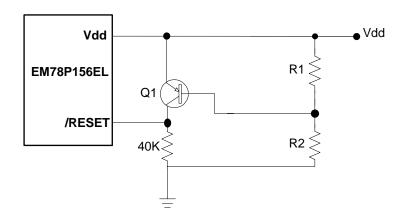

When battery is replaced, device power (Vdd) is taken off but residue-voltage remains. The residue-voltage may trips below Vdd minimum, but not to zero. This condition may cause a poor power on reset. Fig.18 and Fig. 19 show how to build a residue-voltage protection circuit.

Fig. 17 Circuit 1 for the Residue Voltage Protection

Fig. 18 Circuit 2 for the Residue Voltage Protection

#### 4.12 Instruction Set

Each instruction in the instruction set is a 13-bit word divided into an OP code and one or more operands. Normally, all instructions are executed within one single instruction cycle (one instruction consists of 2 oscillator periods), unless the program counter is changed by instruction "MOV R2,A", "ADD R2,A", or by instructions of arithmetic or logic operation on R2 (e.g. "SUB R2,A", "BS(C) R2,6", "CLR R2", ....). In this case, the execution takes two instruction cycles.

If for some reasons, the specification of the instruction cycle is not suitable for certain applications, try modifying the instruction as follows:

- (A) Change one instruction cycle to consist of 4 oscillator periods.

- (B) "JMP", "CALL", "RET", "RETL", "RETI", or the conditional skip ("JBS", "JBC", "JZ", "JZA", "DJZ", "DJZA") commands which were tested to be true, are executed within two instruction cycles. The instructions that are written to the program counter also take two instruction cycles.

Case (A) is selected by the CODE Option bit, called CLK. One instruction cycle consists of two oscillator clocks if CLK is low, and four oscillator clocks if CLK is high.

Note that once the 4 oscillator periods within one instruction cycle is selected as in Case (A), the internal clock source to TCC should be CLK=Fosc/4, instead of Fosc/ 2 as indicated in Fig. 5.

In addition, the instruction set has the following features:

(1) Every bit of any register can be set, cleared, or tested directly.

(2) The I/O register can be regarded as general register. That is, the same instruction can operate on I/O register.

The symbol "R" represents a register designator that specifies which one of the registers (including operational registers and general purpose registers) is to be utilized by the instruction. "b" represents a bit field designator that selects the value for the bit which is located in the register "R", and affects operation. "k" represents an 8 or 10-bit constant or literal value.

| INSTRUCTION BINARY | HEX  | MNEMONIC | OPERATION                                                              | STATUS AFFECTED      |

|--------------------|------|----------|------------------------------------------------------------------------|----------------------|

| 0 0000 0000 0000   | 0000 | NOP      | No Operation                                                           | None                 |

| 0 0000 0000 0001   | 0001 | DAA      | Decimal Adjust A                                                       | С                    |

| 0 0000 0000 0010   | 0002 | CONTW    | $A \rightarrow CONT$                                                   | None                 |

| 0 0000 0000 0011   | 0003 | SLEP     | 0 → WDT, Stop oscillator                                               | T,P                  |

| 0 0000 0000 0100   | 0004 | WDTC     | $0 \rightarrow WDT$                                                    | T,P                  |

| 0 0000 0000 rrrr   | 000r | IOW R    | $A \rightarrow IOCR$                                                   | None <note1></note1> |

| 0 0000 0001 0000   | 0010 | ENI      | Enable Interrupt                                                       | None                 |

| 0 0000 0001 0001   | 0011 | DISI     | Disable Interrupt                                                      | None                 |

| 0 0000 0001 0010   | 0012 | RET      | [Top of Stack] → PC                                                    | None                 |

| 0 0000 0001 0011   | 0013 | RETI     | [Top of Stack] → PC, Enable<br>Interrupt                               | None                 |

| 0 0000 0001 0100   | 0014 | CONTR    | $CONT \rightarrow A$                                                   | None                 |

| 0 0000 0001 rrrr   | 001r | IOR R    | $IOCR \rightarrow A$                                                   | None <note1></note1> |

| 0 0000 01rr rrrr   | 00rr | MOV R,A  | $A \rightarrow R$                                                      | None                 |

| 0 0000 1000 0000   | 0800 | CLRA     | $0 \rightarrow A$                                                      | Z                    |

| 0 0000 11rr rrrr   | 00rr | CLR R    | $0 \rightarrow R$                                                      | Z                    |

| 0 0001 00rr rrrr   | 01rr | SUB A,R  | $R-A \rightarrow A$                                                    | Z,C,DC               |

| 0 0001 01rr rrrr   | 01rr | SUB R,A  | $R-A \rightarrow R$                                                    | Z,C,DC               |

| 0 0001 10rr rrrr   | 01rr | DECA R   | $R-1 \rightarrow A$                                                    | Z                    |

| 0 0001 11rr rrrr   | 01rr | DEC R    | $R-1 \rightarrow R$                                                    | Z                    |

| 0 0010 00rr rrrr   | 02rr | OR A,R   | $A \lor R \to A$                                                       | Z                    |

| 0 0010 01rr rrrr   | 02rr | OR R,A   | $A \lor R \to R$                                                       | Z                    |

| 0 0010 10rr rrrr   | 02rr | AND A,R  | $A \& R \rightarrow A$                                                 | Z                    |

| 0 0010 11rr rrrr   | 02rr | AND R,A  | $A \& R \rightarrow R$                                                 | Z                    |

| 0 0011 00rr rrrr   | 03rr | XOR A,R  | $A \oplus R \rightarrow A$                                             | Z                    |

| 0 0011 01rr rrrr   | 03rr | XOR R,A  | $A \oplus R \rightarrow R$                                             | Z                    |

| 0 0011 10rr rrrr   | 03rr | ADD A,R  | $A + R \rightarrow A$                                                  | Z,C,DC               |

| 0 0011 11rr rrrr   | 03rr | ADD R,A  | $A + R \rightarrow R$                                                  | Z,C,DC               |

| 0 0100 00rr rrrr   | 04rr | MOV A,R  | $R \rightarrow A$                                                      | Z                    |

| 0 0100 01rr rrrr   | 04rr | MOV R,R  | $R \rightarrow R$                                                      | Z                    |

| 0 0100 10rr rrrr   | 04rr | COMA R   | $/R \rightarrow A$                                                     | Z                    |