TrilithIC™ BTS 7811K

#### **Data Sheet**

#### 1 Overview

#### 1.1 Features

- Quad D-MOS switch

- Free configurable as bridge or quad-switch

- Optimized for DC motor management applications

- Low  $R_{\rm DS\,ON}$ : 26 m $\Omega$  high-side switch, 14 m $\Omega$  low-side switch (typical values @ 25 °C)

- Maximum peak current: typ. 42 A @ 25 °C

- Very low quiescent current: typ. 4 μA @ 25 °C

- Small outline, thermal optimized PowerPak

- Load and GND-short-circuit-protection

- Operates up to 40 V

- Status flag for over temperature

- · Open load detection in Off-mode

- Overtemperature shut down with hysteresis

- Internal clamp diodes

- PWM capability up to 25kHz

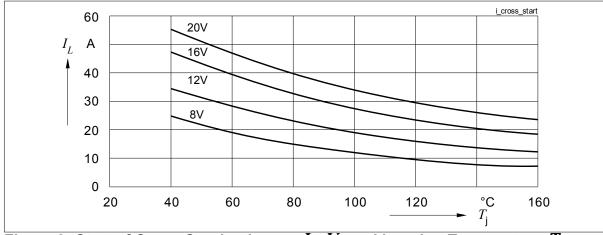

- Cross current free operation up to 13A load current (typ. value @ 12V/150°C)

- Under-voltage detection with hysteresis

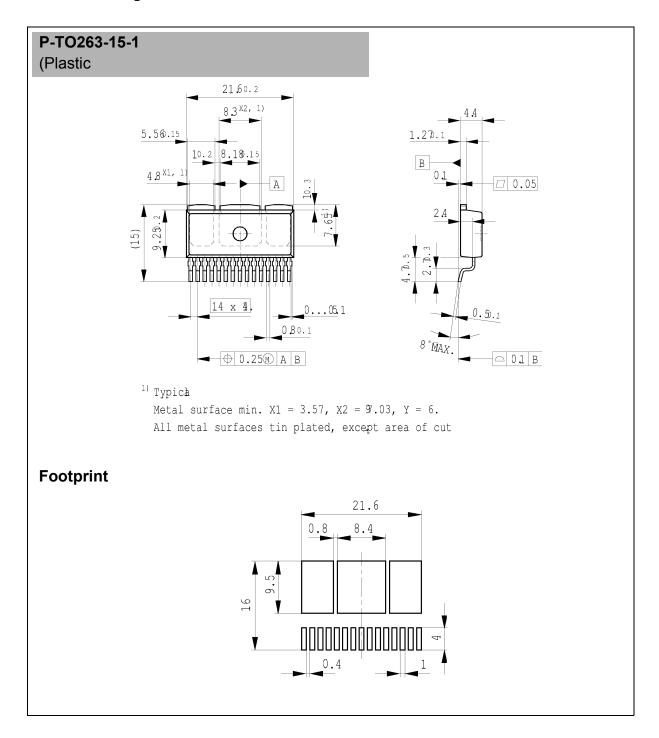

| Туре      | Package      |

|-----------|--------------|

| BTS 7811K | P-TO263-15-1 |

### 1.2 Description

The BTS 7811K is part of the TrilithIC<sup>TM</sup> family containing three dies in one package: One double high-side switch and two low-side switches. The drains of these three vertical DMOS chips are mounted on separated leadframes. The sources are connected to individual pins, so the BTS 7811K can be used in H-bridge- as well as in any other configuration. The double high-side is manufactured in SMART SIPMOS® technology which combines low  $R_{\rm DS \,ON}$  vertical DMOS power stages with CMOS control circuit. The protected high-side switch contains the control and diagnosis circuit. To achieve low  $R_{\rm DS \,ON}$  and fast switching performance, the low-side switches are manufactured in S-FET 2 logic level technology.

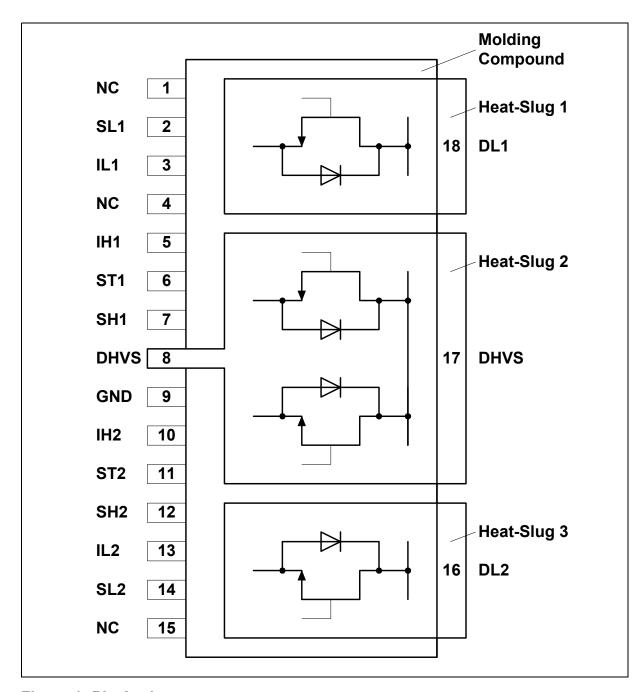

# 1.3 Pin Configuration

(top view)

Figure 1: Pin Assignment

### 1.4 Pin Definitions and Functions

| Pin No. | Symbol | Function                                                         |

|---------|--------|------------------------------------------------------------------|

| 1       | NC     | Not connected                                                    |

| 2       | SL1    | Source of low-side switch 1                                      |

| 3       | IL1    | Analog input of low-side switch 1                                |

| 4       | NC     | Not connected                                                    |

| 5       | IH1    | Digital input of high-side switch 1                              |

| 6       | ST1    | Status of high-side switch 1; open Drain output                  |

| 7       | SH1    | Source of high-side switch 1                                     |

| 8       | DHVS   | Drain of high-side switches and power supply voltage             |

| 9       | GND    | Ground of high-side switches                                     |

| 10      | IH2    | Digital input of high-side switch 2                              |

| 11      | ST2    | Status of high-side switch 2; open Drain output                  |

| 12      | SH2    | Source of high-side switch 2                                     |

| 13      | IL2    | Analog input of low-side switch 2                                |

| 14      | SL2    | Source of low-side switch 2                                      |

| 15      | NC     | Not connected                                                    |

| 16      | DL2    | Drain of low-side switch 2<br>Heat-Slug 3                        |

| 17      | DHVS   | Drain of high-side switches and power supply voltage Heat-Slug 2 |

| 18      | DL1    | Drain of low-side switch 1<br>Heat-Slug 1                        |

Pins written in **bold type** need power wiring.

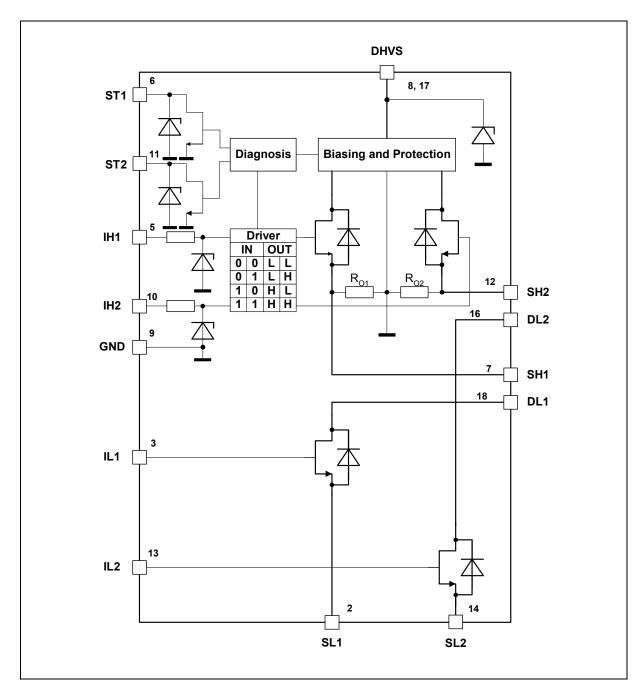

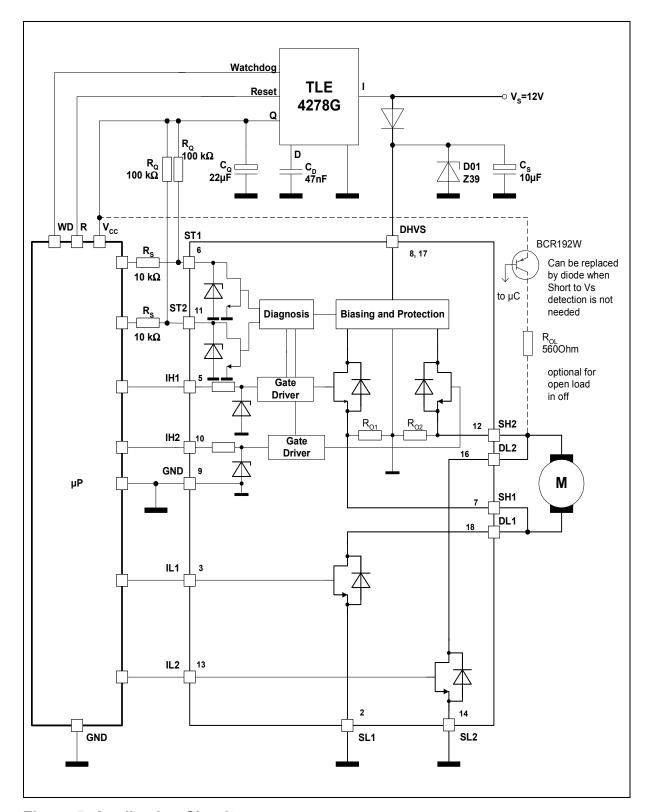

## 1.5 Functional Block Diagram

Figure 2: Block Diagram

#### 1.6 Circuit Description

#### **Input Circuit**

The control inputs IH1,2 consist of TTL/CMOS compatible Schmitt-Triggers with hysteresis. Buffer amplifiers are driven by these stages and convert the logic signal into the necessary form for driving the power output stages. The inputs are protected by ESD clamp-diodes. The inputs IL1 and IL2 are connected to the gates of the standard N-channel vertical power-MOS-FETs.

#### **Output Stages**

The output stages consist of a low  $R_{\rm DS\,ON}$  Power-MOS H-bridge. In H-bridge configuration, the D-MOS body diodes can be used for freewheeling when commutating inductive loads. If the high-side switches are used as single switches, positive and negative voltage spikes which occur when driving inductive loads are limited by integrated power clamp diodes.

#### **Short Circuit Protection**

The outputs are protected against

- output short circuit to ground

- overload (load short circuit).

An internal OP-amp controls the Drain-Source-voltage by comparing the DS-voltagedrop with an internal reference voltage. Above this trippoint the OP-Amp reduces the output current depending on the junction temperature and the drop voltage.

#### **Overtemperature Protection**

The high-side switches incorporate an overtemperature protection circuit with hysteresis which switches off the output transistors and sets the status output to low.

#### **Undervoltage-Lockout (UVLO)**

When  $V_{\rm S}$  reaches the switch-on voltage  $V_{\rm UVON}$  the IC becomes active with a hysteresis. The high-side output transistors are switched off if the supply voltage  $V_{\rm S}$  drops below the switch off value  $V_{\rm UVOFE}$ .

#### **Open Load Detection**

The open load detection of the BTS 7811K works in OFF condition and is based on a voltage measurement at the source of the high side switch. In order to use the open load detection a pull up resistor to 5V has to be connected to source of one of the high side switches. Because in ON condition this pull up resistor would connect the bridge output to the  $\mu$ C supply it needs to be disconnected by a transistor when the high side switch is

Data Sheet 5 Rev. 2.0, 2006-07-18

on. In the data sheet application example (Figure 5) the open load detection would be used the following way:

- Set IH1 = IH2 = LOW (both high side switches off)

- Set IL2 = LOW, IL1 = HIGH (only low side switch 1 is on)

- Connect Rol (open load pull up) to 5V via transistor

If the load is connected properly it will pull down the voltage at SH2 to a value close to 0V. If the load is disconnected the resistor will pull the voltage at SH2 to value close to 5V. If the voltage at SH2 is higher than the open load detection voltage (VOUT(OL)) then ST2 will be pulled down.

#### **Status Flag**

The two status flag outputs are an open drain output with Zener-diode which require a pull-up resistor, c.f. the application circuit on page 16. ST1 and ST2 provide separate diagnosis for each high-side switch. Various errors as listed in the table "Diagnosis" are detected by switching the open drain output ST1/2 to low. Forward current in the integrated body diode of the highside switch may cause undefined voltage levels at the corresponding status output. The open load detection can be used to detect a short to Vs as long as both lowside switches are off and  $R_{OL}$  is disconnected from 5V by BCR192W.

### 2 Truthtable and Diagnosis (valid only for the High-Side-Switches)

| Flag                                  | IH1 | IH2 | SH1 | SH2  | ST1 | ST2 | Remarks              |

|---------------------------------------|-----|-----|-----|------|-----|-----|----------------------|

|                                       | Inp | uts | Out | puts |     |     |                      |

|                                       | 0   | 0   | L   | L    | 1   | 1   | stand-by mode        |

| Normal operation;                     | 0   | 1   | L   | Н    | 1   | 1   | switch2 active       |

| identical with functional truth table | 1   | 0   | Н   | L    | 1   | 1   | switch1 active       |

|                                       | 1   | 1   | Н   | Н    | 1   | 1   | both switches active |

| Open load at high-side switch 1       | 0   | Х   | Z   | Х    | 0   | 1   | detected             |

| , ,                                   | 1   | X   | Н   | X    | 1   | 1   |                      |

| Open load at high-side switch 2       | Χ   | 0   | X   | Z    | 1   | 0   | detected             |

|                                       | Χ   | 1   | X   | Н    | 1   | 1   |                      |

| Overtemperature high-side switch1     | 0   | Х   | L   | Х    | 1   | 1   |                      |

| · · · · · ·                           | 1   | X   | L   | X    | 0   | 1   | detected             |

| Overtemperature high-side switch2     | Χ   | 0   | Х   | L    | 1   | 1   |                      |

|                                       | Χ   | 1   | X   | L    | 1   | 0   | detected             |

| Overtemperature both high-side        | 0   | 0   | L   | L    | 1   | 1   |                      |

| switches                              | 0   | 1   | L   | L    | 1   | 0   | detected             |

|                                       | 1   | 0   | L   | L    | 0   | 1   | detected             |

|                                       | 1   | 1   | L   | L    | 0   | 0   | detected             |

| Undervoltage                          | Х   | Х   | L   | L    | 1   | 1   | not detected         |

Note: \* multiple simultaneous errors are not shown in this table

Inputs: Outputs: Status:

0 = Logic LOW Z = Output in tristate condition <math>1 = No error

1 = Logic HIGH L = Output in sink condition 0 = Error

X = don't care H = Output in source condition

X = Voltage level undefined

#### 3 Electrical Characteristics

## 3.1 Absolute Maximum Ratings

$-40 \, ^{\circ}\text{C} < T_{j} < 150 \, ^{\circ}\text{C}$

| Parameter | Symbol | Limit Values |      | Unit | Remarks |

|-----------|--------|--------------|------|------|---------|

|           |        | min.         | max. |      |         |

|           |        |              |      |      |         |

### High-Side-Switches (Pins DHVS, IH1,2 and SH1,2)

| Supply voltage                                   | $V_{S}$          | - 0.3       | 42 | V  | _                       |

|--------------------------------------------------|------------------|-------------|----|----|-------------------------|

| Supply voltage for full short circuit protection | $V_{S(SCP)}$     |             | 28 | V  | _                       |

| HS-drain current                                 | $I_{\mathbb{S}}$ | <b>– 14</b> | *  | Α  | $T_{\rm C}$ = 125°C; DC |

| HS-input current                                 | $I_{IH}$         | <b>-</b> 5  | 5  | mA | Pin IH1 and IH2         |

| HS-input voltage                                 | $V_{IH}$         | <b>–</b> 10 | 16 | V  | Pin IH1 and IH2         |

Note: \* internally limited

## **Status Output ST (Pins ST1 and ST2)**

| Status pull up voltage | $V_{ST}$ | - 0.3      | 5.4 | V  | _              |

|------------------------|----------|------------|-----|----|----------------|

| Status Output current  | $I_{ST}$ | <b>-</b> 5 | 5   | mA | Pin ST1 or ST2 |

## Low-Side-Switches (Pins DL1,2, IL1,2 and SL1,2)

| Drain- source break down voltage | $V_{ m DSL}$ | 55          | _  | V | $V_{\rm IL}$ = 0 V, $I_{\rm D}$ $\leq$ 1 mA, $T_{\rm j}$ = 25°C |

|----------------------------------|--------------|-------------|----|---|-----------------------------------------------------------------|

| LS-drain current                 | $I_{DL}$     | -21         | 26 | Α | $T_{\rm C}$ = 125°C; DC                                         |

| LS-drain current                 | $I_{DL}$     | _           | 42 | Α | <i>t</i> <sub>p</sub> < 100 ms; v < 0.1                         |

| $T_{\rm C}$ = 85°C               |              | _           | 67 | Α | $t_{\rm p}$ < 1 ms; v < 0.1                                     |

| LS-input voltage                 | $V_{IL}$     | <b>– 20</b> | 20 | V | Pin IL1 and IL2                                                 |

## **Temperatures**

| Junction temperature | $T_{j}$   | <b>- 40</b> | 150 | °C | _ |

|----------------------|-----------|-------------|-----|----|---|

| Storage temperature  | $T_{stg}$ | <b>–</b> 55 | 150 | °C | _ |

### 3.1 Absolute Maximum Ratings (cont'd)

$-40 \, ^{\circ}\text{C} < T_{i} < 150 \, ^{\circ}\text{C}$

| Parameter | Symbol | Limit Values |      | Unit | Remarks |

|-----------|--------|--------------|------|------|---------|

|           |        | min.         | max. |      |         |

#### Thermal Resistances (one HS-LS-Path active)

| LS-junction case                                                                          | $R_{thjCL}$   | _ | 1.05 | K/W |                                                                      |

|-------------------------------------------------------------------------------------------|---------------|---|------|-----|----------------------------------------------------------------------|

| HS-junction case                                                                          | $R_{thjC\;H}$ | _ | 1.45 | K/W |                                                                      |

| Junction ambient $R_{\text{thja}} = T_{j(\text{HS})}/(P_{(\text{HS})} + P_{(\text{LS})})$ | $R_{thja}$    | _ | 35   | K/W | device soldered to reference PCB with 6 cm <sup>2</sup> cooling area |

**ESD Protection** (Human Body Model acc. MIL STD 883D, method 3015.7 and EOS/ ESD assn. standard S5.1 - 1993)

| Input LS-Switch         | $V_{ESD}$ | 0.5 | kV |                                    |

|-------------------------|-----------|-----|----|------------------------------------|

| Input HS-Switch         | $V_{ESD}$ | 1   | kV |                                    |

| Status HS-Switch        | $V_{ESD}$ | 2   | kV |                                    |

| Output LS and HS-Switch | $V_{ESD}$ | 4   | kV | all other pins connected to Ground |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

## 3.2 Operating Range

$$-40 \, ^{\circ}\text{C} < T_{j} < 150 \, ^{\circ}\text{C}$$

| Parameter                        | Symbol                | Limit Values |      | Unit | Remarks                                       |

|----------------------------------|-----------------------|--------------|------|------|-----------------------------------------------|

|                                  |                       | min.         | max. |      |                                               |

| Supply voltage                   | $V_{S}$               | $V_{UVOFF}$  | 42   | V    | After $V_{\rm S}$ rising above $V_{\rm UVON}$ |

| Supply voltage for PWM operation | $V_{\mathrm{S(PWM)}}$ | 8            | 18   | V    | _                                             |

| Input voltages HS                | $V_{IH}$              | - 0.3        | 15   | V    | _                                             |

| Input voltages LS                | $V_{IL}$              | - 0.3        | 20   | V    | _                                             |

| Status output current            | $I_{ST}$              | 0            | 2    | mA   | _                                             |

| Junction temperature             | $T_{jHS}$             | <b>- 40</b>  | 150  | °C   | _                                             |

Note: In the operating range the functions given in the circuit description are fulfilled.

### 3.3 Electrical Characteristics

$I_{\rm SH1}$  =  $I_{\rm SH2}$  =  $I_{\rm SL1}$  =  $I_{\rm SL2}$  = 0 A; - 40 °C <  $T_{\rm j}$  < 150 °C; 8 V <  $V_{\rm S}$  < 18 V unless otherwise specified

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |  |

|-----------|--------|--------------|------|------|----------------|--|

|           |        | min.         | typ. | max. |                |  |

### **Current Consumption HS-switch**

|                                                              | 1                                                     |   | 1   |    | 1  |                                                                                                        |

|--------------------------------------------------------------|-------------------------------------------------------|---|-----|----|----|--------------------------------------------------------------------------------------------------------|

| Quiescent current                                            | $I_{SQ}$                                              | _ | 4   | 9  | μΑ | IH1 = IH2 = 0 V                                                                                        |

|                                                              | J Q                                                   |   |     |    | •  | <i>T</i> <sub>j</sub> = 85 °C                                                                          |

|                                                              |                                                       | _ | _   | 20 | μΑ | IH1 = IH2 = 0 V                                                                                        |

| Supply current                                               | $I_{\mathtt{S}}$                                      | _ | 4   | 8  | mA | IH1 or IH2 = 5 V                                                                                       |

|                                                              |                                                       | _ | 8   | 16 | mA | IH1 and IH2 = 5 V                                                                                      |

| Leakage current of highside switch                           | $I_{SHLK}$                                            | _ | _   | 7  | μΑ | $V_{\rm IH} = V_{\rm SH} = 0 \text{ V}$<br>$T_{\rm j} = 85 ^{\circ}\text{C}, \ V\text{s} = 12\text{V}$ |

| Leakage current through logic GND in free wheeling condition | $I_{\text{LKCL}}$ = $I_{\text{FH}}$ + $I_{\text{SH}}$ | _ | 2.2 | 10 | mA | $I_{\text{FH}}$ =5 A $V_{\text{S}}$ = 12V                                                              |

## **Current Consumption LS-switch**

| Input current                     | $I_{IL}$     | _ | 10 | 100 | nA | V <sub>IL</sub> = 20 V                                            |

|-----------------------------------|--------------|---|----|-----|----|-------------------------------------------------------------------|

|                                   |              |   |    |     |    | $V_{\rm DSL}$ = 0 V                                               |

| Leakage current of lowside switch | $I_{DL\;LK}$ | _ | _  | 12  | μΑ | $V_{\rm IL}$ = 0 V<br>$V_{\rm DSL}$ = 40 V<br>$T_{\rm j}$ = 85 °C |

## Under Voltage Lockout (UVLO) HS-switch

| Switch-ON voltage        | $V_{UVON}$     | _   | _ | 5   | V | $V_{\rm S}$ increasing         |

|--------------------------|----------------|-----|---|-----|---|--------------------------------|

| Switch-OFF voltage       | $V_{UVOFF}$    | 1.8 | _ | 4.5 | V | $V_{\rm S}$ decreasing         |

| Switch ON/OFF hysteresis | $V_{\sf UVHY}$ | _   | 1 | _   | V | $V_{\rm UVON} - V_{\rm UVOFF}$ |

Data Sheet 10 Rev. 2.0, 2006-07-18

$I_{\rm SH1}$  =  $I_{\rm SH2}$  =  $I_{\rm SL2}$  = 0 A; - 40 °C <  $T_{\rm j}$  < 150 °C; 8 V <  $V_{\rm S}$  < 18 V unless otherwise specified

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |  |

|-----------|--------|--------------|------|------|----------------|--|

|           |        | min.         | typ. | max. |                |  |

### **Output Stages**

| Inverse diode of high-<br>side switch; Forward-<br>voltage | $V_{FH}$              | _ | 0.8 | 1.2 | V  | I <sub>FH</sub> = 5 A                                                                                  |

|------------------------------------------------------------|-----------------------|---|-----|-----|----|--------------------------------------------------------------------------------------------------------|

| Inverse diode of lowside switch; Forward-voltage           | $V_{\sf FL}$          | _ | 0.8 | 1.2 | V  | I <sub>FL</sub> = 5 A                                                                                  |

| Static drain-source on-resistance of highside switch       | $R_{	extsf{DS ON H}}$ | _ | 26  | 35  | mΩ | $I_{\text{SH}}$ = 5 A<br>$T_{\text{j}}$ = 25 °C<br>Vs = 12V                                            |

| Static drain-source on-resistance of lowside switch        | $R_{DSONL}$           | _ | 14  | 17  | mΩ | $I_{SL}$ = 5 A;<br>$V_{IL}$ = 5 V<br>$T_{j}$ = 25 °C                                                   |

| Static path on-resistance                                  | $R_{DSON}$            | _ | _   | 100 | mΩ | $R_{\text{DS ON H}} + R_{\text{DS ON L}}$<br>$I_{\text{SH}} = 5 \text{ A}; V_{\text{S}} = 12 \text{V}$ |

| Maximum load current for                                   | $I_{Lmax\;ccf}$       | 5 | 8   | _   | Α  | $V_{\rm S} > 8V, T_{\rm j} = 150  ^{\circ}{\rm C}$                                                     |

| cross current free                                         |                       | _ | 10  | _   | Α  | $V$ s = 10V, $T_{\rm j}$ = 150 °C                                                                      |

| operation $V_{\rm IL}$ = 7V; $R_{\rm Gate}$ = 50 $\Omega$  |                       | _ | 13  | _   | А  | $V$ s = 12V, $T_{\rm j}$ = 150 °C                                                                      |

Note: The device is regarded as cross current free if the reverse flowing charge through the high side switch is less than  $1\mu$ C.

Figure 3: Start of Cross Conduction vs.  $I_{\mathsf{L}},\,V_{\mathsf{S}}$  and junction Temperature  $T_{\mathsf{j}}$

Data Sheet 11 Rev. 2.0, 2006-07-18

$I_{\rm SH1}$  =  $I_{\rm SH2}$  =  $I_{\rm SL1}$  =  $I_{\rm SL2}$  = 0 A; - 40 °C <  $T_{\rm j}$  < 150 °C; 8 V <  $V_{\rm S}$  < 18 V unless otherwise specified

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |  |

|-----------|--------|--------------|------|------|----------------|--|

|           |        | min.         | typ. | max. |                |  |

#### **Short Circuit of Highside Switch to GND**

| Initial peak SC current                                             | $I_{SCPH}$ | 35 | 48 | 65 | А | $T_{\rm j}$ = $-40~{\rm ^{\circ}C}$ |

|---------------------------------------------------------------------|------------|----|----|----|---|-------------------------------------|

| $t_{\text{del}} = 150 \mu \text{s}; \ V_{\text{S}} = 12 \text{ V};$ |            | _  | 42 | _  | Α | T <sub>j</sub> = + 25 °C            |

| $V_{\rm DSH}$ = 12V                                                 |            | 25 | 32 | 42 | Α | T <sub>j</sub> = + 150 °C           |

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions. Protection functions are not designed for continuous or repetitive operation.

Peak short circuit current is significantly lower at  $V_S > 18V$ .

## Short Circuit of Highside Switch to $V_{\mathtt{S}}$

| Output pull-down-resistor | $R_{\rm O}$ | 7 | 14 | 42 | kΩ | $V_{\mathrm{DSL}}$ = 3 V |

|---------------------------|-------------|---|----|----|----|--------------------------|

|                           | •           |   |    |    |    | 202                      |

#### **Thermal Shutdown**

| Thermal shutdown junction temperature  | $T_{\rm jSD}$ | 155 | 180 | 190 | °C | _                                      |

|----------------------------------------|---------------|-----|-----|-----|----|----------------------------------------|

| Thermal switch-on junction temperature | $T_{\rm jSO}$ | 150 | 170 | 180 | °C | _                                      |

| Temperature hysteresis                 | $\Delta T$    | _   | 10  | _   | °C | $\Delta T = T_{\rm jSD} - T_{\rm jSO}$ |

## Status Flag Output ST of Highside Switch

| Low output voltage                                                    | $V_{STL}$        | _   | 0.2 | 0.6 | V  | $I_{\rm ST}$ = 1.6 mA |

|-----------------------------------------------------------------------|------------------|-----|-----|-----|----|-----------------------|

| Leakage current                                                       | $I_{ m STLK}$    | _   | _   | 5   | μΑ | V <sub>ST</sub> = 5 V |

| Zener-limit-voltage                                                   | $V_{STZ}$        | 5.4 |     | _   | V  | $I_{\rm ST}$ = 1.6 mA |

| Status change after positive input slope with open load 1)            | $t_{d(SToffo+)}$ | _   | _   | 20  | μs |                       |

| Status change after negative input slope with open load <sup>1)</sup> | $t_{d(SToffo-)}$ | _   | _   | 700 | μs |                       |

<sup>1)</sup>Defined by design. Not subject to production test.

Data Sheet 12 Rev. 2.0, 2006-07-18

$I_{\rm SH1}$  =  $I_{\rm SH2}$  =  $I_{\rm SL1}$  =  $I_{\rm SL2}$  = 0 A; - 40 °C <  $T_{\rm j}$  < 150 °C; 8 V <  $V_{\rm S}$  < 18 V unless otherwise specified

| Parameter                                                        | Symbol               | Limit Values |      |      | Unit | Test Condition               |

|------------------------------------------------------------------|----------------------|--------------|------|------|------|------------------------------|

|                                                                  |                      | min.         | typ. | max. |      |                              |

| Status change after positive input slope with overtemperature 1) | $t_{d(STofft+)}$     | _            | 1.6  | 10   | μs   | $R_{\rm ST}$ = 47 k $\Omega$ |

| Status change after negative input slope with overtemperature 1) | $t_{\sf d(STofft-)}$ | _            | 14   | 100  | μs   | $R_{\rm ST}$ = 47 k $\Omega$ |

## **Open Load Detection in Off Condition**

| Open Load Detection | $V_{OUT(OL)}$ | 2 | 3 | 4 | V | V <sub>S</sub> = 12 V |

|---------------------|---------------|---|---|---|---|-----------------------|

| Voltage             | , ,           |   |   |   |   |                       |

### **Switching Times of High Side Switch**

| Turn-On-Time to 90% $V_{\rm SH}$     | $t_{ON}$          | _ | 100 | 220 | μs   | $R_{Load}$ = 12 $\Omega$<br>$V_{S}$ = 12 $V$ |

|--------------------------------------|-------------------|---|-----|-----|------|----------------------------------------------|

| Turn-Off-time to 10% $V_{\rm SH}$    | $t_{OFF}$         | _ | 120 | 250 | μs   |                                              |

| Slew Rate On 10 to 30% $V_{\rm SH}$  | $dV/dt_{\sf ON}$  | _ | 0.5 | 1.1 | V/µs |                                              |

| Slew Rate Off 70 to 40% $V_{\rm SH}$ | $-dV/$ $dt_{OFF}$ | _ | 0.7 | 1.3 | V/µs |                                              |

## **Switching Times of Low Side Switch**

| Turn-ON Delay Time <sup>1)</sup>    | $t_{\sf d(on)}$  | _ | 20 | _ | ns | resistive load                                  |

|-------------------------------------|------------------|---|----|---|----|-------------------------------------------------|

| Rise Time <sup>1)</sup>             | $t_{r}$          | _ | 85 | _ | ns | $I_{\rm SL}$ = 10 A; $V_{\rm DSL}$ = 12 V       |

| Switch-Off Delay Time <sup>1)</sup> | $t_{\sf d(off)}$ | _ | 60 | _ | ns | $V_{\rm IL}$ = 5V; $R_{\rm Gate}$ = 16 $\Omega$ |

| Fall Time <sup>1)</sup>             | $t_{f}$          | _ | 80 | _ | ns |                                                 |

<sup>1)</sup>Defined by design. Not subject to production test.

$I_{\rm SH1}$  =  $I_{\rm SH2}$  =  $I_{\rm SL2}$  = 0 A; - 40 °C <  $T_{\rm j}$  < 150 °C; 8 V <  $V_{\rm S}$  < 18 V unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

#### **Gate Charge Characteristics**

| Input to source charge <sup>1)</sup> | $Q_{IS}$         | _ | 4.5 | _  | nC | $I_{\rm SL}$ = 10 A; $V_{\rm S}$ = 12 V                         |

|--------------------------------------|------------------|---|-----|----|----|-----------------------------------------------------------------|

| Input to drain charge <sup>1)</sup>  | $Q_{ID}$         | _ | 12  | _  | nC | $I_{\rm SL}$ = 10 A; $V_{\rm S}$ = 12 V                         |

| Input charge total <sup>1)</sup>     | $Q_{I}$          | _ | 30  | 60 | nC | $I_{\rm SL}$ = 10 A; $V_{\rm S}$ = 12 V $V_{\rm IL}$ = 0 to 5 V |

| Input plateau voltage <sup>1)</sup>  | $V_{ m plateau}$ | _ | 2.6 | _  | V  | $I_{\rm SL}$ = 10 A; $V_{\rm S}$ = 12 V                         |

### Control Inputs of High Side Switches IH1, IH2

| -                       |                |     |     |     |    |                          |

|-------------------------|----------------|-----|-----|-----|----|--------------------------|

| H-input voltage         | $V_{IH\;High}$ | _   | _   | 3.0 | V  | _                        |

| L-input voltage         | $V_{IH\ Low}$  | 1   | _   | _   | V  | _                        |

| Input voltage hysterese | $V_{IHHY}$     | _   | 0.5 | _   | V  | _                        |

| H-input current         | $I_{IH\;High}$ | 5   | 30  | 65  | μΑ | V <sub>IH</sub> = 5 V    |

| L-input current         | $I_{IH\ Low}$  | 5   | 14  | 25  | μΑ | V <sub>IH</sub> = 0.4 V  |

| Input series resistance | $R_{I}$        | 2.7 | 4   | 6   | kΩ | _                        |

| Zener limit voltage     | $V_{IHZ}$      | 5.4 | _   | _   | V  | I <sub>IH</sub> = 1.6 mA |

## **Control Inputs IL1, IL2**

| Gate-threshold-voltage | $V_{ILth}$ | _   | 1.9 | 3.0 | V | T <sub>j</sub> = -40 °C   |

|------------------------|------------|-----|-----|-----|---|---------------------------|

| $I_{\rm DL}$ = 1 mA    |            | _   | 1.7 | -   |   | T <sub>j</sub> = + 25 °C  |

|                        |            | 8.0 | 1.1 | -   |   | T <sub>j</sub> = + 150 °C |

<sup>1)</sup> Defined by design. Not subject to production test.

Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A$  = 25 °C and  $V_S$  = 12 V.

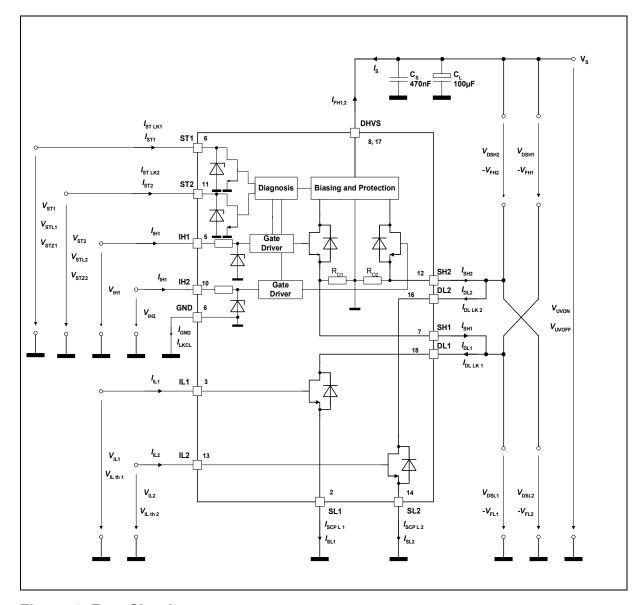

Figure 4: Test Circuit

| HS-Source-Current    | _          | Named during Leakage-<br>Cond. |

|----------------------|------------|--------------------------------|

| $I_{\mathrm{SH1,2}}$ | $I_{SCPH}$ | $I_{DLLK}$                     |

Figure 5: Application Circuit

### 4 Package Outlines

#### **Sorts of Packing**

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/packages...

SMD = Surface Mounted Device

Dimensions in mm

Edition June 2006

Published by Infineon Technologies AG, Am Campeon 1-12, 87559 Neubiberg, Germany

© Infineon Technologies AG 2006. All Rights Reserved.

#### Attention please!

The information given in this Data Sheet shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office. Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.