March 2012

# FR011L5J (11mΩ, -30V) Low-Side Reverse Bias Protector

#### **Features**

- Up to -30V Reverse-Bias Protection

- Nano Seconds of Reverse-Bias Blocking Response Time

- +29V 24-Hour "Withstand" Rating

- 11mΩ Typical Series Resistance at 5V

- MicroFET™ 2x2mm Package Size

- RoHs Compliant

- USB Tested and Compatible

# **Applications**

- USB 1.0, 2.0 and 3.0 Devices

- USB Charging

- Mobile Devices

- Mobile Medical

- POS Systems

- Toys

- Any DC Barrel Jack Powered Device

- Any DC Devices subject to Negative Hot Plug or Inductive Transients

- Automotive Peripherals

MicroFET2x2 mm

# Description

Reverse bias is an increasingly common fault event that may be generated by user error, improperly installed batteries, automotive environments, erroneous connections to third-party chargers, negative "hot plug" transients, inductive transients, and readily available negatively biased rouge USB chargers.

Fairchild circuit protection is proud to offer a new type of reverse bias protection devices. The FR devices are low resistance, series switches that, in the event of a reverse bias condition, shut off power and block the negative voltage to help protect downstream circuits.

The FR devices are optimized for the application to offer best in class reverse bias protection and voltage capabilities while minimizing size, series voltage drop, and normal operating power consumption.

In the event of a reverse bias application, FR011L5J devices effectively provide a full voltage block and can easily protect -0.3V rated silicon.

From a power perspective, in normal bias, an  $11m\Omega$  FR device in a 1.5A application will generate only 17mV of voltage drop or 25mW of power loss. In reverse bias, FR devices dissipate less then  $20\mu W$  in a 16V reverse bias event. This type of performance is not possible with a diode solution.

Benefits extend beyond the device. Due to low power dissipation, not only is the device small, but heat sinking requirements and cost can be minimized as well.

# **Ordering Information**

| Part Number | Top Mark | Package                                                                                | Packing Method                                 |

|-------------|----------|----------------------------------------------------------------------------------------|------------------------------------------------|

| FR011L5J    | 11L      | 6-Lead, Molded Leadless Package (MLP), Dual,<br>Non-JEDEC, 2mm Square, Single-Tied DAP | 3000 on Tape & Reel;<br>7-inch Reel, 12mm Tape |

# **Diagrams**

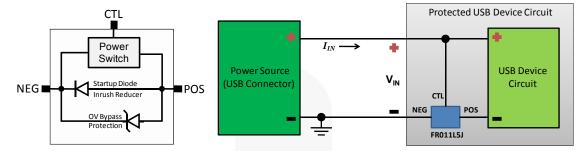

Figure 1. Block Diagram

Figure 2. Typical Schematic

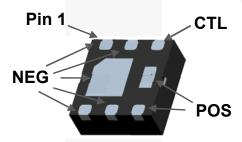

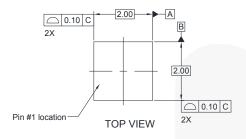

# **Pin Configuration**

Figure 3. Pin Assignments

# **Pin Definitions**

| Name | Pin                                                                                                    | Description                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| POS  | 4                                                                                                      | The ground of the load circuit being protected. Current flows into this pin during normal operation.                                                    |

| CTL  | 3                                                                                                      | The control pin of the device. A positive voltage to the NEG pin turns the switch on and a negative voltage turns the switch to a high-impedance state. |

| NEG  | NEG 1, 2, 5, 6 The ground of the input power source. Current flows out of this pin during normal opera |                                                                                                                                                         |

# **Absolute Maximum Ratings**

Values are at T<sub>A</sub>=25°C unless otherwise noted.

| Symbol                   |                                                                                                                                      | Values                                   | Unit |     |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|-----|

| V+ MAX_OP                | Steady-State Normal Operating Voltage between CTL and NEG Pins $(V_{IN} = V + {}_{MAX\_OP}, I_{IN} = 1.5A, Switch On)$               |                                          | +20  |     |

| V+ <sub>24</sub>         | 24-Hour Normal Operating Voltage Withstand Capability between CTL and NEG Pins ( $V_{IN}$ = V+ $_{24}$ , $I_{IN}$ = 1.5A, Switch On) |                                          | +29  | V   |

| V- MAX_OP                | Steady-State Reverse Bias Standoff Voltage between CTL and NEG Pins $(V_{IN} = V_{-MAX\_OP})$                                        |                                          | -30  |     |

| TJ                       | Operating Junction Temperature                                                                                                       |                                          | 150  | °C  |

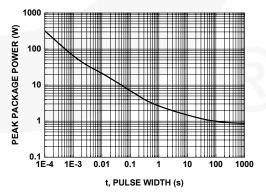

| В                        | Dower Dissination                                                                                                                    | $T_A = 25^{\circ}C^{(2)}$ (see Figure 4) | 2.4  | W   |

| P <sub>D</sub> P         | Power Dissipation                                                                                                                    | $T_A = 25^{\circ}C^{(2)}$ (see Figure 5) | 0.9  |     |

| I <sub>DIODE_CONT</sub>  | Steady-State Diode Continuous Forward Current from POS to NEG                                                                        |                                          | 2    | Α   |

| I <sub>DIODE_PULSE</sub> | Pulsed Diode Forward Current from POS to NEG (300µs Pulse)                                                                           |                                          | 210  | _ A |

| ESD                      | Electrostatic Discharge Capability                                                                                                   | Human Body Model, JESD22-A114            | 600  | V   |

| ESD                      |                                                                                                                                      | Charged Device Model, JESD22-C101        | 2000 |     |

#### Notes:

- 1. The V<sub>+24</sub> rating is NOT a survival guarantee. It is a statistically calculated survivability reference point taken on qualification devices, where the predicted failure rate is less than 0.01% at the specified voltage for 24 hours. It is intended to indicate the device's ability to withstand transient events that exceed the recommended operating voltage rating. Specification is based on qualification devices tested using accelerated destructive testing at higher voltages, as well as production pulse testing at the V<sub>+24</sub> level. Production device field life results may vary. Results are also subject to variation based on implementation, environmental considerations, and circuit dynamics. Systems should never be designed with the intent to normally operate at V<sub>+24</sub> levels. Contact Fairchild Semiconductor for additional information.

- The device power dissipation and thermal resistance (R<sub>θ</sub>) are characterized with device mounted on the following FR4 printed circuit boards, as shown in Figure 4 and Figure 5

Figure 4. 1 Square Inch of 2-ounce copper

Figure 5. Minimum Pads of 2-ounce Copper

# **Thermal Characteristics**

| Symbol           | Parameter                                                             | Value | Unit |  |

|------------------|-----------------------------------------------------------------------|-------|------|--|

| R <sub>0JA</sub> | Thermal Resistance, Junction to Ambient <sup>(2)</sup> (see Figure 4) | 61    | °C/W |  |

| $R_{\theta JA}$  | Thermal Resistance, Junction to Ambient <sup>(2)</sup> (see Figure 5) | 153   | C/VV |  |

# **Electrical Characteristics**

Values are at  $T_A$  = 25°C unless otherwise noted.

| Symbol                                  | Parameter                                                                                                             | Conditions                                                                                          | Min.          | Тур. | Max. | Unit  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|------|------|-------|

| Positive Bia                            | as Characteristics                                                                                                    |                                                                                                     |               | •    |      | •     |

| Ron D                                   | Device Resistance, Switch On                                                                                          | V <sub>IN</sub> = +4V, I <sub>IN</sub> = 1.5A                                                       |               | 13   | 20   | mΩ    |

|                                         |                                                                                                                       | V <sub>IN</sub> = +5V, I <sub>IN</sub> = 1.5A                                                       |               | 11   | 15   |       |

|                                         |                                                                                                                       | $V_{IN} = +5V$ , $I_{IN} = 1.5A$ , $T_J = 125$ °C                                                   |               | 15   |      |       |

|                                         |                                                                                                                       | V <sub>IN</sub> = +12V, I <sub>IN</sub> = 1.5A                                                      |               | 9    | 13   |       |

| $V_{ON}$                                | Input Voltage, V <sub>IN</sub> , at which Voltage at POS, V <sub>POS</sub> , Reaches a Certain Level at Given Current | I <sub>IN</sub> = 100mA, V <sub>POS</sub> = 45mV,<br>V <sub>NFG</sub> = 0V                          | 1.4           | 2.4  | 3.5  | V     |

| $\Delta V_{ON}$ / $\Delta T_J$          | Temperature Coefficient of V <sub>ON</sub>                                                                            |                                                                                                     |               | -3.9 |      | mV/°C |

| I <sub>DIODE_CONT</sub>                 | Continuous Diode Forward Current                                                                                      | V <sub>CTL</sub> = V <sub>POS</sub>                                                                 |               |      | 2    | Α     |

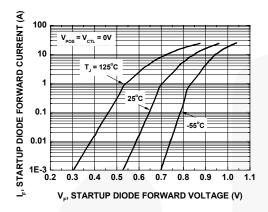

| V <sub>F</sub>                          | Diode Forward Voltage                                                                                                 | $V_{CTL} = V_{POS}$ , $I_{DIODE} = 0.1A$ , Pulse width < 300 $\mu$ s                                | 0.56          | 0.60 | 0.73 | V     |

| I <sub>BIAS</sub>                       | Bias Current Flowing out of NEG Pin during Normal Bias Operation                                                      | V <sub>CTL</sub> = 5V, V <sub>NEG</sub> = 0V,<br>No Load                                            |               | 15   |      | nA    |

| Negative B                              | ias Characteristics                                                                                                   |                                                                                                     |               |      |      |       |

| V- <sub>MAX_OP</sub>                    | Reverse Bias Breakdown Voltage                                                                                        |                                                                                                     | - 1           |      | -30  | V     |

| ΔV- <sub>MAX_OP</sub> / ΔT <sub>J</sub> | Reverse Bias Breakdown Voltage<br>Temperature Coefficient                                                             | $I_{IN} = -250 \mu A, V_{CTL} = V_{POS} = 0V$                                                       |               | 16   |      | mV/°C |

| I-                                      | Leakage Current from NEG to POS in Reverse-Bias Condition                                                             | V <sub>NEG</sub> = 20V, V <sub>CTL</sub> = V <sub>POS</sub> = 0V                                    |               | 1    |      | μA    |

| t <sub>RN</sub>                         | Time to Respond to Negative Bias<br>Condition                                                                         | $V_{NEG}$ = 5V, $V_{CTL}$ = 0V, $C_{LOAD}$ = 10 $\mu$ F, Reverse Bias Startup Inrush Current = 0.2A |               |      | 50   | ns    |

| Dynamic C                               | haracteristics                                                                                                        |                                                                                                     |               |      |      |       |

| Cı                                      | Input Capacitance between CTL and NEG                                                                                 |                                                                                                     |               | 1011 |      |       |

| Cs                                      | Switch Capacitance between POS and NEG                                                                                | $V_{IN} = -5V$ , $V_{CTL} = V_{POS} = 0V$ , $f = 1MHz$                                              | $\mathcal{A}$ | 81   |      | pF    |

| Co                                      | Output Capacitance between CTL and POS                                                                                |                                                                                                     |               | 1456 |      |       |

| Rc                                      | Control Internal Resistance                                                                                           |                                                                                                     |               | 1.7  |      | Ω     |

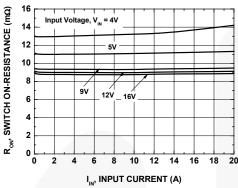

# **Typical Characteristics**

$T_J$  = 25°C unless otherwise specified.

Figure 6. Switch On Resistance vs. Switch Current

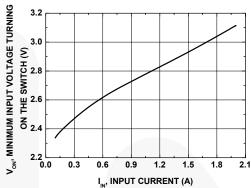

Figure 7. Minimum Input Voltage to Turn On Switch vs. Current at 45mV Switch Voltage Drop

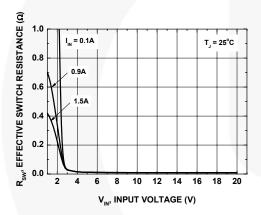

Figure 8. Effective Switch Resistance  $R_{SW}$  vs. Input Voltage  $V_{IN}$

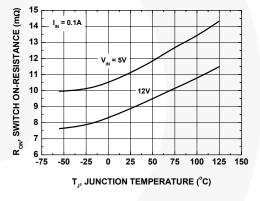

Figure 9. Switch On Resistance vs. Junction Temperature at 0.1A

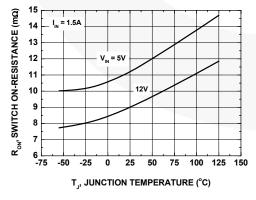

Figure 10. Switch On Resistance vs. Junction Temperature at 1.5A

Figure 11. Single-Pulse Maximum Power vs. Time

# **Typical Characteristics**

$T_J = 25^{\circ}C$  unless otherwise specified.

Figure 12. Startup Diode Current vs. Forward Voltage

# **Application Test Configurations**

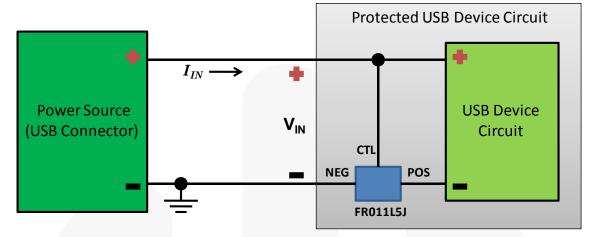

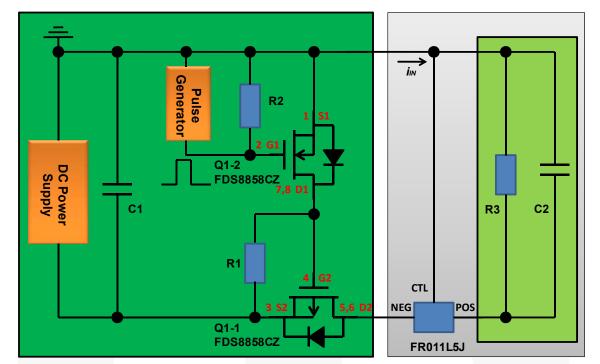

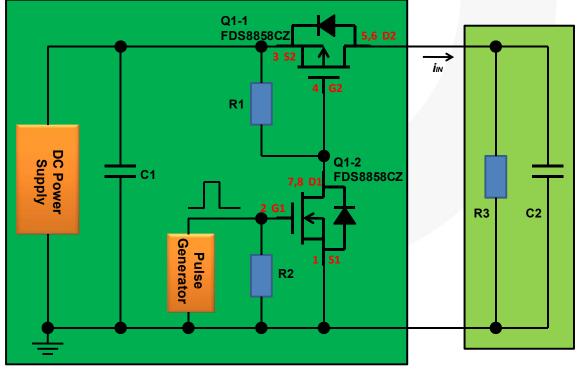

Figure 13. Typical Application Circuit for USB Applications

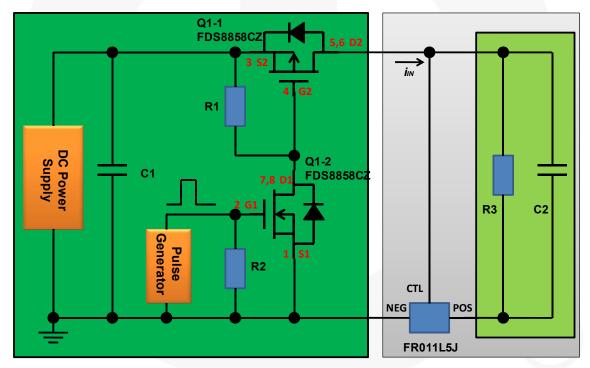

Figure 14. Startup Test Circuit - Normal Bias with FR011L5J

# **Application Test Configurations** (Continued)

Figure 15. Startup Test Circuit - Reverse Bias with FR011L5J

Figure 16. Startup Test Circuit - without FR011L5J

8

© 2012 Fairchild Semiconductor Corporation FR011L5J • Rev. C

www.fairchildsemi.com

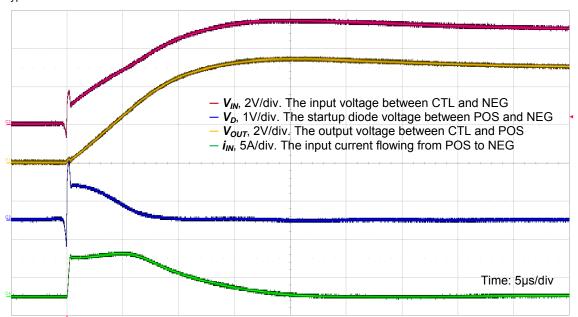

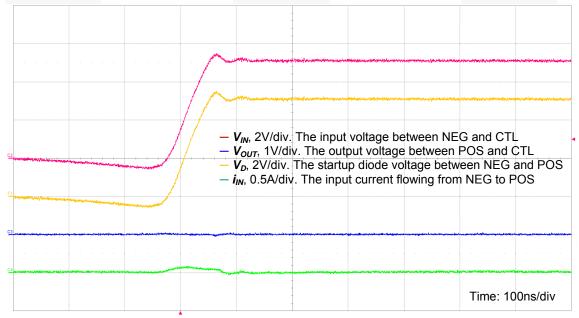

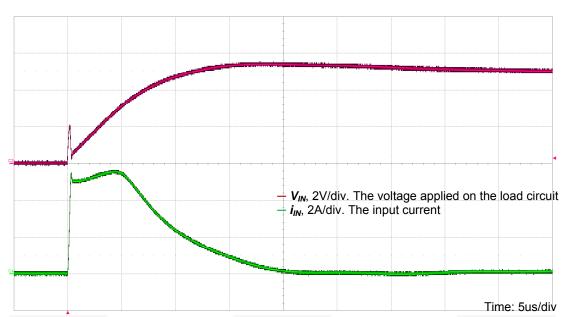

# **Typical Application Waveforms**

Typical USB3.0 conditions.

Figure 17. Normal Bias Startup Waveform, DC Power Source=5V,  $C_1$ =100 $\mu$ F,  $C_2$ =10 $\mu$ F,  $R_1$ = $R_2$ =10k $\Omega$ ,  $R_3$ =27 $\Omega$

Figure 18. Reverse Bias Startup Waveform, DC Power Source=5V, C<sub>1</sub>=100μF, C<sub>2</sub>=10μF, R<sub>1</sub>=R<sub>2</sub>=10kΩ, R<sub>3</sub>=27Ω

# Typical Application Waveforms (Continued)

Typical USB3.0 conditions.

Figure 19. Startup Waveform without FR011L5J, DC Power Source=5V, C<sub>1</sub>=100 $\mu$ F, C<sub>2</sub>=10 $\mu$ F, R<sub>1</sub>=R<sub>2</sub>=10k $\Omega$ , R<sub>3</sub>=27 $\Omega$

# **Application Information**

Figure 17 shows the voltage and current waveforms when a virtual USB3.0 device is connected to a 5V source. A USB application allows a maximum source output capacitance of  $C_1$  = 120 $\mu$ F and a maximum device-side input capacitance of  $C_2$  = 10 $\mu$ F plus a maximum load (minimum resistance) of  $R_3$  = 27 $\Omega$ .  $C_1$  = 100 $\mu$ F,  $C_2$  = 10 $\mu$ F and  $R_3$  = 27 $\Omega$  were used for testing.

When the DC power source is connected to the circuit (refer to Figure 13), the built-in startup diode initially conducts the current such that the USB device powers up. Due to the initial diode voltage drop, the FR011L5J effectively reduces the peak inrush current of a hot plug event. Under these test conditions, the input inrush current reaches about 6.3A peak. While the current flows, the input voltage increases. The speed of this input voltage increase depends on the time constant formed by the load resistance R<sub>3</sub> and load capacitance C<sub>2</sub>. The larger the time constant, the slower the input voltage increase. As the input voltage approaches a level equal to the protector's turn-on voltage, V<sub>ON</sub>, the protector turns on and operates in Low-Resistance Mode as defined by V<sub>IN</sub> and operating current I<sub>IN</sub>.

In the event of a negative transient, or when the DC power source is reversely connected to the circuit, the device blocks the flow of current and holds off the voltage, thereby protecting the USB device. Figure 18 shows the voltage and current waveforms when a virtual

USB3.0 device is reversely biased; the output voltage is near 0 and response time is less than 50ns.

Figure 19 shows the voltage and current waveforms when no reverse bias protection is implemented. In Figure 17, while the reverse bias protector is present, the input voltage,  $V_{\text{IN}}$ , and the output voltage,  $V_{\text{O}}$ , are separated and look different. When this reverse bias protector is removed,  $V_{\text{IN}}$  and  $V_{\text{O}}$  merge, as shown in Figure 19 as  $V_{\text{IN}}$ . This  $V_{\text{IN}}$  is also the voltage applied to the load circuit. It can be seen that, with reverse bias protection, the voltage applied to the load and the current flowing into the load look very much the same as without reverse bias protection.

#### **Benefits of Reverse Bias Protection**

The most important benefit is to prevent accidently reverse-biased voltage from damaging the USB load. Another benefit is that, the peak startup inrush current can be reduced. How fast the input voltage rises, the input/output capacitance, the input voltage, and how heavy the load is determine how much the inrush current can be reduced. In a 5V USB application, for example, the inrush current can be 5% - 20% less with different input voltage rising rate and other factors. This can offer a system designer the option of increasing C2 while keeping "effective" USB device capacitance down.

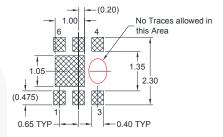

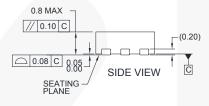

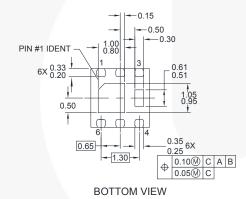

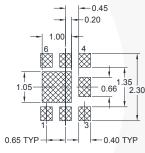

# **Physical Dimensions**

**RECOMMENDED LAND PATTERN OPT 1**

RECOMMENDED LAND PATTERN OPT 2

#### NOTES:

- A. DOES NOT FULLY CONFORM TO JEDEC REGISTRATION MO-229 DATED AUG/2003

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER

- ASME Y14.5M, 1994 D. DRAWING FILENAME: MKT-MLP06Lrev3.

Figure 20. 6-Lead, Molded Leadless Package (MLP), Dual, Non-JEDEC, 2mm Square, Single-Tied DAP

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

F-PESTM 2Cool™ FRFET® AccuPower™ Global Power Resource<sup>SM</sup> AX-CAP™ BitSiC™ GreenBridge™ Green FPS™ Build it Now™ Green FPS™ e-Series™ CorePLUS™ CorePOWER™ Gmax™ GTO™ CROSSVOLT™ IntelliMAX™ CTL™ ISOPLANAR™ Current Transfer Logic™

Making Small Speakers Sound Louder DEUXPEED<sup>®</sup> and Better™

MegaBuck™

MicroFET™

MicroPak™

MicroPak2™

MillerDrive™

MotionMax™

mWSaver™

OptoHiT™

Motion-SPM™

OPTOLOGIC®

**OPTOPLANAR®**

MICROCOUPLER™

Dual Cool™ EcoSPARK® EfficientMax™ ESBC™

Fairchild<sup>®</sup>

Fairchild Semiconductor® FACT Quiet Series™ FACT FAST® FastvCore™

FETBench™ FlashWriter®\* **FPSTM**

PowerTrench® PowerXS™

Programmable Active Droop™ QFET<sup>®</sup>

QS™ Quiet Series™ RapidConfigure™ **○**TM

Saving our world, 1mW/W/kW at a time™

SignalWise<sup>TM</sup> SmartMax™ SMART START™

Solutions for Your Success™

STEALTH™ SuperFET<sup>®</sup> SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™ SYSTEM GENERAL®\* puwer franchis TinyBoost™ TinyBuck™ TinyCalc™

The Power Franchise®

TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ TranSiC™ TriFault Detect™ TRUECURRENT®\*

μSerDes™ UHC Ultra FRFET™ UniFET™ VCX™ VisualMax™ VoltagePlus™

XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor,

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification |                       | Definition                                                                                                                                                                                          |  |  |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 161

www.fairchildsemi.com 12