July 2010

# FAN6982 CCM Power Factor Correction Controller

# Features

SEMICONDUCTOR

- Continuous Conduction Mode

- Innovative Switching-Charge Multiplier-Divider

- Average-Current-Mode for Input-Current Shaping

- TriFault Detect<sup>™</sup> Prevent Abnormal Operation for Feedback Loop

- Power-On Sequence Control

- Soft-Start Capability

- Brownout Protection

- Cycle-by-Cycle Peak Current Limiting.

- Improves Light-Load Efficiency

- Fulfills Class-D Requirements of IEC 1000-3-2

- Wide Range Universal AC Input Voltage

- Maximum Duty Cycle 97%

- V<sub>DD</sub> Under-Voltage Lockout (UVLO)

# Applications

- Desktop PC Power Supply

- Internet Server Power Supply

- LCD TV/Monitor Power Supply

- DC Motor Power Supply

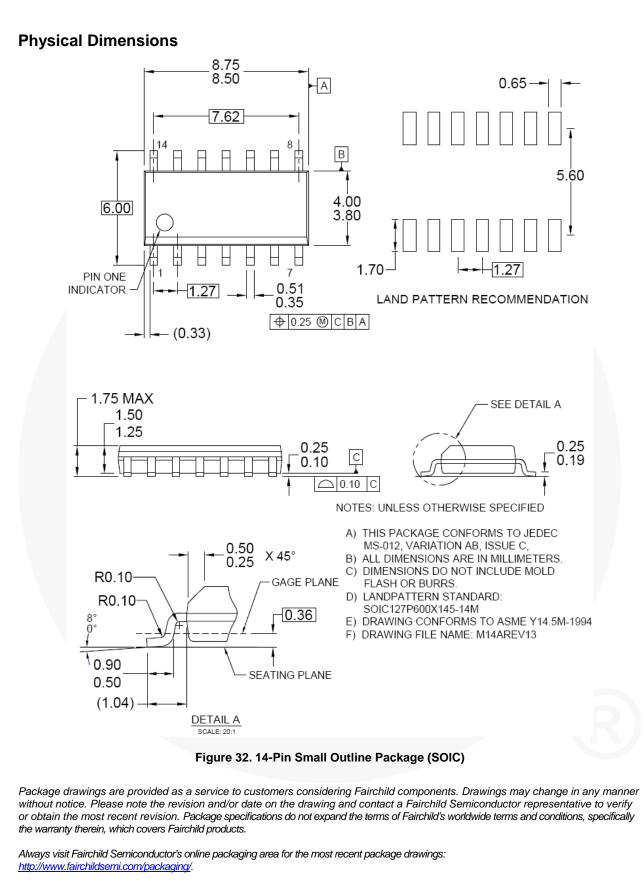

# **Ordering Information**

| Part Number | Operating Temperature Range | Package                            | Packing Method |  |

|-------------|-----------------------------|------------------------------------|----------------|--|

| FAN6982MY   | -40°C to +105°C             | 14-Pin Small Outline Package (SOP) | Tape & Reel    |  |

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

# Description

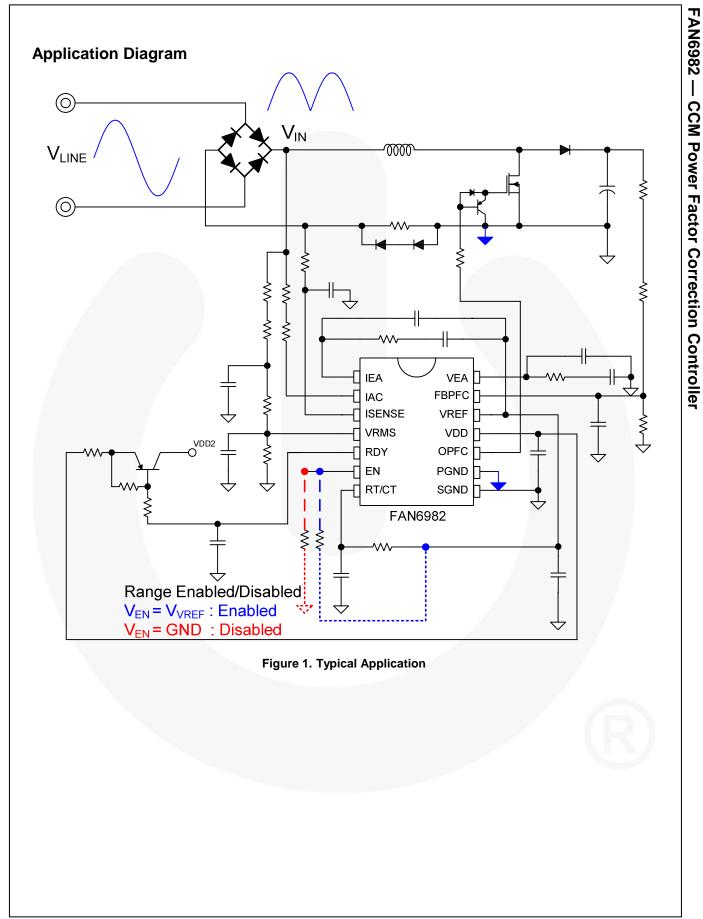

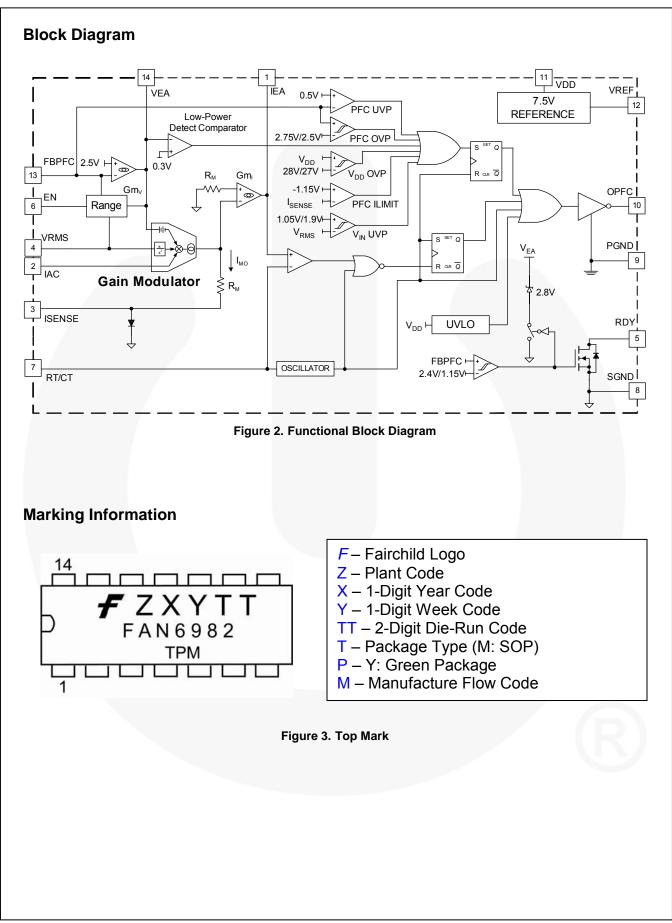

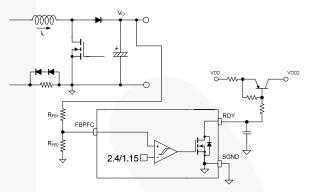

The FAN6982 is a 14-pin, Continuous Conduction Mode (CCM) PFC controller IC intended for Power Factor Correction (PFC) pre-regulators. The FAN6982 includes circuits for the implementation of leading edge, average current, "boost"-type power factor correction, and results in a power supply that fully complies with the IEC1000-3-2 specification.

A TriFault Detect<sup>™</sup> function helps reduce external components and provides full protection for feedback loops such as open, short, and over voltage. An overvoltage comparator shuts down the PFC stage in the event of a sudden load decrease. The RDY signal can be used for power-on sequence control. The EN function can choose to enable or disable the range function. FAN6982 also includes PFC soft-start, peak current limiting, and input voltage brownout protection.

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

Figure 4. Pin Configuration

# **Pin Definitions**

| Pin # | Name   | Description                                                                                                                                                                                                                                      |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IEA    | <b>Output of Current Amplifier</b> . This is the output of the PFC current amplifier. The signal from this pin is compared with sawtooth and determines the pulsewidth for PFC gate drive.                                                       |

| 2     | IAC    | <b>Input AC Current</b> . For normal operation, this input is used to provide current reference for the multiplier. The suggested maximum $I_{AC}$ is 100µA.                                                                                     |

| 3     | ISENSE | <b>Current Sense</b> . The non-inverting input of the PFC current amplifier and the output of multiplier and PFC I <sub>LIMIT</sub> comparator.                                                                                                  |

| 4     | VRMS   | Line-Voltage Detection. The pin is used for PFC multiplier.                                                                                                                                                                                      |

| 5     | RDY    | <b>Ready Signal</b> . This pin controls the power-on sequence. Once the FAN6982 is turned on and the FBPFC voltage exceeds in 2.4V, the RDY pin pulls LOW impedance. If the FBPFC voltage is lower than 1.15V, the RDY pin pulls HIGH impedance. |

| 6     | EN     | <b>Enable Range Function</b> . The range function is enabled when EN is connected to $V_{REF}$ . The range function is disabled when EN is connected to GND.                                                                                     |

| 7     | RT/CT  | Oscillator RC Timing Connection. Oscillator timing node; timing set by RT and CT.                                                                                                                                                                |

| 8     | SGND   | Signal Ground.                                                                                                                                                                                                                                   |

| 9     | PGND   | Power Ground.                                                                                                                                                                                                                                    |

| 10    | OPFC   | <b>Gate Drive</b> . The totem-pole output drive for PFC MOSFET. This pin is internally clamped under 15V to protect the MOSFET.                                                                                                                  |

| 11    | VDD    | <b>Power Supply</b> . The threshold voltages for startup and turn-off are 11V and 9.3V, respectively. The operating current is lower than 10mA.                                                                                                  |

| 12    | VREF   | Reference Voltage. Buffered output for the internal 7.5V reference.                                                                                                                                                                              |

| 13    | FBPFC  | <b>Voltage Feedback Input</b> . The feedback input for PFC voltage loop. The inverting input of PFC error amplifier. This pin is connected to the PFC output through a divider network.                                                          |

| 14    | VEA    | <b>Output of Voltage Amplifier</b> . The error-amplifier output for PFC voltage feedback loop. A compensation network is connected between this pin and ground.                                                                                  |

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol               | Paramete                                 | er                                | Min.   | Max.                   | Unit |

|----------------------|------------------------------------------|-----------------------------------|--------|------------------------|------|

| V <sub>DD</sub>      | DC Supply Voltage                        |                                   |        | 30                     | V    |

| V <sub>H</sub>       | OPFC, RDY, EN, VREF                      |                                   | -0.3   | 30.0                   | V    |

| VL                   | IAC, VRMS, RT/CT, FBPFC, VEA             |                                   | -0.3   | 7.0                    | V    |

| VIEA                 | IEA                                      |                                   | 0      | V <sub>VREF</sub> +0.3 | V    |

| V <sub>N</sub>       | ISENSE                                   |                                   | -5.0   | 0.7                    | V    |

| I <sub>AC</sub>      | Input AC Current                         |                                   |        | 1                      | mA   |

| I <sub>REF</sub>     | VREF Output Current                      |                                   |        | 5                      | mA   |

| I <sub>PFC-OUT</sub> | Peak PFC OUT Current, Source or S        |                                   | 0.5    | А                      |      |

| PD                   | Power Dissipation, T <sub>A</sub> < 50°C |                                   |        | 800                    | mW   |

| R <sub>⊝ j-a</sub>   | Thermal Resistance (Junction-to-Air)     |                                   | 104.10 | °C/W                   |      |

| R <sub>⊖ j-c</sub>   | Thermal Resistance (Junction-to-Case)    |                                   |        | 40.61                  | °C/W |

| TJ                   | Operating Junction Temperature           |                                   | -40    | +125                   | °C   |

| T <sub>STG</sub>     | Storage Temperature Range                |                                   | -55    | +150                   | °C   |

| TL                   | Lead Temperature (Soldering)             |                                   |        | +260                   | °C   |

| ESD                  | Electrostatic Discharge Conshility       | Human Body Model,<br>JESD22-A114  |        | 4.5                    | kV   |

| ESD                  | Electrostatic Discharge Capability       | Charged Device Model, JESD22-C101 |        | 1.0                    | κv   |

### Notes:

1. All voltage values, except differential voltage, are given with respect to the GND pin.

2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                     | Min. | Max. | Unit |  |

|----------------|-------------------------------|------|------|------|--|

| T <sub>A</sub> | Operating Ambient Temperature |      | +105 | °C   |  |

| FAN6982 -  |  |

|------------|--|

| - CCM P    |  |

| ower Facto |  |

| r Corre    |  |

| ection Con |  |

| troller    |  |

| Symbol                          | Parameter                                                 | Conditions                                                                                       | Min. | Тур. | Max. | Units |

|---------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DD</sub> Section         |                                                           |                                                                                                  | L    |      |      |       |

| V <sub>DD-OP</sub>              | Continuously Operating<br>Voltage                         |                                                                                                  |      |      | 22   | V     |

| I <sub>DD ST</sub>              | Startup Current                                           | V <sub>DD</sub> =V <sub>TH-ON</sub> -0.1V; OPFC Open                                             |      | 30   | 80   | μA    |

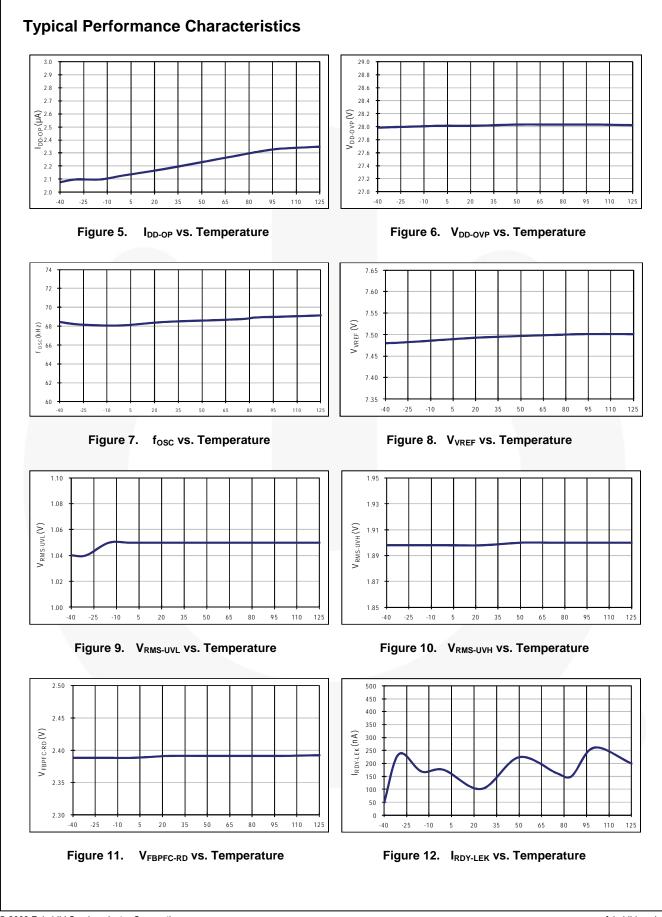

| I <sub>DD-OP</sub>              | Operating Current                                         | V <sub>DD</sub> =13V; OPFC Open                                                                  | 2.0  | 2.3  | 3.0  | mA    |

| $V_{\text{TH-ON}}$              | Turn-on Threshold Voltage                                 |                                                                                                  | 10   | 11   | 12   | V     |

| $	riangle V_{TH}$               | Hysteresis                                                |                                                                                                  | 1.35 |      | 1.90 | V     |

| V <sub>DD-OVP</sub>             | V <sub>DD</sub> OVP                                       |                                                                                                  | 27   | 28   | 29   | V     |

| $	riangle V_{\text{DD-OVP}}$    | V <sub>DD</sub> OVP Hysteresis                            |                                                                                                  |      | 1    |      | V     |

| Oscillator                      |                                                           |                                                                                                  |      |      |      |       |

| f <sub>OSC</sub>                | PFC Frequency                                             | R <sub>T</sub> =27kΩ, C <sub>T</sub> =1000pF                                                     | 60   | 64   | 67   | kHz   |

| f <sub>DV</sub> <sup>(3)</sup>  | Voltage Stability                                         | $11V \leq V_{DD} \leq 22V$                                                                       |      |      | 2    | %     |

| f <sub>DT</sub> <sup>(3)</sup>  | Temperature Stability                                     | -40°C ~ +105°C                                                                                   |      |      | 2    | %     |

| f <sub>TV</sub>                 | Total Variation                                           | Line, Temperature                                                                                | 58   |      | 70   | kHz   |

| f <sub>RV</sub>                 | Ramp Voltage                                              | Valley-to-Peak                                                                                   |      | 2.8  |      | V     |

| IOSC-DIS                        | Discharge Current                                         | V <sub>RAMP</sub> =0V, V <sub>RT/CT</sub> =2.5V                                                  | 6.5  |      | 15.0 | mA    |

| <b>f</b> RANGE                  | Frequency Range                                           |                                                                                                  | 50   |      | 75   | kHz   |

| t <sub>PFC-DEAD</sub>           | PFC Dead Time                                             | R <sub>T</sub> =27kΩ, C <sub>T</sub> =1000pF                                                     | 400  | 600  | 800  | ns    |

| V <sub>REF</sub>                |                                                           |                                                                                                  |      |      |      |       |

| V <sub>VREF</sub>               | Reference Voltage                                         | I <sub>REF</sub> =0mA, C <sub>REF</sub> =0.1µF                                                   | 7.4  | 7.5  | 7.6  | V     |

| $	riangle V_{VREF1}$            | Load Regulation of<br>Reference Voltage                   | $C_{REF}$ =0.1µF, I <sub>REF</sub> =0mA to 3.5mA<br>V <sub>VDD</sub> =14V, Rise/Fall Time > 20µs |      | 30   | 50   | mV    |

| $	riangle V_{VREF2}$            | Line Regulation of Reference Voltage                      | $C_{REF}=0.1\mu F$ , $V_{VDD}=11V$ to 22V                                                        |      |      | 25   | mV    |

| $	riangle V_{VREF-DT}$          | Temperature Stability <sup>(3)</sup>                      | -40°C ~ +105°C                                                                                   |      | 0.4  | 0.5  | %     |

| $\triangle V_{\text{VREF-TV}}$  | Total Variation <sup>(3)</sup>                            | Line, Load, Temperature                                                                          | 7.35 |      | 7.65 | V     |

| $	riangle V_{VREF-LS}$          | Long-Term Stability <sup>(3)</sup>                        | T <sub>J</sub> =125°C, 0 ~ 1000HRs                                                               | 5    |      | 25   | mV    |

| I <sub>REF-MAX</sub>            | Maximum Current                                           | V <sub>VREF</sub> > 7.35V                                                                        | 5    |      | /    | mA    |

| Brownout                        |                                                           |                                                                                                  |      |      | 1    |       |

| V <sub>RMS-UVL</sub>            | V <sub>RMS</sub> Threshold Low                            | When V <sub>RMS</sub> =1.05V at 75 V <sub>RMS</sub>                                              | 1.00 | 1.05 | 1.10 | V     |

| V <sub>RMS-UVH</sub>            | V <sub>RMS</sub> Threshold High                           | When V <sub>RMS</sub> =1.9V at 85 • 1.414                                                        | 1.85 | 1.90 | 1.95 | V     |

| $\triangle V_{RMS-UVP}$         | Hysteresis                                                |                                                                                                  | 750  | 850  | 950  | mV    |

| t <sub>UVP</sub>                | Under-Voltage Protection<br>Debounce Time                 |                                                                                                  | 340  | 410  | 480  | ms    |

| RDY Section                     |                                                           |                                                                                                  |      |      |      |       |

| V <sub>FBPFC-RD</sub>           | FBPFC Voltage Level to Pull<br>Low Impedance with RDY Pin |                                                                                                  | 2.3  | 2.4  | 2.5  | V     |

| $\triangle V_{\text{FBPFC-RD}}$ | Hysteresis                                                |                                                                                                  | 1.15 | 1.25 | 1.35 | V     |

| I <sub>RDY-LEK</sub>            | Leakage Current of RDY<br>High Impedance                  | V <sub>FBPFC</sub> <2.4V                                                                         |      |      | 500  | nA    |

| V <sub>RDY-L</sub>              | RDY Low Voltage                                           | I <sub>SINK</sub> =2mA                                                                           |      | İ    | 0.5  | V     |

Continued on the following page...

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

www.fairchildsemi.com

| Symbol                           | Parameter                             | Conditions                                                                              | Min. | Тур. | Max.  | Units |

|----------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------|------|------|-------|-------|

| Voltage Erro                     | r Amplifier                           |                                                                                         | •    | •    | •     |       |

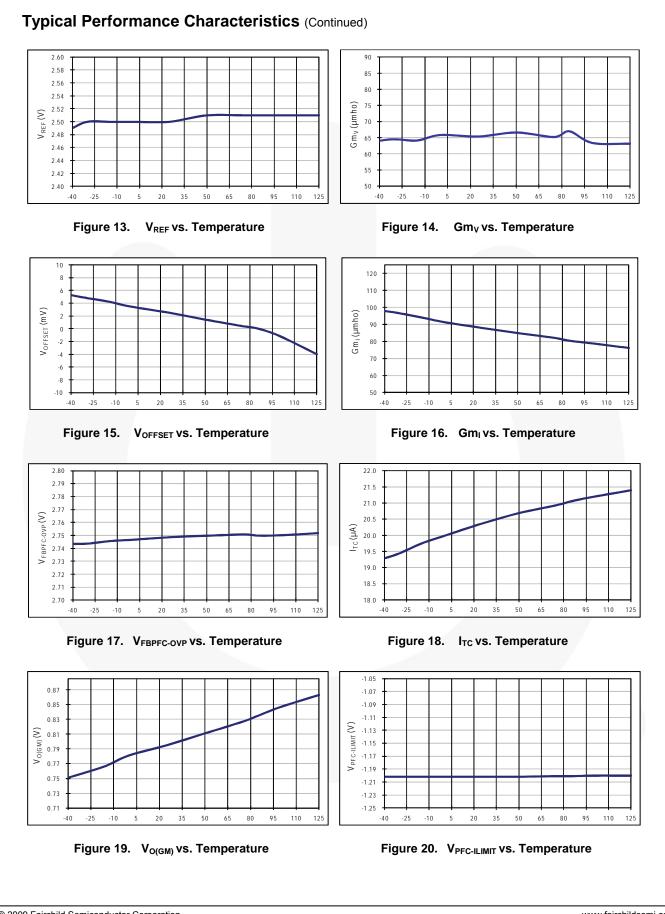

| V <sub>REF</sub>                 | Reference Voltage                     |                                                                                         | 2.45 | 2.50 | 2.55  | V     |

| Av                               | Open-Loop Gain <sup>(3)</sup>         | At T <sub>A</sub> =25°C                                                                 | 35   | 42   |       | dB    |

| $Gm_V$                           | Transconductance                      | V <sub>NONINV</sub> =V <sub>INV</sub> , V <sub>VEA</sub> =3.75V at T <sub>A</sub> =25°C | 50   | 70   | 90    | µmho  |

| I <sub>FBPFC-L</sub>             | Maximum Source Current                | V <sub>FBPFC</sub> =2V, V <sub>VEA</sub> =1.5V                                          | 40   | 50   |       | μA    |

| I <sub>FBPFC-H</sub>             | Maximum Sink Current                  | V <sub>FBPFC</sub> =3V, V <sub>VEA</sub> =6V                                            |      | -50  | -40   | μA    |

| I <sub>BS</sub>                  | Input Bias Current                    |                                                                                         | -1   |      | 1     | μA    |

| $V_{\text{VEA-H}}$               | Output High Voltage on VVEA           |                                                                                         | 5.8  | 6.0  |       | V     |

| V <sub>VEA-L</sub>               | Output Low Voltage on VVEA            |                                                                                         |      | 0.1  | 0.4   | V     |

| Current Erro                     | or Amplifier                          |                                                                                         |      |      |       |       |

| VISENSE                          | Input Voltage Range                   |                                                                                         | -1.5 |      | 0.7   | V     |

| Aı                               | Open-Loop Gain <sup>(3)</sup>         | At T <sub>A</sub> =25°C                                                                 | 40   | 50   |       | dB    |

| Gmı                              | Transconductance                      | V <sub>NONINV</sub> =V <sub>INV</sub> , V <sub>IEA</sub> =3.75V                         | 75   | 88   | 100   | µmho  |

| VOFFSET                          | Input Offset Voltage                  | V <sub>VEA</sub> =0V, I <sub>AC</sub> Open                                              | -10  |      | 10    | mV    |

| V <sub>IEA-H</sub>               | Output High Voltage                   |                                                                                         | 6.8  | 7.4  | 8.0   | V     |

| V <sub>IEA-L</sub>               | Output Low Voltage                    |                                                                                         |      | 0.1  | 0.4   | V     |

| ΙL                               | Source Current                        | V <sub>ISENSE</sub> = -0.6V, V <sub>IEA</sub> =1.5V                                     | 35   | 50   |       | μA    |

| l <sub>Η</sub>                   | Sink Current                          | V <sub>ISENSE</sub> = +0.6V, V <sub>IEA</sub> =4.0V                                     |      | -50  | -35   | μA    |

| PFC OVP Co                       | omparator                             |                                                                                         |      |      |       |       |

| V <sub>FBPFC-OVP</sub>           | Over Voltage Protection               |                                                                                         | 2.70 | 2.75 | 2.80  | V     |

| $\triangle V_{\text{FBPFC-OVP}}$ | PFC OVP Hysteresis                    |                                                                                         | 200  | 250  | 300   | mV    |

| Low-Power I                      | Detect Comparator                     |                                                                                         |      |      | •     |       |

| V <sub>VEA-OFF</sub>             | VEA Voltage Off OPFC                  |                                                                                         | 0.2  | 0.3  | 0.4   | V     |

| PFC Soft-Sta                     | art                                   | 1                                                                                       |      | 1    | 1     |       |

| VVEA_CLAMP                       | PFC Soft-Start                        | V <sub>FBPFC</sub> < 2.4V                                                               | 2.2  | 2.8  | 3.3   | V     |

| EN Section                       |                                       | 1                                                                                       | 1    |      |       |       |

| V <sub>EN-H</sub>                | High Voltage Level of V <sub>EN</sub> | V <sub>EN</sub> =V <sub>VREF</sub>                                                      | 7.4  | 7.5  | 7.6   | V     |

| V <sub>EN-L</sub>                | Low Voltage Level of VEN              | V <sub>EN</sub> =GND                                                                    |      | 0    |       | V     |

| Range                            |                                       |                                                                                         |      |      | /     | 1     |

| V <sub>VRMS-L</sub>              | RMS AC Voltage Low                    | When V <sub>VRMS</sub> =1.95V at 132V <sub>RMS</sub>                                    | 1.90 | 1.95 | 20.00 | V     |

| V <sub>VRMS-H</sub>              | RMS AC Voltage High                   | When $V_{VRMS}$ =2.45V at 150 $V_{RMS}$                                                 | 2.40 | 2.45 | 2.50  | V     |

| V <sub>VEA-L</sub>               | VEA Low                               | When V <sub>VEA</sub> =1.95V at 30% Loading                                             | 1.90 | 1.95 | 2.00  | V     |

| V <sub>VEA-H</sub>               | VEA High                              | When V <sub>VEA</sub> =2.45V at 40% Loading                                             | 2.40 | 2.45 | 2.50  | V     |

| I <sub>TC</sub>                  | Source Current from FBPFC             |                                                                                         | 18   | 20   | 22    | μA    |

# Electrical Characteristics (Continued)

Continued on the following page...

# Electrical Characteristics (Continued)

Unless otherwise noted;  $V_{DD}$ =15V,  $T_A$ = 25°C,  $T_A$ =T<sub>J</sub>,  $R_T$ =27k $\Omega$ , and  $C_T$ =1000pF.

| Symbol                  | Parameter                                                            | Conditions                                                                                            | Min.  | Тур.  | Max.   | Units |

|-------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|--------|-------|

| Gain Modula             | ator                                                                 |                                                                                                       |       |       |        |       |

| I <sub>AC</sub>         | Input for AC Current                                                 | Multiplier Linear Range                                                                               | 0     |       | 100    | μA    |

|                         |                                                                      | $I_{IAC}$ =17.67µA, V <sub>VRMS</sub> =1.080V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C   | 7.500 | 9.000 | 10.500 |       |

|                         |                                                                      | $I_{IAC}$ =20µA, V <sub>VRMS</sub> =1.224V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C      | 6.367 | 7.004 | 7.704  |       |

| GAIN                    | Gain Modulator <sup>(3)(4)</sup>                                     | $I_{IAC}$ =25.69µA, V <sub>VRMS</sub> =1.585V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C   | 3.801 | 4.182 | 4.600  |       |

|                         |                                                                      | $I_{IAC}$ =51.62µA, V <sub>VRM</sub> S=3.169V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C   | 0.950 | 1.045 | 1.149  |       |

|                         |                                                                      | $I_{IAC}$ =62.23µA, V <sub>VRMS</sub> =3.803V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C   | 0.660 | 0.726 | 0.798  |       |

| BW                      | Bandwidth                                                            | I <sub>IAC</sub> =40µA                                                                                |       | 2     |        | kHz   |

| V <sub>O(GM)</sub>      | Output Voltage=5.7kΩ ×<br>(I <sub>SENSE</sub> -I <sub>OFFSET</sub> ) | I <sub>AC</sub> =20μA, V <sub>RMS</sub> =1.224V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C | 0.710 | 0.798 | 0.885  | V     |

| PFC ILIMIT CO           | mparator                                                             |                                                                                                       |       |       |        |       |

| Vpfc-ilimit             | Peak Current Limit<br>Threshold Voltage<br>Cycle-by-Cycle Limit      |                                                                                                       | -1.25 | -1.15 | -1.05  | v     |

| $	riangle V_{pk}$       | PFC I <sub>LIMIT</sub> -Gain Modulator<br>Output                     | $I_{IAC}$ =17.67µA, V <sub>VRMS</sub> =1.08V<br>V <sub>FBPFC</sub> =2.25V, at T <sub>A</sub> =25°C    | 200   |       |        | mV    |

| PFC Output              | Driver                                                               |                                                                                                       |       |       |        |       |

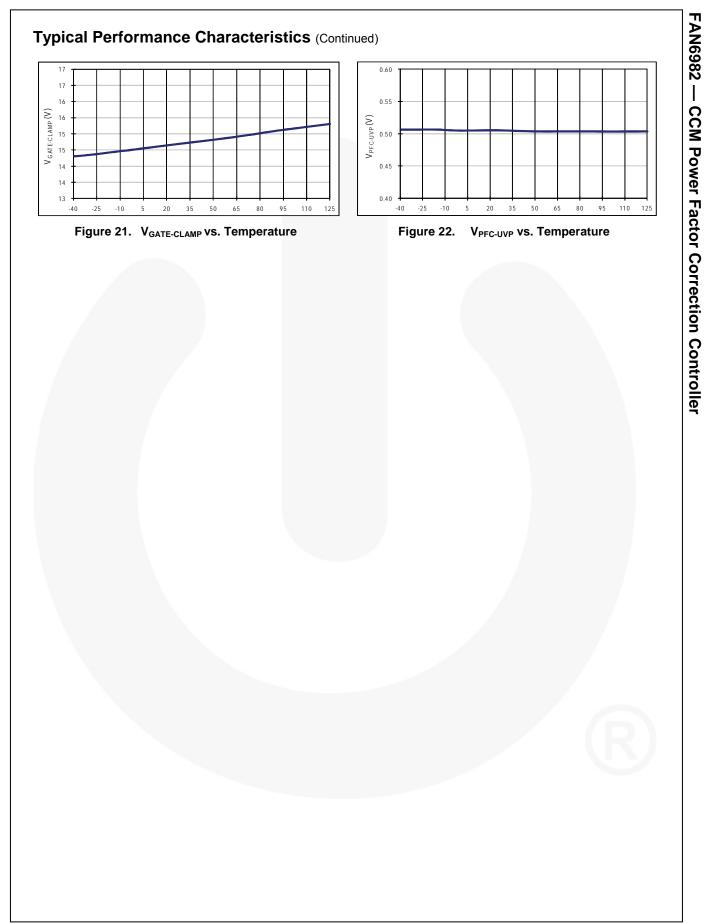

| $V_{\text{GATE-CLAMP}}$ | Gate Output Clamping<br>Voltage                                      | V <sub>DD</sub> =22V                                                                                  | 13    | 15    | 17     | V     |

| $V_{GATE-L}$            | Gate Low Voltage                                                     | V <sub>DD</sub> =15V; I <sub>O</sub> =100mA                                                           |       |       | 1.5    | V     |

| $V_{\text{GATE-H}}$     | Gate High Voltage                                                    | V <sub>DD</sub> =13V; I <sub>O</sub> =100mA                                                           | 8     |       |        | V     |

| t <sub>R</sub>          | Gate Rising Time                                                     | V <sub>DD</sub> =15V; C <sub>L</sub> =4.7nF;<br>O/P= 2V to 9V                                         | 40    | 70    | 120    | ns    |

| t <sub>F</sub>          | Gate Falling Time                                                    | V <sub>DD</sub> =15V; C <sub>L</sub> =4.7nF;<br>O/P= 9V to 2V                                         | 40    | 60    | 110    | ns    |

| D <sub>PFC-MAX</sub>    | Maximum Duty Cycle                                                   | V <sub>IEA</sub> <1.2V                                                                                | 94    | 97    | /-     | %     |

| D <sub>PFC-MIN</sub>    | Minimum Duty Cycle                                                   | V <sub>IEA</sub> >4.5V                                                                                |       |       | 0      | %     |

| Tri-Fault Det           | tect                                                                 |                                                                                                       |       |       |        |       |

| t <sub>fbpfc_open</sub> | Time to FBPFC Open                                                   | V <sub>FBPFC</sub> =V <sub>FBPFC-OVP</sub> to FBPFC<br>OPEN, 470pF from FBPFC to GND                  |       | 2     | 4      | ms    |

| V <sub>PFC-UVP</sub>    | PFC Feedback Under-<br>Voltage Protection                            |                                                                                                       | 0.4   | 0.5   | 0.6    | v     |

Notes:

3. This parameter, although guaranteed by design, is not 100% production tested.

4. This gain is the maximum gain of modulation with a given V<sub>RMS</sub> voltage when V<sub>EA</sub> is saturated to high.

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

# **Functional Description**

### Oscillator

The internal oscillator frequency of FAN6982 is determined by the timing resistor and capacitor on the RT/CT pin, but note that the optimum operation for FAN6982 is between 50 and 75kHz. The frequency of the internal oscillator is given by:

$$f_{OSC} = \frac{1}{0.56 \cdot R_T \cdot C_T + 360C_T}$$

(1)

The dead time for the PFC gate drive signal is determined by

$$t_{DEAD} = 360C_T \tag{2}$$

The dead time should be smaller than 2% of switching period to minimize line current distortion around line zero crossing.

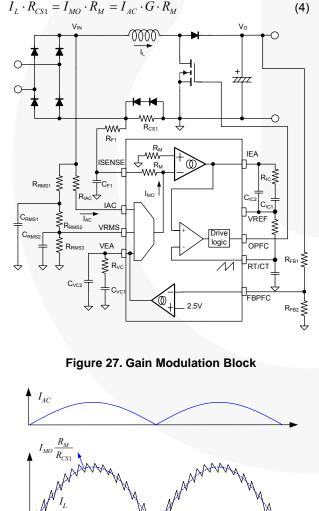

### **Gain Modulator**

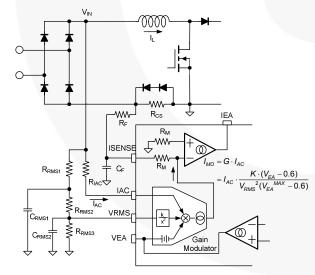

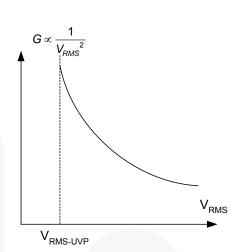

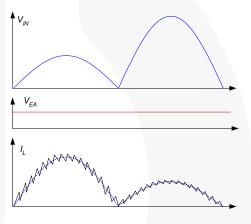

Gain modulator is the key block for PFC stage because it provides the reference to the current control error amplifier for the input current shaping, as shown in Figure 23. The output current of gain modulator is a function of V<sub>EA</sub>, I<sub>AC</sub> and V<sub>RMS</sub>. The gain of the gain modulator is given as a ratio between I<sub>MO</sub> and I<sub>AC</sub> with a given V<sub>RMS</sub> when V<sub>EA</sub> is saturated to high. The gain is inversely proportional to V<sub>RMS</sub><sup>2</sup>, as shown in Figure 24, to implement line feed-forward. This automatically adjusts the reference of current control error amplifier according to the line voltage such that the input power of PFC converter is not changed with line voltage, as shown in, Figure 25.

Figure 23. Gain Modulator Block

**Figure 24. Modulation Gain Characteristics**

Figure 25. Line Feed-Forward Operation

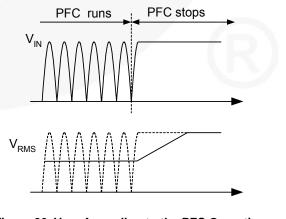

To sense the RMS value of the line voltage, an averaging circuit with two poles is typically employed as shown in Figure 23. Notice that the input voltage of PFC is clamped at the peak of the line voltage once PFC stops switching since the junction capacitance of bridge diode is not discharged, as shown in Figure 26.

Therefore, the voltage divider for  $V_{\text{RMS}}$  should be designed considering the brownout protection trip point and minimum operation line voltage.

Figure 26. V<sub>RMS</sub> According to the PFC Operation

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

The rectified sinusoidal signal is obtained by the current flowing into the IAC pin. The resistor RIAC should be large enough to prevent saturation of the gain modulator as:

$$\frac{\sqrt{2}V_{LINE.BO}}{R_{LAC}} \cdot G^{MAX} < 159 \mu A \tag{3}$$

where  $V_{\text{LINE},BQ}$  is the line voltage that trips brownout protection,  $G^{MAX}$  is the maximum modulator gain when  $V_{\text{RMS}}$  is 1.08V, and 159µA is the maximum output current of the gain modulator.

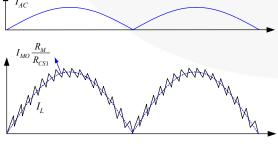

### **Current-Control of Boost Stage**

As shown in Figure 27 the FAN6982 employs two control loops for power factor correction, a currentcontrol loop and a voltage-control loop. The currentcontrol loop shapes inductor current, as shown in Figure 28, based on the reference signal obtained at IAC pin as:

Figure 28. Inductor Current Shaping

The current-control feedback loop also has a pulse-bypulse current limit comparator that forces the PFC switch to turn off if the ISENSE pin voltage drops below -1.15V until the next switching cycle.

### Voltage-Control of Boost Stage

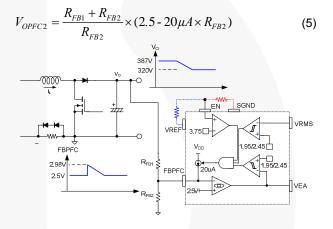

The voltage-control loop regulates PFC output voltage using internal error amplifier such that the FBPFC voltage is same as internal reference of 2.5V.

To improve system efficiency at low AC line voltage and light-load condition, FAN6982 provides adjustable PFC output voltage. As shown in Figure 29, FAN6982 monitors VEA and VRMS to adjust the PFC output voltage. When V<sub>EA</sub> and V<sub>RMS</sub> are lower than thresholds, internal current source of 20µA is enabled that flows through R<sub>FB2</sub>, increasing the voltage of the FBPFC pin. This causes the PFC output voltage to reduce when 20µA is enabled as:

Figure 29. Block of Adjustable PFC Output

### **Brownout Protection**

FAN6982 has a built-in internal brownout protection comparator monitoring the voltage of the VRMS pin. Once the VRMS pin voltage is lower than 1.05V, the PFC stage is shutdown to protect the system from over current. FAN6982 starts up the boost stage once the VRMS voltage increases above 1.9V.

### TriFault Detect<sup>™</sup>

To improve power supply reliability, reduce system component count, and simplify compliance to UL 1950 safety standards; the FAN6982 includes TriFault Detect technology. This feature monitors FBPFC for certain PFC fault conditions.

In the case of a feedback path failure, the output of the PFC could exceed operating limits. Should FBPFC go too low, or too high, or open; TriFault Detect senses the error and terminates the PFC output drive.

TriFault detect is an entirely internal circuit. It requires no external components to serve its protective function.

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3

### **PFC Soft-Start Function**

The FAN6982 PFC soft-start function is shown in Figure 30. When bulk voltage is under the 96% of setting voltage;  $V_{EA}$  clamps to 2.8V, the output current of multiplier cuts half, the rectifier line current is limited by current loop, and PFC output rise time increases.

When bulk voltage is over 96%, the clamping function is disabled, and the bulk voltage can be regulated by voltage error amplifier.

There have two advantages with PFC soft-start: one is the MOSFET experience of current is reduced, which can obtain more de-rating with MOSFET current level. The other one is to reduce the overshoot of PFC bulk voltage at the rising time because the charge current becomes small, the bulk voltage can not exceed to setting voltage easily.

| - AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA |

|----------------------------------------|

| 96% V <sub>Bulk</sub>                  |

| VEA.2.8V                               |

Figure 30. PFC Soft-Start

# **RDY Function**

The FAN6982 RDY function, is shown in Figure 31, is controlled by voltage of FBPFC. If the voltage of FBPFC is over than 96% of 2.5V, the RDY pin is connected to SGND. If the FBPFC is under the 46% of 2.5V, the RDY appears open-drain situation. Usually the capacitor is parallel with the RDY pin to prevent the layout noise.

The PNP transistor can control the AHB LLC or dualforward controller on the same side or the "op-to" to control the LLC controller on the other side.

Figure 31. RDY Application Circuit

Downloaded from Elcodis.com electronic components distributor

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

### PRODUCT STATUS DEFINITIONS

### Definition of Terms

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in<br>any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes<br>at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

|                          |                       | Rev. 149                                                                                                                                                                                               |

© 2009 Fairchild Semiconductor Corporation FAN6982 • Rev. 1.0.3 www.fairchildsemi.com