#### **Features**

- High Performance, Low Power 32-bit AVR® Microcontroller

- Compact Single-cycle RISC Instruction Set Including DSP Instruction Set

- Built-in Floating-Point Processing Unit (FPU)

- Read-Modify-Write Instructions and Atomic Bit Manipulation

- Performing 1.49 DMIPS / MHz

- Up to 68 DMIPS Running at 50 MHz from Flash (1 Wait-State)

- Up to 37 DMIPS Running at 25 MHz from Flash (0 Wait-State)

- Memory Protection Unit

- Multi-hierarchy Bus System

- High-Performance Data Transfers on Separate Buses for Increased Performance

- 16 Peripheral DMA Channels Improves Speed for Peripheral Communication

- Internal High-Speed Flash

- 512 Kbytes, 256 Kbytes, 128 Kbytes, 64 Kbytes Versions

- Single Cycle Access up to 25 MHz

- FlashVault<sup>™</sup> Technology Allows Pre-programmed Secure Library Support for End User Applications

- Prefetch Buffer Optimizing Instruction Execution at Maximum Speed

- 10,000 Write Cycles, 15-year Data Retention Capability

- Flash Security Locks and User Defined Configuration Area

- Internal High-Speed SRAM, Single-Cycle Access at Full Speed

- 64 Kbytes (512 KB and 256 KB Flash), 32 Kbytes (128 KB Flash), 16 Kbytes (64 KB Flash)

- 4 Kbytes on the Multi-Layer Bus System (HSB RAM)

- External Memory Interface on AT32UC3C0 Derivatives

- SDRAM / SRAM Compatible Memory Bus (16-bit Data and 24-bit Address Buses)

- Interrupt Controller

- Autovectored Low Latency Interrupt Service with Programmable Priority

- System Functions

- Power and Clock Manager

- Internal 115KHz (RCSYS) and 8MHz/1MHz (RC8M) RC Oscillators

- One 32 KHz and Two Multipurpose Oscillators

- Clock Failure detection

- Two Phase-Lock-Loop (PLL) allowing Independent CPU Frequency from USB or CAN Frequency

- Windowed Watchdog Timer (WDT)

- . Asynchronous Timer (AST) with Real-Time Clock Capability

- Counter or Calendar Mode Supported

- Frequency Meter (FREQM) for Accurate Measuring of Clock Frequency

- Ethernet MAC 10/100 Mbps interface

- 802.3 Ethernet Media Access Controller

- Supports Media Independent Interface (MII) and Reduced MII (RMII)

- Universal Serial Bus (USB)

- Device 2.0 and Embedded Host Low Speed and Full Speed

- Flexible End-Point Configuration and Management with Dedicated DMA Channels

- On-chip Transceivers Including Pull-Ups

- One 2-channel Controller Area Network (CAN)

- CAN2A and CAN2B protocol compliant, with high-level mailbox system

- Two independent channels, 16 Message Objects per Channel

# 32-bit AVR® Microcontroller

AT32UC3C0512C AT32UC3C1512C AT32UC3C2512C

**Automotive**

Summary

**NOTE:** This is a summary document. The complete document is available on the Atmel website at www.atmel.com.

9166BS-AVR-02/11

- One 4-Channel 20-bit Pulse Width Modulation Controller (PWM)

- Complementary outputs, with Dead Time Insertion

- Output Override and Fault Protection

- Two Quadrature Decoders

- One 16-channel 12-bit Pipelined Analog-To-Digital Converter (ADC)

- Dual Sample and Hold Capability Allowing 2 Synchronous Conversions

- Single-Ended and Differential Channels, Window Function

- Two 12-bit Digital-To-Analog Converters (DAC), with Dual Output Sample System

- Four Analog Comparators

- Six 16-bit Timer/Counter (TC) Channels

- External Clock Inputs, PWM, Capture and Various Counting Capabilities

- One Peripheral Event Controller

- Trigger Actions in Peripherals Depending on Events Generated from Peripherals or from Input Pins

- Deterministic Trigger

- 34 Events and 22 Event Actions

- Five Universal Synchronous/Asynchronous Receiver/Transmitters (USART)

- Independent Baudrate Generator, Support for SPI, LIN, IrDA and ISO7816 interfaces

- Support for Hardware Handshaking, RS485 Interfaces and Modem Line

- Two Master/Slave Serial Peripheral Interfaces (SPI) with Chip Select Signals

- One Inter-IC Sound (I2S) Controller

- Compliant with I2S Bus Specification

- Time Division Multiplexed mode

- Three Master and Three Slave Two-Wire Interfaces (TWI), 400 kbit/s I<sup>2</sup>C-compatible

- QTouch<sup>®</sup> Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch<sup>®</sup> and QMatrix<sup>®</sup> Acquisition

- On-Chip Non-intrusive Debug System

- Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

- aWire<sup>™</sup> single-pin programming trace and debug interface muxed with reset pin

- NanoTrace<sup>™</sup> provides trace capabilities through JTAG or aWire interface

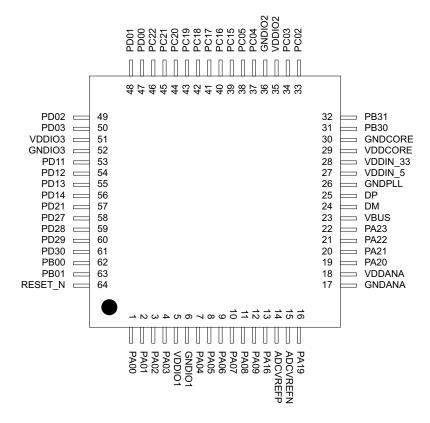

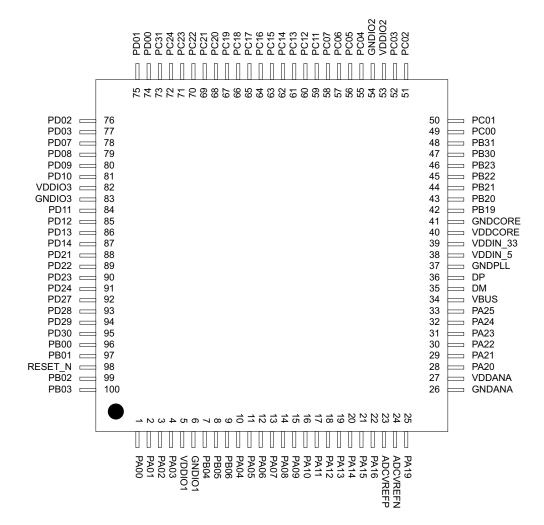

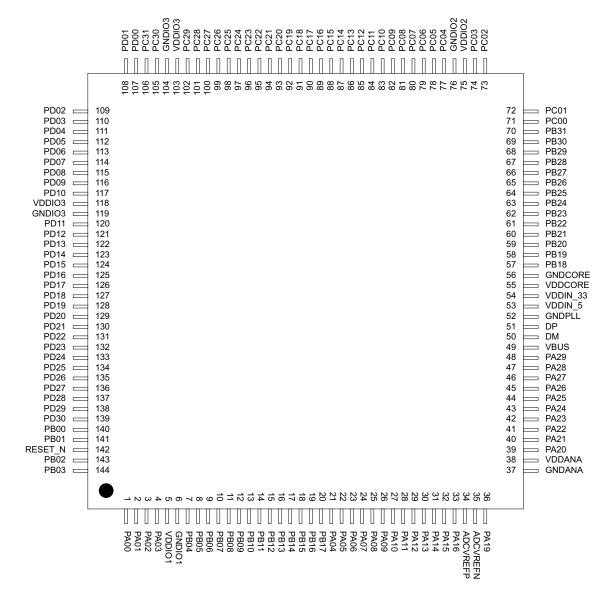

- · 3 package options

- 64-pin QFN/TQFP (45 GPIO pins)

- 100-pin TQFP (81 GPIO pins)

- 144-pin LQFP (123 GPIO pins)

- · Two operating voltage ranges:

- Single 5V Power Supply

- Single 3.3V Power Supply

# 1. Description

The AT32UC3C is a complete System-On-Chip microcontroller based on the AVR32UC RISC processor running at frequencies up to 50 MHz. AVR32UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Using the Secure Access Unit (SAU) together with the MPU provides the required security and integrity.

Higher computation capabilities are achievable either using a rich set of DSP instructions or using the floating-point instructions.

The AT32UC3C incorporates on-chip Flash and SRAM memories for secure and fast access. For applications requiring additional memory, an external memory interface is provided on AT32UC3C0 derivatives.

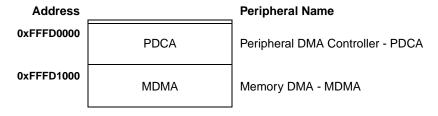

The Memory Direct Memory Access controller (MDMA) enables transfers of block of data from memories to memories without processor involvement.

The Peripheral Direct Memory Access (PDCA) controller enables data transfers between peripherals and memories without processor involvement. The PDCA drastically reduces processing overhead when transferring continuous and large data streams.

The AT32UC3C incorporates on-chip Flash and SRAM memories for secure and fast access. The FlashVault technology allows secure libraries to be programmed into the device. The secure libraries can be executed while the CPU is in Secure State, but not read by non-secure software in the device. The device can thus be shipped to end custumers, who are able to program their own code into the device, accessing the secure libraries, without any risk of compromising the proprietary secure code.

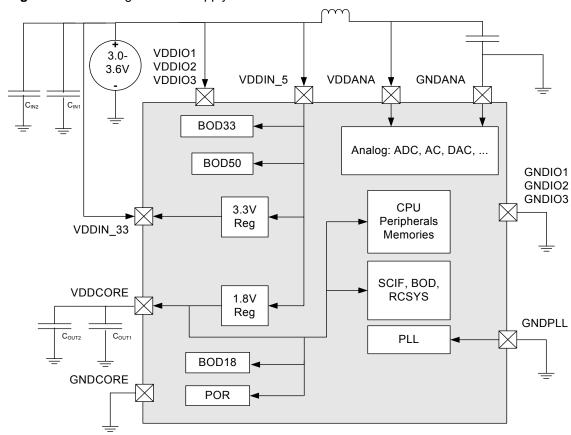

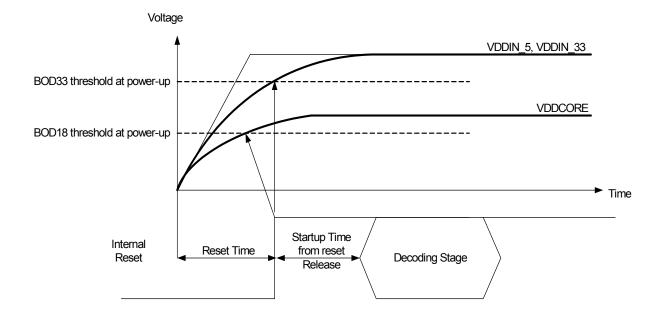

The Power Manager improves design flexibility and security. Power monitoring is supported by on-chip Power-On Reset (POR), Brown-Out Detectors (BOD18, BOD33, BOD50). The CPU runs from the on-chip RC oscillators, the PLLs, or the Multipurpose Oscillators. The Asynchronous Timer (AST) combined with the 32 KHz oscillator keeps track of the time. The AST can operate in counter or calendar mode.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The PWM module provides four channels with many configuration options including polarity, edge alignment and waveform non overlap control. The PWM channels can operate independently, with duty cycles set independently from each other, or in interlinked mode, with multiple channels updated at the same time. It also includes safety feature with fault inputs and the ability to lock the PWM configuration registers and the PWM pin assignment.

The AT32UC3C also features many communication interfaces for communication intensive applications. In addition to standard serial interfaces like UART, SPI or TWI, other interfaces like flexible CAN, USB and Ethernet MAC are available. The USART supports different communication modes, like SPI mode and LIN mode.

The Inter-IC Sound Controller (I2SC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with off-chip audio devices. The controller is compliant with the I2S bus specification.

The Full-Speed USB 2.0 Device interface supports several USB Classes at the same time thanks to the rich End-Point configuration. The On-The-GO (OTG) Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor.

The media-independent interface (MII) and reduced MII (RMII) 10/100 Ethernet MAC module provides on-chip solutions for network-connected devices.

The Peripheral Event Controller (PEVC) allows to redirect events from one peripheral or from input pins to another peripheral. It can then trigger, in a deterministic time, an action inside a peripheral without the need of CPU. For instance a PWM waveform can directly trigger an ADC capture, hence avoiding delays due to software interrupt processing.

The AT32UC3C features analog functions like ADC, DAC, Analog comparators. The ADC interface is built around a 12-bit pipelined ADC core and is able to control two independent 8-channel or one 16-channel. The ADC block is able to measure two different voltages sampled at the same time. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch library for embedding capacitive touch buttons, sliders, and wheels functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and included fully debounced reporting of touch keys and includes Adjacent Key Suppression® (AKS®) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

AT32UC3C integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control. The Nanotrace interface enables trace feature for aWire- or JTAG-based debuggers. The single-pin aWire interface allows all features available through the JTAG interface to be accessed through the RESET pin, allowing the JTAG pins to be used for GPIO or peripherals.

#### 1.1 Disclaimer

Typical values contained in this data sheet are based on simulations and characterization of other 32-bit AVR Microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

#### 1.2 Automotive Quality Grade

The AT32UC3C have been developed and manufactured according to the most stringent requirements of the international standard ISO-TS 16949. This data sheet contains limit values extracted from the results of extensive characterization (Temperature and Voltage). The quality and reliability of the AT32UC3C have been verified during regular product qualification as per AEC-Q100 grade 1.

As indicated in the ordering information paragraph, the product is available in only one temperature grade, Table 1-1.

**Table 1-1.** Temperature Grade Identification for Automotive Products

| Temperature(°C) | Temperature Identifier | Comments                          |

|-----------------|------------------------|-----------------------------------|

| -40;+125        | Z                      | Full Automotive Temperature Range |

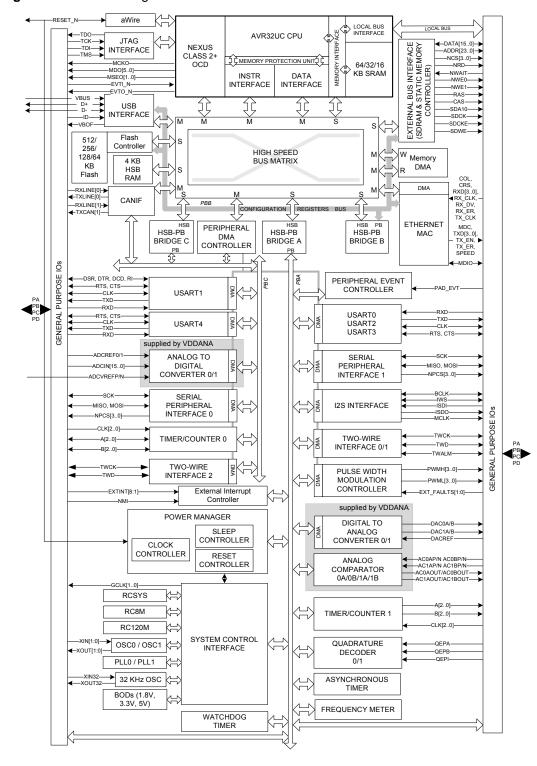

## 2. Overview

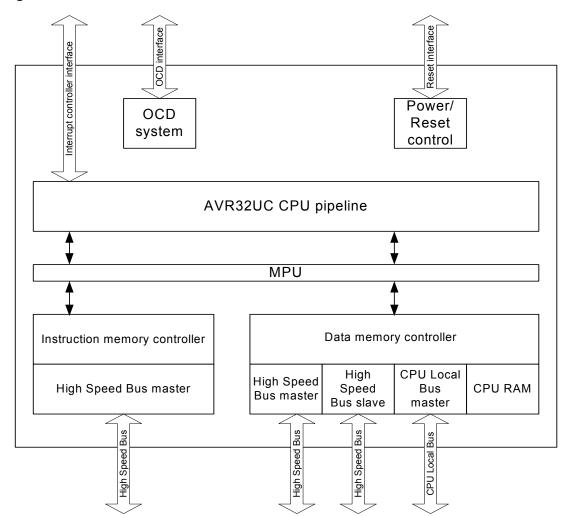

## 2.1 Block diagram

Figure 2-1. Block diagram

# 2.2 Configuration Summary

Table 2-1.

Configuration Summary

| Feature                 | AT32UC3C0512C                                                                                                                                                                              | AT32UC3C1512C | AT32UC3C2512C |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--|--|

| Flash                   | 512 KB                                                                                                                                                                                     | 512 KB        | 512 KB        |  |  |

| SRAM                    | 64KB                                                                                                                                                                                       | 64KB          | 64KB          |  |  |

| HSB RAM                 |                                                                                                                                                                                            | 4 KB          |               |  |  |

| EBI                     | 1                                                                                                                                                                                          | 0             | 0             |  |  |

| GPIO                    | 123                                                                                                                                                                                        | 81            | 45            |  |  |

| External Interrupts     | 8                                                                                                                                                                                          | 8             | 8             |  |  |

| TWI                     | 3                                                                                                                                                                                          | 3             | 2             |  |  |

| USART                   | 5                                                                                                                                                                                          | 5             | 4             |  |  |

| Peripheral DMA Channels | 16                                                                                                                                                                                         | 16            | 16            |  |  |

| Peripheral Event System | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| SPI                     | 2                                                                                                                                                                                          | 2             | 1             |  |  |

| CAN channels            | 2                                                                                                                                                                                          | 2             | 2             |  |  |

| USB                     | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| Ethernet MAC 10/100     | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| Lillethet MAC 10/100    | RMII/MII                                                                                                                                                                                   | RMII/MII      | MII only      |  |  |

| I2S                     | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| Asynchronous Timers     | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| Timer/Counter Channels  | 6                                                                                                                                                                                          | 6             | 3             |  |  |

| PWM channels            |                                                                                                                                                                                            | 4x2           |               |  |  |

| QDEC                    | 2                                                                                                                                                                                          | 2             | 1             |  |  |

| Frequency Meter         |                                                                                                                                                                                            | 1             |               |  |  |

| Watchdog Timer          |                                                                                                                                                                                            | 1             |               |  |  |

| Power Manager           |                                                                                                                                                                                            | 1             |               |  |  |

| Oscillators             | PLL 80-240 MHz (PLL0/PLL1) Crystal Oscillator 0.4-20 MHz (OSC0) Crystal Oscillator 32 KHz (OSC32K) RC Oscillator 115 kHz (RCSYS) RC Oscillator 8 MHz (RC8M) RC Oscillator 120 MHz (RC120M) |               |               |  |  |

|                         | 0.4-20 M                                                                                                                                                                                   | Hz (OSC1)     | -             |  |  |

| 12-bit ADC              | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| number of channels      | 16                                                                                                                                                                                         | 16            | 11            |  |  |

| 12-bit DAC              | 1                                                                                                                                                                                          | 1             | 1             |  |  |

| number of channels      | 4                                                                                                                                                                                          | 4             | 2             |  |  |

| Analog Comparators      | 4 4 2                                                                                                                                                                                      |               |               |  |  |

| JTAG                    |                                                                                                                                                                                            | 1             |               |  |  |

Table 2-1.

Configuration Summary

| Feature       | AT32UC3C0512C | AT32UC3C1512C | AT32UC3C2512C |

|---------------|---------------|---------------|---------------|

| aWire         |               | 1             |               |

| Max Frequency |               | 50 MHz        |               |

| Package       | LQFP144       | TQFP100       | TQFP64/QFN64  |

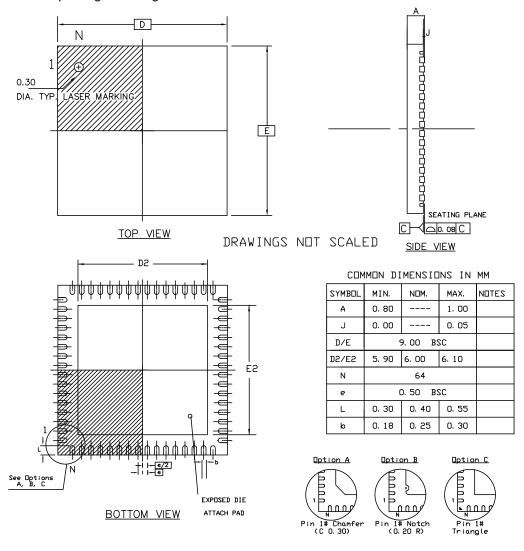

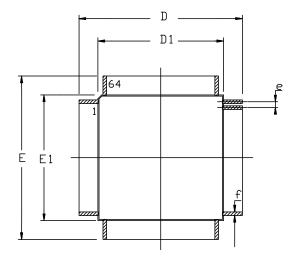

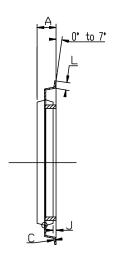

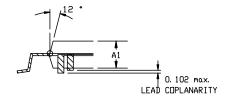

# 3. Package and Pinout

## 3.1 Package

The device pins are multiplexed with peripheral functions as described in Table 3-1 on page 11.

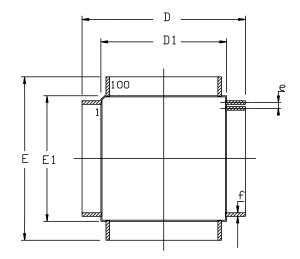

Figure 3-1. QFN64/TQFP64 Pinout

Note: on QFN packages, the exposed pad is unconnected.

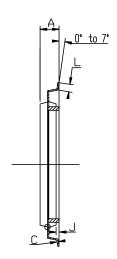

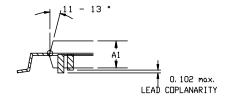

Figure 3-2. TQFP100 Pinout

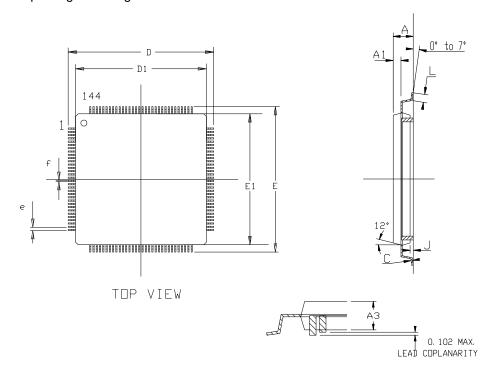

Figure 3-3. LQFP144 Pinout

# 3.2 Peripheral Multiplexing on I/O lines

# 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following table describes the peripheral signals multiplexed to the GPIO lines.

Table 3-1.

GPIO Controller Function Multiplexing

| TQFP           |             |             |             | G           |        |             |                   |                      | GPIO fu                   | ınction |   |   |

|----------------|-------------|-------------|-------------|-------------|--------|-------------|-------------------|----------------------|---------------------------|---------|---|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN         | P<br>I<br>O | Supply | Pin<br>Type | A                 | В                    | С                         | D       | E | F |

| 1              | 1           | 1           | PA00        | 0           | VDDIO1 | x1/x2       |                   | CANIF -<br>TXLINE[1] |                           |         |   |   |

| 2              | 2           | 2           | PA01        | 1           | VDDIO1 | x1/x2       |                   | CANIF -<br>RXLINE[1] | PEVC -<br>PAD_EVT<br>[0]  |         |   |   |

| 3              | 3           | 3           | PA02        | 2           | VDDIO1 | x1/x2       | SCIF -<br>GCLK[0] |                      | PEVC -<br>PAD_EVT<br>[1]  |         |   |   |

| 4              | 4           | 4           | PA03        | 3           | VDDIO1 | x1/x2       | SCIF -<br>GCLK[1] | EIC -<br>EXTINT[1]   |                           |         |   |   |

| 7              | 10          | 21          | PA04        | 4           | VDDANA | x1/x2       | ADCIN0            | USBC - ID            | ACIFA0 -<br>ACAOUT        |         |   |   |

| 8              | 11          | 22          | PA05        | 5           | VDDANA | x1/x2       | ADCIN1            | USBC -<br>VBOF       | ACIFA0 -<br>ACBOUT        |         |   |   |

| 9              | 12          | 23          | PA06        | 6           | VDDANA | x1/x2       | ADCIN2            | AC1AP1               | PEVC -<br>PAD_EVT<br>[2]  |         |   |   |

| 10             | 13          | 24          | PA07        | 7           | VDDANA | x1/x2       | ADCIN3            | AC1AN1               | PEVC -<br>PAD_EVT<br>[3]  |         |   |   |

| 11             | 14          | 25          | PA08        | 8           | VDDANA | x1/x2       | ADCIN4            | AC1BP1               | EIC -<br>EXTINT[2]        |         |   |   |

| 12             | 15          | 26          | PA09        | 9           | VDDANA | x1/x2       | ADCIN5            | AC1BN1               |                           |         |   |   |

|                | 16          | 27          | PA10        | 10          | VDDANA | x1/x2       | ADCIN6            | EIC -<br>EXTINT[4]   | PEVC -<br>PAD_EVT<br>[13] |         |   |   |

|                | 17          | 28          | PA11        | 11          | VDDANA | x1/x2       | ADCIN7            | ADCREF1              | PEVC -<br>PAD_EVT<br>[14] |         |   |   |

|                | 18          | 29          | PA12        | 12          | VDDANA | x1/x2       | AC1AP0            | SPI0 -<br>NPCS[0]    | AC1AP0 or<br>DAC1A        |         |   |   |

|                | 19          | 30          | PA13        | 13          | VDDANA | x1/x2       | AC1AN0            | SPI0 -<br>NPCS[1]    | ADCIN15                   |         |   |   |

|                | 20          | 31          | PA14        | 14          | VDDANA | x1/x2       | AC1BP0            | SPI1 -<br>NPCS[0]    |                           |         |   |   |

|                | 21          | 32          | PA15        | 15          | VDDANA | x1/x2       | AC1BN0            | SPI1 -<br>NPCS[1]    | AC1BN0 or<br>DAC1B        |         |   |   |

| 13             | 22          | 33          | PA16        | 16          | VDDANA | x1/x2       | ADCREF0           |                      | DACREF                    |         |   |   |

| 14             | 23          | 34          | ADC<br>REFP |             |        |             |                   |                      |                           |         |   |   |

| 15             | 24          | 35          | ADC<br>REFN |             |        |             |                   |                      |                           |         |   |   |

Table 3-1.

GPIO Controller Function Multiplexing

| TQFP           |             |             |      | G           |        | ·           |                   |                          | GPIO fu                   | ınction                   |                  |   |

|----------------|-------------|-------------|------|-------------|--------|-------------|-------------------|--------------------------|---------------------------|---------------------------|------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P<br>I<br>O | Supply | Pin<br>Type | A                 | В                        | С                         | D                         | E                | F |

| 16             | 25          | 36          | PA19 | 19          | VDDANA | x1/x2       | ADCIN8            | EIC -<br>EXTINT[1]       |                           |                           |                  |   |

| 19             | 28          | 39          | PA20 | 20          | VDDANA | x1/x2       | ADCIN9            | AC0AP0                   | AC0AP0 or<br>DAC0A        |                           |                  |   |

| 20             | 29          | 40          | PA21 | 21          | VDDANA | x1/x2       | ADCIN10           | AC0BN0                   | AC0BN0 or<br>DAC0B        |                           |                  |   |

| 21             | 30          | 41          | PA22 | 22          | VDDANA | x1/x2       | ADCIN11           | AC0AN0                   | PEVC -<br>PAD_EVT<br>[4]  |                           | MACB -<br>SPEED  |   |

| 22             | 31          | 42          | PA23 | 23          | VDDANA | x1/x2       | ADCIN12           | AC0BP0                   | PEVC -<br>PAD_EVT<br>[5]  |                           | MACB -<br>WOL    |   |

|                | 32          | 43          | PA24 | 24          | VDDANA | x1/x2       | ADCIN13           | SPI1 -<br>NPCS[2]        |                           |                           |                  |   |

|                | 33          | 44          | PA25 | 25          | VDDANA | x1/x2       | ADCIN14           | SPI1 -<br>NPCS[3]        | EIC -<br>EXTINT[0]        |                           |                  |   |

|                |             | 45          | PA26 | 26          | VDDANA | x1/x2       | AC0AP1            | EIC -<br>EXTINT[1]       |                           |                           |                  |   |

|                |             | 46          | PA27 | 27          | VDDANA | x1/x2       | AC0AN1            | EIC -<br>EXTINT[2]       |                           |                           |                  |   |

|                |             | 47          | PA28 | 28          | VDDANA | x1/x2       | AC0BP1            | EIC -<br>EXTINT[3]       |                           |                           |                  |   |

|                |             | 48          | PA29 | 29          | VDDANA | x1/x2       | AC0BN1            | EIC -<br>EXTINT[0]       |                           |                           |                  |   |

| 62             | 96          | 140         | PB00 | 32          | VDDIO1 | x1          | USART0 -<br>CLK   | CANIF -<br>RXLINE[1]     | EIC -<br>EXTINT[8]        | PEVC -<br>PAD_EVT<br>[10] |                  |   |

| 63             | 97          | 141         | PB01 | 33          | VDDIO1 | x1          |                   | CANIF -<br>TXLINE[1]     |                           | PEVC -<br>PAD_EVT<br>[11] |                  |   |

|                | 99          | 143         | PB02 | 34          | VDDIO1 | x1          |                   | USBC - ID                | PEVC -<br>PAD_EVT<br>[6]  | TC1 - A1                  |                  |   |

|                | 100         | 144         | PB03 | 35          | VDDIO1 | x1          |                   | USBC -<br>VBOF           | PEVC -<br>PAD_EVT<br>[7]  |                           |                  |   |

|                | 7           | 7           | PB04 | 36          | VDDIO1 | x1/x2       | SPI1 -<br>MOSI    | CANIF -<br>RXLINE[0]     | QDEC1 -<br>QEPI           |                           | MACB -<br>TXD[2] |   |

|                | 8           | 8           | PB05 | 37          | VDDIO1 | x1/x2       | SPI1 -<br>MISO    | CANIF -<br>TXLINE[0]     | PEVC -<br>PAD_EVT<br>[12] | USART3 -<br>CLK           | MACB -<br>TXD[3] |   |

|                | 9           | 9           | PB06 | 38          | VDDIO1 | x2/x4       | SPI1 -<br>SCK     |                          | QDEC1 -<br>QEPA           | USART1 -<br>CLK           | MACB -<br>TX_ER  |   |

|                |             | 10          | PB07 | 39          | VDDIO1 | x1/x2       | SPI1 -<br>NPCS[0] | EIC -<br>EXTINT[2]       | QDEC1 -<br>QEPB           |                           | MACB -<br>RX_DV  |   |

|                |             | 11          | PB08 | 40          | VDDIO1 | x1/x2       | SPI1 -<br>NPCS[1] | PEVC -<br>PAD_EVT<br>[1] | PWM -<br>PWML[0]          |                           | MACB -<br>RXD[0] |   |

|                |             | 12          | PB09 | 41          | VDDIO1 | x1/x2       | SPI1 -<br>NPCS[2] |                          | PWM -<br>PWMH[0]          |                           | MACB -<br>RXD[1] |   |

|                |             | 13          | PB10 | 42          | VDDIO1 | x1/x2       | USART1 -<br>DTR   | SPIO -<br>MOSI           | PWM -<br>PWML[1]          |                           |                  |   |

Table 3-1.

GPIO Controller Function Multiplexing

| TQFP           |             |             |      | G           |        |             |                 |                   | GPIO fu                    | ınction            |                      |   |

|----------------|-------------|-------------|------|-------------|--------|-------------|-----------------|-------------------|----------------------------|--------------------|----------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P<br>I<br>O | Supply | Pin<br>Type | A               | В                 | С                          | D                  | E                    | F |

|                |             | 14          | PB11 | 43          | VDDIO1 | x1/x2       | USART1 -<br>DSR | SPI0 -<br>MISO    | PWM -<br>PWMH[1]           |                    | _                    | - |

|                |             | 15          | PB12 | 44          | VDDIO1 | x1/x2       | USART1 -<br>DCD | SPI0 -<br>SCK     | PWM -<br>PWML[2]           |                    |                      |   |

|                |             | 16          | PB13 | 45          | VDDIO1 | x1/x2       | USART1 -<br>RI  | SPI0 -<br>NPCS[0] | PWM -<br>PWMH[2]           |                    | MACB -<br>RX_ER      |   |

|                |             | 17          | PB14 | 46          | VDDIO1 | x1/x2       | USART1 -<br>RTS | SPI0 -<br>NPCS[1] | PWM -<br>PWML[3]           |                    | MACB -<br>MDC        |   |

|                |             | 18          | PB15 | 47          | VDDIO1 | x1/x2       | USART1 -<br>CTS | USART1 -<br>CLK   | PWM -<br>PWMH[3]           |                    | MACB -<br>MDIO       |   |

|                |             | 19          | PB16 | 48          | VDDIO1 | x1/x2       | USART1 -<br>RXD | SPI0 -<br>NPCS[2] | PWM -<br>EXT_<br>FAULTS[0] |                    | CANIF -<br>RXLINE[0] |   |

|                |             | 20          | PB17 | 49          | VDDIO1 | x1/x2       | USART1 -<br>TXD | SPI0 -<br>NPCS[3] | PWM -<br>EXT_<br>FAULTS[1] |                    | CANIF -<br>TXLINE[0] |   |

|                |             | 57          | PB18 | 50          | VDDIO2 | x1/x2       | TC0 -<br>CLK2   |                   | EIC -<br>EXTINT[4]         |                    |                      |   |

|                | 42          | 58          | PB19 | 51          | VDDIO2 | x1/x2       | TC0 - A0        | SPI1 -<br>MOSI    | IISC -<br>ISDO             |                    | MACB -<br>CRS        |   |

|                | 43          | 59          | PB20 | 52          | VDDIO2 | x1/x2       | TC0 - B0        | SPI1 -<br>MISO    | IISC - ISDI                | ACIFA1 -<br>ACAOUT | MACB -<br>COL        |   |

|                | 44          | 60          | PB21 | 53          | VDDIO2 | x2/x4       | TC0 -<br>CLK1   | SPI1 -<br>SCK     | IISC -<br>IMCK             | ACIFA1 -<br>ACBOUT | MACB -<br>RXD[2]     |   |

|                | 45          | 61          | PB22 | 54          | VDDIO2 | x1/x2       | TC0 - A1        | SPI1 -<br>NPCS[3] | IISC -<br>ISCK             | SCIF -<br>GCLK[0]  | MACB -<br>RXD[3]     |   |

|                | 46          | 62          | PB23 | 55          | VDDIO2 | x1/x2       | TC0 - B1        | SPI1 -<br>NPCS[2] | IISC - IWS                 | SCIF -<br>GCLK[1]  | MACB -<br>RX_CLK     |   |

|                |             | 63          | PB24 | 56          | VDDIO2 | x1/x2       | TC0 -<br>CLK0   | SPI1 -<br>NPCS[1] |                            |                    |                      |   |

|                |             | 64          | PB25 | 57          | VDDIO2 | x1/x2       | TC0 - A2        | SPI1 -<br>NPCS[0] | PEVC -<br>PAD_EVT<br>[8]   |                    |                      |   |

|                |             | 65          | PB26 | 58          | VDDIO2 | x2/x4       | TC0 - B2        | SPI1 -<br>SCK     | PEVC -<br>PAD_EVT<br>[9]   |                    | MACB -<br>TX_EN      |   |

|                |             | 66          | PB27 | 59          | VDDIO2 | x1/x2       | QDEC0 -<br>QEPA | SPI1 -<br>MISO    | PEVC -<br>PAD_EVT<br>[10]  | TC1 -<br>CLK0      | MACB -<br>TXD[0]     |   |

|                |             | 67          | PB28 | 60          | VDDIO2 | x1/x2       | QDEC0 -<br>QEPB | SPI1 -<br>MOSI    | PEVC -<br>PAD_EVT<br>[11]  | TC1 - B0           | MACB -<br>TXD[1]     |   |

|                |             | 68          | PB29 | 61          | VDDIO2 | x1/x2       | QDEC0 -<br>QEPI | SPI0 -<br>NPCS[0] | PEVC -<br>PAD_EVT<br>[12]  | TC1 - A0           |                      |   |

| 31             | 47          | 69          | PB30 | 62          | VDDIO2 | x1          |                 |                   |                            |                    |                      |   |

| 32             | 48          | 70          | PB31 | 63          | VDDIO2 | x1          |                 |                   |                            |                    |                      |   |

|                | 49          | 71          | PC00 | 64          | VDDIO2 | x1/x2       | USBC - ID       | SPI0 -<br>NPCS[1] | USART2 -<br>CTS            | TC1 - B2           | CANIF -<br>TXLINE[1] |   |

|                | 50          | 72          | PC01 | 65          | VDDIO2 | x1/x2       | USBC -<br>VBOF  | SPI0 -<br>NPCS[2] | USART2 -<br>RTS            | TC1 - A2           | CANIF -<br>RXLINE[1] |   |

Table 3-1.

GPIO Controller Function Multiplexing

| TQFP           |             |             |      | G     |        |             |                            |                      | GPIO fu           | unction                  |                      |                   |

|----------------|-------------|-------------|------|-------|--------|-------------|----------------------------|----------------------|-------------------|--------------------------|----------------------|-------------------|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P I O | Supply | Pin<br>Type | A                          | В                    | С                 | D                        | E                    | F                 |

| 33             | 51          | 73          | PC02 | 66    | VDDIO2 | x1          | TWIMS0 -<br>TWD            | SPI0 -<br>NPCS[3]    | USART2 -<br>RXD   | TC1 -<br>CLK1            | MACB -<br>MDC        |                   |

| 34             | 52          | 74          | PC03 | 67    | VDDIO2 | x1          | TWIMS0 -<br>TWCK           | EIC -<br>EXTINT[1]   | USART2 -<br>TXD   | TC1 - B1                 | MACB -<br>MDIO       |                   |

| 37             | 55          | 77          | PC04 | 68    | VDDIO2 | x1          | TWIMS1 -<br>TWD            | EIC -<br>EXTINT[3]   | USART2 -<br>TXD   | TC0 - B1                 |                      |                   |

| 38             | 56          | 78          | PC05 | 69    | VDDIO2 | x1          | TWIMS1 -<br>TWCK           | EIC -<br>EXTINT[4]   | USART2 -<br>RXD   | TC0 - A2                 |                      |                   |

|                | 57          | 79          | PC06 | 70    | VDDIO2 | x1          | PEVC -<br>PAD_EVT<br>[15]  | USART2 -<br>CLK      | USART2 -<br>CTS   | TC0 -<br>CLK2            | TWIMS2 -<br>TWD      | TWIMS0 -<br>TWALM |

|                | 58          | 80          | PC07 | 71    | VDDIO2 | x1          | PEVC -<br>PAD_EVT<br>[2]   | EBI -<br>NCS[3]      | USART2 -<br>RTS   | TC0 - B2                 | TWIMS2 -<br>TWCK     | TWIMS1 -<br>TWALM |

|                |             | 81          | PC08 | 72    | VDDIO2 | x1/x2       | PEVC -<br>PAD_EVT<br>[13]  | SPI1 -<br>NPCS[1]    | EBI -<br>NCS[0]   |                          | USART4 -<br>TXD      |                   |

|                |             | 82          | PC09 | 73    | VDDIO2 | x1/x2       | PEVC -<br>PAD_EVT<br>[14]  | SPI1 -<br>NPCS[2]    | EBI -<br>ADDR[23] |                          | USART4 -<br>RXD      |                   |

|                |             | 83          | PC10 | 74    | VDDIO2 | x1/x2       | PEVC -<br>PAD_EVT<br>[15]  | SPI1 -<br>NPCS[3]    | EBI -<br>ADDR[22] |                          |                      |                   |

|                | 59          | 84          | PC11 | 75    | VDDIO2 | x1/x2       | PWM -<br>PWMH[3]           | CANIF -<br>RXLINE[1] | EBI -<br>ADDR[21] | TC0 -<br>CLK0            |                      |                   |

|                | 60          | 85          | PC12 | 76    | VDDIO2 | x1/x2       | PWM -<br>PWML[3]           | CANIF -<br>TXLINE[1] | EBI -<br>ADDR[20] | USART2 -<br>CLK          |                      |                   |

|                | 61          | 86          | PC13 | 77    | VDDIO2 | x1/x2       | PWM -<br>PWMH[2]           | EIC -<br>EXTINT[7]   |                   | USART0 -<br>RTS          |                      |                   |

|                | 62          | 87          | PC14 | 78    | VDDIO2 | x1/x2       | PWM -<br>PWML[2]           | USART0 -<br>CLK      | EBI -<br>SDCKE    | USART0 -<br>CTS          |                      |                   |

| 39             | 63          | 88          | PC15 | 79    | VDDIO2 | x1/x2       | PWM -<br>PWMH[1]           | SPI0 -<br>NPCS[0]    | EBI -<br>SDWE     | USART0 -<br>RXD          | CANIF -<br>RXLINE[1] |                   |

| 40             | 64          | 89          | PC16 | 80    | VDDIO2 | x1/x2       | PWM -<br>PWML[1]           | SPI0 -<br>NPCS[1]    | EBI - CAS         | USART0-<br>TXD           | CANIF -<br>TXLINE[1] |                   |

| 41             | 65          | 90          | PC17 | 81    | VDDIO2 | x1/x2       | PWM -<br>PWMH[0]           | SPIO -<br>NPCS[2]    | EBI - RAS         | IISC -<br>ISDO           |                      | USART3 -<br>TXD   |

| 42             | 66          | 91          | PC18 | 82    | VDDIO2 | x1/x2       | PWM -<br>PWML[0]           | EIC -<br>EXTINT[5]   | EBI -<br>SDA10    | IISC -<br>ISDI           |                      | USART3 -<br>RXD   |

| 43             | 67          | 92          | PC19 | 83    | VDDIO3 | x1/x2       | PWM -<br>PWML[2]           | SCIF -<br>GCLK[0]    | EBI -<br>DATA[0]  | IISC -<br>IMCK           |                      | USART3 -<br>CTS   |

| 44             | 68          | 93          | PC20 | 84    | VDDIO3 | x1/x2       | PWM -<br>PWMH[2]           | SCIF -<br>GCLK[1]    | EBI -<br>DATA[1]  | IISC -<br>ISCK           |                      | USART3 -<br>RTS   |

| 45             | 69          | 94          | PC21 | 85    | VDDIO3 | x1/x2       | PWM -<br>EXT_<br>FAULTS[0] | CANIF -<br>RXLINE[0] | EBI -<br>DATA[2]  | IISC - IWS               |                      |                   |

| 46             | 70          | 95          | PC22 | 86    | VDDIO3 | x1/x2       | PWM -<br>EXT_<br>FAULTS[1] | CANIF -<br>TXLINE[0] | EBI -<br>DATA[3]  |                          | USART3 -<br>CLK      |                   |

|                | 71          | 96          | PC23 | 87    | VDDIO3 | x1/x2       | QDEC1 -<br>QEPB            | CANIF -<br>RXLINE[1] | EBI -<br>DATA[4]  | PEVC -<br>PAD_EVT<br>[3] |                      |                   |

Table 3-1. GPIO Controller Function Multiplexing

| Table 3-  | 3    | 1 10 001 |      |        | ction Mult | ibioviilé | <i>3</i>          |                      | CDIO 4            | ınction                  |                  |   |

|-----------|------|----------|------|--------|------------|-----------|-------------------|----------------------|-------------------|--------------------------|------------------|---|

| IQFP<br>/ |      |          |      | G<br>P |            | Pin       |                   |                      | GPIO fu           | inction                  |                  |   |

| QFN       | TQFP | LQFP     |      | ı      |            | Туре      |                   |                      |                   |                          |                  |   |

| 64        | 100  | 144      | PIN  | 0      | Supply     | (1)       | Α                 | В                    | С                 | D                        | E                | F |

|           | 72   | 97       | PC24 | 88     | VDDIO3     | x1/x2     | QDEC1 -<br>QEPA   | CANIF -<br>TXLINE[1] | EBI -<br>DATA[5]  | PEVC -<br>PAD_EVT<br>[4] |                  |   |

|           |      | 98       | PC25 | 89     | VDDIO3     | x1/x2     |                   | TC1 -<br>CLK2        | EBI -<br>DATA[6]  | SCIF -<br>GCLK[0]        | USART4 -<br>TXD  |   |

|           |      | 99       | PC26 | 90     | VDDIO3     | x1/x2     | QDEC1 -<br>QEPI   | TC1 - B2             | EBI -<br>DATA[7]  | SCIF -<br>GCLK[1]        | USART4 -<br>RXD  |   |

|           |      | 100      | PC27 | 91     | VDDIO3     | x1/x2     |                   | TC1 - A2             | EBI -<br>DATA[8]  | EIC -<br>EXTINT[0]       | USART4 -<br>CTS  |   |

|           |      | 101      | PC28 | 92     | VDDIO3     | x1/x2     | SPI1 -<br>NPCS[3] | TC1 -<br>CLK1        | EBI -<br>DATA[9]  |                          | USART4 -<br>RTS  |   |

|           |      | 102      | PC29 | 93     | VDDIO3     | x1/x2     | SPI0 -<br>NPCS[1] | TC1 - B1             | EBI -<br>DATA[10] |                          |                  |   |

|           |      | 105      | PC30 | 94     | VDDIO3     | x1/x2     | SPI0 -<br>NPCS[2] | TC1 - A1             | EBI -<br>DATA[11] |                          |                  |   |

|           | 73   | 106      | PC31 | 95     | VDDIO3     | x1/x2     | SPIO -<br>NPCS[3] | TC1 - B0             | EBI -<br>DATA[12] | PEVC -<br>PAD_EVT<br>[5] | USART4 -<br>CLK  |   |

| 47        | 74   | 107      | PD00 | 96     | VDDIO3     | x1/x2     | SPI0 -<br>MOSI    | TC1 -<br>CLK0        | EBI -<br>DATA[13] | QDEC0 -<br>QEPI          | USART0 -<br>TXD  |   |

| 48        | 75   | 108      | PD01 | 97     | VDDIO3     | x1/x2     | SPIO -<br>MISO    | TC1 - A0             | EBI -<br>DATA[14] | TC0 -<br>CLK1            | USART0 -<br>RXD  |   |

| 49        | 76   | 109      | PD02 | 98     | VDDIO3     | x2/x4     | SPI0 -<br>SCK     | TC0 -<br>CLK2        | EBI -<br>DATA[15] | QDEC0 -<br>QEPA          |                  |   |

| 50        | 77   | 110      | PD03 | 99     | VDDIO3     | x1/x2     | SPI0 -<br>NPCS[0] | TC0 - B2             | EBI -<br>ADDR[0]  | QDEC0 -<br>QEPB          |                  |   |

|           |      | 111      | PD04 | 100    | VDDIO3     | x1/x2     | SPIO -<br>MOSI    |                      | EBI -<br>ADDR[1]  |                          |                  |   |

|           |      | 112      | PD05 | 101    | VDDIO3     | x1/x2     | SPI0 -<br>MISO    |                      | EBI -<br>ADDR[2]  |                          |                  |   |

|           |      | 113      | PD06 | 102    | VDDIO3     | x2/x4     | SPI0 -<br>SCK     |                      | EBI -<br>ADDR[3]  |                          |                  |   |

|           | 78   | 114      | PD07 | 103    | VDDIO3     | x1/x2     | USART1 -<br>DTR   | EIC -<br>EXTINT[5]   | EBI -<br>ADDR[4]  | QDEC0 -<br>QEPI          | USART4 -<br>TXD  |   |

|           | 79   | 115      | PD08 | 104    | VDDIO3     | x1/x2     | USART1 -<br>DSR   | EIC -<br>EXTINT[6]   | EBI -<br>ADDR[5]  | TC1 -<br>CLK2            | USART4 -<br>RXD  |   |

|           | 80   | 116      | PD09 | 105    | VDDIO3     | x1/x2     | USART1 -<br>DCD   | CANIF -<br>RXLINE[0] | EBI -<br>ADDR[6]  | QDEC0 -<br>QEPA          | USART4 -<br>CTS  |   |

|           | 81   | 117      | PD10 | 106    | VDDIO3     | x1/x2     | USART1 -<br>RI    | CANIF -<br>TXLINE[0] | EBI -<br>ADDR[7]  | QDEC0 -<br>QEPB          | USART4 -<br>RTS  |   |

| 53        | 84   | 120      | PD11 | 107    | VDDIO3     | x1/x2     | USART1 -<br>TXD   | USBC - ID            | EBI -<br>ADDR[8]  | PEVC -<br>PAD_EVT<br>[6] | MACB -<br>TXD[0] |   |

| 54        | 85   | 121      | PD12 | 108    | VDDIO3     | x1/x2     | USART1 -<br>RXD   | USBC -<br>VBOF       | EBI -<br>ADDR[9]  | PEVC -<br>PAD_EVT<br>[7] | MACB -<br>TXD[1] |   |

| 55        | 86   | 122      | PD13 | 109    | VDDIO3     | x2/x4     | USART1 -<br>CTS   | USART1 -<br>CLK      | EBI -<br>SDCK     | PEVC -<br>PAD_EVT<br>[8] | MACB -<br>RXD[0] |   |

| 56        | 87   | 123      | PD14 | 110    | VDDIO3     | x1/x2     | USART1 -<br>RTS   | EIC -<br>EXTINT[7]   | EBI -<br>ADDR[10] | PEVC -<br>PAD_EVT<br>[9] | MACB -<br>RXD[1] |   |

Table 3-1. GPIO Controller Function Multiplexing

| TQFP           |             |             |      | G           |        |             |                 |                      | GPIO fu           | ınction           |                  |   |

|----------------|-------------|-------------|------|-------------|--------|-------------|-----------------|----------------------|-------------------|-------------------|------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P<br>I<br>O | Supply | Pin<br>Type | A               | В                    | С                 | D                 | E                | F |

|                |             | 124         | PD15 | 111         | VDDIO3 | x1/x2       | TC0 - A0        | USART3 -<br>TXD      | EBI -<br>ADDR[11] |                   |                  |   |

|                |             | 125         | PD16 | 112         | VDDIO3 | x1/x2       | TC0 - B0        | USART3 -<br>RXD      | EBI -<br>ADDR[12] |                   |                  |   |

|                |             | 126         | PD17 | 113         | VDDIO3 | x1/x2       | TC0 - A1        | USART3 -<br>CTS      | EBI -<br>ADDR[13] | USART3 -<br>CLK   |                  |   |

|                |             | 127         | PD18 | 114         | VDDIO3 | x1/x2       | TC0 - B1        | USART3 -<br>RTS      | EBI -<br>ADDR[14] |                   |                  |   |

|                |             | 128         | PD19 | 115         | VDDIO3 | x1/x2       | TC0 - A2        |                      | EBI -<br>ADDR[15] |                   |                  |   |

|                |             | 129         | PD20 | 116         | VDDIO3 | x1/x2       | TC0 - B2        |                      | EBI -<br>ADDR[16] |                   |                  |   |

| 57             | 88          | 130         | PD21 | 117         | VDDIO3 | x1/x2       | USART3 -<br>TXD | EIC -<br>EXTINT[0]   | EBI -<br>ADDR[17] | QDEC1 -<br>QEPI   |                  |   |

|                | 89          | 131         | PD22 | 118         | VDDIO1 | x1/x2       | USART3 -<br>RXD | TC0 - A2             | EBI -<br>ADDR[18] | SCIF -<br>GCLK[0] |                  |   |

|                | 90          | 132         | PD23 | 119         | VDDIO1 | x1/x2       | USART3 -<br>CTS | USART3 -<br>CLK      | EBI -<br>ADDR[19] | QDEC1 -<br>QEPA   |                  |   |

|                | 91          | 133         | PD24 | 120         | VDDIO1 | x1/x2       | USART3 -<br>RTS | EIC -<br>EXTINT[8]   | EBI -<br>NWE1     | QDEC1 -<br>QEPB   |                  |   |

|                |             | 134         | PD25 | 121         | VDDIO1 | x1/x2       | TC0 -<br>CLK0   | USBC - ID            | EBI -<br>NWE0     |                   | USART4 -<br>CLK  |   |

|                |             | 135         | PD26 | 122         | VDDIO1 | x1/x2       | TC0 -<br>CLK1   | USBC -<br>VBOF       | EBI - NRD         |                   |                  |   |

| 58             | 92          | 136         | PD27 | 123         | VDDIO1 | x1/x2       | USART0 -<br>TXD | CANIF -<br>RXLINE[0] | EBI -<br>NCS[1]   | TC0 - A0          | MACB -<br>RX_ER  |   |

| 59             | 93          | 137         | PD28 | 124         | VDDIO1 | x1/x2       | USART0 -<br>RXD | CANIF -<br>TXLINE[0] | EBI -<br>NCS[2]   | TC0 - B0          | MACB -<br>RX_DV  |   |

| 60             | 94          | 138         | PD29 | 125         | VDDIO1 | x1/x2       | USART0 -<br>CTS | EIC -<br>EXTINT[6]   | USART0 -<br>CLK   | TC0 -<br>CLK0     | MACB -<br>TX_CLK |   |

| 61             | 95          | 139         | PD30 | 126         | VDDIO1 | x1/x2       | USART0 -<br>RTS | EIC -<br>EXTINT[3]   | EBI -<br>NWAIT    | TC0 - A1          | MACB -<br>TX_EN  |   |

Note:

1. Pin type x1 is pin with drive strength of x1. Pin type x1/x2 is pin with programmable drive strength of x1 or x2. Pin type x2/x4 is pin with programmable drive strength of x2 or x4. The drive strength is programmable through ODCR0, ODCR0S, ODCR0C, ODCR0T registers of GPIO. Refer to "Electrical Characteristics" on page 49 for a description of the electrical properties of the pin types used.

See Section 3.3 for a description of the various peripheral signals.

#### 3.2.2 Peripheral Functions

Each GPIO line can be assigned to one of several peripheral functions. The following table describes how the various peripheral functions are selected. The last listed function has priority in case multiple functions are enabled on the same pin.

Table 3-2. Peripheral Functions

| Function                              | Description                               |

|---------------------------------------|-------------------------------------------|

| GPIO Controller Function multiplexing | GPIO and GPIO peripheral selection A to F |

| Nexus OCD AUX port connections        | OCD trace system                          |

| aWire DATAOUT                         | aWire output in two-pin mode              |

| JTAG port connections                 | JTAG debug port                           |

| Oscillators                           | OSC0, OSC32                               |

#### 3.2.3 Oscillator Pinout

The oscillators are not mapped to the normal GPIO functions and their muxings are controlled by registers in the System Control Interface (SCIF). Please refer to the SCIF chapter for more information about this.

Table 3-3. Oscillator pinout

| QFN64/     |             |             |      |                |

|------------|-------------|-------------|------|----------------|

| TQFP64 pin | TQFP100 pin | LQFP144 pin | Pad  | Oscillator pin |

| 31         | 47          | 69          | PB30 | xin0           |

|            | 99          | 143         | PB02 | xin1           |

| 62         | 96          | 140         | PB00 | xin32          |

| 32         | 48          | 70          | PB31 | xout0          |

|            | 100         | 144         | PB03 | xout1          |

| 63         | 97          | 141         | PB01 | xout32         |

#### 3.2.4 JTAG port connections

If the JTAG is enabled, the JTAG will take control over a number of pins, irrespectively of the I/O Controller configuration.

Table 3-4. JTAG pinout

| QFN64/<br>TQFP64 pin | TQFP100 pin | LQFP144 pin | Pin name | JTAG pin |

|----------------------|-------------|-------------|----------|----------|

| 2                    | 2           | 2           | PA01     | TDI      |

| 3                    | 3           | 3           | PA02     | TDO      |

| 4                    | 4           | 4           | PA03     | TMS      |

| 1                    | 1           | 1           | PA00     | TCK      |

#### 3.2.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the GPIO configuration. Two different OCD trace pin mappings are possible,

depending on the configuration of the OCD AXS register. For details, see the AVR32UC Technical Reference Manual.

Table 3-5.Nexus OCD AUX port connections

| Pin     | AXS=0 | AXS=1 | AXS=2 |

|---------|-------|-------|-------|

| EVTI_N  | PA08  | PB19  | PA10  |

| MDO[5]  | PC05  | PC31  | PB06  |

| MDO[4]  | PC04  | PC12  | PB15  |

| MDO[3]  | PA23  | PC11  | PB14  |

| MDO[2]  | PA22  | PB23  | PA27  |

| MDO[1]  | PA19  | PB22  | PA26  |

| MDO[0]  | PA09  | PB20  | PA19  |

| EVTO_N  | PD29  | PD29  | PD29  |

| МСКО    | PD13  | PB21  | PB26  |

| MSEO[1] | PD30  | PD08  | PB25  |

| MSEO[0] | PD14  | PD07  | PB18  |

#### 3.2.6 Other Functions

The functions listed in Table 3-6 are not mapped to the normal GPIO functions. The aWire DATA pin will only be active after the aWire is enabled. The aWire DATAOUT pin will only be active after the aWire is enabled and the 2\_PIN\_MODE command has been sent.

Table 3-6. Other Functions

| QFN64/<br>TQFP64 pin | TQFP100 pin | LQFP144 pin | Pad     | Oscillator pin |

|----------------------|-------------|-------------|---------|----------------|

| 64                   | 98          | 142         | RESET_N | aWire DATA     |

| 3                    | 3           | 3           | PA02    | aWire DATAOUT  |

# 3.3 Signals Description

The following table give details on the signal name classified by peripherals.

Table 3-7.

Signal Description List

| Signal Name                | Function            | Туре           | Active<br>Level | Comments                            |  |  |  |  |  |

|----------------------------|---------------------|----------------|-----------------|-------------------------------------|--|--|--|--|--|

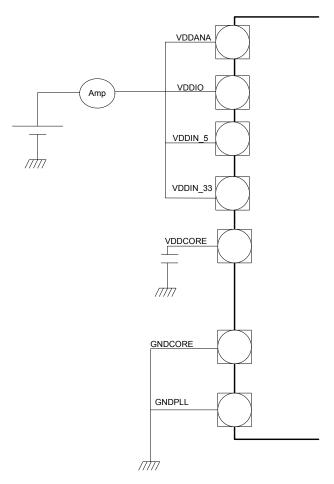

| Power                      |                     |                |                 |                                     |  |  |  |  |  |

| VDDIO1<br>VDDIO2<br>VDDIO3 | I/O Power Supply    | Power<br>Input |                 | 4.5V to 5.5V<br>or<br>3.0V to 3.6 V |  |  |  |  |  |

| VDDANA                     | Analog Power Supply | Power<br>Input |                 | 4.5V to 5.5V<br>or<br>3.0V to 3.6 V |  |  |  |  |  |

Table 3-7.

Signal Description List

| Signal Name                | Function                                                  | Туре                      | Active<br>Level | Comments                                                                           |

|----------------------------|-----------------------------------------------------------|---------------------------|-----------------|------------------------------------------------------------------------------------|

| VDDIN_5                    | 1.8V Voltage Regulator Input                              | Power<br>Input            |                 | Power Supply:<br>4.5V to 5.5V<br>or<br>3.0V to 3.6 V                               |

| VDDIN_33                   | USB I/O power supply                                      | Power<br>Output/<br>Input |                 | Capacitor Connection for the 3.3V voltage regulator or power supply: 3.0V to 3.6 V |

| VDDCORE                    | 1.8V Voltage Regulator Output                             | Power output              |                 | Capacitor Connection for the 1.8V voltage regulator                                |

| GNDIO1<br>GNDIO2<br>GNDIO3 | I/O Ground                                                | Ground                    |                 |                                                                                    |

| GNDANA                     | Analog Ground                                             | Ground                    |                 |                                                                                    |

| GNDCORE                    | Ground of the core                                        | Ground                    |                 |                                                                                    |

| GNDPLL                     | Ground of the PLLs                                        | Ground                    |                 |                                                                                    |

|                            | Analog Comparator Interf                                  | ace - ACIFA               | 0/1             |                                                                                    |

| AC0AN1/AC0AN0              | Negative inputs for comparator AC0A                       | Analog                    |                 |                                                                                    |

| AC0AP1/AC0AP0              | Positive inputs for comparator AC0A                       | Analog                    |                 |                                                                                    |

| AC0BN1/AC0BN0              | Negative inputs for comparator AC0B                       | Analog                    |                 |                                                                                    |

| AC0BP1/AC0BP0              | Positive inputs for comparator AC0B                       | Analog                    |                 |                                                                                    |

| AC1AN1/AC1AN0              | Negative inputs for comparator AC1A                       | Analog                    |                 |                                                                                    |

| AC1AP1/AC1AP0              | Positive inputs for comparator AC1A                       | Analog                    |                 |                                                                                    |

| AC1BN1/AC1BN0              | Negative inputs for comparator AC1B                       | Analog                    |                 |                                                                                    |

| AC1BP1/AC1BP0              | Positive inputs for comparator AC1B                       | Analog                    |                 |                                                                                    |

| ACAOUT/ACBOUT              | analog comparator outputs                                 | output                    |                 |                                                                                    |

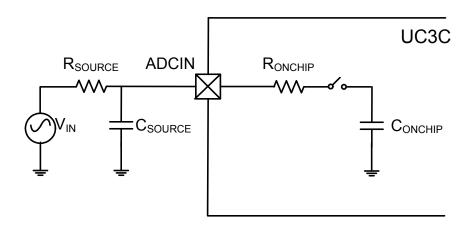

|                            | ADC Interface - A                                         | DCIFA                     | <u> </u>        |                                                                                    |

| ADCIN[15:0]                | ADC input pins                                            | Analog                    |                 |                                                                                    |

| ADCREF0                    | Analog positive reference 0 voltage input                 | Analog                    |                 |                                                                                    |

| ADCREF1                    | Analog positive reference 1 voltage input                 | Analog                    |                 |                                                                                    |

| ADCVREFP                   | Analog positive reference connected to external capacitor | Analog                    |                 |                                                                                    |

Table 3-7.Signal Description List

| Signal Name  | Function                                                  | Туре             | Active<br>Level | Comments |

|--------------|-----------------------------------------------------------|------------------|-----------------|----------|

| ADCVREFN     | Analog negative reference connected to external capacitor | Analog           |                 |          |

|              | Auxiliary Po                                              | rt - AUX         |                 |          |

| мско         | Trace Data Output Clock                                   | Output           |                 |          |

| MDO[5:0]     | Trace Data Output                                         | Output           |                 |          |

| MSEO[1:0]    | Trace Frame Control                                       | Output           |                 |          |

| EVTI_N       | Event In                                                  | Output           | Low             |          |

| EVTO_N       | Event Out                                                 | Output           | Low             |          |

|              | aWire - A                                                 | AW               |                 |          |

| DATA         | aWire data                                                | I/O              |                 |          |

| DATAOUT      | aWire data output for 2-pin mode                          | I/O              |                 |          |

|              | Controller Area Network                                   | k Interface - CA | NIF             |          |

| RXLINE[1:0]  | CAN channel rxline                                        | I/O              |                 |          |

| TXLINE[1:0]  | CAN channel txline                                        | I/O              |                 |          |

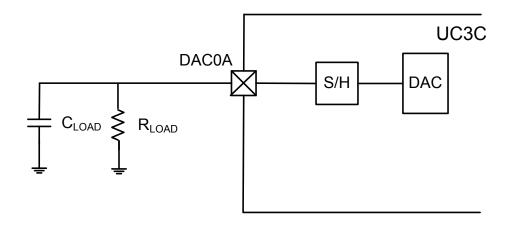

|              | DAC Interface -                                           | DACIFB0/1        |                 |          |

| DAC0A, DAC0B | DAC0 output pins of S/H A                                 | Analog           |                 |          |

| DAC1A, DAC1B | DAC output pins of S/H B                                  | Analog           |                 |          |

| DACREF       | Analog reference voltage input                            | Analog           |                 |          |

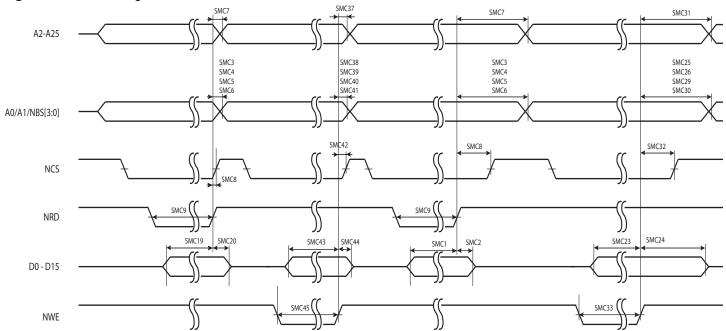

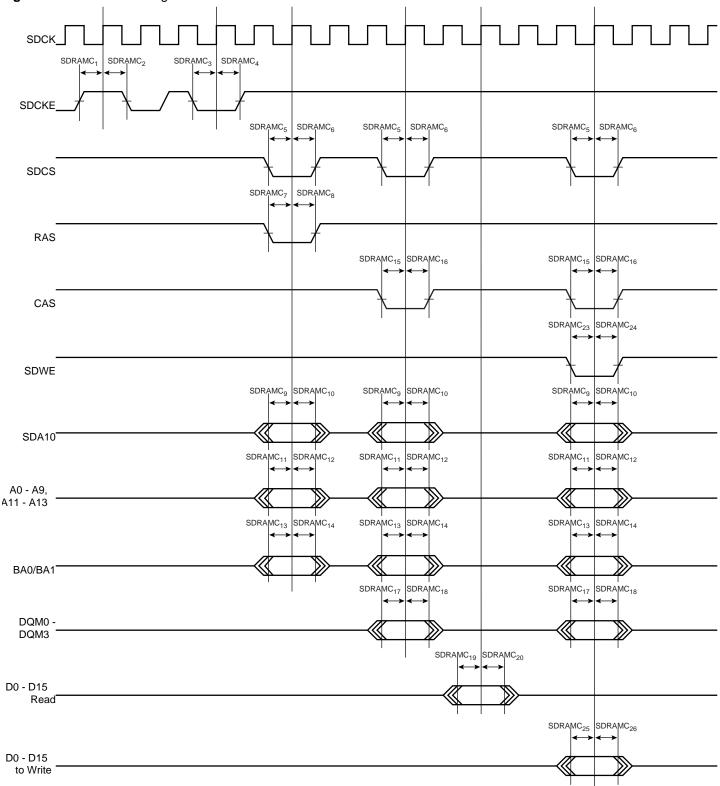

|              | External Bus Into                                         | erface - EBI     |                 | 1        |

| ADDR[23:0]   | Address Bus                                               | Output           |                 |          |

| CAS          | Column Signal                                             | Output           | Low             |          |

| DATA[15:0]   | Data Bus                                                  | I/O              |                 |          |

| NCS[3:0]     | Chip Select                                               | Output           | Low             |          |

| NRD          | Read Signal                                               | Output           | Low             |          |

| NWAIT        | External Wait Signal                                      | Input            | Low             |          |

| NWE0         | Write Enable 0                                            | Output           | Low             |          |

| NWE1         | Write Enable 1                                            | Output           | Low             |          |

| RAS          | Row Signal                                                | Output           | Low             |          |

| SDA10        | SDRAM Address 10 Line                                     | Output           |                 |          |

Table 3-7.Signal Description List

| Signal Name          | Function                      | Туре                | Active<br>Level | Comments |  |  |  |

|----------------------|-------------------------------|---------------------|-----------------|----------|--|--|--|

| SDCK                 | SDRAM Clock                   | Output              |                 |          |  |  |  |

| SDCKE                | SDRAM Clock Enable            | Output              | Output          |          |  |  |  |

| SDWE                 | SDRAM Write Enable            | Output              | Low             |          |  |  |  |

|                      | External Interrup             | ot Controller - EIC |                 |          |  |  |  |

| EXTINT[8:1]          | External Interrupt Pins       | Input               |                 |          |  |  |  |

| NMI_N = EXTINT[0]    | Non-Maskable Interrupt Pin    | Input               | Low             |          |  |  |  |

|                      | General Purpose Input/Output  | - GPIOA, GPIOB, O   | GPIOC, GPI      | OD       |  |  |  |

| PA[29:19] - PA[16:0] | Parallel I/O Controller GPIOA | I/O                 |                 |          |  |  |  |

| PB[31:0]             | Parallel I/O Controller GPIOB | I/O                 |                 |          |  |  |  |

| PC[31:0]             | Parallel I/O Controller GPIOC | I/O                 |                 |          |  |  |  |

| PD[30:0]             | Parallel I/O Controller GPIOD | I/O                 |                 |          |  |  |  |

|                      | Inter-IC Sound (I2            | S) Controller - IIS | C               |          |  |  |  |

| IMCK                 | I2S Master Clock              | Output              |                 |          |  |  |  |

| ISCK                 | I2S Serial Clock              | I/O                 |                 |          |  |  |  |

| ISDI                 | I2S Serial Data In            | Input               |                 |          |  |  |  |

| ISDO                 | I2S Serial Data Out           | Output              |                 |          |  |  |  |

| IWS                  | I2S Word Select               | I/O                 |                 |          |  |  |  |

|                      | JT                            | AG                  | l               |          |  |  |  |

| тск                  | Test Clock                    | Input               |                 |          |  |  |  |

| TDI                  | Test Data In                  | Input               |                 |          |  |  |  |

| TDO                  | Test Data Out                 | Output              |                 |          |  |  |  |

| TMS                  | Test Mode Select              | Input               |                 |          |  |  |  |

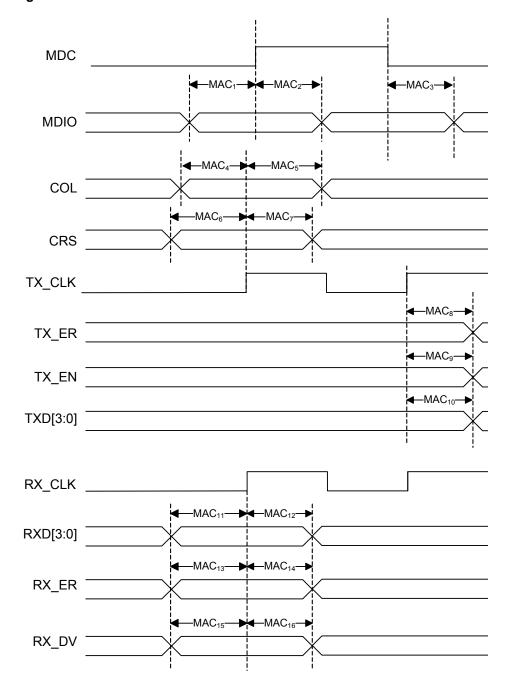

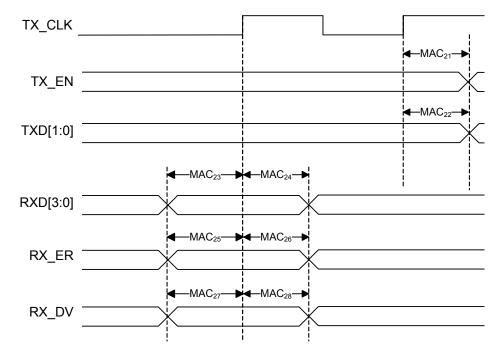

|                      | Ethernet N                    | IAC - MACB          |                 |          |  |  |  |

| COL                  | Collision Detect              | Input               |                 |          |  |  |  |

| CRS                  | Carrier Sense and Data Valid  | Input               | Input           |          |  |  |  |

| MDC                  | Management Data Clock         | Output              | Output          |          |  |  |  |

| MDIO                 | Management Data Input/Output  | I/O                 | I/O             |          |  |  |  |

| RXD[3:0]             | Receive Data                  | Input               | Input           |          |  |  |  |

Table 3-7.

Signal Description List

| Signal Name             | Function                          | Туре         | Active<br>Level | Comments |  |  |

|-------------------------|-----------------------------------|--------------|-----------------|----------|--|--|

| RX_CLK                  | Receive Clock                     | Input        |                 |          |  |  |

| RX_DV                   | Receive Data Valid                | Input        |                 |          |  |  |

| RX_ER                   | Receive Coding Error              | Input        |                 |          |  |  |

| SPEED                   | Speed                             | Output       |                 |          |  |  |

| TXD[3:0]                | Transmit Data                     | Output       |                 |          |  |  |

| TX_CLK                  | Transmit Clock or Reference Clock | Input        |                 |          |  |  |

| TX_EN                   | Transmit Enable                   | Output       |                 |          |  |  |

| TX_ER                   | Transmit Coding Error             | Output       |                 |          |  |  |

| WOL                     | Wake-On-LAN                       | Output       |                 |          |  |  |

|                         | Peripheral Event Contr            | oller - PEVC | ;               |          |  |  |

| PAD_EVT[15:0]           | Event Input Pins                  | Input        |                 |          |  |  |

|                         | Power Manager                     | - PM         |                 |          |  |  |

| RESET_N                 | Reset Pin                         | Input        | Low             |          |  |  |

|                         | Pulse Width Modula                | tor - PWM    |                 |          |  |  |

| PWMH[3:0]<br>PWML[3:0]  | PWM Output Pins                   | Output       |                 |          |  |  |

| EXT_FAULT[1:0]          | PWM Fault Input Pins              | Input        |                 |          |  |  |

|                         | Quadrature Decoder- Qi            | DEC0/QDEC    | 1               |          |  |  |

| QEPA                    | QEPA quadrature input             | Input        |                 |          |  |  |

| QEPB                    | QEPB quadrature input             | Input        |                 |          |  |  |

| QEPI                    | Index input                       | Input        |                 |          |  |  |

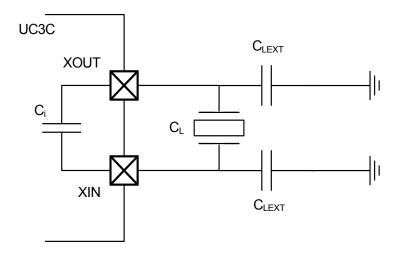

|                         | System Controller Inte            | rface- SCIF  |                 |          |  |  |

| XIN0, XIN1, XIN32       | Crystal 0, 1, 32K Inputs          | Analog       |                 |          |  |  |

| XOUT0, XOUT1,<br>XOUT32 | Crystal 0, 1, 32K Output          | Analog       |                 |          |  |  |

| GCLK0 - GCLK1           | Generic Clock Pins                | Output       |                 |          |  |  |

|                         | Serial Peripheral Interfac        | e - SPI0, SP | 11              |          |  |  |

| MISO                    | Master In Slave Out               | I/O          |                 |          |  |  |

| MOSI                    | Master Out Slave In               | I/O          |                 |          |  |  |

Table 3-7.Signal Description List

| Signal Name | Function                               | Туре              | Active<br>Level | Comments               |  |  |  |  |

|-------------|----------------------------------------|-------------------|-----------------|------------------------|--|--|--|--|

| NPCS[3:0]   | SPI Peripheral Chip Select             | I/O               | Low             |                        |  |  |  |  |

| SCK         | Clock                                  | Output            |                 |                        |  |  |  |  |

|             | Timer/Cour                             | nter - TC0, TC1   |                 |                        |  |  |  |  |

| A0          | Channel 0 Line A                       | I/O               |                 |                        |  |  |  |  |

| A1          | Channel 1 Line A                       | I/O               |                 |                        |  |  |  |  |

| A2          | Channel 2 Line A                       | I/O               |                 |                        |  |  |  |  |

| B0          | Channel 0 Line B                       | I/O               |                 |                        |  |  |  |  |

| B1          | Channel 1 Line B                       | I/O               |                 |                        |  |  |  |  |

| B2          | Channel 2 Line B                       | I/O               |                 |                        |  |  |  |  |

| CLK0        | Channel 0 External Clock Input         | Input             |                 |                        |  |  |  |  |

| CLK1        | Channel 1 External Clock Input         | Input             |                 |                        |  |  |  |  |

| CLK2        | Channel 2 External Clock Input         | Input             |                 |                        |  |  |  |  |

|             | Two-wire Interface - T\                | WIMSO, TWIMS1, T  | WIMS2           |                        |  |  |  |  |

| TWALM       | SMBus SMBALERT                         | I/O               | Low             | Only on TWIMS0, TWIMS1 |  |  |  |  |

| TWCK        | Serial Clock                           | I/O               |                 |                        |  |  |  |  |

| TWD         | Serial Data                            | I/O               |                 |                        |  |  |  |  |

| Universal   | Synchronous Asynchronous Receiver Tran | smitter - USART0, | USART1, U       | SART2, USART3, USART4  |  |  |  |  |

| CLK         | Clock                                  | I/O               |                 |                        |  |  |  |  |

| CTS         | Clear To Send                          | Input             | Low             |                        |  |  |  |  |

| DCD         | Data Carrier Detect                    | Input             | Low             | Only USART1            |  |  |  |  |

| DSR         | Data Set Ready                         | Input             | Low             | Only USART1            |  |  |  |  |

| DTR         | Data Terminal Ready                    | Output            | Low             | Only USART1            |  |  |  |  |

| RI          | Ring Indicator                         | Input             | Low             | Only USART1            |  |  |  |  |

| RTS         | Request To Send                        | Output            | Low             |                        |  |  |  |  |

| RXD         | Receive Data                           | Input             |                 |                        |  |  |  |  |

| TXD         | Transmit Data                          | Output            |                 |                        |  |  |  |  |

|             | Universal Serial                       | Bus Device - USB  | I               | 1                      |  |  |  |  |

| DM          | USB Device Port Data -                 | Analog            |                 |                        |  |  |  |  |

Table 3-7. Signal Description List

| Signal Name | Function                                | Туре            | Active<br>Level | Comments |

|-------------|-----------------------------------------|-----------------|-----------------|----------|

| DP          | USB Device Port Data +                  | Analog          |                 |          |

| VBUS        | USB VBUS Monitor and OTG Negociation    | Analog<br>Input |                 |          |

| ID          | ID Pin of the USB Bus                   | Input           |                 |          |

| VBOF        | USB VBUS On/off: bus power control port | output          |                 |          |

#### 3.4 I/O Line Considerations

#### 3.4.1 JTAG pins

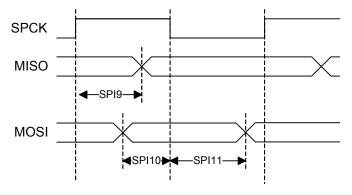

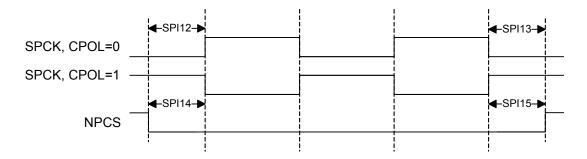

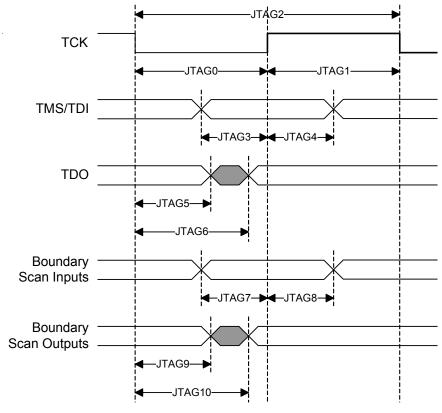

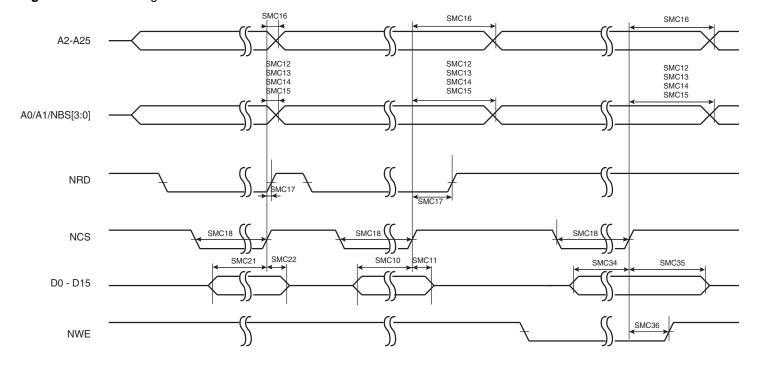

The JTAG is enabled if TCK is low while the RESET\_N pin is released. The TCK, TMS, and TDI pins have pull-up resistors when JTAG is enabled. The TCK pin always have pull-up enabled during reset. The TDO pin is an output, driven at VDDIO1, and has no pull-up resistor. The JTAG pins can be used as GPIO pins and muxed with peripherals when the JTAG is disabled. Please refer to Section 3.2.4 for the JTAG port connections.