### 3A SINK/SOURCE BUS TERMINATION REGULATOR

#### **FEATURES**

- Ideal for DDR-I, DDR-II and DDR-III V<sub>TT</sub> Applications

- Sink and Source 3A Continuous Current

- Integrated Power MOSFETs

- Generates Termination Voltage for SSTL\_2, SSTL\_18, HSTL, SCSI-2 and SCSI-3 Interfaces.

- High Accuracy Output Voltage at Full-Load

- Output Adjustment by Two External Resistors

- Low External Component Count

- Shutdown for Suspend to RAM (STR) Functionality with High-Impedance Output

- **■** Current Limiting Protection

- On-Chip Thermal Protection

- Available in TO-252-5L & ESOP-8 Packages

- V<sub>IN</sub> and V<sub>CNTL</sub> No Power Sequence Issue

- RoHS Compliant and 100% Lead (Pb)-Free

### **APPLICATION**

- Desktop PCs, Notebooks, and Workstations

- Graphics Card Memory Termination

- Set Top Boxes, Digital TVs, Printers

- Embedded Systems

- Active Termination Buses

- DDR-I, DDR-II and DDR-III Memory Systems

#### **DESCRIPTIOON**

The AP1270 is a simple, cost-effective and high-speed linear regulator designed to generate termination voltage in double data rate (DDR) memory system to comply with the JEDEC SSTL\_2 and SSTL\_18 or other specific interfaces such as HSTL, SCSI-2 and SCSI-3 etc. devices requirements. The regulator is capable of actively sinking or sourcing up to 3A while regulating an output voltage to within 40mV. The output termination voltage cab be tightly regulated to track 1/2V DDQ by two external voltage divider resistors or the desired output voltage can be pro-grammed by externally forcing the REFEN pin voltage.

The AP1270 also incorporates a high-speed differential amplifier to provide ultra-fast response in line/load transient. Other features include extremely low initial offset voltage, excellent load regulation, current limiting in bi-directions and on-chip thermal shut-down protection.

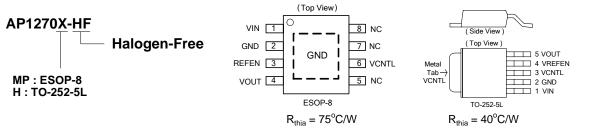

The AP1270 are available in the TO-252-5L & ESOP-8 (Exposed Pad) surface mount packages.

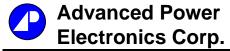

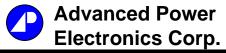

### **TYPICAL APPLICATION**

$R_1 = R_2 = 100 \text{K}\Omega$ ,  $R_{TT} = 50 \Omega / 33 \Omega / 25 \Omega$

C<sub>OUT,min</sub> = 10uF (Ceramic) + 1000uF under the worst case testing condition

$C_{\text{SS}} = 1 \mu \text{F, } C_{\text{IN}} = 470 \mu \text{F(Low ESR), } C_{\text{CNTL}} = 47 \mu \text{F}$

# ABSOLUTE MAXIMUM RATINGS<sup>(Note1)</sup>

Input Voltage  $(V_{IN})$  ----- 6V CNTL Pin Voltage  $(V_{CNTL})$  ----- 6V

Lead Temperature (Soldering, 10sec.) ----- 260°C

Thermal Resistance from Junction to Case (R<sub>thic</sub>)

ESOP-8 28°C/W TO-252-5L 6°C/W

Note1 : Exceeding the absolute maximum rating may damage the device.

## OPERATING RATING(Note2)

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

### ORDERING / PACKAGE INFORMATION

### **ELECTRICAL SPECIFICATIONS**

(V<sub>IN</sub>=1.8V, V<sub>CNTL</sub>=3.3V, V<sub>REFEN</sub>=0.9V, C<sub>OUT</sub>=10uF(Ceramic), T<sub>A</sub> =25°C, unless otherwise specified)

| Parameter                                | SYM                | TEST CONDITION                                           | MIN  | TYP | MAX | UNITS |

|------------------------------------------|--------------------|----------------------------------------------------------|------|-----|-----|-------|

| Input                                    |                    |                                                          |      |     |     |       |

| VCNTL Operation Current                  | I <sub>CNTL</sub>  | $I_{OUT} = 0A$                                           | -    | 1   | 2.5 | mA    |

| Standby Current                          | I <sub>STBY</sub>  | $V_{REFEN}$ < 0.2V (Shutdown), $R_{LOAD}$ = 180 $\Omega$ | -    | 50  | 90  | uA    |

| Output (DDR / DDRII / DDRIII)            |                    |                                                          |      |     |     |       |

| Output Offset Voltage <sup>(Note3)</sup> | Vos                | $I_{OUT} = 0A$                                           | -20  | -   | 20  | mV    |

| Load Regulation <sup>(Note4)</sup>       | $\Delta  V_{Load}$ | I <sub>OUT</sub> = 10mA ~ 3A                             | -20  | -   | 20  |       |

|                                          |                    | I <sub>OUT</sub> = -10mA ~ -3A                           | -20  | -   | 20  |       |

| Protection                               |                    |                                                          |      |     |     |       |

| Current Limit                            | I <sub>LIM</sub>   |                                                          | 3.2  | -   | -   | Α     |

| Thermal Shutdown Temperature             | T <sub>SD</sub>    | 3.3V <u>&lt;</u> VCNTL <u>&lt;</u> 5V                    | 130  | 160 | -   | °C    |

| Thermal Shutdown Hysteresis              | $\DeltaT_{SD}$     | 3.3V <u>&lt;</u> VCNTL <u>&lt;</u> 5V                    | -    | 30  | -   |       |

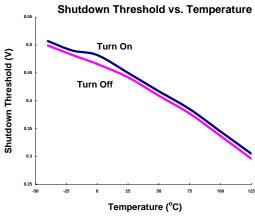

| REFEN Shutdown                           |                    |                                                          |      |     |     |       |

| Shutdown Threshold                       | $V_{IH}$           | Enable                                                   | 0.65 | -   | -   | V     |

|                                          | $V_{IL}$           | Shutdown                                                 | -    | -   | 0.2 | ]     |

Note3.  $V_{OS}$  offset is the voltage measurement defined as  $V_{OUT}$  subtracted from  $V_{REFEN}$ .

Note4. Regulation is measured at constant junction temperature by using a 5ms current pulse. Devices are tested for load regulation

in the load range from 0A to 3A.

### PIN DESCRIPTIONS

| PIN SYMBOL        | PIN DESCRIPTION                         |  |

|-------------------|-----------------------------------------|--|

| $V_{\rm IN}$      | Power Input Voltage.                    |  |

| GND               | Ground Pin                              |  |

| V <sub>OUT</sub>  | Output Voltage                          |  |

| V <sub>CNTL</sub> | Gate Drive Voltage                      |  |

| REFEN             | Reference Voltage Input and Chip Enable |  |

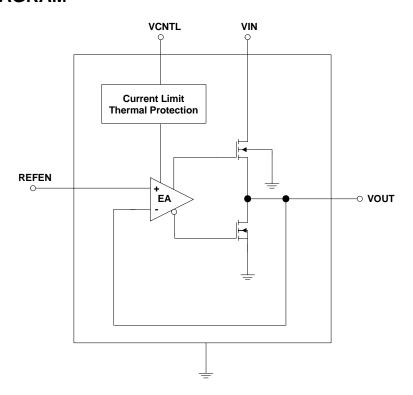

### **BLOCK DIAGRAM**

### **APPLICATION INFORMATION**

#### **Input Capacitor and Layout Consideration**

Place the input bypass capacitor as close as possible to the AP1270. A low ESR capacitor larger than 470uF is recommended for the input capacitor. Use short and wide traces to minimize parasitic resistance and inductance.

Inappropriate layout may result in large parasitic inductance and cause undesired oscillation between AP1270 and the preceding powe converter.

#### Consideration while designs the resistance of voltage divider

Make sure the sinking current capability of pull-down NMOS if the lower resistance was chosen so that the voltage on  $V_{\mathsf{REFEN}}$  is below 0.2V. In addition, the capacitor and voltage divider form the lowpass filter. There are two reasons doing this design; one is for output voltage soft-start while another is for noise immunity.

#### **Thermal Consideration**

AP1270MP regulators have internal thermal limiting circuitry designed to protect the device during overload conditions. For continued operation, do not exceed maximum operation junction temperature 125°C. The power dissipation definition in device is:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{Q}$$

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / R_{thja}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature 125°C,  $T_A$  is the ambient temperature and the  $R_{thja}$  is the junction to ambient thermal resistance. The junction to ambient thermal resistance ( $R_{thja}$  is layout dependent) for ESOP-8 package (Exposed Pad) is 75°C/W on standard JEDEC 51-7 (4 layers, 2S2P) thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / 75^{\circ}C/W = 1.33W$$

The thermal resistance  $R_{thja}$  of ESOP-8 (Exposed Pad) is determined by the package design and the PCB design. However, the package design has been decided. If possible, it's useful to increase thermal performance by the PCB design. The thermal resistance can be decreased by adding copper under the expose pad of ESOP-8 package. We have to consider the copper couldn't stretch infinitely and avoid the tin overflow.

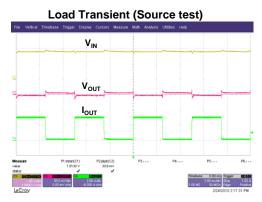

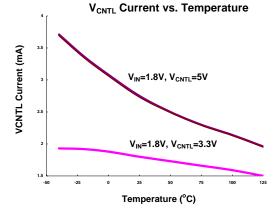

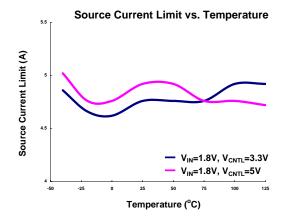

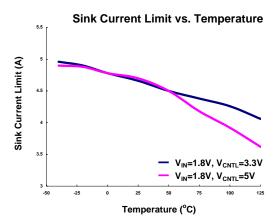

### TYPICAL PERFORMANCE CHARACTERISTICS

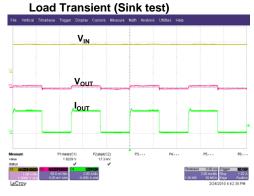

$V_{\text{IN}} = 1.8 \text{V}, \, V_{\text{CNTL}} = 3.3 \text{V}$   $V_{\text{REF}} = 0.9 \text{V Supplied by a regulator}$

$V_{\text{IN}} = 1.8 \text{V}, \, V_{\text{CNTL}} = 3.3 \text{V}$   $V_{\text{REF}} = 0.9 \text{V Supplied by a regulator}$

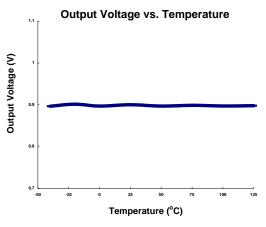

$V_{IN}$  = 1.8V,  $V_{CNTL}$  = 3.3V,  $I_{OUT}$  = 0A, Source test

$V_{IN}$  = 1.8V,  $V_{CNTL}$  = 3.3V,  $I_{OUT}$  = 10mA, Source test

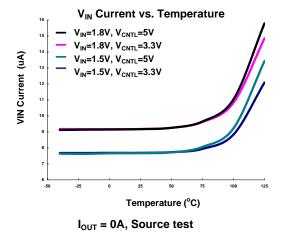

I<sub>OUT</sub> = 0A, Source test

### **TYPICAL PERFORMANCE CHARACTERISTICS**

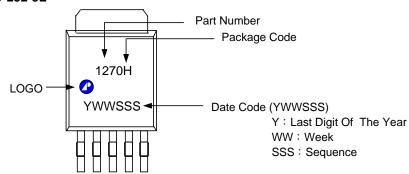

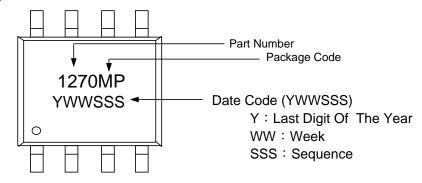

### **MARKING INFORMATION**

#### ESOP-8

#### TO-252-5L