# Single Synchronous Step-down Controller

### **FEATURES**

- High Efficiency and Low Power Consumption

- 4700ppm/°C R<sub>DS-ON</sub> Current Sense

Compensation

- Selectable Auto-Skip / PWM-Only Mode

- Low-Side R<sub>DS-ON</sub> Current Sense

- Positive and Negative Current Limit

- Integrate OV/UV and Thermal Shutdown

Protections

- Integrated Boost Diode

- Wide Input Range: 3V to 28V

- Output Range: 0.7V to 5.5V

- 4 Selectable Frequencies (290 / 340 / 380 / 430 kHz)

- 0.5% Output Voltage Accuracy

- Power Good (PGOOD) Signal

- 1ms Soft Start and Output Discharge Function (Soft-stop)

- 100ns Load Step Transient Response

- RoHS Compliant and 100% Lead (Pb)-Free

### **APPLICATIONS**

- Notebook and Sub-Notebook Computers

- I/O Supplies

- System Power Supplies

### DESCRIPTION

The APE3312 is a high efficiency synchronous buck controller for POL voltage regulator in notebook PC application. A small size and minimize pin cont scants PCB space. The quasi-fixed frequency mode with four frequencies selectable provides ease of use, fast transient response, and low external component count. APE3312 supports two operating modes. Auto-skip mode is for high efficiency in light loading. PWM-only mode is for low noise operation.

The APE3312 has several protect function, includes over voltage protection, positive and negative over current protection, and over temperature protection to prevent system or IC damage. Besides, the internal soft-start function prevents inrush-current and overshoot voltage issues in the start up. The device receives a 5V supply form another regulator. The conversion input ranging is from 3V to 28V, and output ranging is from 0.7V to 5.5V.

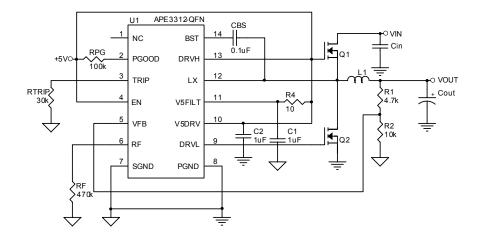

The APE3312 is available in a 10-pin DFN and 14-pin QFN packages.

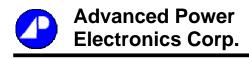

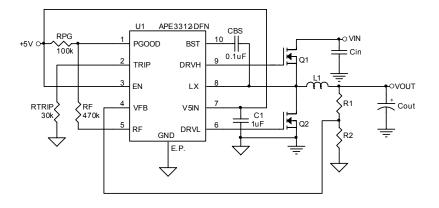

# **TYPICAL APPLICATION**

# **ORDERING / PACKAGE INFORMATION**

### APE3312<u>X</u>

<sup>-</sup> Package Type GN3: DFN 3x3-10L VN35: QFN 3.5x3.5-14L

8

PGND

# ABSOLUTE MAXIMUM RATINGS (at T<sub>A</sub>=25°C)

| VBST                                                        | -0.3V to 36V  |

|-------------------------------------------------------------|---------------|

| VBST to LX                                                  | -0.3V to 6V   |

| EN, TRIP, V5IN, V5DRV, V5FILT                               | -0.3V to 6V   |

| RF                                                          | -0.3V to 6V   |

| DRVH                                                        | -1V to 36V    |

| DRVH to LX                                                  | -0.3V to 6V   |

| LX                                                          | -1V to 30V    |

| PGOOD, DRVL                                                 | -0.3V to 6V   |

| PGND, GND                                                   | -0.3V to 0.3V |

| Storage Temperature Range (T <sub>ST</sub> )                | -65 to +150°C |

| Junction Temperature (T <sub>J</sub> )                      | 125°C         |

| Lead Temperature (Soldering, 10sec.)                        | 260°C         |

| Thermal Resistance from Junction to Case ( $R\theta_{JC}$ ) |               |

| DFN-10 (3mmx3mm)                                            | 43°C/W        |

| QFN-14 (3.5mmx3.5mm)                                        | 60°C/W        |

|                                                             |               |

# **RECOMMENDED OPERATING CONDITIONS**

| VBST                          | 4.5V to 34V   |

|-------------------------------|---------------|

| VBST to LX                    | 4.5V to 5.5V  |

| EN, TRIP, V5IN, V5DRV, V5FILT | -0.1V to 5.5V |

| DRVH                          | -0.8V to 34V  |

| DRVH to LX                    | -0.1V to 5.5V |

| LX                            | -0.8V to 28V  |

| PGOOD, DRVL                   | -0.1V to 5.5V |

| PGND, GND                     | -0.1V to 0.1V |

| Operating Temperature Range   | -40°C to 85°C |

Advanced Power Electronics Corp.

# **ELECTRICAL SPECIFICATIONS**

(VIN=2.95 to 6V,  $T_A$  =25°C, unless otherwise specified)

| PARAMETER                        | SYM                   | TEST CONDITION                                                      | MIN   | TYP | MAX   | UNIT |

|----------------------------------|-----------------------|---------------------------------------------------------------------|-------|-----|-------|------|

| Input                            |                       |                                                                     | 1     |     |       |      |

|                                  | V <sub>IN</sub>       |                                                                     | 3     |     | 28    | V    |

| Input Voltage Range              | V5IN                  |                                                                     | 4.5   |     | 5.5   | V    |

| V5IN Supply Current              | I <sub>V5IN</sub>     | V5IN current, EN=5V, VFB=0.735V,<br>LX = -0.1V, no loading          |       | 320 | 500   | uA   |

| V5IN Shutdown Current            | I <sub>V5IN-SD</sub>  | V5IN current, EN =0V                                                |       | 0   | 1     | uA   |

| Output                           |                       |                                                                     | 1     |     |       |      |

| Output Voltage Range             | V <sub>OUT</sub>      | Adjustable output range                                             | 0.7   |     | 5.5   | V    |

| FB Voltage Regulation            |                       | PWM mode                                                            |       | 700 |       | mV   |

| Range                            | V <sub>FB</sub>       | Auto-Skip mode                                                      | 700.5 | 704 | 707.5 | mV   |

| FB Input Current                 | I <sub>FB</sub>       | V <sub>FB</sub> , absolute value                                    |       | 0.1 |       | uA   |

| Output Discharge Current form LX | I <sub>DIS</sub>      | EN=0V, V <sub>LX</sub> =0.5V                                        | 5     | 13  |       | mA   |

| Soft Start and On-time Ti        | mer                   |                                                                     | •     |     |       | •    |

| Minimum On Time                  | T <sub>ON(MIN)</sub>  | V <sub>OUT</sub> =0.7V, V <sub>LX</sub> =28V, R <sub>RF</sub> =39kΩ |       | 79  |       | ns   |

| Minimum Off Time                 | T <sub>OFF(MIN)</sub> |                                                                     |       | 400 |       | ns   |

| Soft Start Time                  | T <sub>SS</sub>       | From EN=H to V <sub>OUT</sub> =95%                                  |       | 1   |       | ms   |

| Output Drivers                   |                       | -                                                                   |       |     | •     |      |

|                                  | R <sub>DRVH</sub>     | Source, V <sub>VBST-DRVH</sub> =0.5V                                |       | 1.5 | 3     | Ω    |

| DRVH Resistance                  |                       | Sink, V <sub>DRVH-LX</sub> =0.5V                                    |       | 0.7 | 1.8   | Ω    |

|                                  | R <sub>DRVL</sub>     | Source, V <sub>V5IN-DRVL</sub> =0.5V                                |       | 1   | 2.2   | Ω    |

| DRVL Resistance                  |                       | Sink, V <sub>DRVL-GND</sub> =0.5V                                   |       | 0.5 | 1.2   | Ω    |

|                                  | T <sub>D</sub>        | DRVH-low(DRVH=1V) to<br>DRVL-high(DRVL=4V), V <sub>LX</sub> =-0.05V | 7     | 17  | 30    | ns   |

| Dead Time                        |                       | DRVL-low(DRVL=1V) to<br>DRVH-high(DRVH=4V), V <sub>LX</sub> =-0.05V | 10    | 22  | 35    | ns   |

| Boot Strap Switch                | 1                     | 1                                                                   | _1    | L   | 1     |      |

| Forward Voltage                  | V <sub>FBST</sub>     | V <sub>V5IN-VBST</sub> , I <sub>F</sub> =10mA                       |       | 0.2 | 0.3   | V    |

# **ELECTRICAL SPECIFICATIONS (Continued)**

(T<sub>A</sub> =25  $^{\circ}$ C, unless otherwise specified)

| PARAMETER                                       | SYM                | TEST CONDITION                          | MIN     | ТҮР  | MAX  | UNIT       |

|-------------------------------------------------|--------------------|-----------------------------------------|---------|------|------|------------|

| UVLO and LOGIC Thresho                          | old                |                                         |         |      |      | •          |

|                                                 | V <sub>UVLO</sub>  | Raising                                 | 4.2     | 4.38 | 4.5  | V          |

| $V_{5IN}$ UVLO Threshold                        |                    | Falling                                 | 3.7     | 3.93 | 4.1  | V          |

| Switch Fraguenov                                | f <sub>sw</sub>    | R <sub>RF</sub> = 470kΩ                 | 266     | 290  | 314  | kHz        |

| Switch Frequency                                |                    | R <sub>RF</sub> = 200kΩ                 | 312     | 340  | 368  | kHz        |

| ENL/altage Threehold                            |                    | Enable                                  | 1.8     |      |      | V          |

| EN Voltage Threshold                            | $V_{EN}$           | Disable                                 |         |      | 0.5  | V          |

| EN Input Current                                | I <sub>EN</sub>    | EN=5V                                   |         |      | 1    | uA         |

| Modo Sotting Voltago                            | V                  | PWM mode                                | 1.8     |      |      | V          |

| Mode Setting Voltage                            | $V_{RF}$           | Auto-skip mode                          |         |      | 0.5  | V          |

| Current Sense                                   |                    |                                         |         |      |      |            |

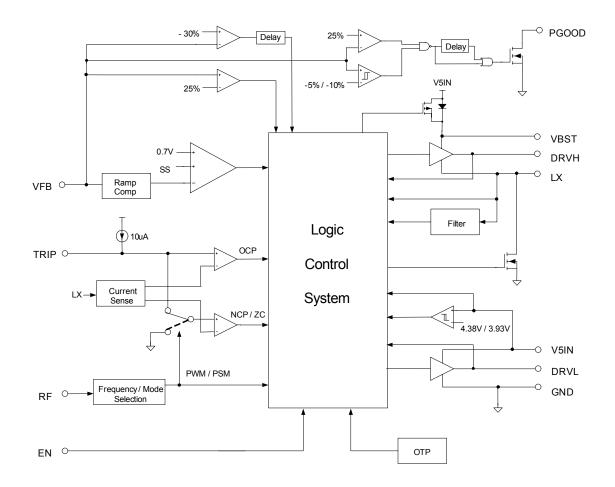

| TRIP Source                                     | I <sub>TRIP</sub>  | V <sub>TRIP</sub> < 0.3V                | 9       | 10   | 11   | uA         |

| I <sub>TRIP</sub> Temperature<br>Coefficient    | $V_{FB}$           |                                         |         | 4700 |      | ppm/<br>°C |

| Current Limit Threshold<br>Range Setting Range  | V <sub>TRIP</sub>  | V <sub>TRIP</sub> to GND                | 0.2     |      | 3    | v          |

|                                                 | V <sub>OCL</sub>   | V <sub>TRIP</sub> =3.0V                 | 355     | 375  | 395  | mV         |

| Overcurrent Limit<br>Threshold                  |                    | V <sub>TRIP</sub> =1.6V                 | 185     | 200  | 215  | mV         |

| mesnolu                                         |                    | V <sub>TRIP</sub> =0.2V                 | 17      | 25   | 33   | mV         |

| Negetine Operations to inside                   | V <sub>NOCL</sub>  | V <sub>TRIP</sub> =3.0V                 | -395    | -375 | -355 | mV         |

| Negative Overcurrent Limit<br>Comparator Offset |                    | V <sub>TRIP</sub> =1.6V                 | -215    | -200 | -185 | mV         |

| Comparator Onset                                |                    | V <sub>TRIP</sub> =0.2V                 | -33     | -25  | -17  | mV         |

| Power Good Function                             |                    |                                         |         |      |      |            |

|                                                 | V <sub>THPG</sub>  | PG lower threshold                      | 92.5 95 | 95   | 97.5 | %          |

| PGOOD Threshold                                 |                    | (PGOOD goes high)                       |         |      | 57.5 | 70         |

|                                                 |                    | PG low hysteresis (PGOOD goes low)      | -2.5    | -5   | -7.5 | %          |

|                                                 |                    | PG higher threshold<br>(PGOOD goes low) | 121     | 125  | 129  | %          |

| PGOOD Sink Current                              | I <sub>PGMAX</sub> | PGOOD=0.5V                              | 3       | 6    |      | mA         |

| PGOOD Delay                                     | T <sub>PGDEL</sub> | Delay for PGOOD in                      | 0.8     | 1    | 1.2  | ms         |

# **ELECTRICAL SPECIFICATIONS (Continued)**

$(T_A = 25^{\circ}C, unless otherwise specified)$

| PARAMETER                                                   | SYM                 | TEST CONDITION          | MIN | ТҮР | МАХ | UNIT |

|-------------------------------------------------------------|---------------------|-------------------------|-----|-----|-----|------|

| Under-Voltage and Over-V                                    | /oltage Pro         | otection                |     |     |     |      |

| V <sub>FB</sub> OVP Trip Threshold                          | V <sub>OVP</sub>    | OVP detect              | 121 | 125 | 129 | %    |

| V <sub>FB</sub> OVP Propagation<br>delay <sup>(Note1)</sup> | T <sub>OVPDEL</sub> |                         |     | 1   |     | us   |

| V <sub>FB</sub> UVP Trip Threshold                          | V <sub>UVP</sub>    | UVP detect              | 65  | 70  | 75  | %    |

| V <sub>FB</sub> UVP Delay                                   | T <sub>UVPDEL</sub> |                         | 0.8 | 1   | 1.2 | ms   |

| UVP Enable Delay                                            | T <sub>UVPEN</sub>  | From Enable to UVP wrok | 1   | 1.2 | 1.4 | ms   |

| Thermal Shutdown                                            |                     |                         |     |     |     |      |

| Thermal Shutdown                                            | -                   |                         |     | 155 |     | °C   |

| Threshold (Note1)                                           | $T_{SD}$            | Hysteresis              |     | 10  |     | °C   |

Note1: Guaranteed by design, not production tested.

# **PIN DESCRIPTIONS**

DFN-10L Package

| PIN No. | PIN SYMBOL | PIN DESCRIPTION                                                             |

|---------|------------|-----------------------------------------------------------------------------|

| 1       | PGOOD      | Power good output pin. PGOOD is an open-drain output. Connect a pull        |

|         | FGOOD      | up resister to 5V. Current capability is 6mA.                               |

|         |            | SMPS current limit threshold setting pin. Connect resistor form this pin to |

| 2       | TRIP       | ground to set threshold for both overcurrent limit and negative overcurrent |

|         |            | limit. Set the OCL trip voltage is $V_{OCL}=V_{TRIP}/8$                     |

| 3       | EN         | SMPS Enable pin.                                                            |

| 4       | VFB        | SMPS voltage feedback input                                                 |

|         |            | Switch frequency / Mode selection pin. Connect a resistance to selection    |

| 5       | RF         | switching frequency. Besides, as the resistance connects to GND is          |

|         |            | auto-skip mode, or connecting to PGOOD pin select PWM mode.                 |

| 6       | DRVL       | Low side N-MOS gate driver output. Drive voltage is V5IN voltage.           |

| 7       | V5IN       | Power supply input.                                                         |

| 8       | LX         | High side N-MOS gate driver return. Also used for on time generation and    |

| 0       | LA         | output discharge.                                                           |

| 9       | DRVH       | High side N-MOS gate driver output. Drive voltage corresponds to VBST       |

| 9       | DKVH       | to LX voltage.                                                              |

|         |            | Supply input for high side N-MOS gate driver (Boost terminal). Connect      |

| 10      | VBST       | capacitor from this pin to LX. An internal MOSFET is connected between      |

| 10      |            | V5IN to this pin. Designer can add external Schottky diode if forward drop  |

|         |            | is critical to drive the power N-MOS.                                       |

| Exposed | GND        | Ground.                                                                     |

| Pad     |            |                                                                             |

#### QFN-14L Package

| PIN No. | PIN SYMBOL | PIN DESCRIPTION                                                             |

|---------|------------|-----------------------------------------------------------------------------|

| 1       | NC         | No connect                                                                  |

| •       | 50005      | Power good output pin. PGOOD is an open-drain output. Connect a pull        |

| 2       | PGOOD      | up resister to 5V. Current capability is 6mA.                               |

|         |            | SMPS current limit threshold setting pin. Connect resistor form this pin to |

| 3       | TRIP       | ground to set threshold for both overcurrent limit and negative overcurrent |

|         |            | limit. Set the OCL trip voltage is $V_{\text{OCL}}=V_{\text{TRIP}}/8$       |

| 4       | EN         | SMPS Enable pin.                                                            |

| 5       | VFB        | SMPS voltage feedback input                                                 |

|         |            | Switch frequency / Mode selection pin. Connect a resistance to selection    |

|         | DE         | switching frequency (refer to Table1). Besides, as the resistance connects  |

| 6       | RF         | to GND is auto-skip mode, or connecting to PGOOD pin select PWM             |

|         |            | mode.                                                                       |

| 7       | GND        | Signal ground.                                                              |

| 8       | PGND       | Power ground.                                                               |

| 9       | DRVL       | Low side N-MOS gate driver output. Drive voltage is V5IN voltage.           |

|         |            | 5V power supply input for MOS gate drivers. Internally connected to         |

| 10      | V5DRV      | VBST by a MOSFET. Connect 1uF or more to PGND to support                    |

|         |            | instantaneous current for gate drivers.                                     |

| 11      | V5FILT     | 5V power supply input for all the control circuitry except gate drivers.    |

| 11      | VOFILI     | Apply RC filter consists of $10\Omega$ + 1uF at the pin input.              |

| 12      | LX         | High side N-MOS gate driver return. Also used for on time generation and    |

| 12      | LA         | output discharge.                                                           |

| 13      | DRVH       | High side N-MOS gate driver output. Drive voltage corresponds to VBST       |

| 15      | BRVII      | to LX voltage.                                                              |

|         |            | Supply input for high side N-MOS gate driver (Boost terminal). Connect      |

| 14      | VBST       | capacitor from this pin to LX. An internal MOSFET is connected between      |

| 14      |            | V5DRV to this pin. Designer can add external Schottky diode if forward      |

|         |            | drop is critical to drive the power N-MOS.                                  |

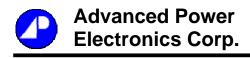

# BLOCK DIAGRAM

Advanced Power Electronics Corp.

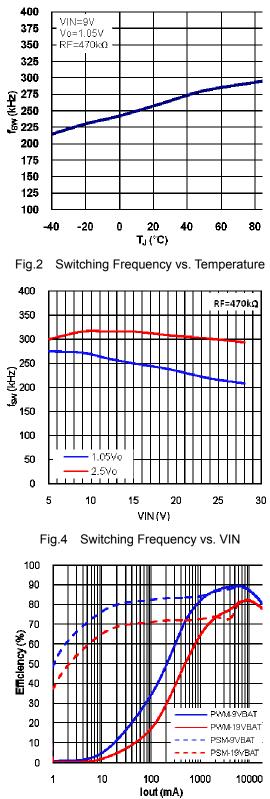

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Fig.6 Efficiency for Vo=1.05V

**Advanced Power**

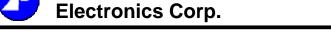

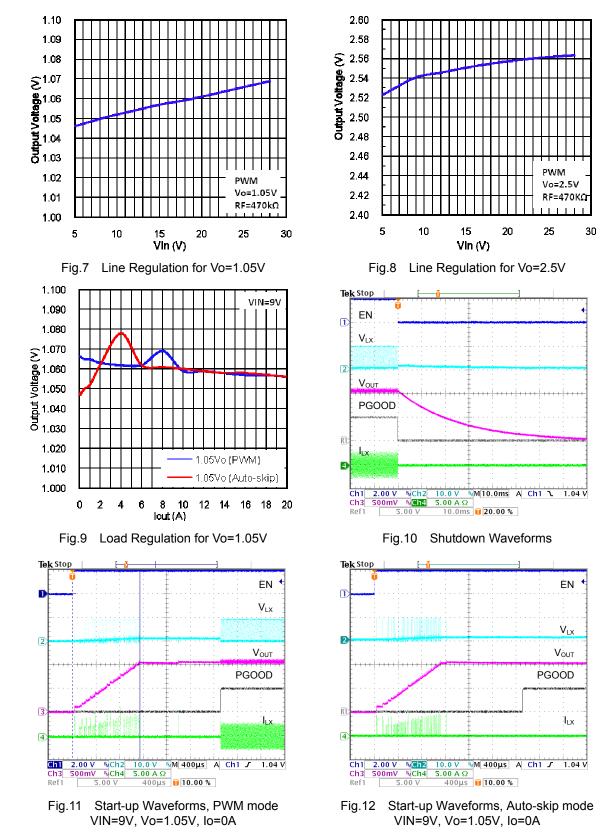

### **TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

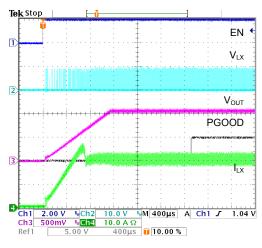

# TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

Advanced Power Electronics Corp.

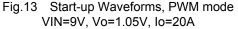

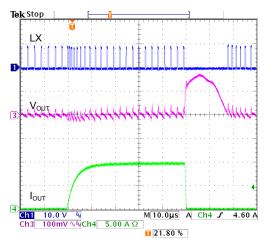

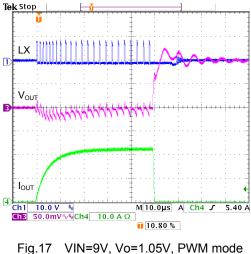

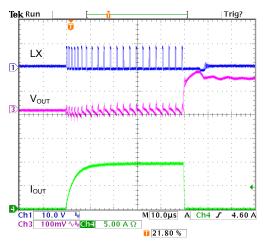

Fig.15 VIN=9V, Vo=1.05V, PWM mode  $f_{SW}$ =340kHz, L=1uH, Cout=330uF/9m $\Omega$  \*1

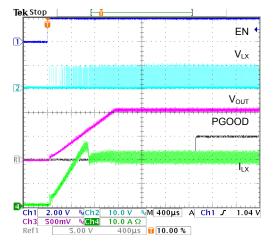

Fig.14 Start-up Waveforms, Auto-skip mode VIN=9V, Vo=1.05V, Io=20A

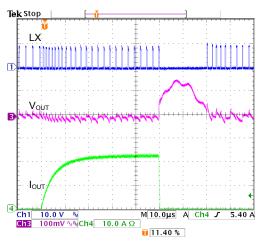

Fig.16 VIN=9V, Vo=1.05V, Auto-skip mode  $f_{SW}$ =340kHz, L=1uH, Cout=330uF/9m $\Omega$ \*1

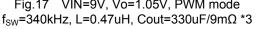

Fig.18 VIN=9V, Vo=1.05V, Auto-skip mode  $f_{SW}$ =340kHz, L=0.47uH, Cout=330uF/9m $\Omega$ \*3

### **DETAIL DESCRIPTION**

The APE3312 synchronous buck controller is designed for low-voltage power supplies for notebook PC applications. The APE3312 control scheme is a constant-on-time, pseudo-fixed frequency, current-mode PWM controller and specifically designed for leading fast load transient while maintaining a relative constant switching frequency and operating over a wide range of input voltage. This architecture depends on the ESR of output capacitor; the output ripple voltage across the ESR provides the PWM ramp signal, eliminating the need for a current sense resistor. The high-side switch on-time is determined by an internal one-shot which pulse width is inversely proportional to input voltage and proportional to output voltage. Another one-shot sets a minimum off-time (400ns typ.). The on-time one-shot is triggered if the error comparator is low.

#### +5V Bias Input

The APE3312 requires an external +5V bias supply in addition to the battery voltage. The external bias supply is needed to supply the PWM control circuitry and gate drivers. The +5V input can be generated by an external linear regulator, if stand-alone capability is needed. The 5V bias supply must be power up after to the battery supply (VIN) is present to ensure startup well.

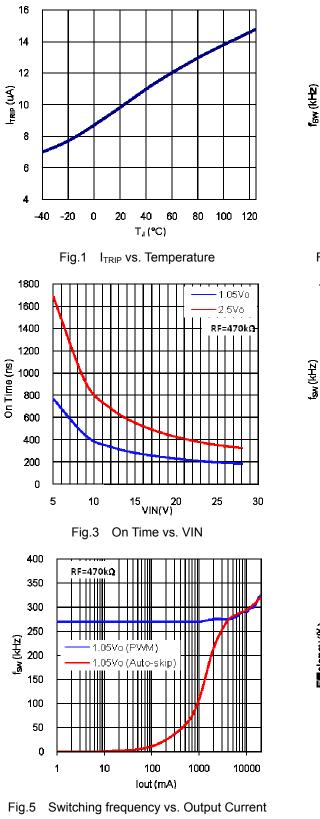

#### On-Time One-Shot (ToN)

The core of pseudo fixed frequency PWM is the one-shot that sets the on-time of high-side switch for the controller. This low jitter, adjustable one-shot includes circuitry that varies the on-time in response to VIN and output voltage. The on-time is disproportional to the input voltage, and proportional to the output voltage, so that the duty ratio is kept as VOUT/VIN theoretically.

#### Switch frequency / Mode selection

The switching frequency is selectable from four preset values by a resistor connected to RF as shown in Table 1. Leave the RF pin open to set the lowest switching frequency, 290 kHz.

The APE3312 operates with PWM-only or auto-skip mode by connecting  $R_{RF}$  high or low to provide multi-function. Pull RF pin low via  $R_{RF}$  to set the APE3312 operates in auto-skip mode. Pull RF pin high via  $R_{RF}$  to force PWM-only mode.

| Resistance (kΩ) | Switching Frequency (kHz) |

|-----------------|---------------------------|

| 470             | 290                       |

| 200             | 340                       |

| 100             | 380                       |

| 39              | 430                       |

Table1. R<sub>RF</sub> vs. f<sub>SW</sub>

### **DETAIL DESCRIPTION (Continued)**

#### Auto-Skip Mode

In auto-skip mode, the internal Zero-Cross comparator looks for inductor current. When the zero current is detected, the controller enters auto-skip mode and turns low-side MOSFET off on each cycle. If the inductor current does not cross zero, the controller immediately exits auto-skip mode. At light load condition, the APE3312 operates in power save mode and reduces the switching frequency automatically to maintain high efficiency. This decreased frequency is performed smoothly and without increasing output ripple. The boundary between continuous and discontinuous inductor-current conduction mode, I<sub>OUT(LB)</sub>, can be calculated by:

$I_{OUT(LB)} = \frac{1}{2 \times L \times f_{sw}} \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$

#### Forced PWM-Only Mode

The low-noise, forced PWM-Only mode disables the zero-crossing comparator, which controls the low-side switch on-time. The constant switching frequency has two benefits: first, the frequency can be selected to avoid noise-sensitive regions; second, the inductor ripple-current remains relatively constant which resulting in easy to design and predictable output voltage ripple.

#### **Output Voltage Setting**

The output can be adjusted to a voltage range from 0.7V to 5.5V. The output voltage can be calculated as:

$$V_{OUT} = 0.7V \times (\frac{R1}{R2} + 1)$$

#### **Current Limit**

The current-limit circuit of APE3312 senses the  $R_{DS-ON}$  of low-side MOSFET, monitors valley inductor current. The actual peak current is greater than the current-limit threshold by an amount equal to the inductor ripple current. The current limit threshold is adjusted with an external resistor at TRIP pin.  $V_{TRIP}$  is set the current limit valley level, which is the following equation:

$V_{\text{TRIP}}(mV) = R_{\text{TRIP}}(k\Omega) \times I_{\text{TRIP}} = R_{\text{TRIP}}(k\Omega) \times 10 uA$

Note that  $V_{TRIP}$  is internally limited ranging is from 0.2V to 3V.

The valley current limit threshold can be given as:

$$I_{OC(Valley)} = \frac{R_{TRIP}(k\Omega) \times I_{TRIP}(uA)}{8 \times R_{DS-ON}(m\Omega)} = \frac{V_{TRIP}(mV)}{8 \times R_{DS-ON}(m\Omega)}$$

Therefore, the load current at over-current threshold, locp, can be calculated as follows:

$$I_{OCP} = I_{OC(Valley)} + \frac{\Delta I_{L}}{2} = \frac{V_{TRIP}}{8 \times R_{DS-ON}} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times f_{SW} \times V_{IN}}$$

The output voltage tends to fall down cause of an over current condition. Finally, it crosses the UVP threshold and shuts down the controller. The APE3312 also supports temperature compensated for  $R_{DS-ON}$  sensing.  $I_{TRIP}$  has 4700ppm/°C temperature coefficient to compensate the temperature dependency of the  $R_{DS-ON}$  to keep almost identical current limit threshold in operation temperature range.

### **DETAIL DESCRIPTION (Continued)**

There is also a negative current limit in the forced continuous conduction mode that prevents excessive reverse inductor currents when VOUT is sinking current. The negative current limit detect threshold is approximate to the negative polarity of positive current limit threshold.

#### Soft Start

The APE3312 has an internal, 1ms, soft start with overcurrent limit. When the EN pin voltage rises above the enable threshold, the controller enters its start-up sequence. Soft-start allows a gradual increase of the internal current-limit level during startup to reduce the input surge currents.

#### Soft Stop

The APE3312 discharges output by an internal MOSFET connected between LX and PGND while EN is low or any fault shutdown condition. The discharge time is depended of the output capacitance and the discharge resistance.

#### **Under-Voltage Lockout Protection (UVLO)**

The APE3312 has V5IN (V5FILT) under-voltage lockout protection (UVLO). This is a non-latched protection. When the V5IN (V5FILT) voltage is lower than 3.93V, the APE3312 is off.

#### **Power Good Output**

The APE3312 provides a power good (PGOOD) output, which is an open-drain output requiring a pull-up resistor. Typically connect to +5V bias supply through a 100k $\Omega$  resistor. The PGOOD comparator continuously monitors the output for both over-voltage and under-voltage conditions. In shutdown and soft-start period, PGOOD is actively low. After soft-start, PGOOD is released after 1ms delay time when the output is within 95% of the threshold. If the output voltage is without 90% or 125% of the target threshold, the PGOOD becomes low immediately. Note that the PGOOD window detector is independent of the output over-voltage and under-voltage protection thresholds, but held low after an UVP or OVP.

#### Under Voltage Protection (UVP)

If VFB falls lower than 70% of nominal value, the DRVH and DRVL are pulled low to turn off the MOSFETs after 1ms. The APE3312 latches off until its EN input is toggled or the +5V bias supply is re-start. The UVP function is disabled during start-up period.

#### **Over Voltage Protection (OVP)**

If VFB exceeds 125% of nominal value, over-voltage protection is triggered. The DRVL latches high and the low side MOSFET is turned on and high side MOSFET is turned off. This action discharges the output capacitor rapidly. DRVL stays high and the output latches off until the EN input is toggled or the +5V bias supply is re-started.

### **APPLICATION INFORMATION**

#### Inductor Selection

The inductor value determines the ripple current and the ripple voltage of the converter. This inductor choice provides trade-offs between size vs. efficiency. Low inductor values cause large ripple currents, resulting in the smallest size, but poor efficiency and high output noise. The inductor selection is based on the ripple current which is typically set between 1/4 to 1/2 of the maximum load current. The switching frequency and ripple current determine the inductor which can be calculated as follows:

$L = \frac{V_{OUT}(V_{IN} - V_{OUT})}{f_{SW} \times \Delta I_L \times V_{IN}}$

The ripple current can be given by:

$$\Delta I_{L} = \frac{(V_{IN}^{-}V_{OUT}) \times V_{OUT}}{L \times f_{SW} \times V_{IN}}$$

#### **Output Capacitor Selection**

The output capacitor must have high enough ESR to satisfy the ripple requirements for loop stability. The important parameters of capacitor are the ESR, the capacitance value, the RMS ripple current rating, and the voltage rating. For the output capacitor of APE3312, ESR is the most important parameter. Determine ESR to meet the required ripple voltage as follow:

$$\mathsf{ESR}(\mathsf{m}\Omega) = \frac{\Delta \mathsf{V}_{\mathsf{OUT}}}{\Delta \mathsf{I}_{\mathsf{L}}}$$

A minimum ESR is required to generate the required ripple voltage for regulation. Due to the pseudo fixed frequency PWM mode not contain an error amplifier in the loop; a sufficient feedback signal needs to be provided from output ripple. The VFB required 15mV ripple signal at least. That will generate output ripple  $\Delta V_{OUT} = (VOUT/0.7) \times 15 \text{ mV}$

The capacitor is usually selected by ESR and voltage rating rather than by capacitance value. The conductive polymer capacitors are recommended to proper high capacitance and low ESR.

#### **MOSFET Selection**

Choose a high side MOSFET that has conduction loss equal to the switching loss at the optimum input voltage for maximum efficiency. Choose a low-side MOSFET that has the lowest  $R_{DS-ON}$ . Ensure that the APE3312 DL gate driver can drive low-side MOSFET. The current ability of the N-channel MOSFET must be more than the peak switching current. The voltage rating  $V_{DS}$  of the N-channel MOSFET should be at least 1.25 times the maximum input voltage. Low  $R_{DS-ON}$  MOSFET is for reducing the conduction loss. Low  $C_{ISS}$  MOSFET is for reducing the switching loss. But most of time, this two factors are trade-off. Consider the system requirement and define the MOSFETs rating.

### **APPLICATION INFORMATION (Continued)**

#### **Stability Consideration**

The constant on-time, pseudo fixed frequency PWM scheme has natural frequency jitter. An mV order of noise on the feedback signal affects the frequency jitter from a few to ten percent of switching frequency. Double pulse and feedback loop unstable results in unstable operation. Double pulse occurs because the insufficient ripple at the VFB, or the VFB and VOUT ripple waveforms are very noisy and trigger the VFB comparator. If the ripple voltage of VFB is too small, the VFB waveform will be interfered with switching noise. The noise causes the VFB comparator to trigger too quickly after the 400ns minimum off -time. Double pulse will result in higher output ripple voltage but in most cases is harmless.

#### **Design Procedure**

First of all, specify the external component, input voltage range, output voltage tolerance, load current, and the desired switching frequency. There are two values of load current to consider: continuous and peak load current. Continuous load current is concerned with thermal stresses of MOSFETs. Peak load current determines the components stresses and design of threshold of the current limit. The following guidelines will help calculate the external components of the APE3312 as Typical Application Circuit.

1. Select inductor. Before determine the inductance, the ripple current,  $\Delta I_L$ , must be defined first, typically set between 1/4 to 1/2 of the maximum load current. The ripple current can be defined as:

$$\Delta I_{L} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{L \times f_{SW} \times V_{IN}}$$

The inductor value can be calculated as follows:

$$L = \frac{V_{OUT} \times (V_{IN(max)} - V_{OUT})}{\Delta I_{L} \times f_{SW} \times V_{IN(max)}}$$

The inductor current must be rated for maximum peak current.

$$I_{L(PEAK)} = I_{OC(Valley)} + \Delta I_{L} = \frac{V_{TRIP}}{R_{DS-ON}} + \frac{(V_{IN}^{-}V_{OUT}) \times V_{OUT}}{L \times f_{SW} \times V_{IN}}$$

2. Select R1 and R2. The recommended value for R2 is between  $10k\Omega$  and  $20k\Omega$ . R1 = R2 ×  $(\frac{V_{OUT}-0.7}{0.7})$

3. Choose output capacitor. The output capacitance is based on transient ability.

$$C_{OUT(min)} = \frac{L \times (I_{out(max)} + 0.5\Delta I_L)^2}{\Delta V_{OUT}^2}$$

Determine ESR to meet the required ripple voltage, above 15mV. ESR(m $\Omega$ ) =  $\frac{\Delta V_{OUT}}{\Delta I_L} = \frac{15mV \times V_{OUT}}{\Delta I_L \times 0.7V}$

4. Decide current limit threshold. Determine the current limit threshold when VIN is minimum and load current is maximum conditions. The R<sub>TRIP</sub> determines by

$$\mathsf{R}_{\mathsf{TRIP}}(\Omega) = \frac{\mathsf{R}_{\mathsf{DS}-\mathsf{ON}}}{10\mathsf{u}\mathsf{A}} \times (\mathsf{I}_{\mathsf{OCP}} - \frac{(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{V}_{\mathsf{OUT}}}{2 \times \mathsf{L} \times \mathsf{f}_{\mathsf{SW}} \times \mathsf{V}_{\mathsf{IN}}})$$

### **APPLICATION INFORMATION (Continued)**

#### Layout Considerations

The switching power stages require more attention in PCB layout. Keep the high current paths short. Separate the ground terminals. Four-layer board is recommended. Use two middle layers as ground planes, with interconnections between top and bottom layers as needed. Below lists help start layout work.

- 1. Minimize the resistance by keeping the power component group together with short and wide trace (60mil at least).

- Minimize the high-side path with short and wide trace. This path starts at VIN, goes through the high-side MOSFET, through the inductor, through the output capacitor, through the input capacitor, and back to the input.

- Minimize the low-side high current path. The high current path starts at the ground of the low-side MOSFET, goes through the low-side MOSFET, through the inductor, through the output capacitor, and back to the ground of the low-side MOSFET.

- Power components should be grouped together near the gate drivers. Connect the drivers of DRVH and DRVL close to the gate of high-side and low-side MOSFET with short trace as possible to reduce stray inductance.

- 5. Place feedback resistors R1 and R2 near VFB and GND pin with short wire and should be far away to the noise source, such as switching loop. Use ground plane to shield feedback trace from power components.

- 6. Keep sensitive analog node (VFB, TRIP, and RF) away from high-speed switching loop to avoid noise coupling.

- 7. The current limit setting resistor, R<sub>TRIP</sub>, should connect to TRIP and GND pin directly, next to the IC.

- 8. The frequency setting resistor,  $R_{RF}$ , should next to the IC.

- Group the analog ground connection of the V5IN (V5FILT) bypass capacitors, VFB, RF, and TRIP. Connect the analog ground plane directly to GND pin of the IC.

- 10. Group the power ground connection of the VIN capacitor, VOUT capacitor, and the source of the low-side MOSFETs as close as possible. Connect this power ground plane directly to PGND pin of the IC.

- 11. PGND is used as the positive current sensing node so PGND should be connected to the source terminal of the bottom MOSFET.

- 12. Use plane connection between GND (analog ground) and PGND (power ground) near the IC.

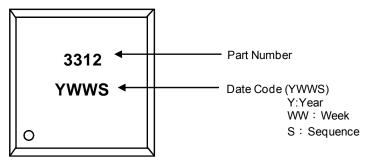

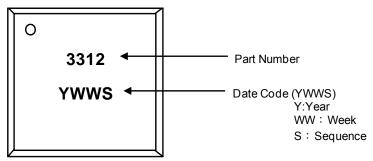

# MARKING INFORMATION

DFN 3x3-10L

QFN 3.5x3.5-14L

# PACKAGE OUTLINE

DFN 3x3-10L

Draw No. 11-N310L-G-v00

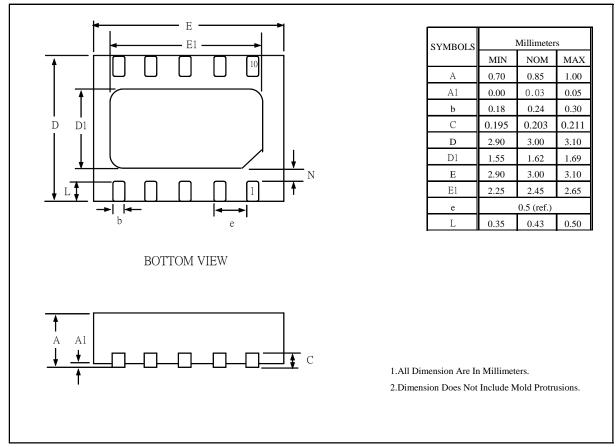

# PACKAGE OUTLINE (Continued)

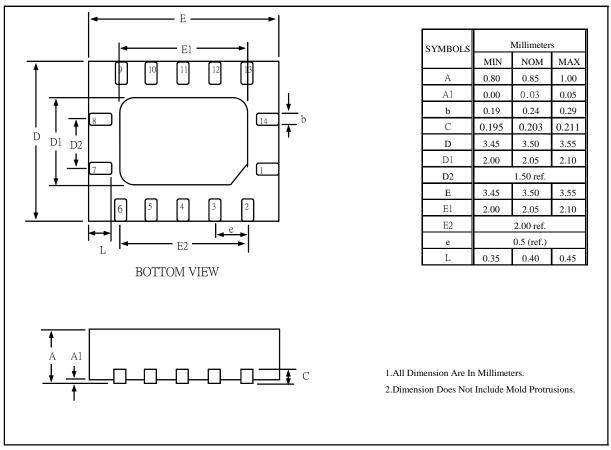

QFN 3.5x3.5-14L

Draw No. 11-VN35-14L-G-v00