## **SRK2000**

## Synchronous rectifier smart driver for LLC resonant converters

#### **Features**

- Secondary-side synchronous rectifier controller optimized for LLC resonant converters

- Protection against current reversal

- Safe management of load transient, light load and startup condition

- Intelligent automatic sleep-mode at light load

- Dual gate driver for N-channel MOSFETs with

1 A source and 3.5 A sink drive current

- Operating voltage range 4.5 to 32 V

- Programmable UVLO with hysteresis

- 250 µA quiescent consumption

- Operating frequency up to 500 kHz

- SO8 package

## **Applications**

- All-in-one PC

- High-power AC-DC adapters

- 80+/85+ compliant ATX SMPS

- 90+/92+ compliant server SMPS

- Industrial SMPS

## **Description**

The SRK2000 smart driver implements a control scheme specific to secondary-side synchronous rectification in LLC resonant converters that use a transformer with center-tap secondary winding for full-wave rectification.

It provides two high-current gate-drive outputs, each capable of driving one or more N-channel Power MOSFETs. Each gate driver is controlled separately and an interlocking logic circuit prevents the two synchronous rectifier MOSFETs from conducting simultaneously.

The control scheme in this IC allows for each synchronous rectifier to be switched on as the

**SO-8**

corresponding half-winding starts conducting and switched off as its current goes to zero. A unique feature of this IC is its intelligent automatic sleep-mode. It allows the detection of a low-power operating condition for the converter and puts the IC into a low consumption sleep-mode where gate driving is stopped and quiescent consumption is reduced. In this way, converter efficiency improves at light load, where synchronous rectification is no longer beneficial. The IC automatically exits sleep-mode and restarts switching as it recognizes that the load for the converter has increased.

A noticeable feature is the very low external component count required.

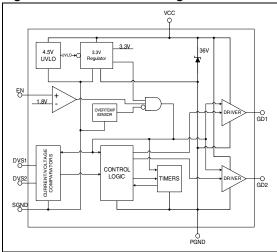

Figure 1. Internal block diagram

Table 1. Device summary

| Order code | Package | Packing       |  |

|------------|---------|---------------|--|

| SRK2000D   | SO-8    | Tube          |  |

| SRK2000DTR | 30-8    | Tape and reel |  |

February 2012 Doc ID 17811 Rev 2 1/17

www.st.com

Contents SRK2000

# **Contents**

| 1 | Pin ( | description 3                         |  |  |  |  |

|---|-------|---------------------------------------|--|--|--|--|

| 2 | Max   | imum ratings                          |  |  |  |  |

| 3 | Турі  | cal application schematic5            |  |  |  |  |

| 4 | Elec  | trical characteristics6               |  |  |  |  |

| 5 | Арр   | lication information                  |  |  |  |  |

|   | 5.1   | EN pin: pin function and usage 8      |  |  |  |  |

|   |       | 5.1.1 Pull-up resistor configuration  |  |  |  |  |

|   |       | 5.1.2 Resistor divider configuration9 |  |  |  |  |

|   |       | 5.1.3 Remote on/off control           |  |  |  |  |

|   | 5.2   | Drain voltage sensing                 |  |  |  |  |

|   | 5.3   | Gate driving                          |  |  |  |  |

|   | 5.4   | Intelligent automatic sleep-mode      |  |  |  |  |

|   | 5.5   | Protection against current reversal   |  |  |  |  |

|   | 5.6   | Layout guidelines                     |  |  |  |  |

| 6 | Pack  | kage mechanical data                  |  |  |  |  |

| 7 | Revi  | sion history                          |  |  |  |  |

SRK2000 Pin description

# 1 Pin description

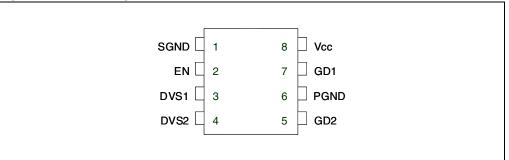

Figure 2. Pin configuration

Table 2. Pin description

| n.     | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SGND         | Signal ground. Return of the bias current of the device and 0 V reference for drain-to-source voltage monitors of both sections. Route this pin directly to PGND.                                                                                                                                                                                                                                                                                                                                                                   |

| 2      | EN           | Drain voltage threshold setting for synchronous rectifier MOSFET turn-off. UVLO threshold programming. This pin is typically biased by either a pull-up resistor connected to Vcc or by a resistor divider sensing Vcc. Pulling the pin to ground disables the gate driver outputs GD1 and GD2 and can therefore be used also as Enable input.                                                                                                                                                                                      |

| 3 4    | DVS1<br>DVS2 | Drain voltage sensing for sections 1 and 2. These pins are to be connected to the respective drain terminals of the corresponding synchronous rectifier MOSFET via limiting resistors. When the voltage on either pin goes negative, the corresponding synchronous rectifier MOSFET is switched on; as its (negative) voltage exceeds a threshold defined by the EN pin, the MOSFET is switched off. An internal logic rejects switching noise, however, extreme care in the proper routing of the drain connection is recommended. |

| 5<br>7 | GD2<br>GD1   | Gate driver output for sections 2 and 1. Each totem pole output stage is able to drive Power MOSFETs with a peak current of 1 A source and 3.5 A sink. The high-level voltage of these pins is clamped at about 12 V to avoid excessive gate voltages in case the device is supplied with a high Vcc.                                                                                                                                                                                                                               |

| 6      | PGND         | Power ground. Return for gate-drive currents. Route this pin to the common point where the source terminals of both synchronous rectifier MOSFETs are connected.                                                                                                                                                                                                                                                                                                                                                                    |

| 8      | Vcc          | Supply voltage of the device. A small bypass capacitor (0.1 µF typ.) to SGND, located as close to the IC's pins as possible, may be useful to obtain a clean supply voltage for the internal control circuitry. A similar bypass capacitor to PGND, again located as close to the IC's pins as possible, may be an effective energy buffer for the pulsed gate-drive currents.                                                                                                                                                      |

Pin description **SRK2000**

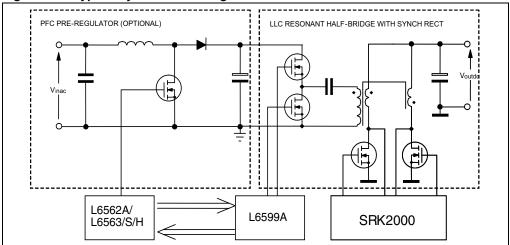

Figure 3. Typical system block diagram

**SRK2000 Maximum ratings**

#### **Maximum ratings** 2

Table 3. **Absolute maximum ratings**

| Symbol                 | Pin     | Parameter Value                                       |                          |    |  |

|------------------------|---------|-------------------------------------------------------|--------------------------|----|--|

| Vcc                    | 8       | DC supply voltage                                     | -0.3 to Vcc <sub>Z</sub> | V  |  |

| Icc <sub>Z</sub>       | 8       | nternal Zener maximum current 25 I                    |                          |    |  |

|                        | 2, 3, 4 | Analog inputs voltage rating -0.3 to Vcc <sub>Z</sub> |                          |    |  |

| I <sub>DVS1,2_sk</sub> | 3, 4    | Analog inputs max. sink current (single pin) 25       |                          | mA |  |

| I <sub>DVS1,2_sr</sub> | 3, 4    | Analog inputs max. source current (single pin) -5     |                          |    |  |

Table 4. Thermal data

| Symbol           | Parameter                                    | Value      | Unit |

|------------------|----------------------------------------------|------------|------|

| $R_{thJA}$       | Max. thermal resistance, junction-to-ambient | 150        | °C/W |

| Ptot             | Power dissipation @ T <sub>A</sub> = 50 °C   | 0.65       | W    |

| T <sub>J</sub>   | Junction temperature operating range         | -40 to 150 | °C   |

| T <sub>stg</sub> | Storage temperature                          | -55 to 150 | °C   |

#### 3 Typical application schematic

L6599A Vin Voutdc <sup>2</sup> **SRK2000**

Figure 4. Typical application schematic

577

Doc ID 17811 Rev 2 5/17 Electrical characteristics SRK2000

## 4 Electrical characteristics

$T_J$  = -25 to 125 °C,  $V_{CC}$  = 12 V,  $C_{GD1}$  =  $C_{GD2}$  = 4.7 nF, EN =  $V_{CC}$ ; unless otherwise specified; typical values refer to  $T_J$  = 25 °C.

Table 5. Electrical characteristics

| Symbol                  | Parameter                                    | Test condition                                   | Min. | Тур.             | Max. | Unit |

|-------------------------|----------------------------------------------|--------------------------------------------------|------|------------------|------|------|

| Supply voltage          |                                              |                                                  |      |                  |      |      |

| V <sub>CC</sub>         | Operating range                              | After turn-on                                    | 4.5  |                  | 32   | V    |

| V <sub>CCOn</sub>       | Turn-on threshold                            | (1)                                              | 4.25 | 4.5              | 4.75 | ٧    |

| V <sub>CCOff</sub>      | Turn-off threshold                           | (1)                                              | 4    | 4.25             | 4.5  | ٧    |

| Hys                     | Hysteresis                                   |                                                  |      | 0.25             |      | ٧    |

| VccZ                    | Zener voltage                                | Icc <sub>Z</sub> = 20 mA                         | 33   | 36               | 39   | ٧    |

| Supply curi             | rent                                         |                                                  |      |                  |      |      |

| I <sub>start-up</sub>   | Startup current                              | Before turn-on, Vcc = 4 V                        |      | 45               | 70   | μΑ   |

| Iq                      | Quiescent current                            | After turn-on                                    |      | 250              | 500  | μΑ   |

| I <sub>CC</sub>         | Operating supply current                     | @ 300 kHz                                        |      | 35               |      | mA   |

| Iq                      | Quiescent current                            | EN = SGND                                        |      | 150              | 250  | μΑ   |

| Drain sensi             | ng inputs and synch functi                   | ons                                              |      |                  |      |      |

| V <sub>DVS1,2_H</sub>   | Upper clamp voltage                          | I <sub>DVS1,2</sub> = 20 mA                      |      | Vcc <sub>Z</sub> |      | ٧    |

| I <sub>DVS1,2_b</sub>   | Input bias current                           | V <sub>DVS1,2</sub> = 0 to Vcc <sup>(2)</sup>    | -1   |                  | 1    | μΑ   |

| V <sub>DVS1,2_A</sub>   | Arming voltage (positive-going edge)         |                                                  |      | 1.4              |      | ٧    |

| V <sub>DVS1,2_PT</sub>  | Pre-triggering voltage (negative-going edge) |                                                  |      | 0.7              |      | V    |

| V <sub>DVS1,2_TH</sub>  | Turn-on threshold                            |                                                  | -250 | -200             | -180 |      |

| I <sub>DVS1,2_On</sub>  | Turn-on source current                       | V <sub>DVS1,2</sub> = -250 mV                    |      | -50              |      | μΑ   |

| V                       | Turn-off threshold                           | $R = 680 \text{ k}\Omega \text{ from EN to Vcc}$ | -18  | -25              | -32  | \/   |

| V <sub>DVS1,2_Off</sub> | (positive-going edge)                        | R = 270 k $\Omega$ from EN to Vcc                | -9   | -12.5            | -16  | mV   |

| T <sub>PD_On</sub>      | Turn-on debounce delay                       | After sourcing I <sub>DS1,2_On</sub>             |      | 250              |      | ns   |

| T <sub>PD_Off</sub>     | Turn-off propagation delay                   | After crossing V <sub>DS1,2_Off</sub>            |      |                  | 60   | ns   |

| T <sub>ON_min</sub>     | Minimum on-time                              |                                                  |      | 150              |      | ns   |

| D <sub>OFF</sub>        | Min. operating duty-cycle                    |                                                  |      | 40               |      | %    |

| D <sub>ON</sub>         | Restart duty-cycle                           |                                                  |      | 60               |      | %    |

| Gate-drive              | enable function                              |                                                  |      |                  |      |      |

| V <sub>EN_On</sub>      | Enable threshold                             | Positive-going edge (1)                          | 1.7  | 1.8              | 1.9  | ٧    |

| Hyst                    | Hysteresis                                   | Below V <sub>EN_On</sub>                         |      | 45               |      | mV   |

|                         | 1                                            | ı.                                               |      |                  |      |      |

Table 5. Electrical characteristics (continued)

| Symbol                | Parameter                    | Test condition                               | Min.  | Тур. | Max. | Unit |  |

|-----------------------|------------------------------|----------------------------------------------|-------|------|------|------|--|

| I <sub>EN</sub>       | Bias current                 | $V_{EN} = V_{EN\_On}$                        |       |      | 1    | μΑ   |  |

| Turn-off thr          | Turn-off threshold selection |                                              |       |      |      |      |  |

| V <sub>EN-Th</sub>    | Selection threshold          | V <sub>CC</sub> = V <sub>CCOn</sub>          | 0.32  | 0.36 | 0.40 | ٧    |  |

| I <sub>EN</sub>       | Pull-down current            | $V_{EN} = V_{EN\_Th}, V_{CC} = V_{CCOn}$     | 7     | 10   | 13   | μΑ   |  |

| Gate drivers          | s                            |                                              |       |      |      |      |  |

| V                     | Output high voltage          | I <sub>GDsource</sub> = 5 mA                 | 11.75 | 11.9 |      | V    |  |

| V <sub>GDH</sub>      | Output high voltage          | I <sub>GDsource</sub> = 5 mA, Vcc = 5 V      | 4.75  | 4.9  |      |      |  |

| V.                    | Output low voltage           | I <sub>GDsink</sub> = 200 mA                 |       | 0.2  |      | V    |  |

| V <sub>GDL</sub>      | Output low voltage           | I <sub>GDsink</sub> = 200 mA, Vcc = 5 V      |       | 0.2  |      |      |  |

| I <sub>sourcepk</sub> | Output source peak current   |                                              |       | -1   |      | Α    |  |

| I <sub>sinkpk</sub>   | Output sink peak current     |                                              |       | 3.5  |      | Α    |  |

| t <sub>f</sub>        | Fall time                    |                                              |       | 18   |      | ns   |  |

| t <sub>r</sub>        | Rise time                    |                                              |       | 40   |      | ns   |  |

| V <sub>GDclamp</sub>  | Output clamp voltage         | I <sub>GDsource</sub> = 5 mA; Vcc = 20 V     | 12    | 13   | 15   | ٧    |  |

| V <sub>GDL_UVLO</sub> | UVLO saturation              | Vcc = 0 to V <sub>CCon</sub><br>Isink = 5 mA |       | 1    | 1.3  | ٧    |  |

<sup>1.</sup> Parameters tracking each other.

<sup>2.</sup> For Vcc>30 V I<sub>DVS1,2\_b</sub> may be greater than 1  $\mu$ A because of the possible current contribution of the internal clamp Zener (few tens of  $\mu$ A).

## 5 Application information

### 5.1 EN pin: pin function and usage

This pin can perform three different functions: it sets the threshold  $V_{DVS1,2\_Off}$  for the drain-to-source voltage of either synchronous rectifier (SR) Power MOSFET to determine their turn-off in each conduction cycle; it allows the user to program the UVLO thresholds of the gate drivers and can be used as Enable (remote on/off control).

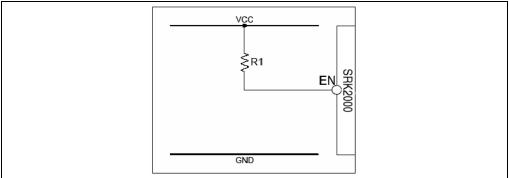

### 5.1.1 Pull-up resistor configuration

At startup, an internal 10  $\mu$ A current sink (I<sub>EN</sub>) is active as long as the device supply voltage Vcc is below the startup threshold V<sub>CCOn</sub>. The moment Vcc equals V<sub>CCOn</sub> (4.5 V typ.), the voltage V<sub>EN</sub> on the EN pin determines the turn-off threshold V<sub>DVS1,2\_Off</sub> for the drain voltage of both synchronous rectifiers during their cycle-by-cycle operation: if V<sub>EN</sub> < V<sub>EN\_Th</sub> (= 0.36 V) the threshold is set at -25 mV, otherwise at -12 mV. Once the decision is made, the setting is frozen as long as Vcc is greater than the turn-off level V<sub>CCOff</sub> (4.25 V typ.).

A simple pull-up resistor  $R_1$  to Vcc can be used to set  $V_{DVS1,2\_Off}$  turn-off threshold. The voltage on the EN pin as the device turns on is given by:

$$V_{EN} = V_{CCOn} - I_{EN} R1$$

Then, considering worst-case scenarios, we have:

$$R1 > 633 \text{ k}\Omega \quad - \quad V_{\text{DVS1,2}\_\text{Off}} = -25 \text{ mV}$$

$$R1 < 296 \ k\Omega \quad - \quad V_{DVS1,2\_Off} = - \ 12 \ mV$$

Some additional margin (equal to the resistor's tolerance) needs to be considered; assuming 5% tolerance, the use of the standard values  $R_1 = 680 \text{ k}\Omega$  in the first case and  $R_1 = 270 \text{ k}\Omega$  in the second case, is suggested.

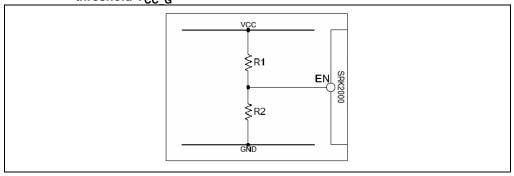

Figure 5. EN pin biased with a pull-up resistor (for logic-level MOSFET driving)

As Vcc exceeds  $V_{CCOn}$ , the internal current sink  $I_{EN}$  is switched off and the enable function is activated. The voltage on the pin is then compared to an internal reference  $V_{EN}$  on set at

1.8 V: if this threshold is exceeded the gate drivers GD1 and GD2 are enabled and the SR MOSFET is operated; otherwise, the device stays in an idle condition and the SR MOSFET in the off state.

Using the pull-up resistor  $R_P$  the voltage on the EN pin rises as  $I_{EN}$  is switched off and tends to Vcc, therefore exceeding  $V_{EN\_On}$  and enabling the operation of both SR MOSFETs. Essentially, this results in enabling the gate-driving as Vcc exceeds  $V_{CCOn}$  and disabling it as Vcc falls below  $V_{CCOn}$ . This configuration is thereby recommended when SR MOSFETs are logic-level types.

### 5.1.2 Resistor divider configuration

To enable gate-driving with a Vcc voltage higher than a predefined value  $V_{CC\_G}$ , to properly drive a standard SR MOSFET, the EN pin is biased by a resistor divider (R1 upper resistor, R2 lower resistor) whose value is chosen so as to exceed  $V_{EN\_On}$  when  $V_{CC\_G}$  and also to set the desired  $V_{DVS1,2\_Off}$  level. Note that, with a falling  $V_{CC}$ , gate-driving is disabled at a Vcc level about 2.5% lower than  $V_{CC\_G}$ , because of the 45 mV hysteresis of the comparator.

The equations that describe the circuit in the two crucial conditions  $Vcc = V_{CCOn}$  (when the decision of the  $V_{DVS1,2\_Off}$  level is made) and  $Vcc = V_{CC\_G}$  (when gate-driving is to be enabled) are respectively:

Figure 6. EN pin biased with a resistor divider to program the gate-drive UVLO threshold  $V_{CC\ G}$

#### **Equation 1**

$$\begin{cases} \frac{V_{CCOn} - V_{EN}}{R1} = I_{EN} + \frac{V_{EN}}{R2} \\ V_{CC\_G} \frac{R2}{R1 + R2} = V_{EN\_On} \end{cases}$$

Solving these equations for  $R_1$  and  $R_2$  we get:

#### **Equation 2**

$$\begin{cases} R1 = \frac{V_{CCOn} - V_{EN}}{V_{EN}} \frac{V_{CC\_G}}{V_{EN\_On}} \\ R2 = R1 \frac{V_{EN\_On}}{V_{CC\_G} - V_{EN\_On}} \end{cases}$$

If  $V_{CC\_G}$  is not too low (<8÷9 V), its tolerance is not critical because it is related only to that of  $V_{EN\_On}$  (±5.6%) and of the external resistors R1, R2 (±1% each is recommended). Then, some care needs to be taken only as far as the selection of the -12/-25 mV threshold is concerned: in fact, the large spread of  $I_{EN}$  considerably affects the voltage on the EN pin as the device turns on, a value that can be found by solving the first of (1) for  $V_{EN}$ :

#### **Equation 3**

$$V_{EN} = \frac{V_{CCOn} - I_{EN}R1}{1 + \frac{R1}{R2}}$$

A couple of examples clarify the suggested calculation methodology.

**Example 1**

$$V_{CC}$$

G = 10 V,  $V_{DVS1.2}$  Off = - 25 mV.

In this case,  $V_{EN}$  must definitely be lower than the minimum value of  $V_{EN\_Th}$  (= 0.32 V). From the second of (2), the nominal ratio of R1 to R2 is (10-1.8)/1.8 = 4.555. Substituting the appropriate extreme values in (3) it must be  $(4.75 - 7 \cdot 10^{-6} \cdot R1)/(1 + 4.555) < 0.32$ ; solving for R1 yields R1 > 425 k $\Omega$ ; let us consider an additional 4% margin to take both the tolerance and the granularity of the R1 and R2 values into account, so that: R1 > 425 \cdot 1.04 = 442 k $\Omega$  Choose R1 = 442 k $\Omega$  (E48 standard value) and, from the second of (2), R2 = 442/4.555 = 97 k $\Omega$ ; use 97.6 k $\Omega$  (E48 standard value).

**Example 2**

$$V_{CC}$$

$_{G}$  = 10 V,  $V_{DVS1.2}$   $_{Off}$  = - 12 mV.

In this case, V<sub>EN</sub> must definitely be higher than the maximum value of V<sub>EN\_Th</sub> (= 0.40 V). From the second of (2), the nominal ratio of R1 to R2 is (10 – 1.8) / 1.8 = 4.555. Substituting the appropriate extreme values in (3) it must be (4.25 - 13·10<sup>-6</sup>·R1) / (1 + 4.555) > 0.4; solving for R1 yields R1 < 156 k $\Omega$ ; with 4% additional margin R1 < 156/1.04 = 150 k $\Omega$  Choose R1 = 147 k $\Omega$  (E48 standard value) and, from the second of (2), R2 = 147/4.555 = 32.3 k $\Omega$ ; use 32.4 k $\Omega$  (E48 standard value).

Note: In both examples the gate drivers are disabled as Vcc falls below 9.75 V (nominal value), as the voltage on the EN pin falls 45 mV below  $V_{EN On}$ .

57

#### 5.1.3 Remote on/off control

Whichever configuration is used, since a voltage on the EN pin 45 mV below  $V_{EN\_On}$  disables the gate drivers, any small-signal transistor can be used to pull down the EN pin and force the gate drivers into an off state.

Finally, it should be noted that during power-up, power-down, and under overload or short-circuit conditions, the gate drivers are shut down if the Vcc voltage is insufficient: < V<sub>CCOff</sub> in case of pull-up resistor configuration, < 0.975  $PV_{CC\_G}$  in case of resistor divider configuration (the coefficient 0.975 depends on the hysteresis on the Enable pin threshold).

### 5.2 Drain voltage sensing

In the following explanations it is assumed that the reader is familiar with the LLC resonant half bridge topology and its waveforms, especially those on the secondary side with a center-tap transformer winding for full-wave rectification.

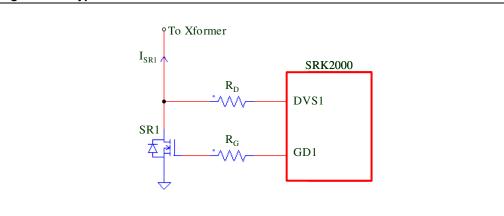

To understand the polarity and the level of the current flowing in the SR MOSFETs (or their body diodes, or diodes in parallel to the MOSFETs) the IC is provided with two pins, DVS1-2, able to sense the voltage level of the MOSFET drains.

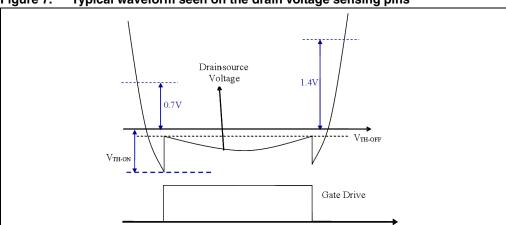

Figure 7. Typical waveform seen on the drain voltage sensing pins

The logic that controls the driving of the two SR MOSFETs is based on two gate-driver state machines working in parallel in an interlocked way to avoid both gate drivers being switched on at the same time.

There are four significant drain voltage thresholds: the first one,  $V_{DVS1,2\_A}$  (= 1.4 V), sensitive to positive-going edges, arms the opposite gate driver (interlock function); the second,  $V_{DVS1,2\_PT}$  (=0.7 V), sensitive to negative-going edges, provides a pre-trigger of the gate driver; the third is the (negative) threshold  $V_{TH-ON}$  that triggers the gate driver as the body diode of the SR MOSFET starts conducting; the fourth is the internal (negative) threshold  $V_{DVS1,2\_Off}$  where the SR MOSFET is switched off (selectable between -12 mV or -25 mV by properly biasing the EN pin).

The value of the ON threshold  $V_{TH-ON}$  is affected by the external resistor in series to each DVS1-2 pin needed essentially to limit the current that might be injected into the pins when one SR MOSFET is off and the other SR MOSFET is conducting. In fact, on the one hand, when one MOSFET is off (and the other one is conducting), its drain-to-source voltage is

57

Doc ID 17811 Rev 2 11/17

slightly higher than twice the output voltage; if this exceeds the voltage rating of the internal clamp (Vcc<sub>Z</sub> = 36 V typ.), a series resistor R<sub>D</sub> must limit the injected current below an appropriate value, lower than the maximum rating (25 mA) and taking the related power dissipation into account. On the other hand, when current starts flowing into the body diode of one MOSFET (or in the diode in parallel with the MOSFET), the drain-to-source voltage is negative ( $\cong$  -0.7 V); when the voltage on pins DVS1,2 reaches the threshold V<sub>DVS1,2\_TH</sub> (-0.2V typ.), an internal current source I<sub>DVS1,2\_On</sub> is activated; as this current exceeds 50  $\mu$ A, the gate of the MOSFET is turned on. Therefore, the actual triggering threshold can be determined by the following formula:

$$V_{TH-ON} = R_D \cdot I_{DVS1,2On} + V_{DVS1,2}$$

TH

For instance, with R<sub>D</sub> = 2 k $\Omega$ , the triggering threshold is located at - (2 k $\Omega$  · 50  $\mu$ A) - 0.2 V = -0.3 V.

To avoid false triggering of the gate driver, a debounce delay  $T_{PD\_On}$  (= 250 ns) is used after sourcing  $I_{DS1,2\_On}$  (i.e. the current sourced by the pin must exceed 50  $\mu$ A for more than 250 ns before the gate driver is turned on). This delay is not critical for the converter's efficiency because the initial current is close to zero or anyway much lower than the peak value.

Once the SR MOSFET has been switched on, its drain-to-source voltage drops to a value given by the flowing current times the MOSFET  $R_{DS(on)}$ . Again, since the initial current is low, the voltage drop across the  $R_{DS(on)}$  may exceed the turn-off threshold  $V_{DVS1,2\_Off}$ , and determine an improper turn-off. To prevent this, the state machine enables the turn-off comparator referenced to  $V_{DVS1,2\_Off}$  only in the second half of the conduction cycle, based on the information of the duration of the previous cycle. In the first half of the conduction cycle only an additional comparator, referenced to zero, is active to prevent the current of the SR MOSFET from reversing, which would impair the operation of the LLC converter.

Once the threshold  $V_{DVS1,2\_Off}$  is crossed (in the second half of the conduction cycle) and the GATE is turned off, the current again flows through the body diode causing the drain-to-source voltage to have a negative jump, going again below  $V_{TH-ON}$ . The interlock logic, however, prevents a false turn-on. It is worth pointing out that, due to the fact that each MOSFET is turned on after its body diode starts conducting, the ON transition happens with the drain-source voltage equal to the body diode forward drop; therefore there is neither a Miller effect nor switching losses at MOSFET turn-on. Also at turn-off the switching losses are not present, in fact, the current is always flowing from source to drain and, when the MOSFET is switched off, it goes on flowing through the body diode (or the external diode in parallel to the MOSFET).

Unlike at turn-on, the turn-off speed is critical to avoid current reversal on the secondary side, especially when the converter operates above the resonance frequency, where the current flowing through the MOSFET exhibits a very steep edge while decreasing down to zero: the turn-off propagation  $T_{PD\ Off}$  delay has a maximum value of 60 ns.

The interlock logic, in addition to checking for consistent secondary voltage waveforms (one MOSFET can be turned on only if the other one has a positive drain-to-source voltage >  $V_{DVS1,2\_A}$ ) to prevent simultaneous conduction, allows only one switching per cycle: after one gate driver has been turned off, it cannot be turned on again before the other gate drive has had its own on/off cycle.

The IC logic also prevents unbalanced current in the two SR MOSFETs: if one SR MOSFET fails to turn on in one cycle, the other SR MOSFET is also not turned on in the next cycle.

Figure 8. Typical connection of the SRK2000 to the SR MOSFET

### 5.3 Gate driving

The IC is provided with two high-current gate-drive outputs (1 A source and 3.5 A sink), each capable of driving one or more N-channel Power MOSFETs. Thanks to the programmable gate-drive UVLO, it is possible to drive both standard MOSFETs and logic level MOSFETs.

The high-level voltage provided by the driver is clamped at  $V_{GDclamp}$  (=12 V) to avoid excessive voltage levels on the gate in case the device is supplied with a high Vcc.

The two gate drivers have a pull-down capability that ensures the SR MOSFETs cannot be spuriously turned on even at low Vcc: in fact, the drivers have a 1 V (typ.) UVLO saturation level at Vcc below the turn-on threshold.

## 5.4 Intelligent automatic sleep-mode

A unique feature of this IC is its intelligent automatic sleep-mode. The logic circuitry is able to detect a light load condition for the converter and stop gate driving, also reducing the IC's quiescent consumption. This improves converter efficiency at light load, where the power losses on the rectification body diodes (or external diodes in parallel to the MOSFETs) go lower than the power losses in the MOSFETs and those related to their driving.

The IC is also able to detect an increase of the converter's load and automatically restart gate driving.

The algorithm used by the intelligent automatic sleep-mode is based on a dual time measurement system. The duration of a switching cycle of an SR MOSFET (that is one half of the resonant converter switching period) is measured using a combination of the negative-going edge of the drain-to-source voltage falling below  $V_{DVS1,2\_PT}$  and the positive-going edge exceeding  $V_{DVS1,2\_A}$ ; the duration of the SR MOSFET conduction is measured from the moment its body diode starts conducting (drain-to-source voltage falling below  $V_{TH-ON}$ ) to the moment the gate drive is turned off (in case the device is operating) or the moment the body diode ceases to conduct (drain-to-source voltage going over  $V_{TH-ON}$ ). While at full load the SR MOSFET conduction time occupies almost 100% of the switching cycle, as the load is reduced, the conduction time is reduced and as it falls below 40% ( $D_{OFF}$ ) of the SR MOSFET switching cycle the device enters sleep-mode. To prevent

57

Doc ID 17811 Rev 2 13/17

erroneous decisions, the sleep-mode condition must be confirmed for 16 consecutive switching cycles of the resonant converter (i.e. 16 consecutive cycles for each SR MOSFET of the center-tap).

Once in sleep-mode, SR MOSFET gate driving is re-enabled when the conduction time of the body diode (or the external diodes in parallel to the MOSFET) exceeds 60% (D<sub>ON</sub>) of the switching cycles. Also in this case the decision is made considering the measurement on 8 consecutive switching cycles (i.e. 8 consecutive cycles for each SR MOSFET of the centertap). Furthermore, after each sleep-mode entering/exiting transition, the timing is ignored for a certain number of cycles, to let the resulting transient in the output current fade out; then the time check is enabled. The number of ignored resonant converter switching cycles is 128 after entering sleep-mode and 256 after exiting sleep-mode.

### 5.5 Protection against current reversal

The IC provides protection against SR MOSFET current reversal. If a current reversal condition is detected for two consecutive switching cycles, the IC goes into sleep-mode, avoiding the turn-on of the SR MOSFETs until a safe condition is restored.

### 5.6 Layout guidelines

The IC is designed with two grounds, SGND and PGND.

SGND is used as the ground reference for all the internal high-precision analog blocks, while PGND is the ground reference for all the noisy digital blocks, as well as the current return for the gate drivers. In addition, it is also the ground for the ESD protection circuits. SGND is protected by ESD events versus PGND through two anti-parallel diodes.

When laying out the PCB, make sure to keep the source terminals of both SR MOSFETs as close as possible to one another and to route the trace that goes to PGND separately from the load current return path. This trace should be as short as possible and be as close to the physical source terminals as possible. A layout that is as geometrically symmetrical as possible helps the circuit to operate in the most electrically symmetrical way as possible. SGND should be directly connected to PGND using a path as short as possible (under the device body).

Also drain voltage sensing should be performed as physically close to the drain terminals as possible: any stray inductance crossed by the load current that is in the drain-to-source voltage sensing circuit may significantly alter the current reading, leading to a premature turn-off of the SR MOSFET. It is worth mentioning that, especially in higher power applications or at higher operating frequencies, even the stray inductance of the internal wire bonding can be detrimental. In this case, a cautious selection of the SR MOSFET package is required.

The use of bypass capacitors between Vcc and both SGND and PGND is recommended. They should be low-ESR, low-ESL types and located as close to the IC pins as possible. Sometimes a series resistor (in the tens) between the converter's output voltage and the Vcc pin, forming an RC filter along with the bypass capacitor, is useful in order to get a cleaner Vcc voltage.

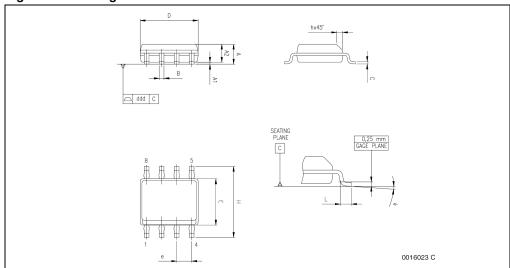

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Table 1. SO-8 mechanical data

| Dim.   | mm.  |                      |      | inch  |       |       |

|--------|------|----------------------|------|-------|-------|-------|

| Dilli. | Min. | Тур.                 | Max. | Min.  | Тур.  | Max.  |

| Α      | 1.35 |                      | 1.75 | 0.053 |       | 0.069 |

|        |      |                      |      |       |       |       |

| A1     | 0.10 |                      | 0.25 | 0.004 |       | 0.010 |

| A2     | 1.10 |                      | 1.65 | 0.043 |       | 0.065 |

| В      | 0.33 |                      | 0.51 | 0.013 |       | 0.020 |

| С      | 0.19 |                      | 0.25 | 0.007 |       | 0.010 |

| D (1)  | 4.80 |                      | 5.00 | 0.189 |       | 0.197 |

| Е      | 3.80 |                      | 4.00 | 0.15  |       | 0.157 |

| е      |      | 1.27                 |      |       | 0.050 |       |

| Н      | 5.80 |                      | 6.20 | 0.228 |       | 0.244 |

| h      | 0.25 |                      | 0.50 | 0.010 |       | 0.020 |

| L      | 0.40 |                      | 1.27 | 0.016 |       | 0.050 |

| k      |      | 0° (min.), 8° (max.) |      |       |       |       |

| ddd    |      |                      | 0.10 |       |       | 0.004 |

D dimensions do not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs should not exceed 0.15 mm (.006 inch) in total (both sides).

Figure 9. Package dimensions

Doc ID 17811 Rev 2

15/17

Revision history SRK2000

# 7 Revision history

Table 6. Document revision history

| Date        | Revision | Changes                                                                                      |

|-------------|----------|----------------------------------------------------------------------------------------------|

| 10-Aug-2010 | 1        | Initial release.                                                                             |

| 08-Feb-2012 | 2        | Minor text changes to improve readability in features, on cover page, and <i>Chapter 5</i> . |

|             |          | Added Chapter 5.5: Protection against current reversal.                                      |

|             |          | Document status promoted from preliminary data to datasheet.                                 |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION). OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2012 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

577

Doc ID 17811 Rev 2

17/17