Product Specification

# RJ45 Modular Stacked Jack With Integrated Magnetics and Integrated Power over Ethernet (PoE)

# 1. SCOPE

# 1.1. Content

This specification covers the performance, tests and quality requirements for the Tyco Electronics Right Angle Stacked RJ45 with LED's and Power over Ethernet (PoE) capability designed for intra-building use only. The RJ45 Modular Stacked Jack With Integrated Magnetics and Integrated PoE integrates new and existing technologies into a single connector unit that provides power compliant to IEEE Standard 802.3af to devices through a standard RJ45 modular jack by sharing data contacts.

# 1.2. Qualification

When tests are preformed on the subject product line, procedures specified in Figure 1 shall be used. All inspections shall be performed using the applicable inspection plan and product drawing.

#### 1.3. Qualification Test Results

Successful qualification testing on the subject product line was completed on 10Apr07. The Qualification Test Report number for this testing is 501-653. This documentation is on file at and available from Engineering Practices and Standards (EPS).

# 2. APPLICABLE DOCUMENTS

The following documents form a part of this specification to the extent herein. Unless otherwise specified, the latest edition of the document applies. In the even of conflict between the requirements of this specification and the product drawing, the product drawing shall take precedence. In the event of conflict between the requirements of this specification and the referenced documents, this specification shall take precedence.

- 2.1. Tyco Electronics Documents

- 109-197: Test Specification (AMP Test Specifications vs EIA and IEC Test Methods)

- 501-653: Qualification Test Report (RJ45 Modular Stacked Jack With Integrated Magnetics and Integrated Power Over Ethernet (PoE))

# 2.2. Commercial Standards

- EIA-364: Electrical Connector/Socket Test Procedure Including Environmental Classifications

- ANSI X3.263: Information Technology Fibre Distributed Interface (MDI) Token Ring Twisted Pair Physical Layer Medium Dependent (TP-PDM)

- IEEE 802.3: Local Area Network; Carrier Sense Multiple Access With Collision Detection (CSMA/CD) Access Method and Physical Layer Specification

- TIA-568-A: Commercial Building Telecommunications Cabling Standards

#### 3. REQUIREMENTS

#### 3.1. Design and Construction

Product shall be of the design, construction and physical dimensions specified on the applicable product drawing.

| ©2007 Tyco Electronics Corporation | * Trademark      | For latest revision, visit our website at www.tycoelectronics.com\documents. | 1 of 11 |

|------------------------------------|------------------|------------------------------------------------------------------------------|---------|

| Harrisburg, PA                     | Indicates change |                                                                              | 10111   |

| All International Rights Reserved. |                  | For Regional Customer Service, visit our website at www.tycoelectronics.com  | LOC B   |

# 3.2. Materials

Materials used in the construction of this product shall be as specified on the applicable product drawing.

#### 3.3. Ratings

- Voltage: 48 volts DC for signal pairs, 2 volts DC for LED signals

- Current:

- 0.1 ampere maximum per signal contact

- 0.020 ampere maximum for LED signals

- 0.275 ampere maximum per contact, PoE contact, RJ45

- 1.5 ampere maximum per contact, host board connector, 48 volts DC, PoE contacts only Integrated and Enabled PoE connectors only

- Temperature:

- Storage: -40 to 85°C

- Operating: 0 to 70°C

- Operating: 0 to 50°C, Integrated PoE only

- 3.4. Performance and Test Description

Product is designed to meet the electrical, mechanical, and environmental performance requirements specified in Figure 1. Unless otherwise specified, all tests shall be performed at the ambient environmental conditions per EIA-364.

# 3.5. Test Requirements and Procedure Summary

| Test Description                                                    | Requirement                            | Procedure                                                                                                                                                                                                                                                           |  |  |  |

|---------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Examination of product.                                             | Meets requirements of product drawing. | EIA-364-18.<br>Visual and dimensional (C of C)<br>inspection per product drawing.                                                                                                                                                                                   |  |  |  |

|                                                                     | ELECTRICAL                             |                                                                                                                                                                                                                                                                     |  |  |  |

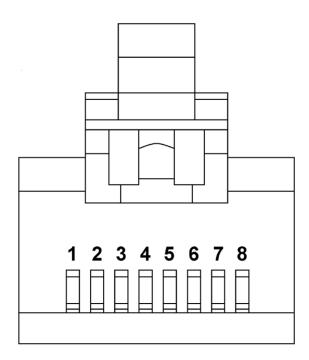

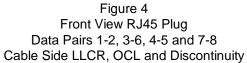

| Low-level contact resistance, RJ45 interface, cable and board side. | ΔR 40 milliohms maximum.               | EIA-364-23.<br>Subject specimens to 100<br>milliamperes maximum and 20<br>millivolts maximum open circuit<br>voltage. Measure the DC resistance<br>across each of the 4 signal pairs on<br>the RJ45 interface (pins 1-2, 3-6,<br>4-5, 7-8).<br>See Figures 4 and 5. |  |  |  |

| Open Circuit Inductance (OCL), cable side only.                     | 350 μh minimum.                        | ANSI X3.263, ref IEEE 802.3.<br>Measure and record OCL across<br>the signal pairs of mated specimens<br>at 100 kHz, 100 millivolts, 8<br>milliamperes DC bias, and 25°C at<br>the RJ45 interface.                                                                   |  |  |  |

Figure 1 (continued)

| Test Description                    | Requirement                                                                                   | Procedure                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Insulation resistance.              | 500 megohms minimum.                                                                          | EIA-364-21.<br>Test between adjacent contacts of<br>mated specimens that are not<br>electrically connected (pairs 3-4, 4-5<br>and 6-7). 500 volts DC, 2 minute<br>hold.                                                                                                                                                                                                     |

| Withstanding voltage.               | 1 minute hold with no breakdown or<br>flashover.                                              | EIA-364-20.<br>For mated plug and jack, all ports:<br>1500 volts AC RMS between<br>adjacent plug and PCB contacts,<br>including shield that is not<br>electrically connected, 15<br>milliamperes cutoff current, 500<br>volts per second maximum ramp.<br>All bridged on either side of<br>magnetics package for RJ45<br>contacts. 60 second dwell.<br>See Figures 7 and 8. |

| Crosstalk (NEXT).                   | 33 - 20 X log (F/50) dB minimum<br>from 1 to 100 MHz.                                         | EIA-568-A.                                                                                                                                                                                                                                                                                                                                                                  |

| Insertion loss.                     | 1.3 dB maximum from 0.5 to 100<br>MHz.                                                        | EIA-568-A.                                                                                                                                                                                                                                                                                                                                                                  |

| Return loss.                        | 18 dB minimum from 0.5 to 40 MHz.<br>12 - 20 X log (F/80) dB minimum<br>from 40.1 to 100 MHz. | EIA-568-A.                                                                                                                                                                                                                                                                                                                                                                  |

| Common Mode Rejection Ratio (CMRR). | 30 dB minimum, 1 to 50 MHz.<br>17 dB minimum, 50.1 to 100 MHz.                                | Procedure details appear in test report EMEB048380-005.                                                                                                                                                                                                                                                                                                                     |

| Functional test: PoE.               | All PoE electronics shall function properly.                                                  | Verify PoE functions using<br>PowerDsine/Microsemi integrated<br>PoE test equipment.                                                                                                                                                                                                                                                                                        |

| Functional test: LEDs.              | All LEDs shall illuminate.                                                                    | Using a current limiting power<br>supply, apply 5 volts in both<br>directions to all LEDs.                                                                                                                                                                                                                                                                                  |

|                                     | MECHANICAL                                                                                    |                                                                                                                                                                                                                                                                                                                                                                             |

| Vibration, random.                  | Monitor for discontinuities.<br>See Note.                                                     | EIA-364-28, Test Condition VII,<br>Condition D.<br>Subject mated specimens to 3.10<br>G's rms between 20-500 Hz. Fifteen<br>minutes in each of 3 mutually<br>perpendicular planes. Loopback<br>contacts on plug side. No loopback<br>needed on PCB side.<br>See Figure 4.                                                                                                   |

Figure 1 (continued)

108-2178

| Test Description              | Requirement                                                                                                                | Procedure                                                                                                                                                                                                                                                                                                              |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Durability.                   | See Note.                                                                                                                  | EIA-364-9.<br>Mate and unmate specimens with<br>the plug locking tab inoperable for<br>500 cycles at a maximum rate of<br>600 cycles per hour.                                                                                                                                                                         |

| Mechanical shock.             | Monitor for discontinuities.<br>See Note.                                                                                  | EIA-364-27, Condition H.<br>Subject mated specimens to 30 G's<br>half-sine shock pulses of 11<br>milliseconds duration. Three shocks<br>in each direction applied along 3<br>mutually perpendicular planes, 18<br>total shocks. Loopback contacts on<br>plug side. No loopback needed on<br>PCB side.<br>See Figure 4. |

| Mating force.                 | 20.02 N [4.5 lbf] maximum.<br>See Note.                                                                                    | EIA-364-13.<br>Measure force necessary to mate<br>specimens at a maximum rate of<br>12.7 mm [0.5 in] per minute.                                                                                                                                                                                                       |

| Unmating force.               | 20.02 N [4.5 lbf] maximum.<br>See Note.                                                                                    | EIA-364-13.<br>Measure force necessary to unmate<br>specimens with the plug locking tab<br>inoperable at a maximum rate of<br>12.7 mm [0.5 in] per minute.                                                                                                                                                             |

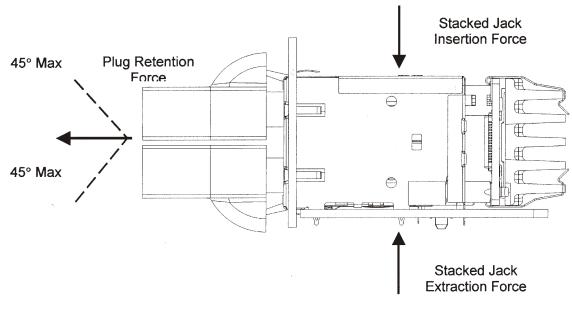

| Plug retention in jack.       | 35.59 N [8 lbf] minimum. Show no<br>evidence of physical damage to the<br>jack, plug shall not disengage from<br>the jack. | EIA-364-98.<br>Subject specimens to specified<br>force applied for 1 minute in 4<br>directions with plug mated in jack<br>and latch engaged, plus axial pull.<br>See Figure 6.                                                                                                                                         |

| Press fit insertion force.    | 6668 N [1500 lbf] maximum.                                                                                                 | Measure force necessary to press<br>connector assembly onto printed<br>circuit board into proper seating<br>location.<br>See Figure 6.                                                                                                                                                                                 |

| Press fit extraction force.   | 445 N [100 lbf] minimum.                                                                                                   | Measure force necessary to extract<br>connector assembly from printed<br>circuit board.<br>See Figure 6.                                                                                                                                                                                                               |

|                               | ENVIRONMENTAL                                                                                                              |                                                                                                                                                                                                                                                                                                                        |

| Thermal shock.                | See Note.                                                                                                                  | EIA-364-32.<br>Subject mated specimens to 5<br>cycles between -40 and 85 +3/-0°C<br>with 60 minute dwell at temperature<br>extremes.                                                                                                                                                                                   |

| Humidity/temperature cycling. | See Note.                                                                                                                  | EIA-364-31, Method IV.<br>Subject mated specimens to 10<br>cycles (10 days) between 25 and<br>65°C at 80 to 100% RH.                                                                                                                                                                                                   |

Figure 1 (continued)

108-2178

| Test Description                                | Requirement                                               | Procedure                                                                                                              |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Temperature life.                               | See Note.                                                 | EIA-364-17, Method A, Test<br>Condition 2, Test Time Condition C.<br>Subject mated specimens to 85°C<br>for 500 hours. |  |  |  |

| Mixed flowing gas.                              | See Note.                                                 | EIA-364-65, Class IIA.<br>Subject mated specimens to<br>environmental Class IIA for 14 days.                           |  |  |  |

| Electrical performance at temperature extremes. | Meets Insertion Loss (IL) and OCL, requirements for part. | Measure at 0 and 50 $\pm$ 5°C for standard parts.                                                                      |  |  |  |

NOTE

Shall meet visual requirements, show no physical damage, and meet requirements of additional tests as specified in the Product Qualification and Requalification Test Sequence shown in Figure 2.

Figure 1 (end)

#### 3.6 Qualification Tests and Sequences

|                                                | Test Groups (a)   |        |        |        |        |        |      |        |

|------------------------------------------------|-------------------|--------|--------|--------|--------|--------|------|--------|

| Test or Examination                            | 1(g)              | 2(g)   | 3(g)   | 4(b,g) | 5(b,g) | 6(b,g) | 7(f) | 8(b,g) |

|                                                | Test Sequence (c) |        |        |        |        |        |      |        |

| Initial examination of product                 | 1                 | 1      | 1      | 1      | 1      | 1      | 1    | 1      |

| LLCR, RJ45 interface, cable and board side     | 5,9               | 3,5    | 3,5    |        |        |        |      |        |

| OCL, cable side                                | 2,12(e)(f)        |        |        | 3,9    |        |        |      | 2,5    |

| Insulation resistance                          |                   |        |        | 4,7    |        |        |      |        |

| Withstanding voltage                           |                   |        |        | 8(f)   |        |        |      |        |

| NEXT                                           |                   |        |        |        |        | 2      |      |        |

| Insertion loss                                 | 13(e)(f)          |        |        | 2,10   |        | 3      |      | 3,6    |

| Return loss                                    |                   |        |        |        |        | 4      |      |        |

| CMRR                                           |                   |        |        |        |        | 5      |      |        |

| Functional test: PoE                           |                   |        | 7(h)   |        |        |        |      |        |

| Functional test: LEDs                          | 3,11(l)           | 2,6(I) | 2,6(I) |        |        |        |      |        |

| Vibration, random                              | 7                 |        |        |        |        |        |      |        |

| Durability                                     | 6                 |        |        |        | 2      |        |      |        |

| Mechanical shock                               | 8                 |        |        |        |        |        |      |        |

| Mating force                                   | 4                 |        |        |        |        |        |      |        |

| Unmating force                                 | 10                |        |        |        |        |        |      |        |

| Plug retention in jack                         |                   |        |        |        |        |        | 3    |        |

| Press fit insertion force                      |                   |        |        |        |        |        | 2    |        |

| Press fit extraction force                     |                   |        |        |        |        |        | 4    |        |

| Thermal shock                                  |                   |        |        | 5      |        |        |      |        |

| Humidity/temperature cycling                   |                   |        |        | 6      |        |        |      |        |

| Temperature life                               |                   | 4(d)   |        |        |        |        |      | 4(d)   |

| Mixed flowing gas                              |                   |        | 4(d)   |        |        |        |      |        |

| Electrical performance at temperature extremes |                   |        |        |        | 3      |        |      |        |

| Final examination of product                   | 14                | 7      | 8      | 11     | 4      | 6      | 5    | 7      |

(a) See paragraph 4.1.A.

- (b) Test Groups are performed with parts NOT mounted to qualification test boards for entire test group.

- (c) Numbers indicate sequence in which tests are performed.

- (d) Precondition specimens with 10 durability cycles.

- (e) Parts to be measured before insertion onto PCB and/or after removal from PCB. Vertical header contact to be probed not soldered.

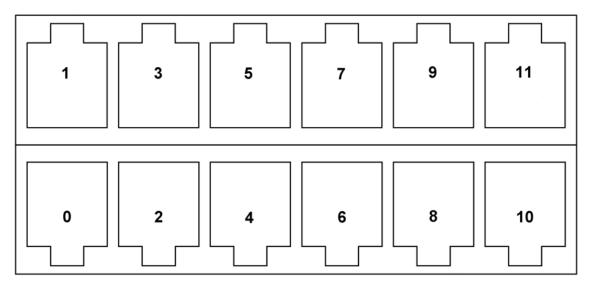

- (f) Test Groups to be performed with all 12 ports populated with cable plug. See Figure 3.

- (g) Test Groups to be performed with only ports 0, 1, 5, 6, 10 and 11 populated with cable plugs. See Figure 3.

- (h) PoE functional test to be performed with PowerDsine/Microsemi Integrated PoE test equipment. Part must be removed from PCB.

- (I) LED functional test to be performed with current-limiting power supply. Verify illumination on both LED's, both directions, all ports.

Figure 2

#### 4 QUALITY ASSURANCE PROVISIONS

- 4.1. Qualification Testing

- A. Specimen Selection

Modular plug and jack test specimens shall be selected at random from current production lots and prepared for testing in accordance with current Application Specifications and Instructions Sheets. Test groups 1, 2, 3, 5, 6 and 8 shall each consist of 4 specimens. Test group 4 shall consist of 3 specimens. Test group 7 shall consist of 1 specimen.

B. Test Sequence

Qualification inspection shall be verified by testing as specified in Figure 2.

4.2. Re-qualification Testing

If changes significantly affecting form, fit, or function are made to the product or manufacturing process, product assurance shall coordinate re-qualification testing, consisting of all or part of the original testing sequences as determined by development/product, quality and reliability engineering.

4.3. Acceptance

Acceptance is based on verification that the product meets the requirements of Figure 1. Failures attributed to equipment, test setup or operator deficiencies shall not disqualify the product. If the product failure occurs, corrective action shall be taken and specimens resubmitted for qualification. Testing to confirm corrective action is required before re-submittal.

4.4. Quality Conformance Inspection

The applicable quality inspection plan shall specify the sampling acceptable quality level to be used. Dimensional and functional requirements shall be in accordance with the applicable product drawing and this specification.

Measurement is repeated across the following signal pairs: Pins 1-2, Pins 3-6, Pins 4-5 and Pins 7-8.

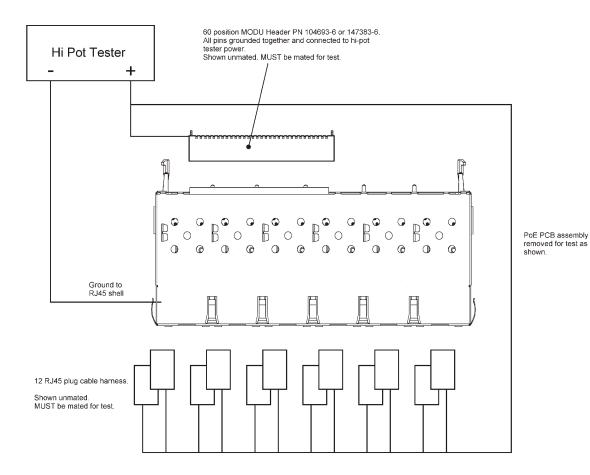

Figure 5 Cable Side LLCR and Discontinuity Measurement Setup

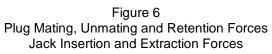

Figure 7 Dielectric Withstanding Voltage Test Setup

Figure 8 Dielectric Withstanding Voltage Test Setup PoE Board Header, All Pins Grounded Together