## INTEGRATED CIRCUITS

# DATA SHEET

# XA-S3

XA 16-bit microcontroller

32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs,

16 MB address range

Preliminary specification Supersedes data of 2000 Aug 22 2000 Dec 01

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

#### GENERAL DESCRIPTION

The XA-S3 device is a member of Philips Semiconductors' XA (eXtended Architecture) family of high performance 16-bit single-chip microcontrollers.

The XA-S3 device combines many powerful peripherals on one chip. With its high performance A/D converter, timers/counters, watchdog, Programmable Counter Array (PCA), I<sup>2</sup>C interface, dual UARTs, and multiple general purpose I/O ports, it is suited for general multipurpose high performance embedded control functions.

#### Specific features of the XA-S3

- 2.7 V to 5.5 V operation.

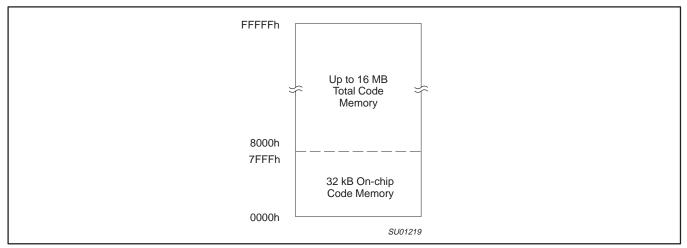

- 32 K bytes of on-chip EPROM/ROM program memory.

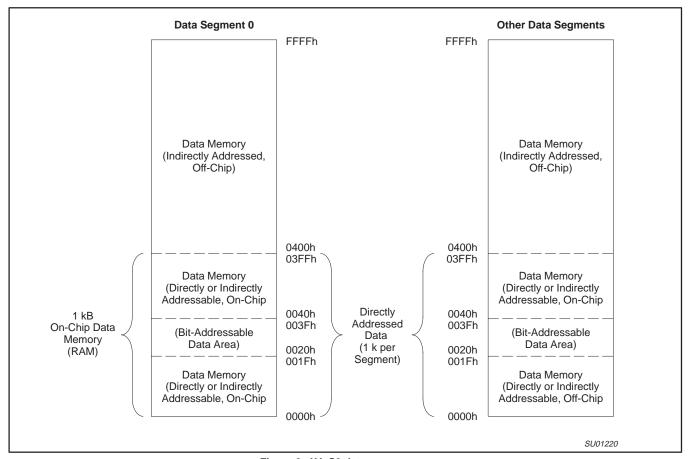

- 1024 bytes of on-chip data RAM.

- Supports off-chip addressing up to 16 megabytes (24 address lines). A clock output reference is added to simplify external bus interfacing.

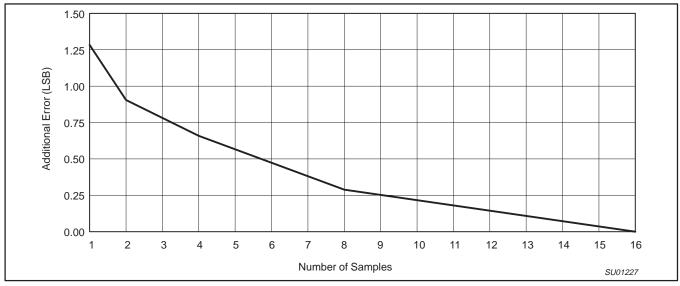

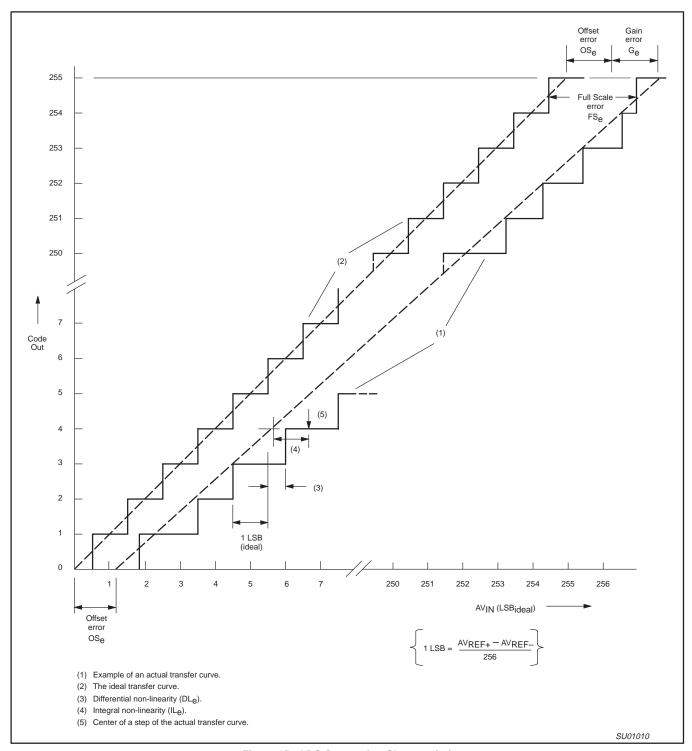

- High performance 8-channel 8-bit A/D converter with automatic channel scan and repeated read functions. Completes a conversion in 4.46 microseconds at 30 MHz. Alternate operating mode allows 10-bit conversion results.

- Three standard counter/timers with enhanced features. All timers have a toggle output capability.

- Watchdog timer.

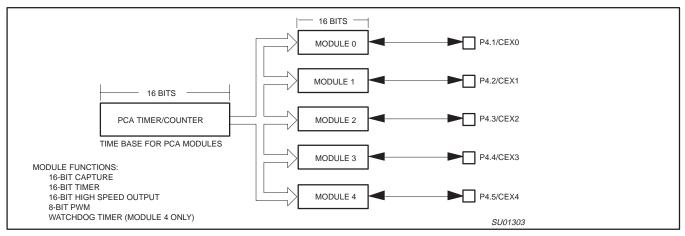

- 5-channel 16-bit Programmable Counter Array (PCA).

- I<sup>2</sup>C-bus serial I/O port with byte-oriented master and slave functions.

- Two enhanced UARTs with independent baud rates.

- Seven software interrupts.

- Active low reset output pin indicates all reset occurrences (external reset, watchdog reset and the RESET instruction). A reset source register allows program determination of the cause of the most recent reset.

- 50 I/O pins, each with 4 programmable output configurations.

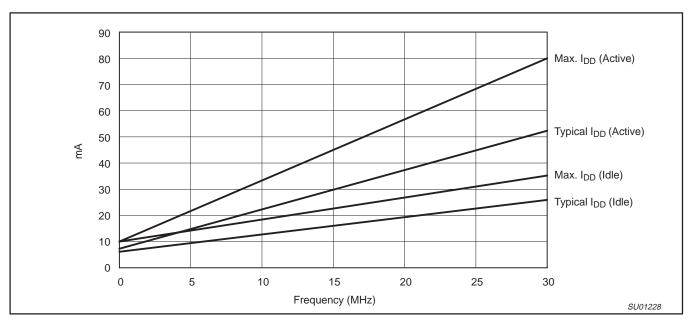

- 30 MHz operating frequency at 2.7-5.5 V V<sub>DD</sub>.

- Power saving operating modes: Idle and Power-down. Wake-up from power-down via an external interrupt is supported.

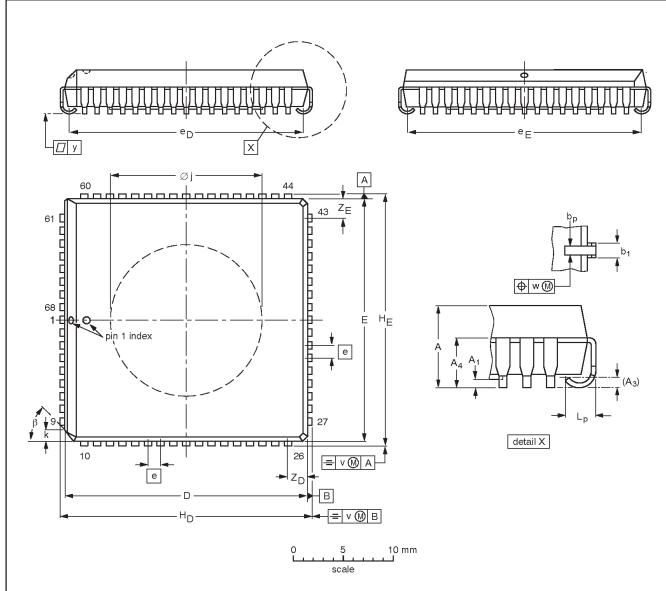

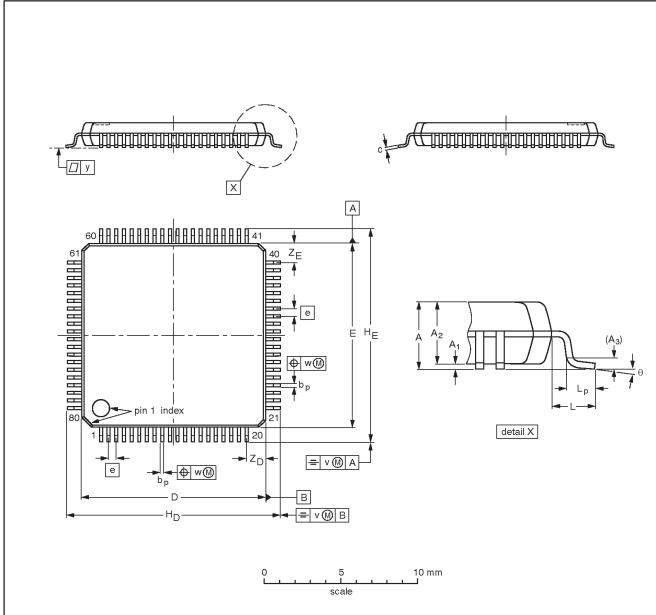

- 68-pin PLCC and 80-pin PQFP packages.

#### ORDERING INFORMATION

| ROMIess    | ROM        | EPROM      |     | TEMPERATURE RANGE (°C)<br>AND PACKAGE                                   | FREQ.<br>(MHz) | DRAWING<br>NUMBER |

|------------|------------|------------|-----|-------------------------------------------------------------------------|----------------|-------------------|

| PXAS30KBA  | PXAS33KBA  | PXAS37KBA  | OTP | 0 to +70, Commercial<br>68-pin Plastic Leaded Chip Carrier              | 30             | SOT188-3          |

| PXAS30KBBE | PXAS33KBBE | PXAS37KBBE | OTP | 0 to +70, Commercial<br>80-pin Plastic Low Profile Quad Flat Pack       | 30             | SOT315-1          |

| PXAS30KFA  | PXAS33KFA  | PXAS37KFA  | OTP | –40°C to +85°C, Industrial 68-pin Plastic<br>Leaded Chip Carrier        | 30             | SOT188-3          |

| PXAS30KFBE | PXAS33KFBE | PXAS37KFBE | OTP | –40°C to +85°C, Industrial 80-pin Plastic Low<br>Profile Quad Flat Pack | 30             | SOT315-1          |

XA-S3

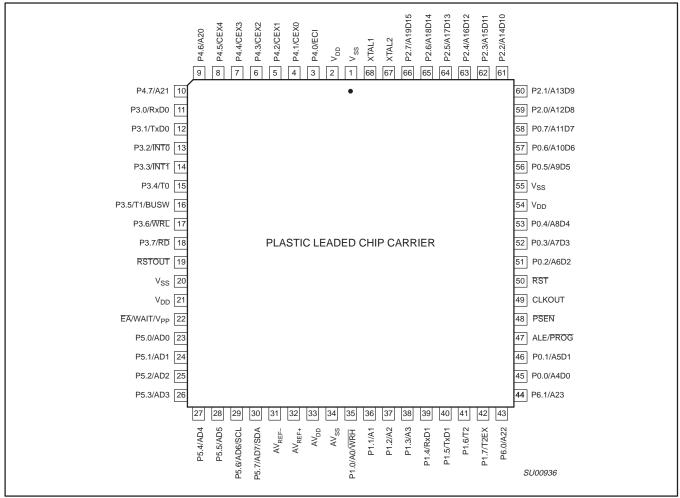

#### **PIN CONFIGURATIONS**

## 68-pin PLCC package

XA-S3

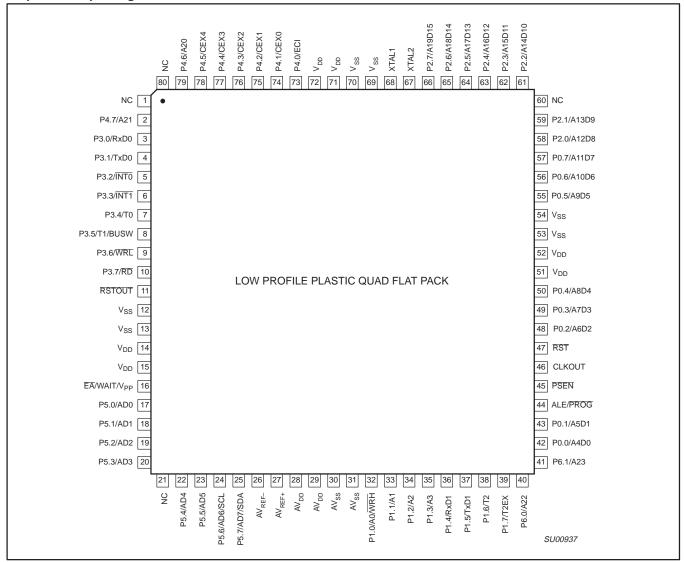

## 80-pin LQFP package

2000 Dec 01

XA-S3

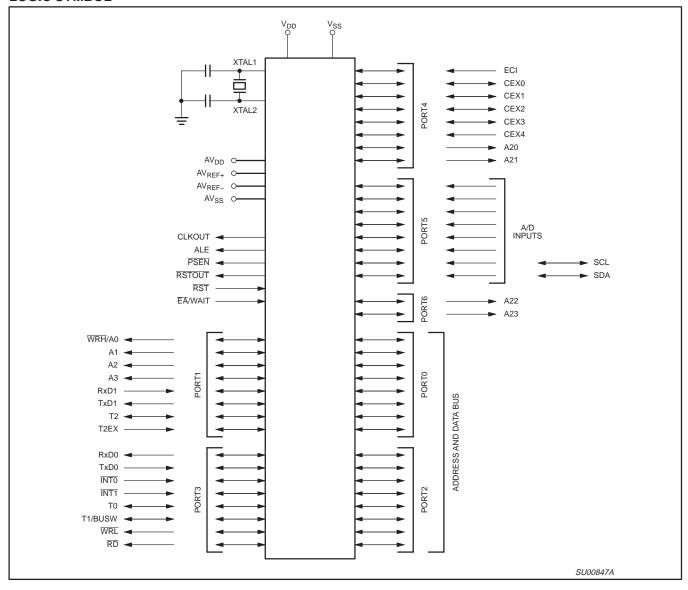

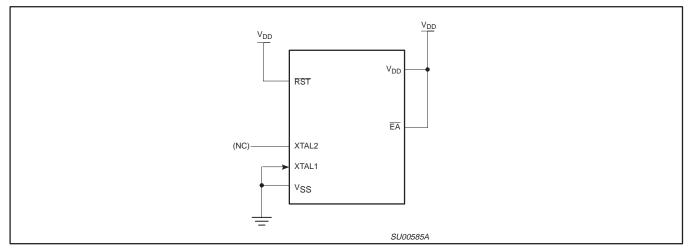

## **LOGIC SYMBOL**

XA-S3

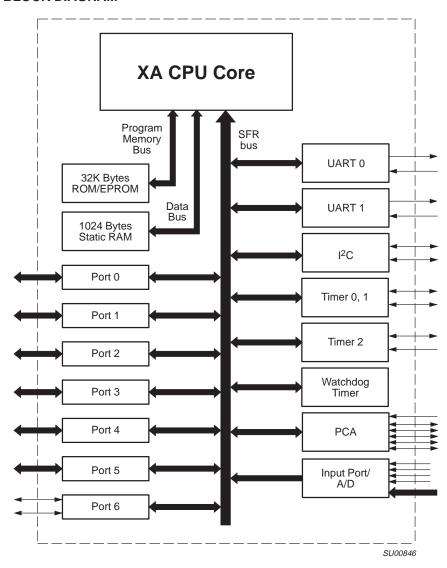

### **BLOCK DIAGRAM**

XA-S3

## **PIN DESCRIPTIONS**

|                         | PIN NU                     | JMBER                        | TVD= | NAME AND EUNOTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|----------------------------|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC                | PLCC                       | LQFP                         | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>         | 1, 20, 55                  | 12, 13,<br>53, 54,<br>69, 70 | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DD</sub>         | 2, 21, 54                  | 14, 15,<br>51, 52,<br>71, 72 | Ι    | <b>Power Supply:</b> This is the power supply voltage for normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RST                     | 50                         | 47                           | _    | <b>Reset:</b> A low on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor to begin execution at the address contained in the reset vector.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RSTOUT                  | 19                         | 11                           | 0    | <b>Reset Output:</b> This pin outputs a low whenever the XA-S3 processor is reset for any reason. This includes an external reset via the RST pin, watchdog reset, and the RESET instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

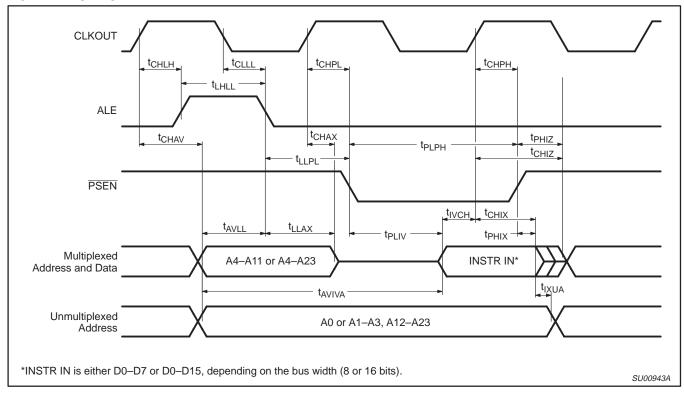

| ALE/PROG                | 47                         | 44                           | I/O  | Address Latch Enable/Program Pulse: A high output on the ALE pin signals external circuitry to latch the address portion of the multiplexed address/data bus. A pulse on ALE occurs only when it is needed in order to process a bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                    |

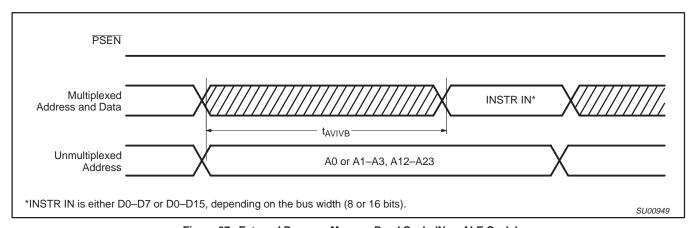

| PSEN                    | 48                         | 45                           | 0    | Program Store Enable: The read strobe for external program memory. When the microcontroller accesses external program memory, PSEN is driven low in order to enable memory devices. PSEN is only active when external code accesses are performed.                                                                                                                                                                                                                                                                                                                                                                                             |

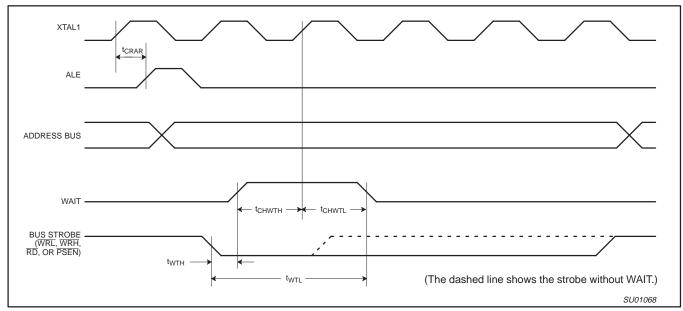

| EA/WAIT/V <sub>PP</sub> | 22                         | 16                           | I    | External Access/Bus Wait: The EA input determines whether the internal program memory of the microcontroller is used for code execution. The value on the EA pin is latched as the external reset input is released and applies during later execution. When latched as a 0, external program memory is used exclusively. When latched as a 1, internal program memory will be used up to its limit, and external program memory used above that point. After reset is released, this pin takes on the function of bus WAIT input. If WAIT is asserted high during an external bus access, that cycle will be extended until WAIT is released. |

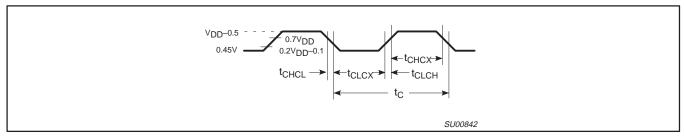

| XTAL1                   | 68                         | 68                           | I    | Crystal 1: Input to the inverting amplifier used in the oscillator circuit and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL2                   | 67                         | 67                           | I    | Crystal 2: Output from the oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLKOUT                  | 49                         | 46                           | 0    | Clock Output: This pin outputs a buffered version of the internal CPU clock. The clock output may be used in conjunction with the external bus to synchronize WAIT state generators, etc. The clock output may be disabled by software.                                                                                                                                                                                                                                                                                                                                                                                                        |

| $AV_DD$                 | 33                         | 28, 29                       | I    | Analog Power Supply: Positive power supply input for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AV <sub>SS</sub>        | 34                         | 30, 31                       | I    | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AV <sub>REF+</sub>      | 32                         | 27                           | I    | A/D Positive Reference Voltage: High end reference for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AV <sub>REF</sub> _     | 31                         | 26                           | Ι    | A/D Negative Reference Voltage: Low end reference for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.0 – P0.7             | 45, 46,<br>51–53,<br>56–58 | 42, 43,<br>48–50,<br>55–57   | I/O  | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. Port 0 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.                                                                                                                                                                                                         |

|                         |                            |                              |      | When the external program/data bus is used, Port 0 becomes the multiplexed low data/instruction byte and address lines 4 through 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

XA-S3

|             | PIN NU | IMBER            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                    | NAME AND EUNOPION                                                                                                                                                                                                                                                                                  |  |  |

|-------------|--------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MNEMONIC    | PLCC   | LQFP             | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                    | NAME AND FUNCTION                                                                                                                                                                                                                                                                                  |  |  |

| P1.0 – P1.7 | 35–42  | 32–39            | I/O  | 1s written to them and ar<br>operation of port 1 pins a<br>selected. Each port pin is                                                                                                                                                                                                                                                                                                                                              | I/O port with a user-configurable output type. Port 1 latches have re configured in the quasi-bidirectional mode during reset. The is inputs and outputs depends upon the port configuration is configured independently. Refer to the section on I/O port Electrical Characteristics for details. |  |  |

|             |        |                  |      | Port 1 also provides vario                                                                                                                                                                                                                                                                                                                                                                                                         | ous special functions as described below:                                                                                                                                                                                                                                                          |  |  |

|             | 35     | 32               | 0    | A0/WRH (P1.0)                                                                                                                                                                                                                                                                                                                                                                                                                      | Address bit 0 of the external address bus when the eternal data bus is configured for an 8-bit width. When the external data bus is configured for a 16-bit width, this pin becomes the high byte write strobe.                                                                                    |  |  |

|             | 36     | 33               | 0    | A1 (P1.1):                                                                                                                                                                                                                                                                                                                                                                                                                         | Address bit 1 of the external address bus.                                                                                                                                                                                                                                                         |  |  |

|             | 37     | 34               | 0    | A2 (P1.2):                                                                                                                                                                                                                                                                                                                                                                                                                         | Address bit 2 of the external address bus.                                                                                                                                                                                                                                                         |  |  |

|             | 38     | 35               | 0    | A3 (P1.3):                                                                                                                                                                                                                                                                                                                                                                                                                         | Address bit 3 of the external address bus.                                                                                                                                                                                                                                                         |  |  |

|             | 39     | 36               | - 1  | RxD1 (P1.4):                                                                                                                                                                                                                                                                                                                                                                                                                       | Serial port 1 receiver input.                                                                                                                                                                                                                                                                      |  |  |

|             | 40     | 37               | 0    | TxD1 (P1.5):                                                                                                                                                                                                                                                                                                                                                                                                                       | Serial port 1 transmitter output.                                                                                                                                                                                                                                                                  |  |  |

|             | 41     | 38               | I/O  | T2 (P1.6):                                                                                                                                                                                                                                                                                                                                                                                                                         | Timer/counter 2 external count input or overflow output.                                                                                                                                                                                                                                           |  |  |

|             | 42     | 39               | 0    | T2EX (P1.7):                                                                                                                                                                                                                                                                                                                                                                                                                       | Timer/counter 2 reload/capture/direction control.                                                                                                                                                                                                                                                  |  |  |

| P2.0 – P2.7 | 59–66  | 58, 59,<br>61–66 | I/O  | <b>Port 2:</b> Port 2 is an 8-bit I/O port with a user-configurable output type. Port 2 latches has written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details. |                                                                                                                                                                                                                                                                                                    |  |  |

|             |        |                  |      | multiplexed high data/ins                                                                                                                                                                                                                                                                                                                                                                                                          | am/data bus is used in 16-bit mode, Port 2 becomes the struction byte and address lines 12 through 19. When the external 1 in 8-bit mode, the number of address lines that appear on Port 2 groups of 4 bits.                                                                                      |  |  |

| P3.0 – P3.7 | 11–18  | 3–10             | I/O  | 1s written to them and ar<br>operation of port 3 pins a<br>selected. Each port pin is                                                                                                                                                                                                                                                                                                                                              | I/O port with a user-configurable output type. Port 3 latches have re configured in the quasi-bidirectional mode during reset. The as inputs and outputs depends upon the port configuration is configured independently. Refer to the section on I/O port Electrical Characteristics for details. |  |  |

|             |        |                  |      | Port 3 also provides the                                                                                                                                                                                                                                                                                                                                                                                                           | various special functions as described below:                                                                                                                                                                                                                                                      |  |  |

|             | 11     | 3                | ı    | RxD0 (P3.0):                                                                                                                                                                                                                                                                                                                                                                                                                       | Receiver input for serial port 0.                                                                                                                                                                                                                                                                  |  |  |

|             | 12     | 4                | 0    | TxD0 (P3.1):                                                                                                                                                                                                                                                                                                                                                                                                                       | Transmitter output for serial port 0.                                                                                                                                                                                                                                                              |  |  |

|             | 13     | 5                | 1    | ĪNT0 (P3.2):                                                                                                                                                                                                                                                                                                                                                                                                                       | External interrupt 0 input.                                                                                                                                                                                                                                                                        |  |  |

|             | 14     | 6                | ı    | ĪNT1 (P3.3):                                                                                                                                                                                                                                                                                                                                                                                                                       | External interrupt 1 input.                                                                                                                                                                                                                                                                        |  |  |

|             | 15     | 7                | I/O  | T0 (P3.4):                                                                                                                                                                                                                                                                                                                                                                                                                         | Timer/counter 0 external count input or overflow output.                                                                                                                                                                                                                                           |  |  |

|             | 16     | 8                | I/O  | T1 / BUSW (P3.5):                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer/counter 1 external count input or overflow output. The value on this pin is latched as an external chip reset is completed and defines the default external data bus width.                                                                                                                  |  |  |

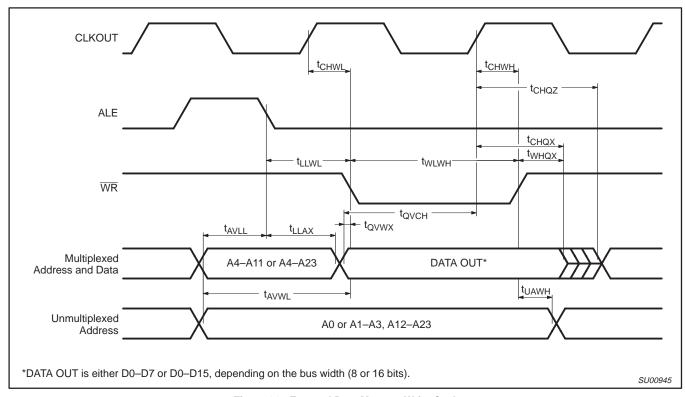

|             | 17     | 9                | 0    | WRL (P3.6):                                                                                                                                                                                                                                                                                                                                                                                                                        | External data memory low byte write strobe.                                                                                                                                                                                                                                                        |  |  |

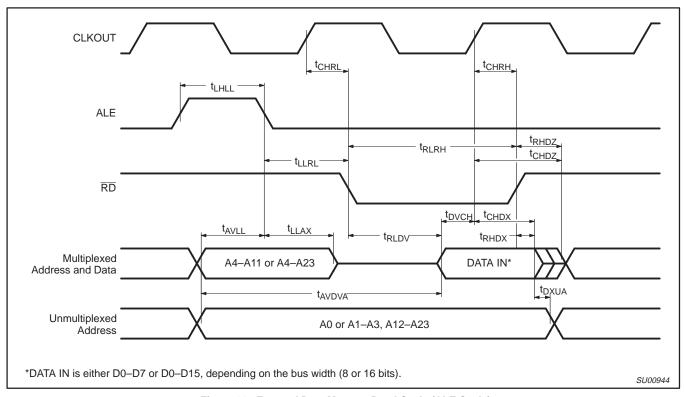

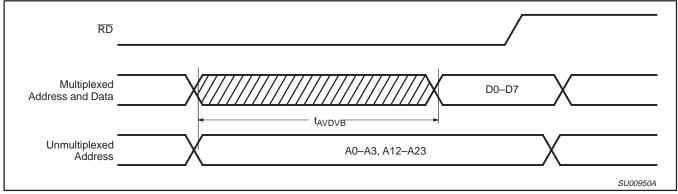

|             | 18     | 10               | 0    | RD (P3.7):                                                                                                                                                                                                                                                                                                                                                                                                                         | External data memory read strobe.                                                                                                                                                                                                                                                                  |  |  |

| P4.0 – P4.7 | 3–10   | 73–79, 2         | I/O  | 1s written to them and ar<br>operation of Port 4 pins a<br>selected. Each port pin is                                                                                                                                                                                                                                                                                                                                              | I/O port with a user-configurable output type. Port 4 latches have re configured in the quasi-bidirectional mode during reset. The as inputs and outputs depends upon the port configuration s configured independently. Refer to the section on I/O port Electrical Characteristics for details.  |  |  |

|             |        |                  |      | Port 4 also provides vario                                                                                                                                                                                                                                                                                                                                                                                                         | ous special functions as described below:                                                                                                                                                                                                                                                          |  |  |

|             | 3      | 73               | ı    | ECI (P4.0):                                                                                                                                                                                                                                                                                                                                                                                                                        | PCA External clock input.                                                                                                                                                                                                                                                                          |  |  |

|             | 4      | 74               | I/O  | CEX0 (P4.1):                                                                                                                                                                                                                                                                                                                                                                                                                       | Capture/compare external I/O for PCA module 0.                                                                                                                                                                                                                                                     |  |  |

|             | 5      | 75               | I/O  | CEX1 (P4.2):                                                                                                                                                                                                                                                                                                                                                                                                                       | Capture/compare external I/O for PCA module 1.                                                                                                                                                                                                                                                     |  |  |

|             | 6      | 76               | I/O  | CEX2 (P4.3):                                                                                                                                                                                                                                                                                                                                                                                                                       | Capture/compare external I/O for PCA module 2.                                                                                                                                                                                                                                                     |  |  |

|             | 7      | 77               | I/O  | CEX3 (P4.4):                                                                                                                                                                                                                                                                                                                                                                                                                       | Capture/compare external I/O for PCA module 3.                                                                                                                                                                                                                                                     |  |  |

|             | 8      | 78               | I/O  | CEX4 (P4.5):                                                                                                                                                                                                                                                                                                                                                                                                                       | Capture/compare external I/O for PCA module 4.                                                                                                                                                                                                                                                     |  |  |

|             | 9      | 79               | 0    | A20 (P4.6):                                                                                                                                                                                                                                                                                                                                                                                                                        | Address bit 20 of the external address bus.                                                                                                                                                                                                                                                        |  |  |

|             | 10     | 2                | 0    | A21 (P4.7):                                                                                                                                                                                                                                                                                                                                                                                                                        | Address bit 21 of the external address bus.                                                                                                                                                                                                                                                        |  |  |

XA-S3

| MNEMONIC    | PIN NU | IMBER           | TYPE |                                                                                                                                                                                                                                                                                                                                                                                                                                        | NAME AND FUNCTION                                                |  |  |

|-------------|--------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| WINEWONIC   | PLCC   | LQFP            | ITPE |                                                                                                                                                                                                                                                                                                                                                                                                                                        | NAME AND FONCTION                                                |  |  |

| P5.0 – P5.7 | 23–30  | 17–20,<br>22–25 | I/O  | <b>Port 5:</b> Port 5 is an 8-bit I/O port with a user-configurable output type. Port 5 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of Port 5 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details. |                                                                  |  |  |

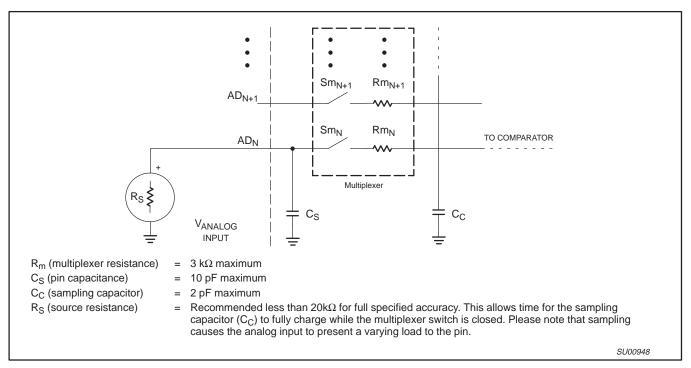

|             |        |                 |      | Port 5 also provides various special functions as described below. Port 5 pins used as A/ inputs must be configured by the user to the high impedance mode.                                                                                                                                                                                                                                                                            |                                                                  |  |  |

|             | 23     | 17              | I    | AD0 (P5.0):                                                                                                                                                                                                                                                                                                                                                                                                                            | A/D channel 0 input.                                             |  |  |

|             | 24     | 18              | I    | AD1 (P5.1):                                                                                                                                                                                                                                                                                                                                                                                                                            | A/D channel 1 input.                                             |  |  |

|             | 25     | 19              | I    | AD2 (P5.2):                                                                                                                                                                                                                                                                                                                                                                                                                            | A/D channel 2 input.                                             |  |  |

|             | 26     | 20              | I    | AD3 (P5.3):                                                                                                                                                                                                                                                                                                                                                                                                                            | A/D channel 3 input.                                             |  |  |

|             | 27     | 22              | I    | AD4 (P5.4):                                                                                                                                                                                                                                                                                                                                                                                                                            | A/D channel 4 input.                                             |  |  |

|             | 28     | 23              | I    | AD5 (P5.5):                                                                                                                                                                                                                                                                                                                                                                                                                            | A/D channel 5 input.                                             |  |  |

|             | 29     | 24              | I/O  | AD6/SCL (P5.6):                                                                                                                                                                                                                                                                                                                                                                                                                        | A/D channel 6 input. I <sup>2</sup> C serial clock input/output. |  |  |

|             | 30     | 25              | I/O  | AD7/SDA (P5.7):                                                                                                                                                                                                                                                                                                                                                                                                                        | A/D channel 7 input. I <sup>2</sup> C serial data input/output.  |  |  |

| P6.0 – P6.7 | 43, 44 | 40, 41          | I/O  | Port 6: Port 6 is a 2-bit I/O port with a user-configurable output type. Port 6 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of Port 6 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.         |                                                                  |  |  |

|             |        |                 |      | Port 6 also provides special functions as described below:                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |  |  |

|             | 43     | 40              | 0    | A22 (P6.0): Address bit 22 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |  |  |

|             | 44     | 41              | 0    | A23 (P6.1):                                                                                                                                                                                                                                                                                                                                                                                                                            | Address bit 23 of the external address bus.                      |  |  |

**Table 1. Special Function Registers**

|         |                                 | SFR     |       |       | BIT FUNC | CTIONS A | ND ADDI | RESSES     |            |       | Reset  |

|---------|---------------------------------|---------|-------|-------|----------|----------|---------|------------|------------|-------|--------|

| NAME    | DESCRIPTION                     | Address | MSB   |       |          |          |         |            |            | LSB   | Value  |

|         |                                 |         | 3F7   | 3F6   | 3F5      | 3F4      | 3F3     | 3F2        | 3F1        | 3F0   |        |

| ADCON#* | A/D control register            | 43E     | _     | _     | _        | -        | ADRES   | ADMOD      | ADSST      | ADINT | 00h    |

|         |                                 |         | 3FF   | 3FE   | 3FD      | 3FC      | 3FB     | 3FA        | 3F9        | 3F8   | ]      |

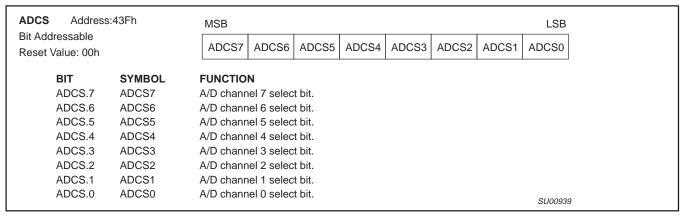

| ADCS#*  | A/D channel select register     | 43F     | ADCS7 | ADCS6 | ADCS5    | ADCS4    | ADCS3   | ADCS2      | ADCS1      | ADCS0 | 00h    |

| ADCFG#  | A/D timing configuration        | 4B9     | _     | _     | _        | _        | A/I     | D Timing ( | Configurat | ion   | 0Fh    |

| ADRSH0# | A/D high byte result, channel 0 | 4B0     |       |       |          |          |         |            |            |       | xx     |

| ADRSH1# | A/D high byte result, channel 1 | 4B1     |       |       |          |          |         |            |            |       | xx     |

| ADRSH2# | A/D high byte result, channel 2 | 4B2     |       |       |          |          |         |            |            |       | xx     |

| ADRSH3# | A/D high byte result, channel 3 | 4B3     |       |       |          |          |         |            |            |       | xx     |

| ADRSH4# | A/D high byte result, channel 4 | 4B4     |       |       |          |          |         |            |            |       | XX     |

| ADRSH5# | A/D high byte result, channel 5 | 4B5     |       |       |          |          |         |            |            |       | XX     |

| ADRSH6# | A/D high byte result, channel 6 | 4B6     |       |       |          |          |         |            |            |       | xx     |

| ADRSH7# | A/D high byte result, channel 7 | 4B7     |       |       |          |          |         |            |            |       | XX     |

| ADRSL#  | Two LSBs of 10-bit A/D result   | 4B8     |       |       |          |          |         |            |            |       | XX     |

| BCR#    | Bus configuration register      | 46A     | _     | _     | CLKD     | WAITD    | BUSD    | BC2        | BC1        | BC0   | Note 1 |

| BTRH    | Bus timing register high byte   | 469     | DW1   | DW0   | DWA1     | DWA0     | DR1     | DR0        | DRA1       | DRA0  | FFh    |

| BTRL    | Bus timing register low byte    | 468     | WM1   | WM0   | ALEW     | _        | CR1     | CR0        | CRA1       | CRA0  | EFh    |

|         |                                 |         | 2D7   | 2D6   | 2D5      | 2D4      | 2D3     | 2D2        | 2D1        | 2D0   |        |

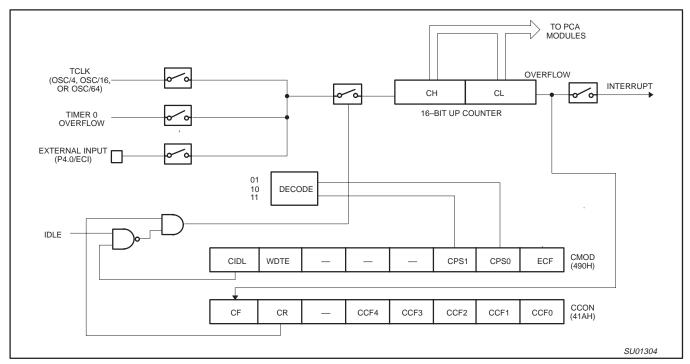

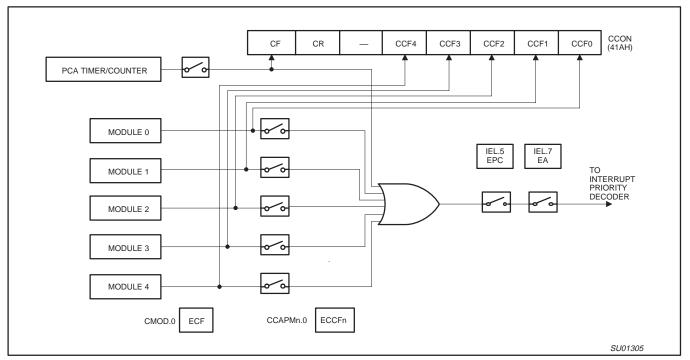

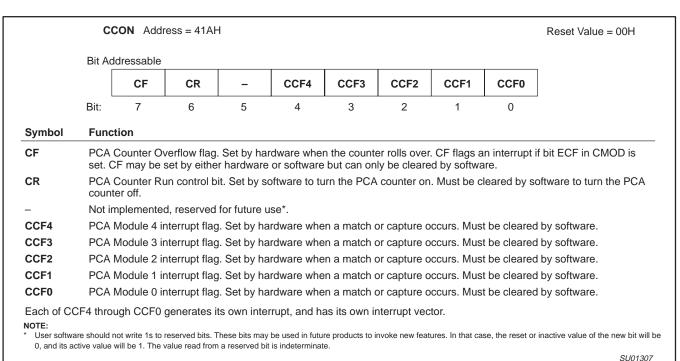

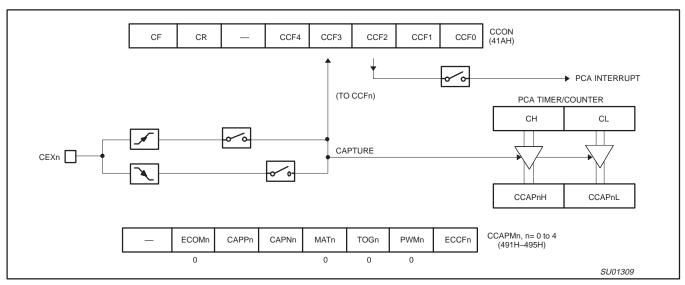

| CCON#*  | PCA counter control             | 41A     | CF    | CR    | _        | CCF4     | CCF3    | CCF2       | CCF1       | CCF0  | 00h    |

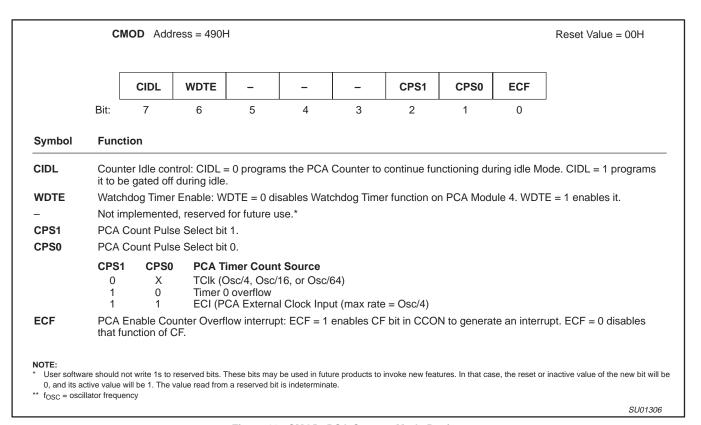

| CMOD#   | PCA mode control                | 490     | CIDL  | WDTE  | _        | -        | _       | CPS1       | CPS0       | ECF   | 00h    |

| CH#     | PCA counter high byte           | 48B     |       | -     |          |          |         |            | -          |       | 00h    |

| CL#     | PCA counter low byte            | 48A     |       |       |          |          |         |            |            |       | 00h    |

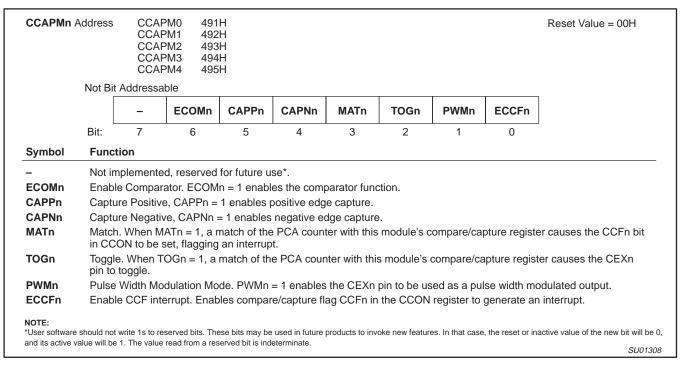

| CCAPM0# | PCA module 0 mode               | 491     | -     | ECOM0 | CAPP0    | CAPN0    | MAT0    | TOG0       | PWM0       | ECCF0 | 00h    |

| CCAPM1# | PCA module 1 mode               | 492     | _     | ECOM1 | CAPP1    | CAPN1    | MAT1    | TOG1       | PWM1       | ECCF1 | 00h    |

2000 Dec 01

XA-S3

|                    |                                                              | SFR        |        |                                | BIT FUN    | CTIONS A | ND ADD  | RESSES |       |        | Reset |

|--------------------|--------------------------------------------------------------|------------|--------|--------------------------------|------------|----------|---------|--------|-------|--------|-------|

| NAME               | DESCRIPTION                                                  | Address    | MSB    |                                |            |          |         |        |       | LSB    | Value |

| CCAPM2#            | PCA module 2 mode                                            | 493        | _      | ECOM2                          | CAPP2      | CAPN2    | MAT2    | TOG2   | PWM2  | ECCF2  | 00h   |

| CCAPM3#            | PCA module 3 mode                                            | 494        | _      | ECOM3                          | CAPP3      | CAPN3    | MAT3    | TOG3   | PWM3  | ECCF3  | 00h   |

| CCAPM4#            | PCA module 4 mode                                            | 495        | -      | ECOM4                          | CAPP4      | CAPN4    | MAT4    | TOG4   | PWM4  | ECCF4  | 00h   |

| CCAP0H#            | PCA module 0 capture high byte                               | 497        |        |                                |            |          |         |        |       |        | xx    |

| CCAP1H#            | PCA module 1 capture high byte                               | 499        |        |                                |            |          |         |        |       |        | XX    |

| CCAP2H#            | PCA module 2 capture high byte                               | 49B        |        |                                |            |          |         |        |       |        | XX    |

| CCAP3H#            | PCA module 3 capture high byte                               | 49D        |        |                                |            |          |         |        |       |        | XX    |

| CCAP4H#<br>CCAP0L# | PCA module 4 capture high byte PCA module 0 capture low byte | 49F<br>496 |        |                                |            |          |         |        |       |        | xx    |

| CCAP1L#            | PCA module 1 capture low byte                                | 498        |        |                                |            |          |         |        |       |        | xx    |

| CCAP2L#            | PCA module 2 capture low byte                                | 49A        |        |                                |            |          |         |        |       |        | XX    |

| CCAP3L#            | PCA module 3 capture low byte                                | 49C        |        |                                |            |          |         |        |       |        | XX    |

| CCAP4L#            | PCA module 4 capture low byte                                | 49E        |        |                                |            |          |         |        |       |        | xx    |

| CS                 | Code segment                                                 | 443        |        |                                |            |          |         |        |       |        | 00h   |

| DS                 | Data segment                                                 | 441        |        |                                |            |          |         |        |       |        | 00h   |

| ES                 | Extra segment                                                | 442        |        |                                |            |          |         |        |       |        | 00h   |

|                    |                                                              |            | 367    | 366                            | 365        | 364      | 363     | 362    | 361   | 360    | ]     |

| I2CON#*            | I <sup>2</sup> C control register                            | 42C        | CR2    | ENA                            | STA        | STO      | SI      | AA     | CR1   | CR0    | 00h   |

| I2STAT#            | I <sup>2</sup> C status register                             | 46C        |        | I <sup>2</sup> C Sta           | itus Code/ | Vector   |         | 0      | 0     | 0      | F8h   |

| I2DAT#             | I <sup>2</sup> C data register                               | 46D        |        |                                |            |          |         | xx     |       |        |       |

| I2ADDR#            | I <sup>2</sup> C address register                            | 46E        |        | I <sup>2</sup> C Slave Address |            |          |         |        | GC    | 00h    |       |

|                    |                                                              |            | 33F    | 33E                            | 33D        | 33C      | 33B     | 33A    | 339   | 338    |       |

| IEH*               | Interrupt enable high byte                                   | 427        | _      | _                              | _          | _        | ETI1    | ERI1   | ETI0  | ERI0   | 00h   |

|                    |                                                              |            | 337    | 336                            | 335        | 334      | 333     | 332    | 331   | 330    |       |

| IEL#*              | Interrupt enable low byte                                    | 426        | EA     | EAD                            | EPC        | ET2      | ET1     | EX1    | ET0   | EX0    | 00h   |

|                    |                                                              |            | 377    | 376                            | 375        | 374      | 373     | 372    | 371   | 370    |       |

| IELB#*             | Interrupt enable B low byte                                  | 42E        | _      | -                              | El2        | EC4      | EC3     | EC2    | EC1   | EC0    | 00h   |

| IPA0               | Interrupt priority A0                                        | 4A0        | -      |                                | PT0        |          | -       |        | PX0   |        | 00h   |

| IPA1               | Interrupt priority A1                                        | 4A1        |        |                                | PT1        |          | _       |        | PX1   |        | 00h   |

| IPA2#              | Interrupt priority A2                                        | 4A2        | _      |                                | PPC        |          | _       |        | PT2   |        | 00h   |

| IPA3#              | Interrupt priority A3                                        | 4A3        | _      |                                | _          |          | _       |        | PAD   |        | 00h   |

| IPA4               | Interrupt priority A4                                        | 4A4        | _      |                                | PTI0       |          | _       |        | PRI0  |        | 00h   |

| IPA5               | Interrupt priority A5                                        | 4A5        | -      |                                | PTI1       |          | -       |        | PRI1  |        | 00h   |

| IPB0#              | Interrupt priority B0                                        | 4A8        | _      |                                | PC1        |          | _       |        | PC0   |        | 00h   |

| IPB1#              | Interrupt priority B1                                        | 4A9        | _      |                                | PC3        |          | _       |        | PC2   |        | 00h   |

| IPB2#              | Interrupt priority B2                                        | 4AA        | -      |                                | PI2        |          | -       |        | PC4   |        | 00h   |

|                    |                                                              |            | 387    | 386                            | 385        | 384      | 383     | 382    | 381   | 380    | 1     |

| P0*                | Port 0                                                       | 430        | A11D7  | A10D6                          | A9D5       | A8D4     | A7D3    | A6D2   | A5D1  | A4D0   | FFh   |

|                    |                                                              |            | 38F    | 38E                            | 38D        | 38C      | 38B     | 38A    | 389   | 388    | 1     |

| P1*                | Port 1                                                       | 431        | T2EX   | T2                             | TxD1       | RxD1     | А3      | A2     | A1    | A0/WRH | FFh   |

|                    |                                                              |            | 397    | 396                            | 395        | 394      | 393     | 392    | 391   | 390    | 1     |

| P2*                | Port 2                                                       | 432        | A19D15 | A18D14                         | A17D13     | A16D12   | A15D11  | A14D10 | A13D9 | A12D8  | FFh   |

|                    |                                                              |            | 39F    | 39E                            | 39D        | 39C      | 39B     | 39A    | 399   | 398    | 1     |

| P3*                | Port 3                                                       | 433        | RD     | WRL                            | T1         | ТО       | INT1    | INT0   | TxD0  | RxD0   | FFh   |

| -                  |                                                              |            | 3A7    | 3A6                            | 3A5        | 3A4      | 3A3     | 3A2    | 3A1   | 3A0    | 1     |

| P4#*               | Port 4                                                       | 434        | A21    | A20                            | CEX4       | CEX3     | CEX2    | CEX1   | CEX0  | ECI    | FFh   |

|                    | 1. 41. 1                                                     | 1 10-1     | , 14-1 | 1 /120                         |            |          | U = /\2 |        |       |        | 1     |

XA-S3

| NAME             | DESCRIPTION                                                       | SFR<br>Address | MSB     |          | BIT FUNC | CTIONS A | ND ADD   | RESSES |       | LSB    | Res       |

|------------------|-------------------------------------------------------------------|----------------|---------|----------|----------|----------|----------|--------|-------|--------|-----------|

|                  |                                                                   |                | 3AF     | 3AE      | 3AD      | 3AC      | 3AB      | 3AA    | 3A9   | 3A8    | $\vdash$  |

| P5#*             | Port 5                                                            | 435            | AD7/SDA | AD6/SCL  | AD5      | AD4      | AD3      | AD2    | AD1   | AD0    | ┫<br>FFh  |

|                  |                                                                   |                |         |          | <u> </u> |          |          |        | 3B1   | 3B0    | 1         |

| P6#*             | Port 6                                                            | 436            | _       |          |          | <u> </u> | <u> </u> | _      | A23   | A22    | <br> FFr  |

|                  |                                                                   |                |         | <u> </u> |          |          | <u> </u> |        |       |        | 1         |

| P0CFGA           | Port 0 configuration A                                            | 470            |         |          |          |          |          |        |       |        | Not       |

| P1CFGA           | Port 1 configuration A                                            | 471            |         |          |          |          |          |        |       |        | Not       |

| P2CFGA           | Port 2 configuration A                                            | 472            |         |          |          |          |          |        |       |        | Not       |

| P3CFGA           | Port 3 configuration A                                            | 473            |         |          |          |          |          | i      |       |        | Not       |

| P4CFGA#          | Port 4 configuration A                                            | 474            |         |          |          |          |          |        |       |        | Not       |

| P5CFGA#          | Port 5 configuration A                                            | 475            |         |          |          |          |          |        |       |        | Not       |

| P6CFGA#          | Port 6 configuration A                                            | 476            | _       | -        | -        | -        | -        | -      |       |        | Not       |

| P0CFGB           | Port 0 configuration B                                            | 4F0            |         |          |          |          |          |        |       |        | Not       |

| P1CFGB           | Port 1 configuration B                                            | 4F1            |         |          |          |          |          |        |       |        | Not       |

| P2CFGB           | Port 2 configuration B                                            | 4F2            |         |          |          |          |          |        |       |        | Not       |

| P3CFGB           | Port 3 configuration B                                            | 4F3            |         |          |          |          |          |        |       |        | Not       |

| P4CFGB#          | Port 4 configuration B                                            | 4F4            |         |          |          |          |          |        |       |        | Not       |

| P5CFGB#          | Port 5 configuration B                                            | 4F5            |         |          |          |          |          |        |       |        | Not       |

| P6CFGB#          | Port 6 configuration B                                            | 4F6            | _       | _        | _        | _        | _        | _      |       |        | Not       |

|                  |                                                                   |                | 227     | 226      | 225      | 224      | 223      | 222    | 221   | 220    | 1         |

| PCON*            | Power control register                                            | 404            | _       | _        | _        | _        | _        | _      | PD    | IDL    | 00h       |

|                  |                                                                   |                | 20F     | 20E      | 20D      | 20C      | 20B      | 20A    | 209   | 208    | 1         |

| PSWH*            | Program status word (high byte)                                   | 401            | SM      | TM       | RS1      | RS0      | IM3      | IM2    | IM1   | IM0    | Not       |

|                  |                                                                   |                | 207     | 206      | 205      | 204      | 203      | 202    | 201   | 200    | 1         |

| PSWL*            | Program status word (low byte)                                    | 400            | С       | AC       | _        | _        | _        | V      | N     | Z      | Not       |

|                  |                                                                   |                | 217     | 216      | 215      | 214      | 213      | 212    | 211   | 210    | ]         |

| PSW51*           | 80C51 compatible PSW                                              | 402            | С       | AC       | F0       | RS1      | RS0      | V      | F1    | Р      | Not       |

| RSTSRC#          | Reset source register                                             | 463            | _       | _        | _        | _        | _        | R_WD   | R_CMD | R_EXT  | Not       |

| RTH0             | Timer 0 reload register, high byte                                | 455            |         |          |          |          |          |        |       |        | 00h       |

| RTH1             | Timer 1 reload register, high byte                                | 457            |         |          |          |          |          |        |       |        | 00h       |

| RTL0             | Timer 0 reload register, low byte                                 | 454            |         |          |          |          |          |        |       |        | 00h       |

| RTL1             | Timer 1 reload register, low byte                                 | 456            | 207     | 200      | 205      | 20.4     | 200      | 200    | 204   | 202    | 00h       |

| 2000             | Carried mant O passived as estate                                 | 400            | 307     | 306      | 305      | 304      | 303      | 302    | 301   | 300    | -         |

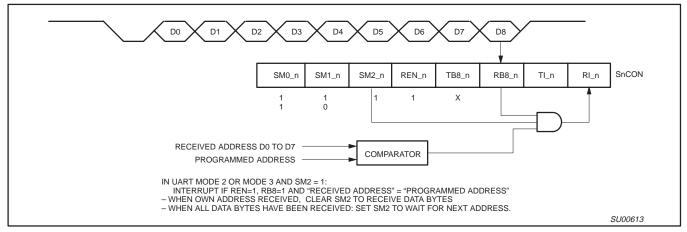

| S0CON*           | Serial port 0 control register                                    | 420            | SM0_0   | SM1_0    | SM2_0    | REN_0    | TB8_0    | RB8_0  | TI_0  | RI_0   | 00h       |

| 200747##         | Operial manufacture of the second                                 | 464            | 30F     | 30E      | 30D      | 30C      | 30B      | 30A    | 309   | 308    | <b>-</b>  |

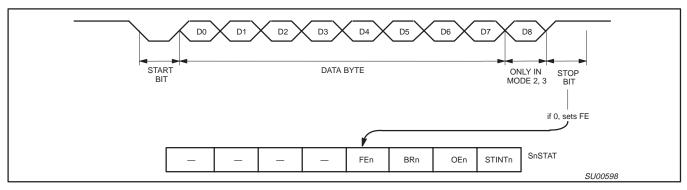

| SOSTAT#*         | Serial port 0 extended status                                     | 421            |         | _        | -        | ERR0     | FE0      | BR0    | OE0   | STINT0 | 00h       |

| S0BUF<br>S0ADDR  | Serial port 0 data buffer register Serial port 0 address register | 460<br>461     |         |          |          |          |          |        |       |        | XX<br>00h |

| SOADDR<br>SOADEN | Serial port 0 address register                                    | 462            |         |          |          |          |          |        |       |        | 00h       |

|                  |                                                                   |                | 327     | 326      | 325      | 324      | 323      | 322    | 321   | 320    |           |

| S1CON*           | Serial port 1 control register                                    | 424            | SM0_1   | SM1_1    | SM2_1    | REN_1    | TB8_1    | RB8_1  | TI_1  | RI_1   | 001       |

|                  |                                                                   |                | 32F     | 32E      | 32D      | 32C      | 32B      | 32A    | 329   | 328    | 1         |

| S1STAT#*         | Serial port 1 extended status                                     | 425            | _       | _        | _        | ERR1     | FE1      | BR1    | OE1   | STINT1 | 00h       |

| S1BUF            | Serial port 1 data buffer register                                | 464            |         | •        | •        | •        | •        | •      | •     | •      | xx        |

| S1ADDR           | Serial port 1 address register                                    | 465            |         |          |          |          |          |        |       |        | 00h       |

XA-S3

| NAME                           | DESCRIPTION                                                                             | SFR<br>Address           | MSB   |       | BIT FUNC | CTIONS A | ND ADD | RESSES |       | LSB    | Reset<br>Value           |

|--------------------------------|-----------------------------------------------------------------------------------------|--------------------------|-------|-------|----------|----------|--------|--------|-------|--------|--------------------------|

| S1ADEN                         | Serial port 1 address enable                                                            | 466                      |       |       |          |          |        |        |       |        | 00h                      |

| SCR                            | System configuration register                                                           | 440                      | -     | _     | _        | _        | PT1    | PT0    | СМ    | PZ     | 00h                      |

|                                |                                                                                         |                          | 21F   | 21E   | 21D      | 21C      | 21B    | 21A    | 219   | 218    | 1                        |

| SSEL*                          | Segment selection register                                                              | 403                      | ESWEN | R6SEG | R5SEG    | R4SEG    | R3SEG  | R2SEG  | R1SEG | R0SEG  | 00h                      |

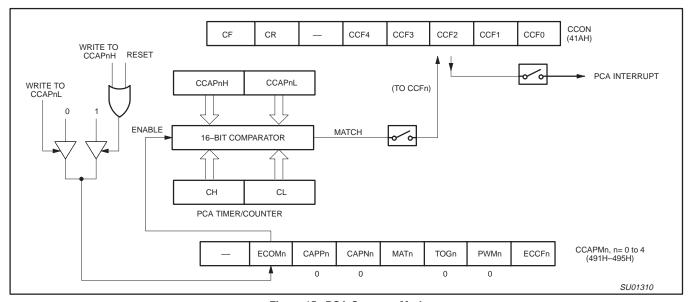

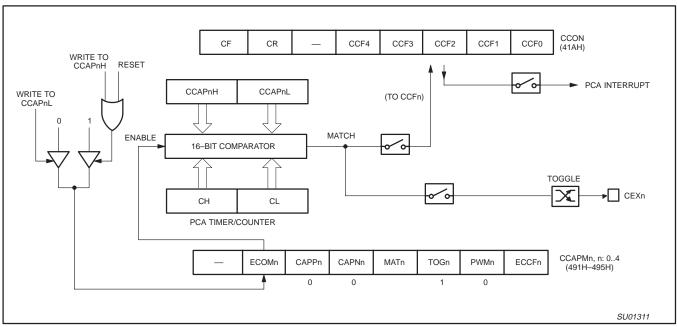

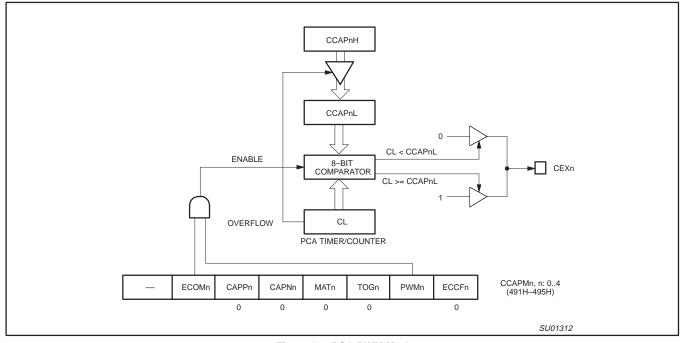

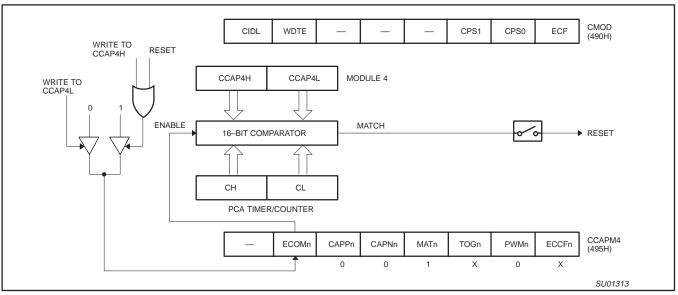

| SWE                            | Software interrupt enable                                                               | 47A                      | _     | SWE7  | SWE6     | SWE5     | SWE4   | SWE3   | SWE2  | SWE1   | 00h                      |