# ANALOG DEVICES

# **Digital Power Factor Correction Controller** with Accurate AC Power Metering

### **Data Sheet**

#### **FEATURES**

Flexible digital power factor correction (PFC) controller Single phase operation (ADP1047); interleaved and bridgeless operation (ADP1048) True rms ac power metering **Enhanced dynamic response Optimized light load efficiency performance Output voltage adjustment Frequency reduction** Inrush current control Switching frequency spread spectrum for improved EMI **External frequency synchronization PMBus compliant** Programmable ac line fault detection and protection Programmable output fault detection and protection Extensive fault protection for high reliability systems Frequency range from 30 kHz to 400 kHz **8 kB EEPROM** Programming via easy-to-use graphical user interface (GUI) APPLICATIONS

AC/DC power supplies for applications **Computing server and storage** Network and communication infrastructure Industrial and medical

#### **GENERAL DESCRIPTION**

The ADP1047/ADP1048 are digital power factor correction (PFC) controllers that provide accurate input power metering capability and inrush current control for ac/dc systems. The ADP1047 is designed for single phase PFC applications; the ADP1048 is designed especially for interleaved and bridgeless PFC applications.

ADP1047/ADP1048

The digital PFC function is based on a conventional boost PFC with multiplication of the output voltage feedback combined with the input current and voltage to provide optimum harmonic correction and power factor for ac/dc systems. All signals are converted into the digital domain to provide maximum flexibility; all key parameters can be reported and adjusted via the PMBus<sup>TM</sup> interface. The ADP1047/ADP1048 allow users to optimize system performance, maximize efficiency across the load range, and reduce design time to market.

The ADP1047/ADP1048 provide accurate rms measurement of input voltage, current, and power. This information can be reported to the microcontroller of the power supply via the PMBus interface.

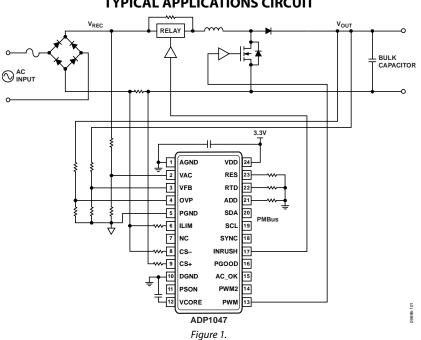

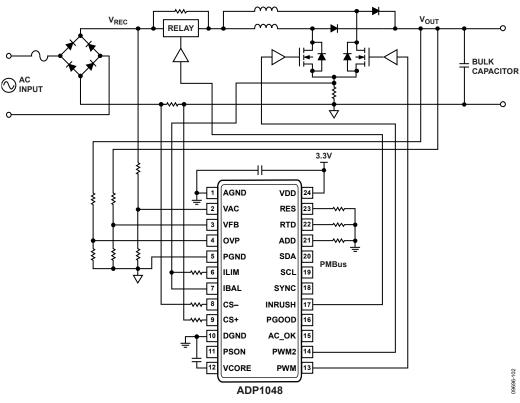

#### **TYPICAL APPLICATIONS CIRCUIT**

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features                                         |

|--------------------------------------------------|

| Applications                                     |

| General Description                              |

| Typical Applications Circuit                     |

| Revision History 4                               |

| Specifications                                   |

| Absolute Maximum Ratings                         |

| Thermal Resistance                               |

| ESD Caution                                      |

| Pin Configurations and Function Descriptions     |

| Functional Block Diagrams11                      |

| Controller Architecture                          |

| Current Sense12                                  |

| RMS Input Overcurrent Protection                 |

| Fast Overcurrent Protection (ILIM Pin)12         |

| Current Balancing (IBAL Pin, ADP1048 Only)14     |

| Voltage Sense14                                  |

| Overvoltage Protection15                         |

| Power Factor Correction Control Loop 17          |

| Digital Compensation Filters17                   |

| Pulse-Width Modulation18                         |

| Duty Cycle Minimum/Maximum Limits18              |

| Auxiliary PWM Output (ADP1047 Only)18            |

| Switching Frequency Programming19                |

| Line Fault Protections and Soft Start Sequencing |

| PSON Operation                                   |

| AC Line Detection                                |

| Soft Start Procedure                             |

| Line Fault Protections                           |

| Advanced Input Power Metering24                  |

| Power Supply System and Fault Monitoring25       |

| Flag Conventions                                 |

| Manufacturer-Specific Flags25                    |

| Standard PMBus Flags                             |

| PMBus Fault Flag Response                        |

| Manufacturer-Specific Flag Response              |

| Monitoring Functions                             |

| First Error Fault 29                             |

| Overtemperature Protection (OTP)                 |

| AC_OK and PGOOD Signals29                        |

| Advanced Features                                        | 30 |

|----------------------------------------------------------|----|

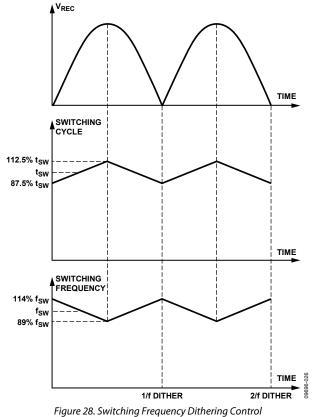

| Frequency Dithering (Spread Spectrum)                    | 30 |

| PWM Frequency Synchronization                            | 30 |

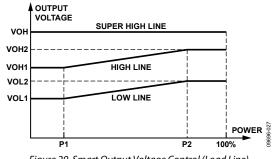

| Smart Output Voltage (Load Line)                         | 30 |

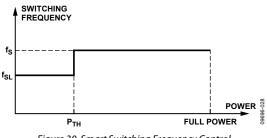

| Smart Switching Frequency                                | 31 |

| Current Loop Filter for Light Load                       | 31 |

| Phase Shedding (ADP1048 Only)                            | 31 |

| Current Loop Feedforward                                 | 31 |

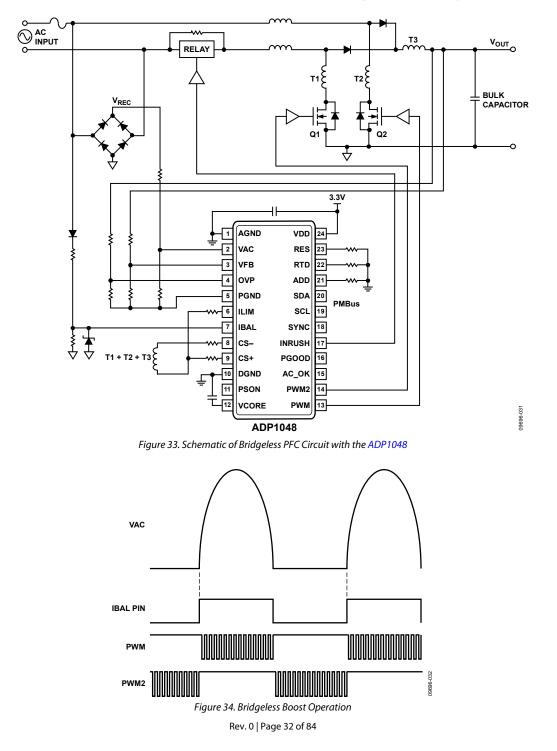

| Bridgeless Boost Operation (ADP1048 Only)                | 32 |

| Power Supply System Calibration and Trim                 | 33 |

| Output Voltage (VFB) Calibration and Trim                | 33 |

| Input Voltage (VAC) Gain and Offset Trim                 | 33 |

| Current Sense Gain and Offset Trim                       | 33 |

| Input Power Gain and Offset Trim                         | 33 |

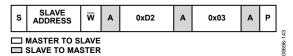

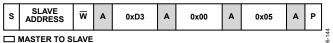

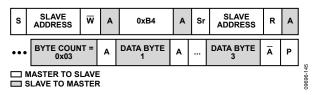

| PMBus Digital Communication                              | 34 |

| Features                                                 | 34 |

| Overview                                                 | 34 |

| PMBus Address                                            | 34 |

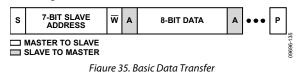

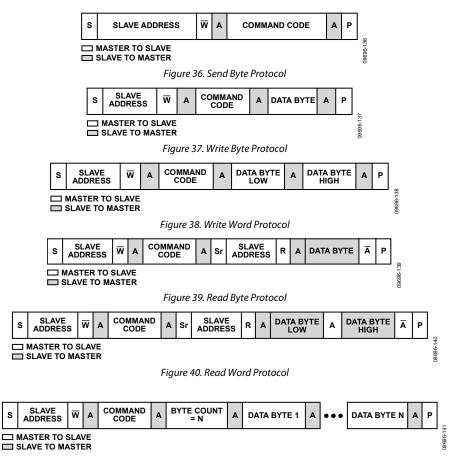

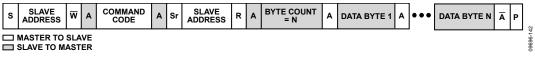

| Data Transfer                                            | 35 |

| General Call Support                                     | 36 |

| Fast Mode                                                | 36 |

| Fault Conditions                                         | 36 |

| Timeout Condition                                        | 36 |

| Data Transmission Faults                                 | 37 |

| Data Content Faults                                      | 37 |

| EEPROM                                                   | 38 |

| Overview                                                 | 38 |

| Page Erase Operation                                     | 38 |

| Read Operation (Byte Read and Block Read)                | 38 |

| Write Operation (Byte Write and Block Write)             |    |

| EEPROM Password                                          | 39 |

| Downloading EEPROM Settings to Internal Registers        | 39 |

| Saving Register Settings into EEPROM                     | 40 |

| EEPROM CRC Checksum                                      | 40 |

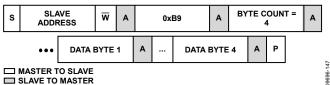

| Software GUI                                             | 41 |

| Standard PMBus Commands Supported by the ADP1047/ADP1048 | 42 |

| Manufacturer-Specific PMBus Commands                     | 43 |

| Detailed Register Descriptions                           | 45 |

| OPERATION Register                                       | 45 |

Rev. 0 | Page 2 of 84

# ADP1047/ADP1048

| ON_OFF_CONFIG Register          | 45 |

|---------------------------------|----|

| CLEAR_FAULTS Command            | 45 |

| WRITE_PROTECT Register          | 45 |

| RESTORE_DEFAULT_ALL Command     | 45 |

| STORE_USER_ALL Command          | 45 |

| RESTORE_USER_ALL Command        | 46 |

| CAPABILITY Register             | 46 |

| VOUT_MODE Register              | 46 |

| VOUT_COMMAND Register           | 46 |

| VOUT_SCALE_LOOP Register        | 46 |

| VOUT_SCALE_MONITOR Register     | 47 |

| VIN_ON Register                 | 47 |

| VIN_OFF Register                | 47 |

| VOUT_OV_FAULT_LIMIT Register    | 47 |

| VOUT_OV_FAULT_RESPONSE Register | 47 |

| VOUT_OV_WARN_LIMIT Register     | 48 |

| VOUT_UV_WARN_LIMIT Register     | 48 |

| VOUT_UV_FAULT_LIMIT Register    | 48 |

| VOUT_UV_FAULT_RESPONSE Register | 49 |

| OT_FAULT_RESPONSE Register      | 49 |

| VIN_OV_FAULT_LIMIT Register     | 50 |

| VIN_OV_FAULT_RESPONSE Register  | 50 |

| VIN_UV_WARN_LIMIT Register      | 51 |

| VIN_UV_FAULT_LIMIT Register     | 51 |

| VIN_UV_FAULT_RESPONSE Register  | 52 |

| IIN_OC_FAULT_LIMIT Register     | 52 |

| IIN_OC_FAULT_RESPONSE Register  | 53 |

| IIN_OC_WARN_LIMIT Register      | 53 |

| PIN_OP_WARN_LIMIT Register      | 54 |

| STATUS_BYTE Register            | 54 |

| STATUS_WORD Register            | 54 |

| STATUS_VOUT Register            | 55 |

| STATUS_INPUT Register           | 55 |

| STATUS_TEMPERATURE Register     | 55 |

| READ_VIN Register               | 55 |

| READ_IIN Register               | 55 |

| READ_VOUT Register              | 56 |

| READ_PIN Register               | 56 |

| PMBUS_REVISION Register         | 56 |

| MFR_ID Register                 | 56 |

| MFR_MODEL Register              | 56 |

| MFR_REVISION Register                             | .56 |

|---------------------------------------------------|-----|

| EEPROM_DATA_00 Through EEPROM_DATA_15<br>Commands | .56 |

| EEPROM_CRC_CHKSUM Register                        | .57 |

| EEPROM_NUM_RD_BYTES Register                      | .57 |

| EEPROM_ADDR_OFFSET Register                       | .57 |

| EEPROM_PAGE_ERASE Register                        | .57 |

| EEPROM_PASSWORD Register                          | .57 |

| FRIM_PASSWORD Register                            | .57 |

| EEPROM_INFO Command                               | .57 |

| CS_FAST_OCP_RESPONSE Register                     | .58 |

| OVP_FAST_OVP_RESPONSE Register                    | .58 |

| DLP_RESPONSE Register                             | .58 |

| VDD3P3_RESPONSE Register                          | .59 |

| VCORE_RESPONSE Register                           | .59 |

| PGOOD_AC_OK_DEBOUNCE_SET Register                 | .59 |

| PSON_SET Register                                 | .60 |

| FLAG_FAULT_ID Register                            | .60 |

| SOFTSTART_FLAGS_BLANK1 Register                   | .61 |

| SOFTSTART_FLAGS_BLANK2 Register                   | .61 |

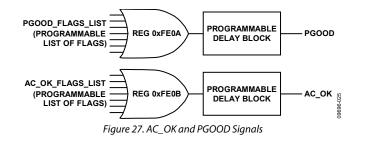

| PGOOD_FLAGS_LIST Register                         | .61 |

| AC_OK_FLAGS_LIST Register                         | .61 |

| PWM and PWM2 Timing Registers                     | .62 |

| PWM_SET Register                                  | .63 |

| PWM_LIMIT Register                                | .63 |

| RTD ADC Offset Trim Setting (MSB) Register        | .63 |

| RTD ADC Offset Trim Setting (LSB) Register        | .63 |

| RTD ADC Gain Trim Setting Register                | .64 |

| DT_FAULT_LIMIT Register                           | .64 |

| DT_WARN_LIMIT Register                            | .64 |

| Switching Frequency Setting Register              | .65 |

| Low Power Switching Frequency Setting Register    | .66 |

| Frequency Dithering Set Register                  | .67 |

| Frequency Synchronization Set Register            | .68 |

| Voltage Loop Filter Gain Register                 | .68 |

| Voltage Loop Filter Zero Register                 | .68 |

| Fast Voltage Loop Filter Gain Register            | .68 |

| Fast Voltage Loop Filter Zero Register            | .68 |

| Fast Voltage Loop Enable Register                 | .68 |

| VAC_THRESHOLD_SET Register                        | .69 |

| VAC_THRESHOLD_READ Register                       | .69 |

Rev. 0 | Page 3 of 84

| n | 9 | ł | a | ( | C | ŀ | 'n | c | 5 | 0 | ł | ŀ |

|---|---|---|---|---|---|---|----|---|---|---|---|---|

| μ | a | Ļ | a | 1 | J | ł | ļ  | C | V | G |   | Ļ |

| MIN_AC_PERIOD_SET Register                                |

|-----------------------------------------------------------|

| MAX_AC_PERIOD_SET Register                                |

| Current Loop Filter Gain for Low Line Input Register      |

| Current Loop Filter Zero for Low Line Input Register      |

| Current Loop Filter Gain for High Line Input Register 70  |

| Current Loop Filter Zero for High Line Input Register 70  |

| Soft Start Set Register70                                 |

| Inrush Set Register                                       |

| FAST_OVP_FAULT_RISE Register71                            |

| FAST_OVP_FAULT_FALL Register71                            |

| FAST OVP Debounce Time Setting Register                   |

| Low Power Mode Operation Threshold Register               |

| Power Metering Offset Trim for Low Line Input Register 72 |

| Power Metering Gain Trim for Low Line Input Register72    |

| High Line Limit Register                                  |

| Low Line Limit Register                                   |

| ILIM_TRIM Register                                        |

| Voltage Loop Output Register                              |

| Exponent Register                                         |

| Read Update Rate Register                                 |

| VIN Scale Monitor Register                                |

| IIN_GSENSE Register                                       |

| CS Fast OCP Blank Register                                |

| CS Fast OCP Setting Register                              |

| Temperature Hysteresis Register                           |

| VAC ADC Gain Trim Register                                |

| VFB ADC Gain Trim Register75                              |

| CS ADC Gain Trim for 500 mV Range Register75              |

| IBAL Gain Register (ADP1048 Only)                         |

| Smart VOUT Low Power Threshold (P1) Register75            |

| Smart VOUT High Power Threshold (P2) Register             |

| Smart VOUT Low Line (VOL1) Register                       |

| Smart VOUT Low Line (VOL2) Register                       |

#### **REVISION HISTORY**

9/11—Revision 0: Initial Version

|   | Smart VOUT High Line (VOH1) Register                                    | 76 |

|---|-------------------------------------------------------------------------|----|

|   | Smart VOUT High Line (VOH2) Register                                    | 76 |

|   | Smart VOUT Upper Limit (VOH) Register                                   | 76 |

|   | Smart VOUT Super High Line Register                                     | 76 |

|   | SYNC Delay Register                                                     | 76 |

|   | SMART_VOUT_SUPER_HIGH_LINE_HYS Register                                 | 77 |

|   | POWER_HYS Register                                                      | 77 |

|   | Advanced Feature Enable Register                                        | 77 |

|   | VOUT_OV_FAULT_HYS Register                                              | 77 |

|   | VIN_UV_FAULT_HYS Register                                               | 77 |

|   | VAC ADC Offset Trim Register                                            | 78 |

|   | CS ADC Offset Trim for 500 mV Range Register                            | 78 |

|   | CS ADC Gain Trim for High (750 mV) Range Register                       | 78 |

|   | CS ADC Offset Trim for High (750 mV) Range Register                     | 78 |

|   | Latched Flag Registers                                                  | 78 |

|   | PWM Value Register                                                      | 79 |

|   | VAC_LINE_PERIOD Register                                                | 79 |

|   | Read Temperature ADC Register                                           | 79 |

|   | Power Metering Offset Trim for High Line Input Register                 | 79 |

|   | Power Metering Gain Trim for High Line Input Register                   | 80 |

|   | Current Loop Filter Gain for Low Line Input and Light<br>Load Register  | 80 |

|   | Current Loop Filter Zero for Low Line Input and Light                   | 00 |

|   | Load Register                                                           | 80 |

|   | Current Loop Filter Gain for High Line Input and Light<br>Load Register | 80 |

|   | Current Loop Filter Zero for High Line Input and Light<br>Load Register | 80 |

|   | Smart VOUT Power Reading Register                                       | 80 |

|   | IBAL Configuration Register (ADP1048 Only)                              | 81 |

|   | Debug Flag Registers                                                    | 81 |

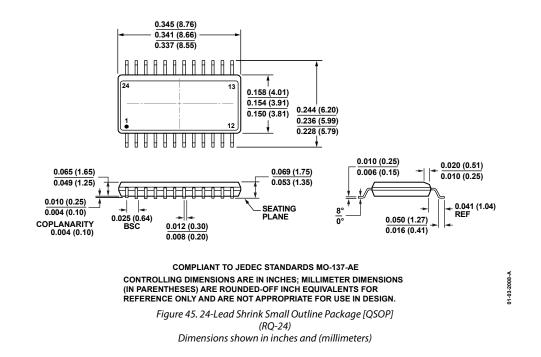

| С | Outline Dimensions                                                      | 83 |

|   | Ordering Guide                                                          | 83 |

## ADP1047/ADP1048

The combination of a flexible, digitally controlled PFC engine and accurate input power metering facilitates the adoption of intelligent power management systems that are capable of making decisions to improve end-user system efficiency. The device supports additional efficiency improvements through programmable frequency reduction at light load and the capability to reduce the output voltage at light load.

The ADP1047/ADP1048 provide enhanced integrated features and functions; the inrush current and soft start control functions provide significant component count reduction with easy design optimization. The devices are designed for high reliability, redundant power supply applications and have extensive and robust protection circuitry: independent overvoltage protection (OVP) and overcurrent protection (OCP), ground continuity monitoring, and ac sensing. Internal overtemperature protection (OTP) is provided whereby the external temperature can be recorded via an external sensing device.

The internal 8 kB EEPROM stores all programmed values and allows standalone control without a microcontroller. All parametric reporting and adjustments can be programmed via an easy-to-use GUI. No complex programming is required.

The ADP1047/ADP1048 operate from a single 3.3 V supply. The devices are available in a 24-lead QSOP package that is specified over an ambient temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Figure 2. Typical Interleaved Application, ADP1048

### **SPECIFICATIONS**

VDD = 3.3 V,  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted.

#### Table 1.

| Parameter                             | Symbol             | Test Conditions/Comments                                                         | Min          | Тур          | Max   | Unit  |

|---------------------------------------|--------------------|----------------------------------------------------------------------------------|--------------|--------------|-------|-------|

| POWER SUPPLY                          |                    |                                                                                  |              |              |       |       |

| Operating Supply Voltage              | VDD                |                                                                                  | 3.0          | 3.3          | 3.6   | V     |

| Supply Current                        | I <sub>DD</sub>    | Normal operation (PSON high) and no load on PWM output                           |              | 17           | 40    | mA    |

| Supply Current for Programming        | I <sub>DD_PK</sub> | During EEPROM programming (50 ms)                                                |              | $I_{DD} + 8$ |       | mA    |

| Shutdown Current                      | IDD_SD             |                                                                                  |              | 100          |       | μA    |

| POWER-ON RESET                        |                    |                                                                                  |              |              |       |       |

| Power-On Reset                        |                    | VDD rising                                                                       | 1.8          |              | 3     | V     |

| Undervoltage Lockout                  | UVLO               | VDD falling                                                                      | 2.75         | 2.85         | 2.95  | V     |

| Overvoltage Lockout                   | OVLO               |                                                                                  | 3.7          | 3.9          | 4.1   | V     |

| VCORE PIN                             |                    |                                                                                  |              |              |       |       |

| Output Voltage Range                  |                    | Temperature = 25°C                                                               | 2.26         | 2.45         | 2.65  | V     |

| PWM OUTPUTS                           |                    | PWM, PWM2 pins                                                                   |              |              |       |       |

| Output Low Voltage                    | VPWMOL             | Sink current = 10 mA                                                             |              |              | 0.4   | V     |

| Output High Voltage                   | VPWMOH             | Source current = 10 mA                                                           | VDD –<br>0.4 |              |       | V     |

| Rise Time                             |                    | C <sub>LOAD</sub> = 50 pF                                                        |              | 4            |       | ns    |

| Fall Time                             |                    | $C_{LOAD} = 50 \text{ pF}$                                                       |              | 4            |       | ns    |

| VAC ADC                               |                    |                                                                                  |              |              |       |       |

| Input Voltage Range                   |                    |                                                                                  | 0            |              | 1.6   | V     |

| Leakage Current                       |                    |                                                                                  |              |              | 5     | μA    |

| Equivalent Resolution                 |                    |                                                                                  |              | 11           |       | Bits  |

| Voltage Sense Measurement<br>Accuracy |                    | From 2.5% to 97.5% of input voltage range                                        |              |              |       |       |

|                                       |                    | VDD = 3.3 V                                                                      | -1.3         |              | +1.3  | % FSR |

|                                       |                    | VDD varies from 3.0 V to 3.6 V                                                   | -1.99        |              | +1.99 | % FSR |

| VFB ADC                               |                    |                                                                                  |              |              |       |       |

| Input Voltage Range                   |                    |                                                                                  | 0            |              | 1.6   | V     |

| Equivalent Resolution                 |                    |                                                                                  |              | 11           |       | Bits  |

| Voltage Sense Measurement<br>Accuracy |                    | From 2.5% to 97.5% of input voltage range                                        |              |              |       |       |

|                                       |                    | VDD = 3.3 V                                                                      | -1.2         |              | +1.2  | % FSR |

|                                       |                    | VDD varies from 3.0 V to 3.6 V                                                   | -1.72        |              | +1.72 | % FSR |

| CURRENT SENSE ADC                     |                    |                                                                                  |              |              |       |       |

| High Input Voltage Range              |                    |                                                                                  | 0            |              | 750   | mV    |

| Low Input Voltage Range               |                    |                                                                                  | 0            |              | 500   | mV    |

| Equivalent Resolution                 |                    |                                                                                  |              | 11           |       | Bits  |

| Current Sense Measurement<br>Accuracy |                    | From 0% to 97.5% of input voltage range                                          |              |              |       |       |

|                                       |                    | VDD = 3.3 V                                                                      | -1.7         |              | +1.7  | % FSR |

|                                       |                    | VDD varies from 3.0 V to 3.6 V                                                   | -2.06        |              | +2.06 | % FSR |

| Current Source                        |                    | 10 k $\Omega$ level shifting resistor, V <sub>CS+</sub> – V <sub>CS-</sub> = 0 V |              |              |       |       |

| High Input                            |                    |                                                                                  |              | 74           |       | μA    |

| Low Input                             |                    |                                                                                  |              | 84           |       | μA    |

| Current Source Resolution             |                    |                                                                                  |              | ±0.03        |       | %     |

| RTD PIN                               |                    |                                                                                  |              |              |       |       |

| Input Voltage Range                   |                    |                                                                                  | 0            |              | 0.8   | V     |

| Current Source Accuracy               |                    |                                                                                  | 9            | 10           | 11    | μΑ    |

| Equivalent Resolution                 |                    |                                                                                  |              | 14           |       | Bits  |

Rev. 0 | Page 6 of 84

# ADP1047/ADP1048

| Parameter                          | Symbol       | Test Conditions/Comments                                     | Min   | Тур  | Max   | Unit   |

|------------------------------------|--------------|--------------------------------------------------------------|-------|------|-------|--------|

| Voltage Sense Measurement          |              | From 2.5% to 97.5% of input voltage range                    |       |      |       |        |

| Accuracy                           |              |                                                              |       |      |       |        |

|                                    |              | VDD = 3.3 V                                                  | -1.52 |      | +1.52 | % FSR  |

|                                    |              | VDD varies from 3.0 V to 3.6 V                               | -1.97 |      | +1.97 | % FSR  |

| IBAL PIN (ADP1048 ONLY)            |              | Interleaved operation mode                                   |       |      |       |        |

| Input Voltage Range                |              |                                                              | 0     |      | 0.8   | V      |

| Equivalent Resolution              |              |                                                              | _     | 11   | _     | Bits   |

| Channel Mismatch                   |              | DC input and acquiring time window on each channel is 526 µs | -5    |      | +5    | % FSR  |

| POWER METER                        |              |                                                              |       |      |       |        |

| Measurement Accuracy               |              | From 2.5% to 97.5% of input voltage range                    |       |      |       |        |

|                                    |              | VDD = 3.3 V                                                  | -2.3  |      | +2.3  | % FSR  |

|                                    |              | VDD varies from 3.0 V to 3.6 V                               | -2.75 |      | +2.75 | % FSR  |

| SWITCHING FREQUENCY                |              |                                                              |       |      |       |        |

| Frequency Range                    |              | Programmable                                                 | 30    |      | 400   | kHz    |

| Accuracy                           |              |                                                              | -3.85 |      | +3.85 | %      |

| OSCILLATOR, CLOCK, AND PLL         |              |                                                              |       |      |       |        |

| Oscillator Frequency               |              |                                                              | 1.516 | 1.56 | 1.62  | MHz    |

| Digital Clock Frequency            |              |                                                              |       | 200  |       | MHz    |

| PLL Frequency                      |              |                                                              |       | 200  |       | MHz    |

| RES PIN                            |              |                                                              |       |      |       |        |

| Temperature Stability              |              |                                                              | -120  | 0    | +120  | ppm/°C |

| PGOOD, AC_OK PINS                  |              |                                                              |       |      |       |        |

| Output Low Voltage                 |              |                                                              |       |      | 0.8   | V      |

| Output High Voltage                |              |                                                              | 2.0   |      |       | V      |

| FAST OVERCURRENT PROTECTION        |              |                                                              |       |      |       |        |

| Fast OCP Threshold                 |              |                                                              |       |      |       |        |

| Positive Signal                    |              |                                                              | 1455  | 1500 | 1550  | mV     |

| Negative Signal                    |              |                                                              | 452   | 500  | 523   | mV     |

| Current Source Accuracy            |              |                                                              |       | ±4.4 |       | %      |

| Current Source Resolution          |              |                                                              |       | ±3.2 |       | %      |

| Propagation Delay                  |              | From threshold trip to PWM disabled                          |       |      | 140   | ns     |

| RMS OVERCURRENT PROTECTION         |              |                                                              |       |      |       |        |

| RMS Accuracy                       |              | VDD = 3.3 V                                                  | -1.7  |      | +1.7  | %      |

| Propagation Delay                  |              | AC line frequency = 50 Hz                                    | -     | 12   |       | ms     |

| FAST OVERVOLTAGE PROTECTION        |              |                                                              |       |      |       |        |

| Fast OVP Threshold                 |              | Fully programmable from 1 V to 1.5 V                         |       |      |       |        |

| Rising                             |              | Register 0xFE2F, Bits[6:0]                                   | 1     |      | 1.5   | V      |

| Falling                            |              | Register 0xFE30, Bits[6:0]                                   | 1     |      | 1.5   | V      |

| OVP Threshold Minimum Step         |              |                                                              |       | 3.9  |       | mV     |

| Accuracy                           |              |                                                              | -4    |      | +4    | LSB    |

| Propagation Delay (Latency)        |              | Does not include blanking/debounce                           |       | 10   | 120   | ns     |

| Blanking Time                      |              | Blanking after threshold reprogramming                       |       | 10   |       | μs     |

| ACCURATE OVERVOLTAGE<br>PROTECTION |              |                                                              |       |      |       |        |

| Accuracy                           |              | VDD = 3.3 V                                                  | -1.2  |      | +1.2  | %      |

| Propagation Delay                  |              | AC line frequency = 50 Hz                                    |       | 12   |       | ms     |

| OPEN-LOOP PROTECTION               |              |                                                              |       |      |       |        |

| VFB Error Threshold                | $\Delta VFB$ |                                                              | ±33   | ±111 | ±242  | mV     |

| Propagation Delay                  |              |                                                              |       | 200  |       | ns     |

| Debounce Time                      |              |                                                              |       | 10   |       | μs     |

| Common-Mode Input Range            |              |                                                              | -0.2  |      | +1.6  | V      |

Rev. 0 | Page 7 of 84

| Parameter                  | Symbol              | Test Conditions/Comments | Min    | Тур | Мах | Unit   |

|----------------------------|---------------------|--------------------------|--------|-----|-----|--------|

| SDA, SCL PINS              |                     | VDD = 3.3 V              |        |     |     |        |

| Input Low Voltage          |                     |                          |        |     | 0.8 | V      |

| Input High Voltage         |                     |                          | 2.2    |     |     | V      |

| Output Low Voltage         |                     |                          |        |     | 0.4 | V      |

| Pull-Up Current            |                     |                          | 100    |     | 350 | μA     |

| Leakage Current            |                     |                          | -5     |     | +5  | μA     |

| SERIAL BUS TIMING          |                     |                          |        |     |     |        |

| Clock Frequency            |                     |                          | 10     | 100 | 400 | kHz    |

| Glitch Immunity            | tsw                 |                          |        |     | 50  | ns     |

| Bus Free Time              | <b>t</b> BUF        |                          | 1.3    |     |     | μs     |

| Start Condition Hold Time  | thd;sta             |                          | 0.6    |     |     | μs     |

| Start Condition Setup Time | t <sub>su;sta</sub> |                          | 0.6    |     |     | μs     |

| Stop Condition Setup Time  | tsu;sto             |                          | 0.6    |     |     | μs     |

| Data Hold Time             | thd;dat             |                          | 300    |     |     | ns     |

| Data Setup Time            | t <sub>su;dat</sub> |                          | 100    |     |     | ns     |

| SCL Low Timeout            | <b>t</b> timeout    |                          | 25     |     | 35  | ms     |

| SCL Low Time               | t <sub>LOW</sub>    |                          | 1.3    |     |     | μs     |

| SCL High Time              | thigh               |                          | 0.6    |     |     | μs     |

| Clock Low Extend Time      | tlow;sext           |                          |        |     | 25  | ms     |

| SCL, SDA Rise Time         | t <sub>R</sub>      |                          | 20     |     | 300 | ns     |

| SCL, SDA Fall Time         | t <sub>F</sub>      |                          | 20     |     | 300 | ns     |

| EEPROM RELIABILITY         |                     |                          |        |     |     |        |

| Endurance                  |                     |                          | 10,000 |     |     | Cycles |

| Data Retention             |                     | Temperature = 85°C       | 20     |     |     | Years  |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                          | Rating                |

|------------------------------------|-----------------------|

| Supply Voltage (Continuous), VDD   | 3.8 V                 |

| Digital Core Supply Voltage, VCORE | 2.7 V                 |

| Digital Pins                       | –0.3 V to VDD + 0.3 V |

| Analog Pins                        | –0.3 V to VDD + 0.3 V |

| AGND to DGND                       | –0.3 V to +0.3 V      |

| Operating Temperature Range        | -40°C to +85°C        |

| Storage Temperature Range          | –65°C to +150°C       |

| Maximum Junction Temperature       | 150°C                 |

| Peak Solder Reflow Temperature     |                       |

| SnPb Assemblies (10 sec to 30 sec) | 240°C                 |

| RoHS-Compliant Assemblies          | 260°C                 |

| (20 sec to 40 sec)                 |                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type         | θ」Α  | θıc | Unit |

|----------------------|------|-----|------|

| 24-Lead QSOP (RQ-24) | 44.4 | 6.4 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

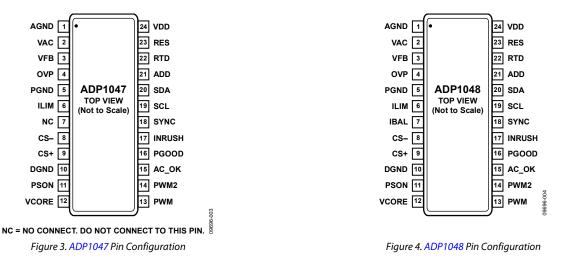

### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                    |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AGND     | Analog Ground. AGND should be connected directly to DGND.                                                                                                                                      |

| 2       | VAC      | Input Line Voltage Sense. The VAC signal is referred to PGND.                                                                                                                                  |

| 3       | VFB      | Feedback Voltage Sense. The VFB signal is referred to PGND. VFB is the feedback signal for PFC power circuit                                                                                   |

|         |          | regulation. It is used as the analog voltage input to the VFB ADC.                                                                                                                             |

| 4       | OVP      | Overvoltage Protection. The OVP signal is referred to PGND. This signal is used for redundant overvoltage protection.                                                                          |

| 5       | PGND     | Power Ground. PGND is the connection for the ground line of the power rail. There should be a low impedance path between PGND and AGND.                                                        |

| 6       | ILIM     | Fast Current Limiting. This pin is referred to PGND.                                                                                                                                           |

| 7       | NC/IBAL  | ADP1047: No Connect. Do not connect to this pin.                                                                                                                                               |

|         |          | ADP1048: Current Balancing Input for Interleaved Operation. The IBAL input is referred to PGND.                                                                                                |

| 8       | CS–      | Differential Current Sense Negative Input. The CS– signal is used for current measurement, monitoring, and protection. A 0.1%, 10 k $\Omega$ resistor must be used to connect to this circuit. |

| 9       | CS+      | Differential Current Sense Positive Input. The CS+ signal is used for current measurement, monitoring, and protection. A 0.1%, 10 k $\Omega$ resistor must be used to connect to this circuit. |

| 10      | DGND     | Digital Ground. DGND should be connected directly to AGND.                                                                                                                                     |

| 11      | PSON     | Power Supply Enable Signal. The PSON signal is used to enable/disable the PFC controller. The PSON signal is referred to DGND.                                                                 |

| 12      | VCORE    | Output of 2.5 V Regulator. Connect a 100 nF capacitor from VCORE to DGND.                                                                                                                      |

| 13      | PWM      | PWM Output for PFC Regulation. The PWM signal is referred to AGND.                                                                                                                             |

| 14      | PWM2     | Auxiliary PWM Output (ADP1047) or Interleaved PWM Output (ADP1048). The PWM2 signal is referred to AGND.                                                                                       |

| 15      | AC_OK    | Open-Drain Output. User-configurable signal from a combination of flags. The AC_OK signal is referred to AGND.                                                                                 |

| 16      | PGOOD    | Open-Drain Output. User-configurable signal from a combination of flags. The PGOOD signal is referred to AGND.                                                                                 |

| 17      | INRUSH   | Inrush Current Control Signal to an External Inrush Driver. This open-drain output is referred to AGND.                                                                                        |

| 18      | SYNC     | Allows parallel PFC controllers to synchronize to reduce interference. This pin is referred to DGND.                                                                                           |

| 19      | SCL      | I <sup>2</sup> C Serial Clock Input. The SCL signal is referred to DGND.                                                                                                                       |

| 20      | SDA      | I <sup>2</sup> C Serial Data Input and Output (Open-Drain). The SDA signal is referred to DGND.                                                                                                |

| 21      | ADD      | Address Select Input. Connect a resistor from ADD to AGND (see the PMBus Address section).                                                                                                     |

| 22      | RTD      | Thermistor Input. A thermistor is placed from RTD to AGND. The RTD signal is referred to AGND.                                                                                                 |

| 23      | RES      | Internal Voltage Reference. Connect a 0.1%, 50 k $\Omega$ resistor from RES to AGND.                                                                                                           |

| 24      | VDD      | Positive Supply Input. The range is from 3.0 V to 3.6 V. The VDD signal is referred to AGND.                                                                                                   |

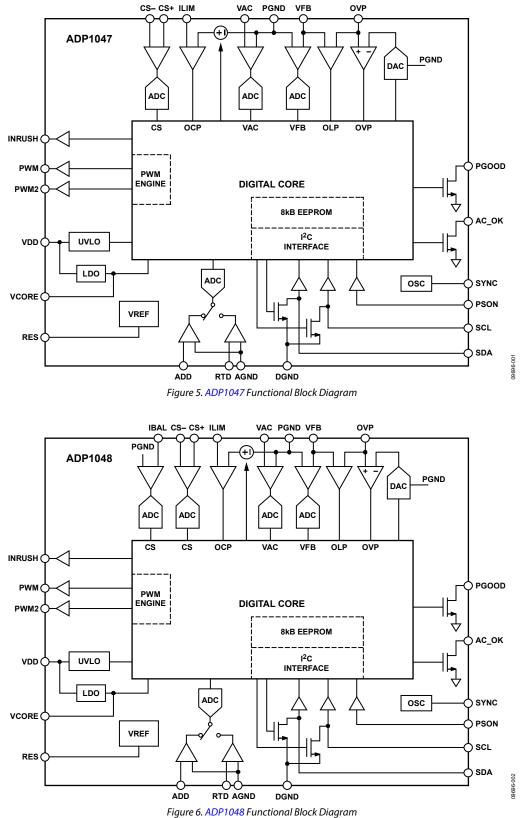

### FUNCTIONAL BLOCK DIAGRAMS

jure 0. ADF 1048 Functional Block Diagra

Rev. 0 | Page 11 of 84

### **CONTROLLER ARCHITECTURE**

The ADP1047/ADP1048 integrate the following functions:

- Power factor correction control loop (see the Power Factor Correction Control Loop section)

- Advanced input power metering (see the Advanced Input Power Metering section)

- PMBus digital communication (see the PMBus Digital Communication section)

This section describes the internal architecture of the chip.

#### **CURRENT SENSE**

Current sensing is used for the control, protection, and monitoring of the PFC stage. For normal operation, the power factor correction control loop requires inductor current information. The typical implementation uses a sense resistor on the input bus. A combination of two current transformers in series with the power switch and the boost diode can be used to reconstruct the inductor current and minimize losses in the resistive shunt, but, in general, a good quality shunt resistor provides much better accuracy in measuring input current and input power.

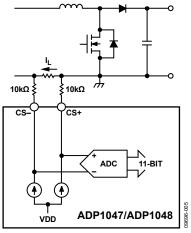

The inputs to the current sense ADC are differential. A pair of matched current sources is provided to level shift the negative signal across the current sense element in the input range of the current sense ADC (see Figure 7).

Figure 7. Current Sense Configuration

The current sense can be calibrated digitally to remove any errors due to external components (see the Current Sense Gain and Offset Trim section). This calibration can be performed in the production environment; the settings are saved in the EEPROM of the ADP1047/ADP1048.

The output of the  $\Sigma$ - $\Delta$  ADC is used for the following purposes:

- The output is decimated at the switching frequency for the control loop. The effective number of bits (ENOB) is >7 when the current loop bandwidth is 10 kHz; the ENOB is >10 when the current loop bandwidth is 1 kHz.

- The 11-bit result is calculated and updated at each half line cycle for high accuracy ac line current and input power monitoring and for overcurrent protection (accurate OCP).

#### **RMS INPUT OVERCURRENT PROTECTION**

The ADP1047/ADP1048 provide rms overcurrent protection (OCP). RMS OCP (or accurate OCP) is distinct from the instantaneous pulse-by-pulse fast overcurrent protection and is based on the rms value of the input ac current.

The measured value is compared to the limit set in the IIN\_OC\_FAULT\_LIMIT register (Register 0x5B) at the end of each half cycle of the ac line. If the limit is exceeded, the action programmed in the IIN\_OC\_FAULT\_RESPONSE register (Register 0x5C) is triggered.

In addition, an input current warning limit can be programmed in the IIN\_OC\_WARN\_LIMIT register (Register 0x5D). This warning limit has no action attached to it, but it sets flags in the STATUS\_BYTE register (Register 0x78, Bit 0), the STATUS\_WORD register (Register 0x79, Bit 13), and the STATUS\_INPUT register (Register 0x7C, Bit 1).

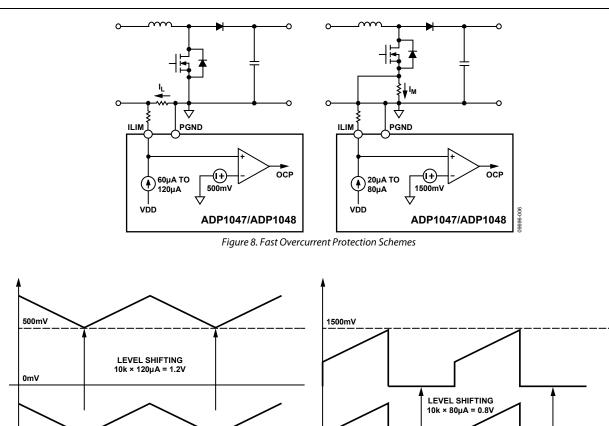

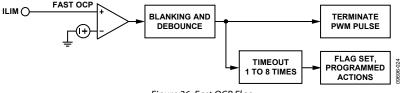

#### **FAST OVERCURRENT PROTECTION (ILIM PIN)**

A dedicated current limiting pin (ILIM) is provided to protect the part from pulse-by-pulse overcurrent events. When the threshold is crossed, the PWM pulse is terminated. This action is independent of any programming of the fast OCP flag. The next switching cycle resumes normally. Additional actions can be programmed (see Table 5).

The OCP comparator on the ILIM pin can accept positive or negative signals; the pin is referred to PGND (power ground) and has programmable level shifting current sources (see Table 5). These sources can be changed during normal operation to adapt to the level at which the overcurrent protection is triggered.

The OCP comparator also features programmable blanking and debounce times (see Table 5). If OCP is triggered, the PWM signal is terminated and operation resumes at the next switching cycle unless a different action is specified for the fast OCP response in Register 0xFE00.

# ADP1047/ADP1048

700-96960

Figure 9. Level Shifting and Threshold for OCP

0mV

| Parameter                      | Values or Options                                                                                                                                                   | Comments                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Debounce Time                  | 40 ns, 80 ns, 120 ns, 240 ns                                                                                                                                        | Register 0xFE3D, Bits[4:3]                                    |

| Blanking Time                  | 40 ns, 80 ns, 120 ns, 160 ns, 200 ns, 400 ns, 600 ns, 800 ns                                                                                                        | Blanking from the leading edge;<br>Register 0xFE3D, Bits[2:0] |

| Propagation Delay              | 140 ns typical                                                                                                                                                      | Fixed value; does not include blanking or debounce            |

| Threshold Value and Polarity   | 500 mV (negative); 1500 mV (positive)                                                                                                                               | Fixed values                                                  |

| Level Shifting Current Sources | 60 μΑ, 80 μΑ, 100 μΑ, 120 μΑ (negative)<br>20 μΑ, 40 μΑ, 60 μΑ, 80 μΑ (positive)                                                                                    | Register 0xFE3E, Bits[7:5]                                    |

| Actions for Fast OCP           | Ignore (still terminates the PWM pulse); allow n switching cycles, then shut down and soft start; allow n switching cycles, then shut down and wait for PSON signal | n = 1, 2, 4, 8; Register 0xFE00, Bits[7:6]                    |

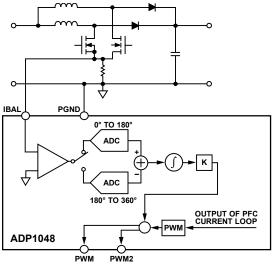

#### CURRENT BALANCING (IBAL PIN, ADP1048 ONLY)

The ADP1048 has a dedicated circuit to maintain current balance in each interleaved phase when operating in interleaved PFC topology. This ensures that each interleaved phase provides equal power regardless of the tolerance of the inductor and the boost switch driving circuitry.

The input is through the IBAL pin specifically provided for the ADP1048. The current balancing circuit monitors the current flowing in both switches of the interleaved PFC topology and stores this information. It compensates the PWM signals, ensuring equal current flow to balance the current between interleaved phases. Several switching cycles are required for the circuit to operate effectively. The current balance settings are programmed in Register 0xFE43 and Register 0xFE95.

Figure 10. Current Balancing (IBAL) for the ADP1048

#### **VOLTAGE SENSE**

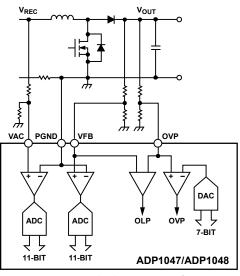

Voltage sensing is used for the control, protection, and monitoring of the PFC stage. Input and output voltages are sensed using dedicated ADCs and references (see Figure 11).

Figure 11. Typical Voltage Sense Configuration

The voltage sense can be calibrated digitally to remove any errors due to external components (see the Output Voltage (VFB) Calibration and Trim section). This calibration can be performed in the production environment; the settings are saved in the EEPROM of the ADP1047/ADP1048.

#### Input Voltage Sensing (VAC Pin)

The VAC pin is used for the monitoring and protection of the rectified power supply input voltage. The sense point on the power rail requires an external resistor divider to bring the signal within the operating input range of the ADC (0 V to 1.6 V). This scaled-down signal is fed into a high speed  $\Sigma$ - $\Delta$  ADC.

The output of the  $\Sigma$ - $\Delta$  ADC goes to the digital filter and is used for the following purposes:

- The output is decimated at the switching frequency for the control loop. The effective number of bits (ENOB) is >7 when the current loop bandwidth is 10 kHz; the ENOB is >10 when the current loop bandwidth is 1 kHz.

- The 11-bit result is calculated and updated at each half line cycle for high accuracy input voltage and power monitoring.

#### **Output Voltage Sensing (VFB Pin)**

The VFB pin is used for the control, monitoring, and protection of the output voltage. This voltage is the main feedback loop for the power supply control loop. The sense point on the power rail requires an external resistor divider to bring the signal within the operating input range of the ADC (0 V to 1.6 V). This scaled-down signal is fed into a high speed  $\Sigma$ - $\Delta$  ADC.

The output of the  $\Sigma$ - $\Delta$  ADC goes to the digital filter and is used for the following purposes:

- The 11-bit result is used at each half line cycle for the normal control loop to control the value of the output voltage.

- The 10-bit, 1.5 kHz update rate is used for the fast voltage control loop to control the value of the output voltage during large transients.

To reduce the current distortion from the output voltage feedback, a prefilter is implemented before the voltage loop filter. The prefilter detects the zero-crossing point of the input voltage to identify the half input line cycle. The prefilter then performs an averaging function for the sampled VFB signal during this half line cycle. In this way, the fundamental frequency of the output bulk voltage ripple and its harmonics are significantly attenuated.

#### **OVERVOLTAGE PROTECTION**

The ADP1047/ADP1048 have two OVP circuits: an ADC-based comparator and a fast comparator.

#### Accurate Overvoltage Protection (VFB Pin)

Overvoltage protection (OVP) is implemented using the information available on the output of the VFB ADC. The information from the VFB ADC is averaged over one half the ac line frequency; therefore, the response of this OVP is relatively slow.

The threshold for the accurate OVP is fully programmable using the VOUT\_OV\_FAULT\_LIMIT register (Register 0x40). The programmed value is the dc average voltage.

When the accurate OVP threshold is crossed, the accurate OVP flag is set. The response to this flag can be programmed for one of several actions using the VOUT\_OV\_FAULT\_RESPONSE register (Register 0x41). If the disable PWM option is selected, a voltage hysteresis can be programmed for the accurate OVP threshold using Register 0xFE50.

#### Fast Overvoltage Protection (OVP Pin)

A fast OVP mode is implemented using a programmable comparator on the OVP pin. Fast OVP is used for overvoltage protection of the bulk capacitors and to provide open-loop protection. The sense point on the power rail requires an external resistor divider to match the divider applied to VFB. This separate divider introduces a level of redundancy in sensing the output voltage to improve system reliability.

If the voltage divider on the VFB pin is damaged or drifts in value, the OVP pin can still detect an overvoltage condition and take the appropriate programmed action.

The fast OVP signal is fed into a comparator with a programmable threshold to set the trip point for overvoltage. The threshold is set using a DAC.

| Parameter            | Values or Options                                                                                                                | Comments                                                                                             |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Debounce Time        | 120 ns, 240 ns, 480 ns, 640 ns                                                                                                   | Minimum duration of pulse to be considered;<br>programmable using Register 0xFE31, Bits[1:0]         |

| Blanking Time        | 10 μs (fixed)                                                                                                                    | Duration of time while the comparator is blanked<br>and the threshold changes from rising to falling |

| Propagation Delay    | 120 ns max (fixed)                                                                                                               | Does not include blanking or debounce                                                                |

| Threshold Rising     | 1 V to 1.5 V                                                                                                                     | Programmable using Register 0xFE2F, Bits[6:0]                                                        |

| Threshold Falling    | 1 V to 1.5 V                                                                                                                     | Programmable using Register 0xFE30, Bits[6:0]                                                        |

| Actions for Fast OVP | Immediate shutdown and wait for PSON;<br>disable PWM until the flag is cleared;<br>shut down and soft start; ignore (do nothing) | Register 0xFE01, Bits[7:6]                                                                           |

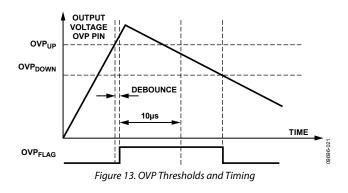

Figure 12 shows an example of the output voltage and the OVP thresholds set. The rising and falling thresholds, FAST\_OVP\_FAULT\_RISE and FAST\_OVP\_FAULT\_FALL, respectively, are used for fast OVP protection. FAST\_OVP\_FAULT\_RISE corresponds to OVP<sub>UP</sub>, which is the trip point for overvoltage protection (see Figure 13). FAST\_OVP\_FAULT\_FALL corresponds to OVP<sub>DOWN</sub>, which is the reset point for the fast OVP.

When the rising threshold is triggered, the programmed action is applied and the threshold is switched to the programmed falling threshold (if the programmed falling threshold is different from the rising threshold).

A blanking time is applied when the thresholds are switched to avoid spurious signals (see the timing diagram in Figure 13). A programmable debounce time is applied to the OVP signal as well to avoid false triggering.

The rising and falling thresholds are programmable from 1 V to 1.5 V (at the OVP pin) using Register 0xFE2F and Register 0xFE30, respectively.

#### **Open-Loop Protection**

Open-loop protection detects differences between the OVP and VFB pins. Identical resistor dividers are applied to these pins; therefore, if a voltage difference is present, it means that one or more resistors in the dividers have the wrong values or are not connected. In this case, it is usually recommended that the user shut down the system to prevent damage.

The open-loop protection detects a difference in voltage in excess of  $\sim$ 100 mV, which equates to approximately 6.6% of the full-scale range.

A debounce time of  $10 \ \mu s$  is added to avoid false triggering. If filtering capacitors are applied to the OVP and VFB pins, care must be taken to make sure that the time constant difference does not exceed  $10 \ \mu s$ .

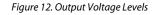

FAST\_OVP\_FAULT\_RISE = 435V (REG 0xFE2F)

FAST OVP

VOUT\_OV\_WARN\_LIMIT = 420V (REG 0x42)

PROGRAMMING

FAST\_OVP\_FAULT\_FALL = 400V (REG 0xFE30)

1.0V

VOUT\_COMMAND = 385V (REG 0x21)

VOUT\_COMMAND = 385V (REG 0x21)

VOUT\_UV\_FAULT\_LIMIT = 200V (REG 0x44)

VOUT\_OV\_FAULT\_LIMIT = 450V (REG 0x40)

ADC INPUT RANGE = 1.6V

1.6V

0.5V

| Parameter         | Values or Options                                                                                                                | Comments                                   |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Debounce Time     | 10 µs (fixed)                                                                                                                    | Minimum duration of pulse to be considered |

| Propagation Delay | 200 ns (fixed)                                                                                                                   | Does not include debounce                  |

| Actions for OLP   | Immediate shutdown and wait for PSON;<br>disable PWM until the flag is cleared;<br>shut down and soft start; ignore (do nothing) | Register 0xFE02, Bits[7:6]                 |

#### Table 7. Programmable Options for Open-Loop Protection (OLP)

ADC FULL

RANGE

# **POWER FACTOR CORRECTION CONTROL LOOP**

The ADP1047/ADP1048 implement the average current mode power factor correction control loop using a traditional multiplier approach. The implementation of the loop is digital, and all the signals are converted from analog to digital before they are processed by the control loop.  $\Sigma$ - $\Delta$  ADCs are used to achieve high performance, cost-effective implementation. Each ADC has its own dedicated voltage reference.

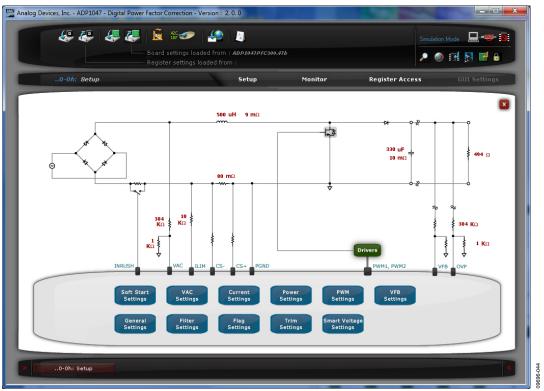

#### DIGITAL COMPENSATION FILTERS

The ADP1047/ADP1048 are digital PFC controllers with ac power monitoring. They are implemented in the digital domain using a dedicated state machine, which allows the user to program the loop response specifically, with no need for external loop compensation.

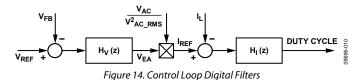

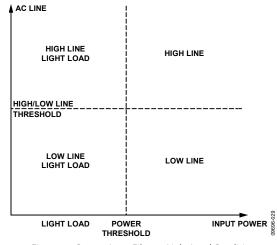

The detailed control loop configuration is illustrated in Figure 14.  $V_{REF}$  is the digital reference voltage setting;  $V_{FB}$  is the sensed feedback voltage of the output. The difference between  $V_{REF}$  and  $V_{FB}$  is processed first by the voltage loop filter ( $H_V$ ). Its output,  $V_{EA}$ , is then multiplied by the instantaneous rectified input voltage,  $V_{AC}$ , and divided by the square of the rms value of  $V_{AC}$ . The result,  $I_{REF}$ , is used as the reference signal for the current. The output of the current loop filter ( $H_I$ ) is the duty cycle command. The mathematical expression is

$$I_{REF} = \frac{V_{EA} \times V_{AC}}{V_{AC\_RMS}^2}$$

Both the voltage loop and current loop digital compensating filters,  $H_V(z)$  and  $H_I(z)$ , are programmable. The filter transfer function in the digital domain is

$$H(z) = k \times b \times \frac{\left(z - \frac{a}{256}\right)}{\left(z - 1\right)}$$

#### where:

*a* is the filter zero.

*b* is the filter gain.

*k* is related to the switching frequency.

The frequency gains and zero locations can all be programmed individually to tailor the loop response to the application. It is recommended that the Analog Devices, Inc., GUI software be used to program the filter (see the Software GUI section). The GUI displays the filter response in Bode plot format and can be used to calculate all stability criteria for the power supply.

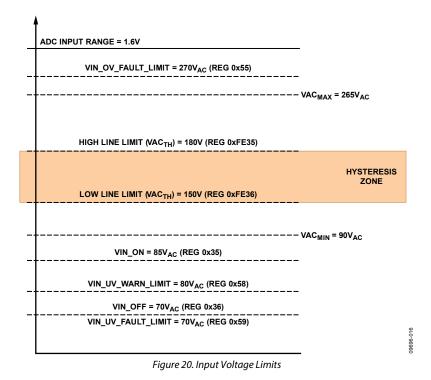

#### **Optimized Compensation Filters**

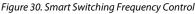

Instead of a single programmable compensation filter, the ADP1047/ADP1048 offer the following filter presets so that the dynamic response of the control loop can be tailored to optimize different operating conditions.

- Low line current filter

- High line current filter

- Fast voltage compensation filter

The ADP1047/ADP1048 can be configured to switch automatically between the high and low line filters when the rms value of the ac line crosses the programmed threshold between the high and low lines. (The high line threshold is programmed in Register 0xFE35; the low line threshold is programmed in Register 0xFE36.)

The ADP1047/ADP1048 check for the value of the rms input voltage at each half line cycle. When a transition between the high and low line threshold is detected, the part waits for four full line cycles before switching to the correct filter at the zero crossing of the input line cycle. This is done to avoid spurious transitions due to a missing or distorted voltage line cycle.

During soft start, one of four combinations of filters can be used, depending on whether the fast loop mode is enabled and whether the high line or low line is detected for soft start (see Table 8).

#### Table 8. Summary of the PFC Digital Compensation Filters for Soft Start

| Line Filter | Normal Compensation Filter                      | Fast Voltage Compensation Filter              |

|-------------|-------------------------------------------------|-----------------------------------------------|

| High Line   | High line current filter, normal voltage filter | High line current filter, fast voltage filter |

| Low Line    | Low line current filter, normal voltage filter  | Low line current filter, fast voltage filter  |

### Data Sheet

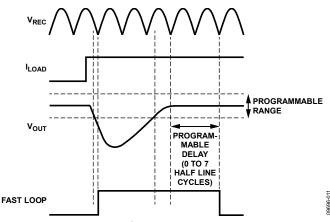

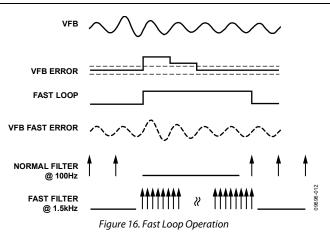

#### Fast Loop Mode

During transients, a fast loop mode is enabled to allow for faster loop responses. Typical timing can be seen in Figure 15. The fast loop mode has separate settings and can be programmed to respond quickly to load transients. The user can disable the fast loop mode if it is not required by the application.

Figure 15. Fast Loop for Transient Response Improvement

When fast loop mode is enabled and the feedback output voltage is out of range from the desired reference value (programmable band of 1.5%, 3%, 6%, or 12%, set in Register 0xFE24), the ADP1047/ADP1048 enter fast loop mode.

To ensure a smooth transition, the ADP1047/ADP1048 switch from the regular filter to the fast loop filter at the zero crossing of the rectified input voltage. When the output voltage returns to regulation within the programmed band, the controller switches back (after a programmable delay of 0 to 7 half line cycles) to the normal loop at the next zero crossing of the rectified input voltage.

If the output voltage does not return to regulation within the programmed band after a fixed time of 630 ms, the control loop automatically switches back to the normal loop.

In the normal compensation loop, the sampling frequency of the output voltage is the same as the ripple oscillation frequency (which is commonly 100 Hz or 120 Hz).

During fast loop operation, the feedback voltage is sampled at 1.5 kHz, and the fast filter is applied to regulate the output voltage. The output voltage is averaged and decimated at 1.5 kHz (see Figure 16).

Based on the requirements of the application, the user can enable or disable the fast loop mode by programming Register 0xFE24. It is recommended that fast loop mode be enabled for the ADP1047/ADP1048 during large load transients. The fast loop mode settings are also used during soft start, even when the fast loop is disabled.

#### **PULSE-WIDTH MODULATION**

The ADP1047/ADP1048 can implement either leading edge or trailing edge modulation. Trailing edge modulation is the more popular modulation scheme. Using trailing edge modulation, the rms ripple current in the bulk capacitors can be reduced when used with downstream converter synchronization. It is recommended that the Analog Devices, Inc., GUI software be used to program PWM (see the Software GUI section).

#### DUTY CYCLE MINIMUM/MAXIMUM LIMITS

The ADP1047/ADP1048 allow the user to program the minimum off time and the minimum on time for the PWM outputs separately, thereby allowing the minimum and maximum duty cycles to be set.

The minimum off time represents the minimum time that the PWM is low during each switching cycle. It can be programmed from 40 ns to 1.2  $\mu$ s in steps of 80 ns using Register 0xFE15, Bits[3:0]. In this way, the maximum duty cycle can be clamped between 96% and 99.8% at the minimum frequency and between 48.8% and 96.8% at the maximum frequency.

The minimum on time is the smallest PWM pulse that the modulator generates on the PWM output. It can be programmed from 0 ns to 1200 ns in steps of 80 ns using Register 0xFE15, Bits[7:4].

#### AUXILIARY PWM OUTPUT (ADP1047 ONLY)

For the ADP1047, the PWM2 pin is the output for the auxiliary PWM, which can be independent of the main PWM output. PWM2 can be used as the control signal for auxiliary switching in the zero-voltage transition soft-switched PFC boost circuit.

#### SWITCHING FREQUENCY PROGRAMMING

The switching frequency of the PWM outputs can be programmed from 30 kHz to 400 kHz using Register 0xFE1B, Bits[5:0] (see Table 9).

| Frequency<br>Setting<br>(Decimal) | Frequency<br>(kHz) | Frequency<br>Setting<br>(Decimal) | Frequency<br>(kHz) | Frequency<br>Setting<br>(Decimal) | Frequency<br>(kHz) | Frequency<br>Setting<br>(Decimal) | Frequency<br>(kHz) |

|-----------------------------------|--------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| 0                                 | 30.05              | 16                                | 107.76             | 32                                | 204.92             | 48                                | 277.78             |

| 1                                 | 32.55              | 17                                | 111.61             | 33                                | 208.33             | 49                                | 284.09             |

| 2                                 | 35.51              | 18                                | 115.74             | 34                                | 211.86             | 50                                | 290.70             |

| 3                                 | 39.06              | 19                                | 120.19             | 35                                | 215.52             | 51                                | 297.62             |

| 4                                 | 43.40              | 20                                | 125.00             | 36                                | 219.30             | 52                                | 304.88             |

| 5                                 | 48.83              | 21                                | 130.21             | 37                                | 223.21             | 53                                | 312.50             |

| 6                                 | 52.06              | 22                                | 135.87             | 38                                | 227.27             | 54                                | 320.51             |

| 7                                 | 55.80              | 23                                | 142.05             | 39                                | 231.48             | 55                                | 328.95             |

| 8                                 | 60.10              | 24                                | 148.81             | 40                                | 235.85             | 56                                | 337.84             |

| 9                                 | 65.10              | 25                                | 156.25             | 41                                | 240.38             | 57                                | 347.22             |

| 10                                | 71.02              | 26                                | 164.47             | 42                                | 245.10             | 58                                | 357.14             |

| 11                                | 78.13              | 27                                | 173.61             | 43                                | 250.00             | 59                                | 367.65             |

| 12                                | 86.81              | 28                                | 183.82             | 44                                | 255.10             | 60                                | 378.79             |

| 13                                | 97.66              | 29                                | 195.31             | 45                                | 260.42             | 61                                | 390.63             |

| 14                                | 100.81             | 30                                | 198.41             | 46                                | 265.96             | 62                                | 403.23             |

| 15                                | 104.17             | 31                                | 201.61             | 47                                | 271.74             | 63                                | 403.23             |

Table 9. Switching Frequency Settings from 30 kHz to 400 kHz (Register 0xFE1B, Bits[5:0])

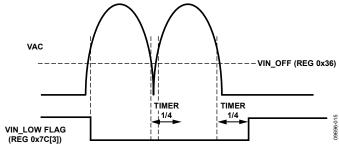

### LINE FAULT PROTECTIONS AND SOFT START SEQUENCING PSON OPERATION AC Line Period

To comply with PMBus standards, the PFC circuit controlled by the ADP1047/ADP1048 can be turned on and off by the hardware PSON pin and/or the software PSON command. The setting of Bit 2 in Register 0x02 determines whether the PSON pin and/or the PSON command is used. If the PSON pin is used, the pin can be configured to be either active high or active low (see Table 18).

#### AC LINE DETECTION

The ADP1047/ADP1048 are capable of detecting several parameters of the ac line input voltage and taking the appropriate programmed actions when necessary. The detection is a combination of time and voltage measurements and is implemented via the VAC pin, which detects the rectified ac input voltage. This allows early detection of ac line faults and early warning for the host system, thereby increasing reliability.

Five main parameters are related to ac line detection.

- VAC\_LINE\_PERIOD (Register 0xFE85)

- VAC\_THRESHOLD\_SET (Register 0xFE25)

- VAC\_THRESHOLD\_READ (Register 0xFE26)

- MIN\_AC\_PERIOD\_SET (Register 0xFE27)

- MAX\_AC\_PERIOD\_SET (Register 0xFE28)

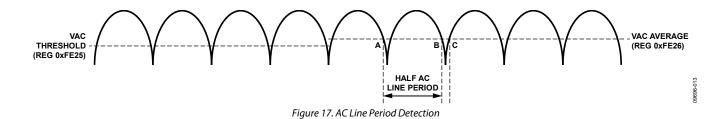

#### AC Line Period and Zero Crossing

The input ac line period is measured every half period of the ac line cycle and is reported in the VAC\_LINE\_PERIOD register (Register 0xFE85).

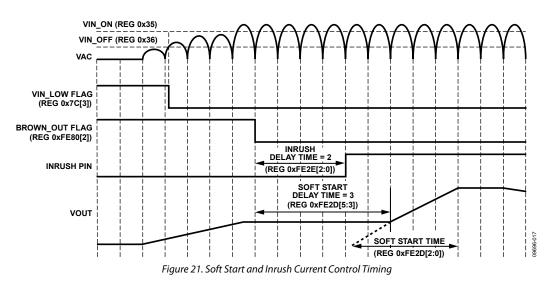

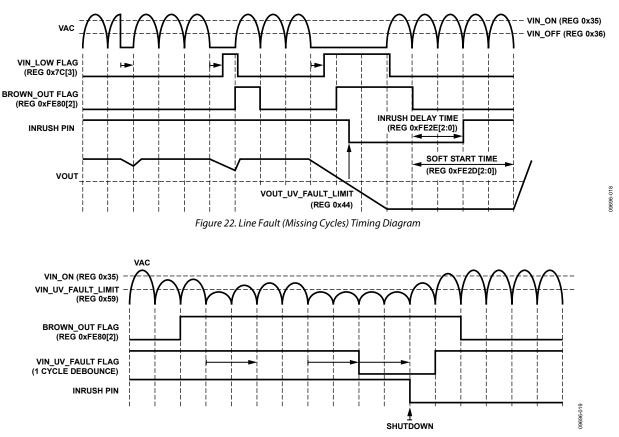

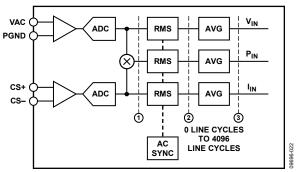

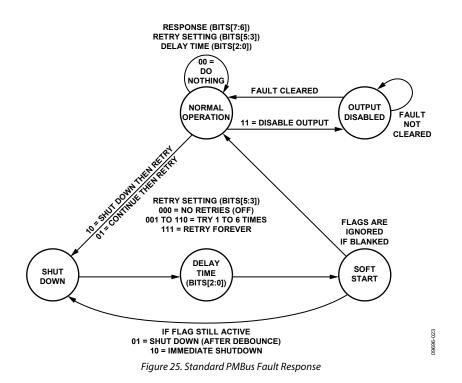

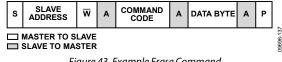

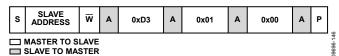

During the first 40 ms, the ac line period is measured between two consecutive falling crossings of the threshold value, which is set in the VAC\_THRESHOLD\_SET register (Register 0xFE25, Bits[6:0]). The ac line period is then measured between two consecutive falling crossings and compared to the average value of the input line voltage, which is calculated during each half line period. The VAC average reading can be found in the VAC\_ THRESHOLD\_READ register (Register 0xFE26, Bits[6:0]).