# Microprocessor Supervisory Circuits

## ADM8696/ADM8697

#### **FEATURES**

Upgrade for ADM696/ADM697, MAX696/MAX697 Specified Over Temperature Adjustable Low Line Voltage Monitor Power OK/Reset Time Delay Reset Assertion Down to 1 V  $V_{CC}$  Watchdog Timer—100 ms, 1.6 s, or Adjustable Low Switch On Resistance 0.7  $\Omega$  Normal, 7  $\Omega$  in Backup 400 nA Standby Current Automatic Battery Backup Switching (ADM8696) Fast On-Board Gating of Chip Enable Signals (ADM8697) Voltage Monitor for Power Fail or Low Battery Warning Also Available in TSSOP Package

### GENERAL DESCRIPTION

The ADM8696/ADM8697 supervisory circuits offer complete single chip solutions for power supply monitoring and battery control functions in microprocessor systems. These functions include  $\mu P$  reset, backup battery switchover, watchdog timer, CMOS RAM write protection and power failure warning.

The ADM8696/ADM8697 are available in 16-pin DIP and small outline packages (including TSSOP) and provide the following functions:

- 1. Power-On Reset output during power-up, power-down and brownout conditions. The RESET voltage threshold is adjustable using an external voltage divider. The  $\overline{RESET}$  output remains operational with  $V_{\rm CC}$  as low as 1 V.

- A Reset pulse if the optional watchdog timer has not been toggled within specified time.

- 3. Separate watchdog timeout and low line status outputs.

- 4. Adjustable reset and watchdog timeout periods.

- 5. A 1.3 V threshold detector for power fail warning, low battery detection or to monitor a power supply other than  $V_{\rm CC}$ .

- 6. Battery backup switching for CMOS RAM, CMOS microprocessor or other low power logic (ADM8696).

- 7. Write protection of CMOS RAM or EEPROM (ADM8697).

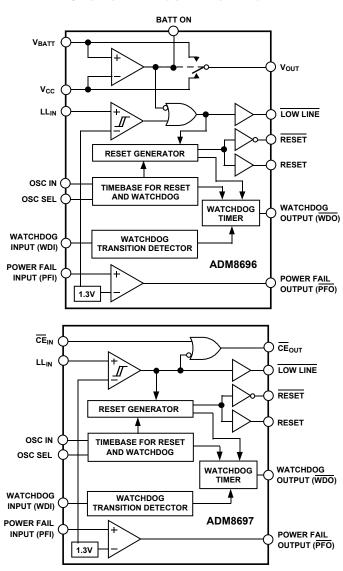

#### FUNCTIONAL BLOCK DIAGRAMS

The ADM8696/ADM8697 is fabricated using an advanced epitaxial CMOS process combining low power consumption (0.7 mW), extremely fast Chip Enable gating (2 ns) and high reliability.  $\overline{RESET}$  assertion is guaranteed with  $V_{CC}$  as low as 1 V. In addition, the power switching circuitry is designed for minimal voltage drop thereby permitting increased output current drive of up to 100 mA without the need for an external pass transistor.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703

# $\label{eq:ADM8696ADM8697-SPECIFICATIONS} \text{($V_{CC}$ = Full Operating Range, $V_{BATT}$ = +2.8 V, $T_A$ = $T_{MIN}$ to $T_{MAX}$ unless otherwise noted.)}$

| Parameter                                                                            | Min                  | Тур                     | Max                          | Units     | <b>Test Conditions/Comments</b>                                                                           |

|--------------------------------------------------------------------------------------|----------------------|-------------------------|------------------------------|-----------|-----------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> Operating Voltage Range<br>V <sub>BATT</sub> Operating Voltage Range | 3.0<br>2.0           |                         | 5.5<br>V <sub>CC</sub> - 0 3 | V<br>V    |                                                                                                           |

| BATTERY BACKUP SWITCHING (ADM8696)                                                   |                      |                         |                              |           |                                                                                                           |

| V <sub>OUT</sub> Output Voltage                                                      | $V_{CC} - 0.005$     | $V_{\rm CC}$ – $0.0025$ |                              | V         | $I_{OUT} = 1 \text{ mA}$                                                                                  |

|                                                                                      | $V_{CC} - 0.2$       | $V_{\rm CC} - 0.125$    |                              | V         | $I_{OUT} \le 100 \text{ mA}$                                                                              |

| V <sub>OUT</sub> in Battery Backup Mode                                              | $V_{BATT} - 0.005$   | $V_{BATT} - 0.002$      |                              | V         | $I_{OUT} = 250 \mu\text{A},  V_{CC} < V_{BATT} - 0.2  \text{V}$                                           |

| Supply Current (Excludes I <sub>OUT</sub> )                                          | DATI                 | 115                     | 200                          | μA        | $I_{OUT} = 100 \text{ mA}$                                                                                |

| Supply Current in Battery Backup Mode                                                |                      | 0.4                     | 1                            | μA        | $V_{CC} = 0 \text{ V}, V_{BATT} = 2.8 \text{ V}$                                                          |

| Battery Standby Current                                                              |                      | 0.1                     | 1                            | μι        | $5.5 \text{ V} > \text{V}_{\text{CC}} > \text{V}_{\text{BATT}} + 0.2 \text{ V}$                           |

|                                                                                      | -0.1                 |                         | +0.02                        |           | 3.3 V > V CC > V BATT + 0.2 V                                                                             |

| (+ = Discharge, - = Charge)                                                          | -0.1                 | 70                      | +0.02                        | μΑ        | D II                                                                                                      |

| Battery Switchover Threshold                                                         |                      | 70                      |                              | mV        | Power-Up                                                                                                  |

| $V_{CC} - V_{BATT}$                                                                  |                      | 50                      |                              | mV        | Power-Down                                                                                                |

| Battery Switchover Hysteresis                                                        |                      | 20                      |                              | mV        |                                                                                                           |

| BATT ON Output Voltage                                                               |                      |                         | 0.3                          | V         | $I_{SINK} = 3.2 \text{ mA}$                                                                               |

| BATT ON Output Short Circuit Current                                                 |                      | 30                      |                              | mA        | BATT ON = V <sub>OUT</sub> = 2.4 V Sink Current                                                           |

| -                                                                                    | 0.5                  | 2.5                     | 25                           | μA        | BATT ON = $V_{OUT}$ , $V_{CC} = 0$ V, Source Curren                                                       |

| RESET AND WATCHDOG TIMER                                                             |                      |                         |                              |           |                                                                                                           |

| Low Line Threshold (LL <sub>IN</sub> )                                               | 1.25                 | 1.3                     | 1.35                         | V         |                                                                                                           |

| Reset Timeout Delay                                                                  | 35                   | 50                      | 70                           | ms        | OSC SEL = HIGH                                                                                            |

|                                                                                      |                      |                         |                              |           |                                                                                                           |

| Watchdog Timeout Period, Internal Oscillator                                         | 1.0                  | 1.6                     | 2.25                         | S         | Long Period                                                                                               |

|                                                                                      | 70                   | 100                     | 140                          | ms        | Short Period                                                                                              |

| Watchdog Timeout Period, External Clock                                              | 4032                 | 4063                    | 4097                         | Cycles    | Long Period                                                                                               |

|                                                                                      | 960                  | 1011                    | 1025                         | Cycles    | Short Period                                                                                              |

| Minimum WDI Input Pulse Width                                                        | 50                   |                         |                              | ns        | $V_{IL} = 0.8, V_{IH} = 3.75 \text{ V}, V_{CC} = 5 \text{ V}$                                             |

| -                                                                                    | 100                  |                         |                              | ns        | $V_{IL} = 0.8, V_{IH} = 3.5 \text{ V}, V_{CC} = 5 \text{ V}$                                              |

|                                                                                      |                      | 100                     |                              | ns        | $V_{IL} = 0.8$ , $V_{IH} = 2.6$ V, $V_{CC} = 3$ V                                                         |

| RESET Output Voltage @ V <sub>CC</sub> = +1 V                                        |                      | 4                       | 20                           | mV        | $I_{SINK} = 10 \mu A, V_{CC} = 1 V$                                                                       |

| RESET, RESET Output Voltage                                                          |                      | 0.1                     | 0.4                          | V         | $I_{SINK} = 400 \mu A$ , $V_{CC} = 2 V$ , $V_{BATT} = 0 V$                                                |

| RESET, RESET Output voltage                                                          |                      | 0.1                     |                              | V         |                                                                                                           |

|                                                                                      | 0.5                  | 0.1                     | 0.4                          |           | $I_{SINK} = 3.2 \text{ mA}, 3 \text{ V} < V_{CC} < 5.5 \text{ V}$                                         |

|                                                                                      | 3.5                  |                         |                              | V         | $I_{SOURCE} = 1 \mu A, V_{CC} = 5 V$                                                                      |

|                                                                                      |                      | 2.7                     |                              | V         | $I_{SOURCE} = 1 \mu A, V_{CC} = 3 V$                                                                      |

| LOW LINE, WDO Output Voltage                                                         |                      |                         | 0.4                          | V         | $I_{SINK} = 3.2 \text{ mA},$                                                                              |

|                                                                                      | 3.5                  |                         |                              | V         | $I_{SOURCE} = 1 \mu A, V_{CC} = 5 V$                                                                      |

|                                                                                      |                      | 2.7                     |                              | V         | $I_{SOURCE} = 1 \mu A, V_{CC} = 3 V$                                                                      |

| Output Short Circuit Source Current                                                  | 1                    | 10                      | 25                           | μA        | $V_{CC} = 5 \text{ V}$                                                                                    |

| WDI Input Threshold <sup>1</sup>                                                     |                      |                         |                              | '         |                                                                                                           |

| Logic Low                                                                            |                      |                         | 0.8                          | V         |                                                                                                           |

| Logic High                                                                           | 3.5                  |                         | 0.0                          | v         | $V_{CC} = 5 \text{ V}$                                                                                    |

| Logic Trigit                                                                         | 5.5                  | 1.2                     |                              | V         | $V_{CC} = 3 V$                                                                                            |

| WDI Input Cumont                                                                     |                      | 1.2                     | 10                           |           |                                                                                                           |

| WDI Input Current                                                                    | -10                  | -1                      | 10                           | μΑ<br>μΑ  | $WD1 = V_{OUT}, (V_{CC})$ $WD1 = 0 V$                                                                     |

|                                                                                      | -10                  | -1                      |                              | μΑ        | VVD1 = 0 V                                                                                                |

| POWER FAIL DETECTOR                                                                  |                      |                         |                              |           |                                                                                                           |

| PFI Input Threshold                                                                  | 1.2                  | 1.3                     | 1.4                          | V         |                                                                                                           |

| PFI-LL <sub>IN</sub> Threshold Difference                                            | -50                  | $\pm 15$                | +50                          | mV        |                                                                                                           |

| PFI Input Current                                                                    | -25                  | $\pm 0.01$              | +25                          | nA        |                                                                                                           |

| LL <sub>IN</sub> Input Current                                                       | -50                  | ±0.01                   | +50                          | nA        |                                                                                                           |

| PFO Output Voltage                                                                   |                      |                         | 0.4                          | V         | $I_{SINK} = 3.2 \text{ mA}$                                                                               |

| output tomage                                                                        | 3.5                  |                         | J                            | V         | $I_{\text{SOURCE}} = 1 \mu\text{A}$                                                                       |

|                                                                                      | 5.5                  | 2.7                     |                              | V         | $I_{\text{SOURCE}} = 1 \mu\text{A}$<br>$I_{\text{SOURCE}} = 1 \mu\text{A}$ , $V_{\text{CC}} = 3 \text{V}$ |

| PFO Short Circuit Source Current                                                     | 1                    | 10                      | 25                           | μA        | PFI = Low, PFO = 0 V                                                                                      |

|                                                                                      | -                    |                         | ~~                           | hr. 2     |                                                                                                           |

| CHIP ENABLE GATING (ADM8697)                                                         |                      |                         | 0.0                          | 3.7       | 37                                                                                                        |

| CE <sub>IN</sub> Threshold                                                           |                      |                         | 0.8                          | V         | $V_{IL}$                                                                                                  |

|                                                                                      | 3.0                  |                         |                              | V         | $V_{IH}$                                                                                                  |

|                                                                                      |                      | 1.2                     |                              | V         | $V_{CC} = 3 V$                                                                                            |

| CE <sub>IN</sub> Pull-Up Current                                                     |                      | 3                       |                              | μA        |                                                                                                           |

| CE <sub>OUT</sub> Output Voltage                                                     |                      |                         | 0.4                          | V         | $I_{SINK} = 3.2 \text{ mA}$                                                                               |

| 1 0                                                                                  | $V_{\rm CC}$ – $0.5$ |                         |                              | V         | $I_{\text{SOURCE}} = 800 \mu\text{A}$                                                                     |

| CE Propagation Delay                                                                 |                      | 2                       | 7                            | ns        | $V_{CC} = 5.0 \text{ V}$                                                                                  |

| OD I Topugution Delay                                                                |                      | 4                       | •                            | ns        | $V_{CC} = 3.0 \text{ V}$ $V_{CC} = 3.0 \text{ V}$                                                         |

| OSCILLATOR                                                                           |                      |                         |                              | -         |                                                                                                           |

| OSCILLATOR                                                                           |                      | . 0                     |                              |           |                                                                                                           |

| OCCUPIT LC                                                                           |                      | $\pm 2$                 |                              | μΑ        |                                                                                                           |

| OSC IN Input Current                                                                 |                      |                         |                              |           |                                                                                                           |

| OSC SEL Input Pull-Up Current                                                        |                      | 5                       |                              | μA        |                                                                                                           |

|                                                                                      | 0                    |                         | 500                          | μA<br>kHz | OSC SEL = 0 V<br>OSC SEL = 0 V, C <sub>OSC</sub> = 47 pF                                                  |

#### NOTE

$<sup>^1</sup>WDI$  is a three-level input internally biased to 38% of  $V_{CC}$  and has an input impedance of approximately 5  $M\Omega.$  Specifications subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = +25^{\circ}C \text{ unless otherwise noted})$ |

|-------------------------------------------------------|

| $V_{CC}$                                              |

| $V_{BATT}$ 0.3 V to +6 V                              |

| All Other Inputs0.3 V to $V_{OUT}$ + 0.5 V            |

| Input Current                                         |

| $V_{CC}$                                              |

| $V_{BATT}$ 50 mA                                      |

| GND 20 mA                                             |

| Digital Output Current                                |

| Power Dissipation, N-16 DIP 600 mW                    |

| $\theta_{JA}$ Thermal Impedance                       |

| Power Dissipation, RU-16 TSSOP500 mW                  |

| $\theta_{IA}$ Thermal Impedance                       |

| Power Dissipation, R-16 SOIC                                        |

|---------------------------------------------------------------------|

| Operating Temperature Range                                         |

| Industrial (A Version)40°C to +85°C                                 |

| Lead Temperature (Soldering, 10 sec) +300°C                         |

| Vapor Phase (60 sec) +215°C                                         |

| Infrared (15 sec) +220°C                                            |

| Storage Temperature Range $\dots -65^{\circ}$ C to $+150^{\circ}$ C |

|                                                                     |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods of time may affect device reliability.

### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADM8696/ADM8697 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

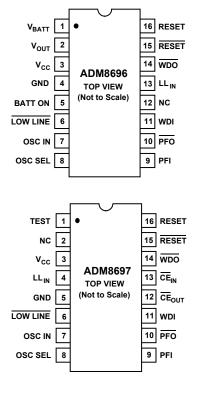

### **PIN CONFIGURATIONS**

REV. A -3-

### PIN FUNCTION DESCRIPTION

| Mnemonic                            | Pin<br>ADM8696 |    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------|----------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{V_{CC}}$                 | 3              | 3  | Power Supply Input +3 V to +5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{BATT}$                          | 1              | _  | Backup Battery Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $V_{OUT}$                           | 2              | _  | Output Voltage, $V_{CC}$ or $V_{BATT}$ is internally switched to $V_{OUT}$ depending on which is at the highest potential. When $V_{CC}$ is higher than $V_{BATT}$ and $LL_{IN}$ is higher than the reset threshold, $V_{CC}$ is switched to $V_{OUT}$ . When $V_{CC}$ is lower than $V_{BATT}$ and $LL_{IN}$ is below the reset threshold, $V_{BATT}$ is switched to $V_{OUT}$ . $V_{OUT}$ can supply up to 100 mA to power CMOS RAM. Connect $V_{OUT}$ to $V_{CC}$ if $V_{OUT}$ and $V_{BATT}$ are not used. |

| GND                                 | 4              | 5  | 0 V. Ground reference for all signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET                               | 15             | 15 | Logic Output. $\overline{RESET}$ goes low whenever $LL_{IN}$ falls below 1.3 V and remains low for 50 ms after $LL_{IN}$ goes above 1.3 V. $\overline{RESET}$ also goes low for 50 ms if the watchdog timer is enabled but not serviced within its timeout period. The $\overline{RESET}$ pulse width can be adjusted as shown in Table I.                                                                                                                                                                     |

| WDI                                 | 11             | 11 | Watchdog Input, WDI is a three level input. If WDI remains either high or low for longer than the watchdog timeout period, $\overline{RESET}$ pulses low and $\overline{WDO}$ goes low. The timer resets with each transition at the WDI input. The watchdog timer is disabled when WDI is left floating or is driven to midsupply.                                                                                                                                                                            |

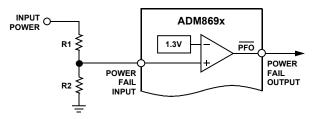

| PFI                                 | 9              | 9  | Power Fail Input. PFI is the noninverting input to the Power Fail Comparator when PFI is less than 1.3 V, PFO goes low. Connect PFI to GND or V <sub>OUT</sub> when not used. See Figure 1.                                                                                                                                                                                                                                                                                                                    |

| PFO                                 | 10             | 10 | Power Fail Output. $\overline{PFO}$ is the output of the Power Fail Comparator. It goes low when PFI is less than 1.3 V. The comparator is turned off and $\overline{PFO}$ goes low when $V_{CC}$ is below $V_{BATT}$ .                                                                                                                                                                                                                                                                                        |

| $\overline{\text{CE}}_{\text{IN}}$  | _              | 13 | Logic Input. The input to the CE gating circuit. Connect to GND or V <sub>OUT</sub> if not used.                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\overline{\text{CE}}_{\text{OUT}}$ | _              | 12 | Logic Output. $\overline{CE}_{OUT}$ is a gated version of the $\overline{CE}_{IN}$ signal. $\overline{CE}_{OUT}$ tracks $\overline{CE}_{IN}$ when $LL_{IN}$ is above 1.3 V. If $LL_{IN}$ is below 1.3 V, $\overline{CE}_{OUT}$ is forced high.                                                                                                                                                                                                                                                                 |

| BATT ON                             | 5              | _  | Logic Output. BATT ON goes high when $V_{OUT}$ is internally switched to the $V_{BATT}$ input. It goes low when $V_{OUT}$ is internally switched to $V_{CC}$ . The output typically sinks 7 mA and can directly drive the base of an external PNP transistor to increase the output current above the 100 mA rating of $V_{OUT}$ .                                                                                                                                                                             |

| LOW LINE                            | 6              | 6  | Logic Output. $\overline{LOW\ LINE}$ goes low when $LL_{IN}$ falls below 1.3 V. It returns high as soon as $LL_{IN}$ rises above 1.3 V.                                                                                                                                                                                                                                                                                                                                                                        |

| RESET                               | 16             | 16 | Logic Output. RESET is an active high output. It is the inverse of RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

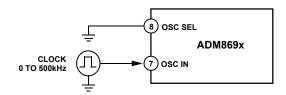

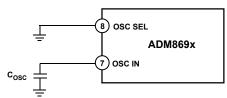

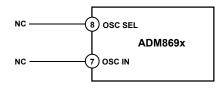

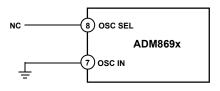

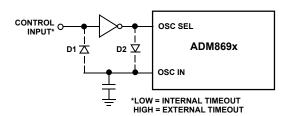

| OSC SEL                             | 8              | 8  | Logic Oscillator Select Input. When OSC SEL is unconnected or driven high, the internal oscillator sets the reset time delay and watchdog timeout period. When OSC SEL is low, the external oscillator input, OSC IN, is enabled. OSC SEL has a 3 $\mu$ A internal pull-up. See Table I and Figure 4.                                                                                                                                                                                                          |

| OSC IN                              | 7              | 7  | Logic Oscillator Input. When OSC SEL is low, OSC IN can be driven by an external clock to adjust both the reset delay and the watchdog timeout period. The timing can also be adjusted by connecting an external capacitor to this pin. See Table I and Figure 4. When OSC SEL is high or floating, OSC IN selects between fast and slow watchdog timeout periods.                                                                                                                                             |

| WDO                                 | 14             | 14 | Logic Output. The Watchdog Output, $\overline{WDO}$ , goes low if WDI remains either high or low for longer than the watchdog timeout period. $\overline{WDO}$ is set high by the next transition at WDI. If WDI is unconnected or at midsupply, $\overline{WDO}$ remains high. $\overline{WDO}$ also goes high when $\overline{LOW\ LINE}$ goes low.                                                                                                                                                          |

| NC                                  | 12             | 2  | No Connect. It should be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $LL_{IN}$                           | 13             | 4  | Voltage Sensing Input. The voltage on the low line input, $LL_{IN}$ , is compared with a 1.3 V reference voltage. This input is normally used to monitor the power supply voltage. The output of the comparator generates a $\overline{LOW\ LINE}$ output signal. It also generates a RESET/ $\overline{RESET}$ output. The comparator output also controls the battery switchover circuitry.                                                                                                                  |

| TEST                                | _              | 1  | This is a special test pin using during device manufacture. It should be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                     |

-4- REV. A

### **CIRCUIT INFORMATION**

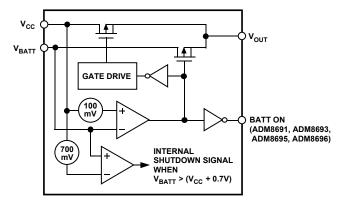

### **Battery Switchover Section (ADM8696)**

The battery switchover circuit is designed to switch over to battery backup in the event of a power failure. When  $LL_{\rm IN}$  is below the reset threshold and  $V_{\rm CC}$  is below  $V_{\rm BATT}$ , then  $V_{\rm BATT}$  is switched to  $V_{\rm OUT}.$

During normal operation, with  $V_{CC}$  higher than  $V_{BATT},\,V_{CC}$  is internally switched to  $V_{OUT}$  via an internal PMOS transistor switch. This switch has a typical on resistance of 0.7  $\Omega$  and can supply up to 100 mA at the  $V_{OUT}$  terminal.  $V_{OUT}$  is normally used to drive a RAM memory bank which may require instantaneous currents of greater than 100 mA. If this is the case, then a bypass capacitor should be connected to  $V_{OUT}.$  The capacitor will provide the peak current transients to the RAM. A capacitance value of 0.1  $\mu F$  or greater may be used.

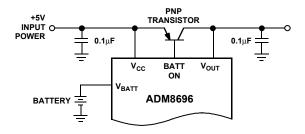

If the continuous output current requirement at  $V_{\rm OUT}$  exceeds 100 mA or if a lower  $V_{\rm CC}$ – $V_{\rm OUT}$  voltage differential is desired, an external PNP pass transistor may be connected in parallel with the internal transistor. The BATT ON output can directly drive the base of the external transistor.

A 7  $\Omega$  MOSFET switch connects the  $V_{BATT}$  input to  $V_{OUT}$  during battery backup. This MOSFET has very low input-to-out-put differential (dropout voltage) at the low current levels required for battery backup of CMOS RAM or other low power CMOS circuitry. The supply current in battery backup is typically  $0.4~\mu A.$

The ADM8696 operates with battery voltages from 2.0 V to  $V_{\rm CC}{\rm -}0.3$  V). High value capacitors, either standard electrolytic or the farad-size double layer capacitors, can also be used for short-term memory backup. A small charging current of typically 10 nA (0.1  $\mu A$  max) flows out of the  $V_{\rm BATT}$  terminal. This current is useful for maintaining rechargeable batteries in a fully charged condition. This extends the life of the backup battery by compensating for its self-discharge current. Also note that this current poses no problem when lithium batteries are used for backup since the maximum charging current (0.1  $\mu A$ ) is safe for even the smallest lithium cells.

If the battery switchover section is not used,  $V_{BATT}$  should be connected to GND and  $V_{OUT}$  should be connected to  $V_{CC}$ .

Figure 1. Battery Switchover Schematic

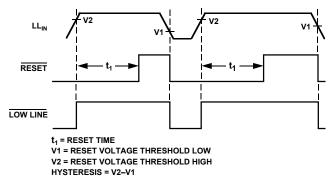

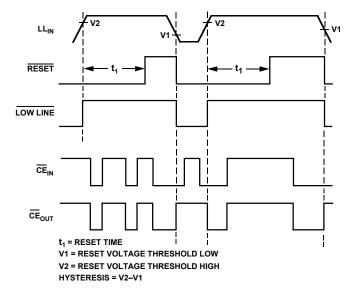

### **Low Line RESET OUTPUT**

$\overline{RESET}$  is an active low output that provides a  $\overline{RESET}$  signal to the microprocessor whenever the Low Line Input (LL\_{IN}) is below 1.3 V. The LL\_{IN} input is normally used to monitor the power supply voltage. An internal timer holds  $\overline{RESET}$  low for 50 ms after the voltage on LL\_{IN} rises above 1.3 V. This is intended as a power-on  $\overline{RESET}$  signal for the processor. It allows time for the power supply and microprocessor to stabilize. On power-down, the  $\overline{RESET}$  output remains low, with  $V_{CC}$  as low as 1 V. This ensures that the microprocessor is held in a stable shutdown condition.

The  $LL_{\rm IN}$  comparator has approximately 12 mV of hysteresis for enhanced noise immunity.

In addition to RESET, an active high RESET output is also available. This is the complement of RESET and is useful for processors requiring an active high RESET.

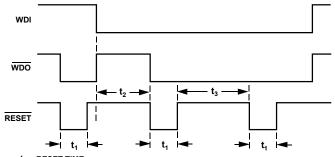

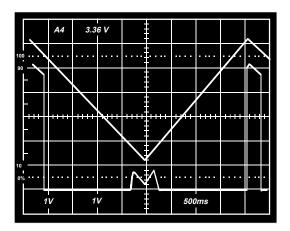

Figure 2. Power-Fail Reset Timing

### Watchdog Timer RESET

The watchdog timer circuit monitors the activity of the microprocessor in order to check that it is not stalled in an indefinite loop. An output line on the processor is used to toggle the Watchdog Input (WDI) line. If this line is not toggled within the selected timeout period, a  $\overline{RESET}$  pulse is generated. The ADM8696/ADM8697 may be configured for either a fixed "short" 100 ms or a "long" 1.6 second timeout period or for an adjustable timeout period. If the "short" period is selected, some systems may be unable to service the watchdog timer immediately after a reset, so a "long" timeout is automatically initiated directly after a reset is issued. The watchdog timer is restarted at the end of Reset, whether the Reset was caused by lack of activity on WDI or by  $LL_{IN}$  falling below the reset threshold.

The normal (short) timeout period becomes effective following the first transition of WDI after RESET has gone inactive. The watchdog timeout period restarts with each transition on the WDI pin. To ensure that the watchdog timer does not time out, either a high-to-low or low-to-high transition on the WDI pin must occur at or less than the minimum timeout period. If WDI remains permanently either high or low, reset pulses will be issued after each timeout period (1.6 s). The watchdog monitor can be deactivated by floating the Watchdog Input (WDI) or by connecting it to midsupply.

| Table I. ADM8696, ADM8697 Reset Pulse Width and Watchdog Timeout Selection | Table I. | ADM8696. | ADM8697 | Reset Puls | e Width and | l Watchdog | Timeout Selection |

|----------------------------------------------------------------------------|----------|----------|---------|------------|-------------|------------|-------------------|

|----------------------------------------------------------------------------|----------|----------|---------|------------|-------------|------------|-------------------|

|                  |                      | Watchdog                                       | Reset Active Period                           |                         |

|------------------|----------------------|------------------------------------------------|-----------------------------------------------|-------------------------|

| OSC SEL          | OSC IN               | Normal                                         | Immediately After Reset                       |                         |

| Low              | External Clock Input | 1024 CLKS                                      | 4096 CLKS                                     | 512 CLKS                |

| Low              | External Capacitor   | $400 \text{ ms} \times \text{C}/47 \text{ pF}$ | $1.6 \text{ s} \times \text{C}/47 \text{ pF}$ | 200 ms $\times$ C/47 pF |

| Floating or High | Low                  | 100 ms                                         | 1.6 s                                         | 50 ms                   |

| Floating or High | Floating or High     | 1.6 s                                          | 1.6 s                                         | 50 ms                   |

### NOTE

With the OSC SEL pin low, OSC IN can be driven by an external clock signal, or an external capacitor can be connected between OSC IN and GND. The nominal internal oscillator frequency is 10.24 kHz. The nominal oscillator frequency with external capacitor is:  $F_{OSC}$  (Hz) = 184,000/C (pF).

- t<sub>1</sub> = RESET TIME

- $\dot{t}_2$  = NORMAL (SHORT) WATCHDOG TIMEOUT PERIOD

- t<sub>3</sub> = WATCHDOG TIMEOUT PERIOD IMMEDIATELY FOLLOWING A RESET

Figure 3. Watchdog Timeout Period and Reset Active Time

The watchdog timeout period defaults to 1.6 s and the reset pulse width defaults to 50 ms, but these times to be adjusted as shown in Table I. Figure 4 shows the various oscillator configurations that can be used to adjust the reset pulse width and watchdog timeout period.

The internal oscillator is enabled when OSC SEL is high or floating. In this mode, OSC IN selects between the 1.6 second and 100 ms watchdog timeout periods. In either case, immediately after a reset the timeout period is 1.6 s. This gives the microprocessor time to reinitialize the system. If OSC IN is low, the 100 ms watchdog period becomes effective after the first transition of WDI. The software should be written such that the I/O port driving WDI is left in its power-up reset state until the initialization routines are completed and the microprocessor is able to toggle WDI at the minimum watchdog timeout period of 70 ms.

Figure 4a. External Clock Source

Figure 4b. External Capacitor

Figure 4c. Internal Oscillator (1.6 s Watchdog)

Figure 4d. Internal Oscillator (100 ms Watchdog)

### Watchdog Output (WDO)

The Watchdog Output  $\overline{WDO}$  provides a status output that goes low if the watchdog timer "times out" and remains low until set high by the next transition on the watchdog input.  $\overline{WDO}$  is also set high when  $LL_{IN}$  goes below the reset threshold.

-6- REV. A

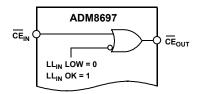

### CE Gating and RAM Write Protection (ADM8697)

The ADM8697 contains memory protection circuitry that ensures the integrity of data in memory by preventing write operations when  $LL_{IN}$  is below the threshold voltage. When  $LL_{IN}$  is greater than 1.3 V,  $\overline{CE}_{OUT}$  is a buffered replica of  $\overline{CE}_{IN}$ , with a 2 ns propagation delay. When  $LL_{IN}$  falls below the 1.3 V threshold, an internal gate forces  $\overline{CE}_{OUT}$  high, independent of  $\overline{CE}_{IN}$ .

$\overline{\text{CE}}_{\text{OUT}}$  typically drives the CE, CS or Write input of battery backed up CMOS RAM. This ensures the integrity of the data in memory by preventing write operations when  $V_{\text{CC}}$  is at an invalid level.

Figure 5. Chip Enable Gating

Figure 6. Chip Enable Timing

### **Power Fail Warning Comparator**

An additional comparator is provided for early warning of failure in the microprocessor's power supply. The Power Fail Input (PFI) is compared to an internal +1.3 V reference. The Power

Fail Output  $(\overline{PFO})$  goes low when the voltage at PFI is less than 1.3 V. Typically PFI is driven by an external voltage divider which senses either the unregulated dc input to the system's 5 V regulator or the regulated 5 V output. The voltage divider ratio

can be chosen such that the voltage at PFI falls below 1.3 V several milliseconds before the +5 V power supply falls below the reset threshold.  $\overline{PFO}$  is normally used to interrupt the microprocessor so that data can be stored in RAM and the shutdown procedure executed before power is lost.

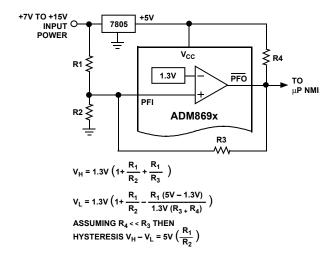

Figure 7. Power Fail Comparator

Table II. Input and Output Status In Battery Backup Mode

| Signal                              | Status                                                                                                                                                                                                                                                       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OUT</sub>                    | (ADM8696) $V_{\rm OUT}$ is connected to $V_{\rm BATT}$ via an internal PMOS switch.                                                                                                                                                                          |

| RESET                               | Logic low.                                                                                                                                                                                                                                                   |

| RESET                               | Logic high. The open circuit output voltage is equal to $\ensuremath{V_{\mathrm{OUT}}}.$                                                                                                                                                                     |

| <b>LOW LINE</b>                     | Logic low.                                                                                                                                                                                                                                                   |

| BATT ON                             | (ADM8696) Logic high. The open circuit voltage is equal to $V_{\rm OUT}. \label{eq:control}$                                                                                                                                                                 |

| WDI                                 | WDI is ignored. It is internally disconnected from the internal pull-up resistor and does not source or sink current as long as its input voltage is between GND and $V_{\rm OUT}$ . The input voltage does not affect supply current.                       |

| WDO                                 | Logic high. The open circuit voltage is equal to $V_{\mathrm{OUT}}$ .                                                                                                                                                                                        |

| PFI                                 | The Power Fail Comparator is turned off and has no effect on the Power Fail Output.                                                                                                                                                                          |

| PFO                                 | Logic low.                                                                                                                                                                                                                                                   |

| $\overline{\text{CE}}_{\text{IN}}$  | $\overline{CE}_{\mathrm{IN}}$ is ignored. It is internally disconnected from its internal pull-up and does not source or sink current as long as its input voltage is between GND and $V_{\mathrm{OUT}}$ . The input voltage does not affect supply current. |

| $\overline{\text{CE}}_{\text{OUT}}$ | Logic high. The open circuit voltage is equal to $V_{\mathrm{OUT}}$ .                                                                                                                                                                                        |

| OSC IN                              | OSC IN is ignored.                                                                                                                                                                                                                                           |

| OSC SEL                             | OSC SEL is ignored.                                                                                                                                                                                                                                          |

REV. A \_7\_

## ADM8696/ADM8697—Typical Performance Curves

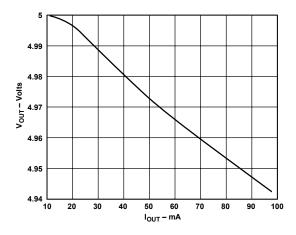

Figure 8. V<sub>OUT</sub> vs. I<sub>OUT</sub> Normal Operation

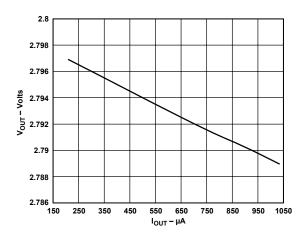

Figure 9.  $V_{OUT}$  vs.  $I_{OUT}$  Battery Backup

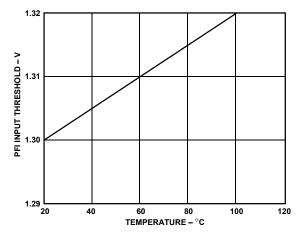

Figure 10. PFI Input Threshold vs. Temperature

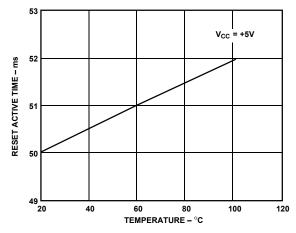

Figure 11. RESET Active Time vs. Temperature

Figure 12. RESET Output Voltage vs. Supply Voltage

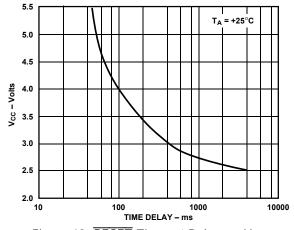

Figure 13.  $\overline{RESET}$  Timeout Delay vs.  $V_{CC}$

-8- REV. A

### APPLICATIONS INFORMATION

### **Increasing the Drive Current (ADM8696)**

If the continuous output current requirements at  $V_{OUT}$  exceeds 100 mA or if a lower  $V_{CC}$ – $V_{OUT}$  voltage differential is desired, an external PNP pass transistor may be connected in parallel with the internal transistor. The BATT ON output (ADM8696) can directly drive the base of the external transistor.

Figure 14. Increasing the Drive Current

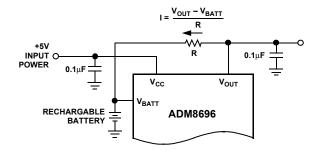

### Using a Rechargeable Battery for Backup (ADM8696)

If a capacitor or a rechargeable battery is used for backup, the charging resistor should be connected to  $V_{\rm OUT}$  since this eliminates the discharge path that would exist during power-down if the resistor is connected to  $V_{\rm CC}$ .

Figure 15. Rechargeable Battery

### **Adding Hysteresis to the Power Fail Comparator**

For increased noise immunity, hysteresis may be added to the power fail comparator. Since the comparator circuit is noninverting, hysteresis can be added by connecting a resistor between the PFO output and the PFI input as shown in Figure 16. When PFO is low, resistor R3 sinks current from the summing junction at the PFI pin. When PFO is high, the series combination of R3 and R4 source current into the PFI summing junction. This results in differing trip levels for the comparator.

### **Alternate Watchdog Input Drive Circuits**

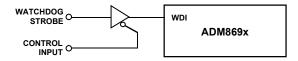

The watchdog feature can be enabled and disabled under program control by driving WDI with a three-state buffer (Figure 17a). When three-stated, the WDI input will float, thereby disabling the watchdog timer.

This circuit is not entirely foolproof and it is possible a software fault could erroneously three-state the buffer. This would prevent the ADM869x from detecting that the microprocessor is no longer operating correctly. In most cases, a better method is to

Figure 16. Adding Hysteresis to the Power Fail Comparator extend the watchdog period rather than disabling the watchdog. This may be done under program control using the circuit shown in Figure 17b. When the control input is high, the OSC SEL pin is low and the watchdog timeout is set by the external capacitor. A 0.01  $\mu$ F capacitor sets a watchdog timeout delay of 100 s. When the control input is low, the OSC SEL pin is driven high, selecting the internal oscillator. The 100 ms or the 1.6 s period is chosen, depending on which diode in Figure 17b is used. With D1 inserted, the internal timeout is set at

100 ms while with D2 inserted the timeout is set at 1.6 s.

Figure 17a. Programming the Watchdog Input

Figure 17b. Programming the Watchdog Input

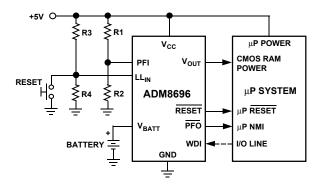

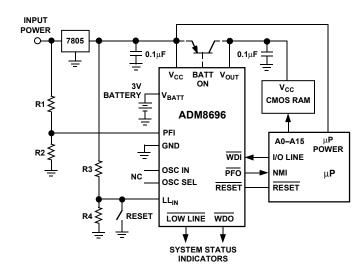

## TYPICAL APPLICATIONS ADM8696

Figure 18 shows the ADM8696 in a typical power monitoring, battery backup application.  $V_{OUT}$  powers the CMOS RAM. Under normal operating conditions with  $V_{\rm CC}$  present,  $V_{\rm OUT}$  is internally connected to  $V_{\rm CC}$ . If a power failure occurs,  $V_{\rm CC}$  will decay and  $V_{\rm OUT}$  will be switched to  $V_{\rm BATT}$ , thereby maintaining power for the CMOS RAM.

#### **Power Fail RESET**

The  $V_{\rm CC}$  power supply is also monitored by the Low Line Input,  $LL_{\rm IN}$ . A RESET pulse is generated when  $LL_{\rm IN}$  falls below 1.3 V. RESET will remain low for 50 ms after  $LL_{\rm IN}$  returns above 1.3 V. This allows for a power-on reset and prevents repeated toggling of RESET if the  $V_{\rm CC}$  power supply is unstable. Resistors R3 and R4 should be chosen to give the desired  $V_{\rm CC}$  reset threshold.

### **Watchdog Timer**

The Watchdog Timer Input (WDI) monitors an I/O line from the  $\mu P$  system. This line must be toggled once every 1.6 s to verify correct software execution. Failure to toggle the line indicates that the  $\mu P$  system is not correctly executing its program and may be tied up in an endless loop. If this happens, a reset pulse is generated to initialize the processor.

If the watchdog timer is not needed the WDI input should be left floating.

#### **Power Fail Detector**

The Power Fail Input, PFI, monitors the input power supply via a resistive divider network R1 and R2. This input is intended as an early warning power fail input. The voltage on the PFI input is compared with a precision 1.3 V internal reference. If the input voltage drops below 1.3 V, a power fail output (PFO) signal is generated. This warns of an impending power failure and may be used to interrupt the processor so that the system may be shut down in an orderly fashion. The resistors in the sensing network are ratioed to give the desired power fail threshold voltage  $V_{\rm T}$ . The threshold should be set at a higher voltage than the RESET threshold so there is sufficient time available to complete the shutdown procedure before the processor is RESET and power is lost.

Figure 18a. ADM8696 Typical Application Circuit A

Figure 18b shows a similar application for the ADM8696 but in this case the PFI input monitors the unregulated input to the 7805 voltage regulator. This gives an earlier warning of an impending power failure. It is useful with processors operating at low speeds or where there are a significant number of house-keeping tasks to be completed before the power is lost.

Figure 18b. ADM8696 Typical Application Circuit B

This application also shows an optional external transistor that may be used to provide in excess of 100 mA current on  $V_{\rm OUT}.$  When  $V_{\rm CC}$  is higher than  $V_{\rm BATT},$  the BATT ON output goes low, providing 25 mA of base drive for the external PNP transistor. The maximum current available is dependent on the power rating of the external transistor.

### **RAM Write Protection**

The ADM8697  $\overline{CE}_{OUT}$  line drives the Chip Select inputs of the CMOS RAM.  $\overline{CE}_{OUT}$  follows  $\overline{CE}_{IN}$  as long as  $LL_{IN}$  is above the reset threshold. If  $LL_{IN}$  falls below the reset threshold,  $\overline{CE}_{OUT}$  goes high, independent of the logic level at  $\overline{CE}_{IN}$ . This prevents the microprocessor from writing erroneous data into RAM during power-up, power-down, brownouts and momentary power interruptions.

-10- REV. A

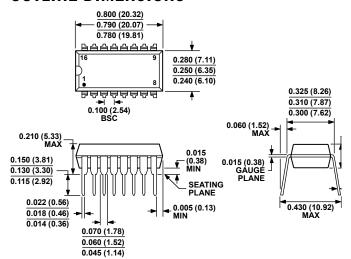

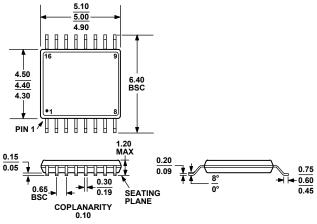

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-153-AB

#### COMPLIANT TO JEDEC STANDARDS MS-001-AB

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 19. 16-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-16) Dimensions shown in inches and (millimeters)

Figure 20. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

032707-B

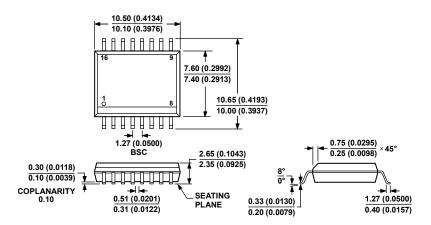

COMPLIANT TO JEDEC STANDARDS MS-013-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 21. 16-Lead Standard Small Outline Package [SOIC\_W] Wide Body (RW-16)

Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1,2</sup> | Notes | Temperature Range | Package Description                               | Package Option |

|----------------------|-------|-------------------|---------------------------------------------------|----------------|

| ADM8696AN            |       | −40°C to + 85°C   | 16-Lead Plastic Dual In-Line Package [PDIP]       | N-16           |

| ADM8696ANZ           |       | -40°C to + 85°C   | 16-Lead Plastic Dual In-Line Package [PDIP]       | N-16           |

| ADM8696ARW           |       | -40°C to + 85°C   | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8969ARW-REEL      |       | -40°C to +85°C    | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8696ARWZ          |       | −40°C to + 85°C   | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8696ARWZ-REEL     |       | -40°C to + 85°C   | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8696ARU           |       | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADM8696ARU-REEL      |       | −40°C to + 85°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADM8697AN            |       | -40°C to + 85°C   | 16-Lead Plastic Dual In-Line Package [PDIP]       | N-16           |

| ADM8697ANZ           |       | −40°C to + 85°C   | 16-Lead Plastic Dual In-Line Package [PDIP]       | N-16           |

| ADM8697ARW           |       | -40°C to + 85°C   | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8697ARW-REEL      |       | −40°C to +85°C    | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8697ARWZ          |       | −40°C to + 85°C   | 16-Lead Standard Small Outline Package [SOIC_W]   | RW-16          |

| ADM8697ARU           | 3     | −40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADM8697ARU-REEL      | 3     | −40°C to + 85°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

### **AUTOMOTIVE PRODUCTS**

The ADM8696/ADM8697 models are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

<sup>&</sup>lt;sup>2</sup> W = Qualified for Automotive Applications. <sup>3</sup> Contact sales for availability and quotation.

### **REVISION HISTORY**

6/10-Rev. 0 to Rev. A

Changes to Ordering Guide......12