# +5 Volt, Parallel Input Complete Dual 12-Bit DAC

## AD8582

### FEATURES

Complete Dual 12-Bit DAC No External Components Single +5 Volt Operation 1 mV/Bit with 4.095 V Full Scale True Voltage Output, ±5 mA Drive Very Low Power: 5 mW

### APPLICATIONS

Digitally Controlled Calibration Portable Equipment Servo Controls Process Control Equipment PC Peripherals

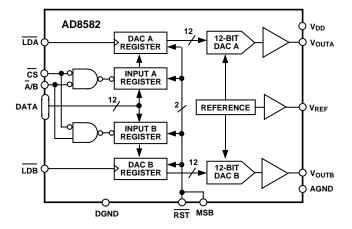

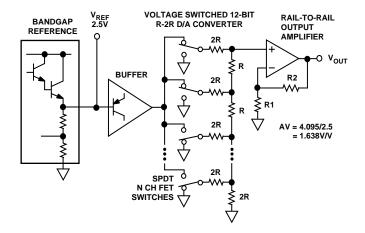

### FUNCTIONAL BLOCK DIAGRAM

### **GENERAL DESCRIPTION**

The AD8582 is a complete, parallel input, dual 12-bit, voltage output DAC designed to operate from a single +5 volt supply. Built using a CBCMOS process, this monolithic DAC offers the user low cost, and ease-of-use in +5 volt only systems.

Included on the chip, in addition to the DACs, are a rail-to-rail amplifier, latch and reference. The reference ( $V_{REF}$ ) is trimmed to 2.5 volts output, and the on-chip amplifier gains up the DAC output to 4.095 volts full scale. The user needs only supply a +5 volt supply.

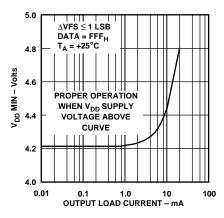

The AD8582 is coded natural binary. The op amp output swings from 0 volt to +4.095 volts for a one-millivolt-per-bit resolution, and is capable of driving  $\pm 5$  mA. Operation down to 4.3 V is possible with output load currents less than 1 mA.

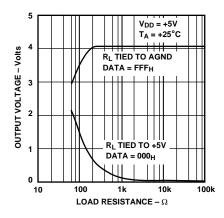

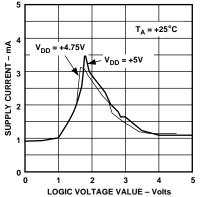

Figure 1. Minimum Supply Voltage vs. Load

### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. The high speed parallel data interface connects to the fastest processors without wait states. The double-buffered input structure allows the user to load the input registers one at a time, then a single load strobe tied to both LDA + LDB inputs will update both DAC outputs simultaneously. LDA and LDB can also be activated independently to immediately update their respective DAC registers. An address input decodes DAC A or DAC B when the chip select  $\overline{CS}$  input is strobed. An asynchronous reset input sets the output to zero scale. The MSB bit can be used to establish a preset to midscale when the reset input is strobed.

The AD8582 is available in the 24-pin plastic DIP and the surface mount SOIC-24. Each part is fully specified for operation over  $-40^{\circ}$ C to  $+85^{\circ}$ C, and the full  $+5 \text{ V} \pm 5\%$  power supply range.

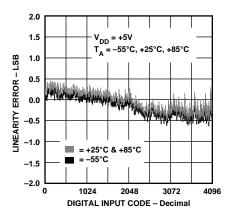

Figure 2. Linearity Error vs. Digital Code and Temperature

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

# AD8582-SPECIFICATIONS

| Parameter                                                                                                                                                                                              | Symbol                                                                                                                   | Condition                                                                                                            | Min                                               | Тур                                             | Max                        | Units                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------|----------------------------|----------------------------------------------------------|

| STATIC PERFORMANCE<br>Resolution<br>Relative Accuracy<br>Differential Nonlinearity<br>Zero-Scale Error<br>Full-Scale Voltage<br>Full-Scale Tempco                                                      | N<br>INL<br>DNL<br>V <sub>ZSE</sub><br>V <sub>FS</sub><br>TCV <sub>FS</sub>                                              | Note 1<br>Monotonic<br>Data = $000_{\rm H}$<br>Data = ${\rm FFF}_{\rm H}$ , <sup>2</sup><br>Notes 2 and 3            | 12<br>-2<br>-1<br>4.079                           | $\pm 3/4 \\ \pm 3/4 \\ +0.2 \\ 4.095 \\ \pm 16$ | +2<br>+1<br>+3<br>4.111    | Bits<br>LSB<br>LSB<br>mV<br>V<br>ppm/°C                  |

| MATCHING PERFORMANCE<br>Linearity Matching Error                                                                                                                                                       | $\Delta V_{FS}A/B$                                                                                                       |                                                                                                                      |                                                   | ±1                                              |                            | LSB                                                      |

| REFERENCE OUTPUT<br>Output Voltage<br>Output Source Current<br>Line Rejection<br>Load Regulation                                                                                                       | V <sub>REF</sub><br>I <sub>REF</sub><br>LN <sub>REJ</sub><br>LD <sub>REG</sub>                                           | Note 4<br>$I_{REF} = 0$ mA to 5 mA                                                                                   | 2.484                                             | 2.500                                           | 2.516<br>-5<br>0.08<br>0.1 | V<br>mA<br>%/V<br>%/mA                                   |

| ANALOG OUTPUT<br>Output Current<br>Load Regulation at Half Scale<br>Capacitive Load                                                                                                                    | $I_{OUT} \\ LD_{REG} \\ C_L$                                                                                             | Data = $800_{\rm H}$<br>$R_{\rm L} = 402 \ \Omega$ to $\infty$ , Data = $800_{\rm H}$<br>No Oscillation <sup>3</sup> |                                                   | 1<br>500                                        | $\frac{\pm 5}{3}$          | mA<br>LSB<br>pF                                          |

| DYNAMIC CHARACTERISTICS <sup>3</sup><br>Crosstalk<br>Voltage Output Settling Time <sup>5</sup><br>Digital Feedthrough                                                                                  | $egin{array}{c} C_{\mathrm{T}} \ t_{\mathrm{S}} \ F_{\mathrm{T}} \end{array}$                                            | To $\pm 1$ LSB of Final Value<br>Signal Measured at DAC Output, While<br>Changing Data (LDA = LDB = "1")             |                                                   | >64<br>16<br>35                                 |                            | dB<br>μs<br>nV s                                         |

| LOGIC INPUTS<br>Logic Input Low Voltage<br>Logic Input High Voltage<br>Input Leakage Current<br>Input Capacitance                                                                                      | $\begin{matrix} V_{\rm IL} \\ V_{\rm IH} \\ I_{\rm IL} \\ C_{\rm IL} \end{matrix}$                                       | Note 3                                                                                                               | 2.4                                               |                                                 | 0.8<br>10<br>10            | V<br>V<br>μA<br>pF                                       |

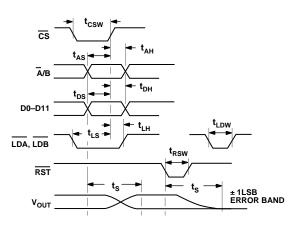

| TIMING SPECIFICATIONS <sup>3, 6</sup><br>Chip Select Pulse Width<br>DAC Select Setup<br>DAC Select Hold<br>Data Setup<br>Data Hold<br>Load Setup<br>Load Hold<br>Load Pulse Width<br>Reset Pulse Width | $\begin{array}{c} t_{CSW} \\ t_{AS} \\ t_{AH} \\ t_{DS} \\ t_{DH} \\ t_{LS} \\ t_{LH} \\ t_{LDW} \\ t_{RSW} \end{array}$ |                                                                                                                      | 30<br>30<br>0<br>30<br>10<br>20<br>10<br>20<br>30 |                                                 |                            | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

| SUPPLY CHARACTERISTICS<br>Positive Supply Current                                                                                                                                                      | I <sub>DD</sub>                                                                                                          | $V_{IH} = 2.4 \text{ V}, V_{IL} = 0.8 \text{ V}$<br>$V_{IL} = 0 \text{ V}, V_{DD} = +5 \text{ V}$                    |                                                   | 4                                               | 7<br>2                     | mA<br>mA                                                 |

| Power Dissipation <sup>7</sup>                                                                                                                                                                         | $\mathbf{P}_{\mathrm{DISS}}$                                                                                             | $V_{IL} = 0 V, V_{DD} = +3 V$<br>$V_{IH} = 2.4 V, V_{IL} = 0.8 V$<br>$V_{IL} = 0 V, V_{DD} = +5 V$                   |                                                   | 20<br>5                                         | 2<br>35<br>10              | mW<br>mW                                                 |

| Power Supply Sensitivity                                                                                                                                                                               | PSS                                                                                                                      | $\Delta V_{\rm DD} = \pm 5\%$                                                                                        |                                                   | 0.002                                           | 0.004                      | %/%                                                      |

NOTES

<sup>1</sup>1 LSB = 1 mV for 0 V to +4.095 V output range.

<sup>2</sup>Includes internal voltage reference error.

<sup>3</sup>These parameters are guaranteed by design and not subject to production testing.

<sup>4</sup>Very little sink current is available at the  $V_{REF}$  pin. Use external buffer if setting up a virtual ground. <sup>5</sup>Settling time is not guaranteed for the first six codes 0 through 5.

<sup>6</sup>All input control signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V. <sup>7</sup>Power dissipation is a calculated value  $I_{DD} \times 5$  V.

Specifications subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS\***

| $V_{DD}$ to DGND & AGND                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Inputs to DGND0.3 V, V <sub>DD</sub> + 0.3 V                                                                                            |

| $V_{OUT}$ to AGND0.3 V, $V_{DD}$ + 0.3 V                                                                                                      |

| $V_{REF}$ to AGND0.3 V, $V_{DD}$ + 0.3 V                                                                                                      |

| AGND to DGND0.3 V, V <sub>DD</sub>                                                                                                            |

| I <sub>OUT</sub> Short Circuit to GND 50 mA                                                                                                   |

| Package Power Dissipation $\dots \dots \dots$ |

| Thermal Resistance, $\theta_{JA}$                                                                                                             |

| 24-Pin Plastic DIP Package (N-24) 62°C/W                                                                                                      |

| 24-Lead SOIC Package (SOL-24)                                                                                                                 |

| Maximum Junction Temperature (T <sub>J</sub> max) 150°C                                                                                       |

| Operating Temperature Range40°C to +85°C                                                                                                      |

| Storage Temperature Range65°C to +150°C                                                                                                       |

| Lead Temperature (Soldering, 10 sec) +300°C                                                                                                   |

|                                                                                                                                               |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Timing Diagram

### **ORDERING INFORMATION\***

| Model                               | Temperature                               | Package                                   | Package        |  |

|-------------------------------------|-------------------------------------------|-------------------------------------------|----------------|--|

|                                     | Range                                     | Description                               | Option         |  |

| AD8582AN<br>AD8582AR<br>AD8582Chips | -40°C to +85°C<br>-40°C to +85°C<br>+25°C | 24-Pin Plastic DIP<br>24-Lead SOIC<br>Die | N-24<br>SOL-24 |  |

\*For die specifications contact your local Analog Devices sales office. The AD8582 contains 1270 transistors.

### **PIN DESCRIPTION**

| Pin No.                 | Name               | Description                                        |

|-------------------------|--------------------|----------------------------------------------------|

| 1, 24 V <sub>OUTA</sub> |                    | Voltage outputs from the DACs. Fixed               |

|                         | V <sub>OUTB</sub>  | output voltage range of 0 V to 4.095 V             |

|                         |                    | with 1 mV/LSB. An internal                         |

|                         |                    | temperature stabilized reference                   |

|                         |                    | maintains a fixed full-scale voltage               |

|                         |                    | independent of time, temperature and               |

|                         |                    | power supply variations.                           |

| 2                       | AGND               | Analog Ground. Ground reference for                |

|                         |                    | the internal bandgap reference voltage,            |

|                         |                    | the DAC, and the output buffer.                    |

| 3                       | DGND               | Digital ground for input logic.                    |

| 4, 21                   | LDA,               | Load DAC register strobes. Transfers               |

|                         | LDB                | input register data to the DAC registers.          |

|                         |                    | Active low inputs, Level sensitive latch.          |

|                         |                    | May be connected together to double-               |

| -                       |                    | buffer load DAC registers.                         |

| 5                       | MSB                | Digital Input: High presets DAC                    |

|                         |                    | registers to half scale $(800_{\rm H})$ , Low      |

|                         |                    | clears DAC registers to zero $(000_{\rm H})$       |

| 0                       | RST                | upon $\overline{\text{RST}}$ assertion.            |

| 6                       | RST                | Active low digital input that clears the           |

|                         |                    | DAC register to zero, setting the DAC              |

|                         |                    | to minimum scale when MSB pin = $0$ ,              |

| 7-18                    |                    | or half-scale when MSB pin = $1$ .                 |

| /-18                    | DB <sub>0-11</sub> | Twelve Binary Data Bit Inputs. DB11 is             |

| 19                      | $\overline{CS}$    | the MSB and DB0 is the LSB.                        |

|                         |                    | Chip Select. Active low input.                     |

| 20                      | Ā/B                | Select DAC $A = 0$ or DAC $B = 1$ .                |

| 22                      | V <sub>DD</sub>    | Positive Supply. Nominal value $+5$ V, $\pm 5\%$ . |

| 23                      | V <sub>REF</sub>   | Nominal 2.5 V reference output                     |

|                         |                    | voltage. This node must be buffered if             |

|                         |                    | required to drive external loads.                  |

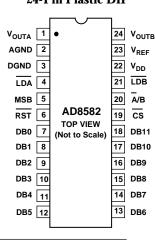

### **PIN CONFIGURATIONS**

#### N-24 24-Pin Plastic DIP

SOL-24 24-Pin SOIC

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8582 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### AD8582

| CS | $\overline{\mathbf{A}}/\mathbf{B}$ | LDA | LDB | RST | MSB | Input Register      | DAC Register        |

|----|------------------------------------|-----|-----|-----|-----|---------------------|---------------------|

| L  | L                                  | Н   | Н   | Н   | Х   | Write to A          | Latched             |

| L  | Н                                  | Н   | Н   | Н   | Х   | Write to B          | Latched             |

| L  | L                                  | L   | Н   | Н   | Х   | Write to A          | A Transparent       |

| L  | Н                                  | Н   | L   | Н   | Х   | Write to B          | B Transparent       |

| Н  | Х                                  | L   | L   | Н   | Х   | Latched             | A & B Transparent   |

| Н  | Х                                  | ^   | ٨   | Н   | Х   | Latched             | Latched             |

| Х  | Х                                  | Х   | Х   | L   | L   | Reset to Zero Scale | Reset to Zero Scale |

| Х  | Х                                  | Х   | Х   | L   | Н   | Reset to Midscale   | Reset to Midscale   |

| Н  | Х                                  | Х   | Х   | ٨   | Х   | Latch Reset Value   | Latch Reset Value   |

Table I. Control Logic Truth Table

^Denotes positive edge triggered.

### **OPERATION**

The AD8582 is a complete, ready-to-use dual 12-bit digital-toanalog converter. Only one +5 V power supply is necessary for operation. It contains two voltage-switched, 12-bit, lasertrimmed digital-to-analog converters, a curvature-corrected bandgap reference, rail-to-rail output op amps, input registers, and DAC registers. The parallel data interface consists of twelve data bits, DB0-DB11, an address select pin  $\overline{A}/B$ , two load strobe pins (LDA, LDB) and an active low  $\overline{CS}$  strobe. In addition an asynchronous  $\overline{RST}$  pin will set all DAC register bits to zero causing the V<sub>OUT</sub> to become zero volts, or to midscale for trimming applications when the MSB pin is programmed to Logic 1. This function is useful for power on reset or system failure recovery to a known state.

### **D/A CONVERTER SECTION**

The internal DAC is a 12-bit voltage-mode device with an output that swings from AGND potential to the 2.5 volt internal bandgap voltage. It uses a laser trimmed R-2R ladder which is switched by N channel MOSFETs. The output voltage of the DAC has a constant resistance independent of digital input code. The DAC output (not available to the user) is internally connected to the rail-to-rail output op amp.

### **AMPLIFIER SECTION**

The internal DAC's output is buffered by a low power consumption precision amplifier. This low power amplifier contains a differential PNP pair input stage which provides low offset voltage and low noise, as well as the ability to amplify the zeroscale DAC output voltages. The rail-to-rail amplifier is configured in a gain of 1.6384 (= 4.095 V/2.5 V) in order to set the 4.095 volt full-scale output (1 mV/LSB). See Figure 3 for an equivalent circuit schematic of the analog section.

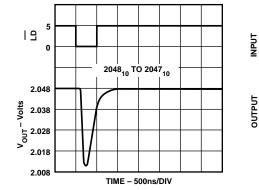

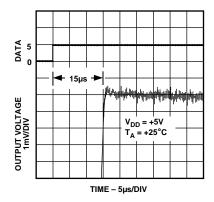

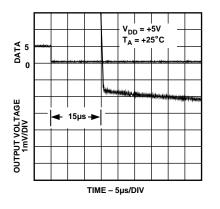

The op amp has a 16  $\mu$ s typical settling time to 0.01%. There are slight differences in settling time for negative slewing signals versus positive. See the oscilloscope photos in the Typical Performances section of this data sheet.

Figure 3. Equivalent Schematic of Analog Portion

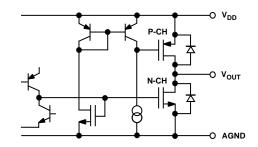

### **OUTPUT SECTION**

The rail-to-rail output stage of this amplifier has been designed to provide precision performance while operating near either power supply. Figure 4 shows an equivalent output schematic of the rail-to-rail amplifier with its N channel pull-down FETs that will pull an output load directly to GND. The output sourcing current is provided by a P channel pull-up device that can supply GND terminated loads, especially important at the -5% supply tolerance value of 4.75 volts.

Figure 4. Equivalent Analog Output Circuit

Figures 5 and 6 in the typical performance characteristics section provide information on output swing performance near ground and full-scale as a function of load. In addition to resistive load driving capability, the amplifier has also been carefully designed and characterized for up to 500 pF capacitive load driving capability.

### **REFERENCE SECTION**

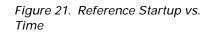

The internal 2.5 V curvature-corrected bandgap voltage reference is laser trimmed for both initial accuracy and low temperature coefficient. The voltage generated by the reference is available at the  $V_{REF}$  pin. Since  $V_{REF}$  is not intended to drive external loads, it must be buffered. The equivalent emitter follower output circuit of the  $V_{REF}$  pin is shown in Figure 3.

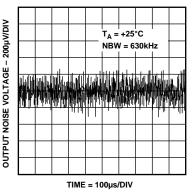

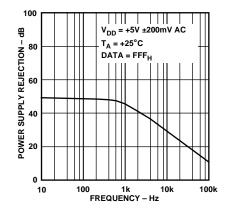

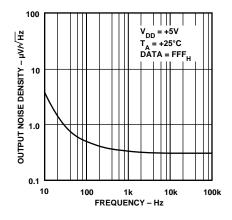

Bypassing the  $V_{REF}$  pin will improve noise performance; however, bypassing is not required for proper operation. Figure 8 shows broadband noise performance.

### **POWER SUPPLY**

The very low power consumption of the AD8582 is a direct result of a circuit design optimizing use of the CBCMOS process. By using the low power characteristics of the CMOS for the logic, and the low noise, tight matching of the complementary bipolar transistors good analog accuracy is achieved.

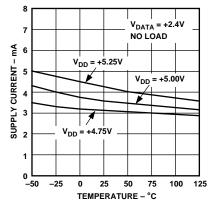

For power-consumption sensitive applications it is important to note that the internal power consumption of the AD8582 is strongly dependent on the actual logic-input voltage levels present on the DB0–DB11,  $\overline{CS}$ ,  $\overline{A}/B$ , MSB,  $\overline{LDA}$ ,  $\overline{LDB}$  and RST pins. Since these inputs are standard CMOS logic structures they contribute static power dissipation dependent on the actual driving logic V<sub>OH</sub> and V<sub>OL</sub> voltage levels. The graph in Figure 9 shows the effect on total AD8582 supply current as a function of the actual value of input logic voltage. Consequently, for optimum dissipation use of CMOS logic versus TTL provides minimal dissipation in the static state. A V<sub>INL</sub> = 0 V on the DB0–11 pins provides the lowest standby dissipation of 1 mA typical with a +5 V power supply.

As with any analog system, it is recommended that the AD8582 power supply be bypassed on the same PC card that contains the chip. Figure 10 shows the power supply rejection versus frequency performance. This should be taken into account when using higher frequency switched-mode power supplies with ripple frequencies of 100 kHz and higher.

One advantage of the rail-to-rail output amplifiers used in the AD8582 is the wide range of usable supply voltage. The part is fully specified and tested over temperature for operation from +4.75 V to +5.25 V. If reduced linearity and source current capability near full scale can be tolerated, operation of the AD8582 is possible down to +4.3 volts. The minimum operating supply voltage versus load current plot, in Figure 1, provides information for operation below  $V_{DD} = +4.75$  V.

### TIMING AND CONTROL

The input registers are level triggered and acquire data from the data bus during the time period when  $\overline{CS}$  is low. The input register selected is determined by the  $\overline{A}/B$  select pin, see Table I. for a complete description. When  $\overline{CS}$  goes high, the data is latched into the register and held until  $\overline{CS}$  returns low. The minimum time required for the data to be present on the bus before  $\overline{CS}$  returns high is called the data setup time ( $t_{DS}$ ) as seen in Timing Diagram. The data hold time ( $t_{DH}$ ) is the amount of time that the data has to remain on the bus after  $\overline{CS}$  goes high. The high speed timing offered by the AD8582 provides for direct interface with no wait states in all but the fastest microprocessors.

The data from the input registers is transferred to the DAC registers by the active low  $\overline{\text{LDA}}$  and  $\overline{\text{LDB}}$  pins. If these inputs are tied together, a single logic input can perform a double buffer update of the DAC registers, which in turn simultaneously changes the analog output voltages to a new value. If the  $\overline{\text{LDA}}$  and  $\overline{\text{LDB}}$  pins are wired low, they become transparent. In this mode the input register data will directly control the output voltages. Refer to the Control Logic Truth Table for a complete description.

### **Unipolar Output Operation**

This is the basic mode of operation for the AD8582. The AD8582 has been designed to drive loads as low as  $820\Omega$  in parallel with 500 pF. The code table for this operation is shown in Table II.

| Hexadecimal<br>Number in DAC<br>Register | Decimal Number<br>in DAC Register | Analog Output<br>Voltage (V) |  |  |

|------------------------------------------|-----------------------------------|------------------------------|--|--|

| FFF                                      | 4095                              | + 4.095                      |  |  |

| 801                                      | 2049                              | + 2.049                      |  |  |

| 800                                      | 2048                              | + 2.048                      |  |  |

| 7FF                                      | 2047                              | + 2.047                      |  |  |

| 000                                      | 0                                 | 0                            |  |  |

Table II. Unipolar Code Table

## AD8582–Typical Performance Characteristics

Figure 5. Output Swing vs. Load

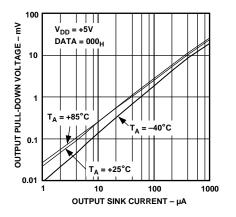

Figure 6. Pull-Down Voltage vs. Output Sink Current Capability

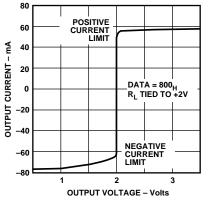

Figure 7. Iout vs. Vout

Figure 8. Broadband Noise

Figure 9. Supply Current vs. Logic Input Voltage

Figure 10. Power Supply Rejection vs. Frequency

Figure 11. Midscale Transition Performance

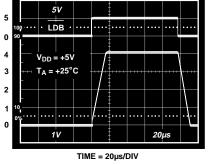

Figure 12. Large Signal Settling Time

Figure 13. Output Voltage Rise Time Detail

### AD8582

Figure 14. Output Voltage Fall Time Detail

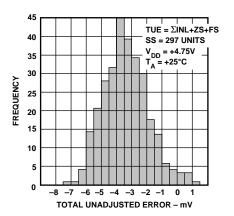

Figure 15. Total Unadjusted Error Histogram

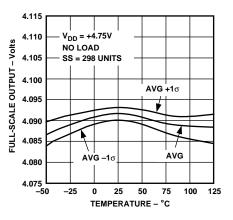

*Figure 16. Full-Scale Voltage vs. Temperature*

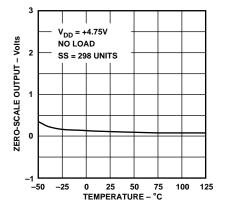

*Figure 17. Zero-Scale Voltage vs. Temperature*

Figure 18. Output Voltage Noise Density vs. Frequency

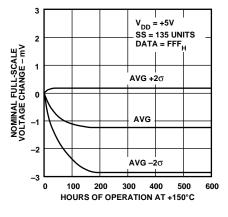

Figure 19. Long-Term Drift Accelerated by Burn-In

$V_{DD}$   $V_{REF}$   $V_{UV}$   $V_{REF}$   $V_{UV}$   $V_{REF}$   $V_{UV}$   $V_{UV}$

*Figure 20. Supply Current vs. Temperature*

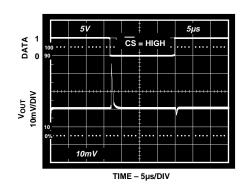

Figure 22. Digital Feedthrough vs. Time

### AD8582

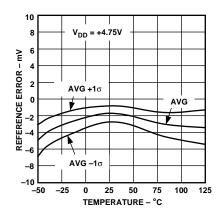

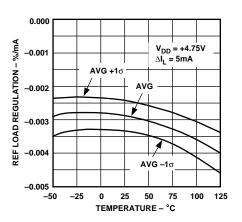

Figure 23. Reference Error vs. Temperature

Figure 24. Reference Load Regulation vs. Temperature

Figure 25. Reference Line Regulation vs. Temperature

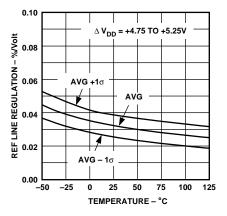

N-24 24-Pin Narrow Body Plastic DIP

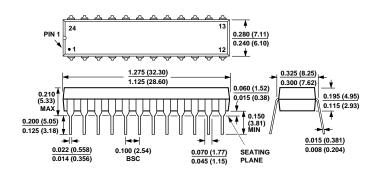

SOL-24 24-Lead Wide Body SOIC

C1869-18-12/93